(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель девиации частоты | 1976 |

|

SU575578A1 |

| Измеритель девиации частоты | 1990 |

|

SU1698818A2 |

| Калибратор девиации частоты частотно-модулированных сигналов | 1987 |

|

SU1511703A1 |

| Устройство для измерения девиации частоты | 1982 |

|

SU1104434A1 |

| ИЗМЕРИТЕЛЬ ДЕВИАЦИИ ЧАСТОТЫ ЧАСТОТНО-МОДУЛИРОВАННЫХ КОЛЕБАНИЙ | 1991 |

|

RU2019843C1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для воспроизведения мно-гОКАНАльНОй МАгНиТНОй зАпиСи | 1979 |

|

SU836662A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

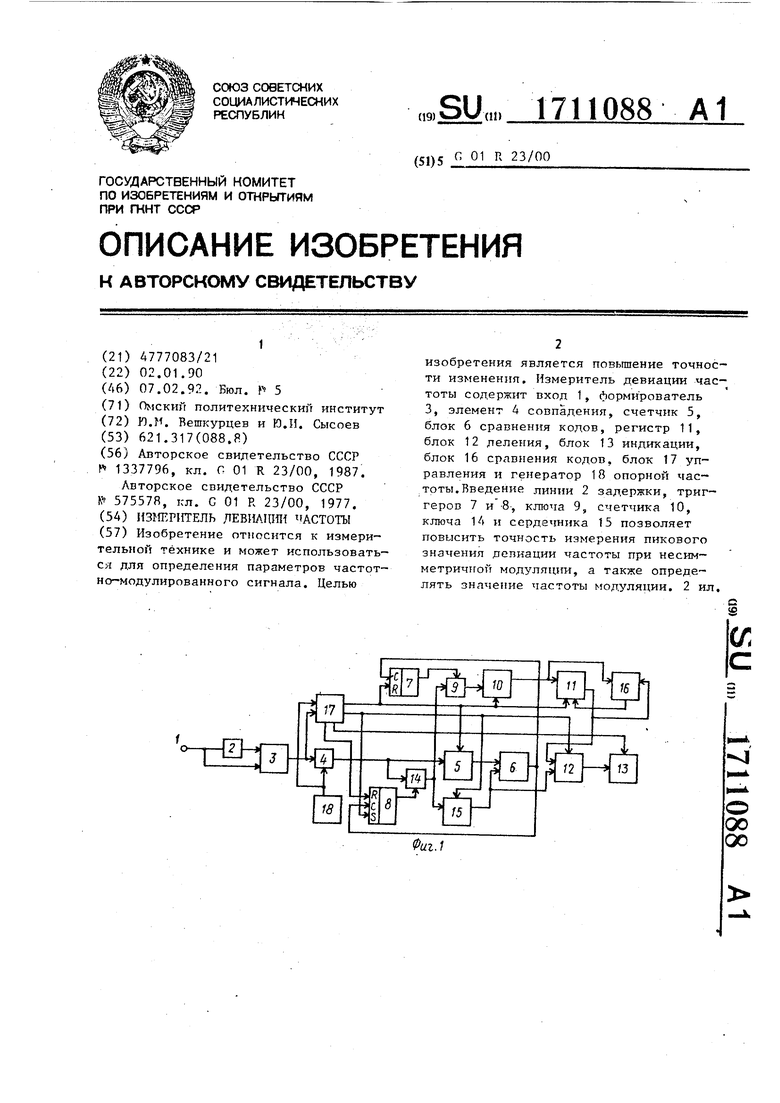

Изобретение относится к измерительной технике и может использоваться для определения параметров частотно-модулированного сигнала. Целью изобретения является повышение точности изменения. Измеритель девиации 4ac-t тоты содержит вход 1, формирователь 3, элемент 4 совпадения, счетчик 5, блок 6 сравнения кодов, регистр 11, блок 12 деления, блок 13 индикации, блок 16 сравнения кодов, блок 17 управления и генератор 18 опорной частоты. Введение линии 2 задержки, триггеров 7 и -8, ключа 9, счетчика 10, ключа 14 и сердечника 15 позволяет повысить точность измерения пикового значения девиации частоты при несимметричной модуляции, а также определять значение частоты модуляции. 2 ил.

Фиг.1

00

оо

Изобретение относится к измерительной технике и может быть использовано при измерении девиации частоты.

Известны измерители девиации час- тотьг, преобразующие входной частотно- модулированный сигнал в последовательность прямоугольных импульсов, тельность которых пропорциональна закону модуляции. К примеру, известно iустройство, которое содержит Формиро- ,ватель, два вентиля, два счетчика, блок вычитания, селектор, накапливающий сумматор, вычислительный блок, (блок индикации и блок управления. При (проведении измерений устройство определяет среднее значение девиации частоты, что обусловливает его высокую точность при любом отклонении закона модуляции от заданного закона.

Наиболее близким техническим решением к изобретению является измеритель девиации частоты, содержащий включенные последовательно вход из- мерителя, формирователь, элемент совпадения, счетчик, первый блок сравнения кодов, а также включенные последовательно второй блок сравнения кодов, регистр, вычислительное уст- ройство и блок индикации, второй вход которого подключен к третьему выходу блока управления, у которого первый выход присоединен к входу Сброс счетчика, второй выход - к третьему входу вычислительного устройства, первый к выходу Формирователя, и генератор опорной частоты, выход которого присоединен к свободно- му входу элемента совпадения и к. второму входу блока управления, тогда как первый и второй входы второго блока сравнения кодов подключены соответственно к первому входу и выходу ,регистра. Работа этого устройства заключается в том, что в течение измерительного цикла оно выделяет N«MMH и Np импульсов, пропорциональных соответственно девиации круговой частоты вверх и девиации круговой частоты вниз, которые могут быть вычислены по формулам вида

лсов «в-со0}дсо„ со0-сам, (1)

где Д6ЭВ девиация круговой частоты

вверх ;

йСОн девиация круговой частоты

С00- круговая частота в отсутствии модуляции;

COg- верхняя составляющая спектра сигнала с частотной модуляцией ;

СО ц- нижняя составляющая спектра сигнала с частотной модуляцией .

В известном измерителе число импульсов и экстремальные составляющие спектра сигнала связаны соотношениями

1Г

Nr

/ it

-on. «в PWQKC

Т„„ СОИ

(2)

где ifln - период, частоты

нератора.

Производимые преобрачислительном устройстве выделить значения ДСО и зультат выдается в виде

АОЭ6 + ДСОи

лоэ

пик

Используя известное соотношение ДСО 2/R&f, выражение (3) может быть записано как

fifft +

&f

Af«

пик.

(4)

Недостатком измерителя является следующее. При условии Д СО ft Д СО н , т.е. несимметричной модуляции, возникает погрешность в вычислении реального пикового значения девиации частоты. Например, пусть параметры частотно-модулированного колебания имеют следующие значения: & fц 100 Гц, Л fв 1000 Гц. Тогда по Формуле (4) ДГПИК 550 Гц, что не соответствует реальному пиковому значению, равному 1000 Гц, а погрешность измерения при этом составит. }55%.

Цель изобретения - повышение точности измерения девиации частоты.

Указанная цель достигается тем, что в измеритель девиации частоты, содержащий включенные последовательно вход устройства, Формирователь, элемент совпадения, счетчик и первый блок сравнения кодов, а также включенные последовательно второй блок сравнения кодов, регистр, вычислителное устройство и блок индикации, вто рой вход которого подключен к третьему выходу блока управления, у которого первый выход присоединен к входу Сброс счетчика, второй выход - к

второму входу вычислительного устройства, а первый вход - к выходу формирователя, и генератор опорной частоты, выход которого присоединен к свободному входу элемента совпадения и к второму входу блока управления, тогда как первый и вторбй входы вторго блока сравнения кодов подключены, соответственно, к первому входу и вы ходу регистра, введены линия задержки и две идентичные цепи из последовательно включенных триггера, ключа и счетчика импульсов выход которого подключен к первому входу регистра, третий вход которого одновременно при присоединен к шине Сброс счетчика первой цепи и к первому выходу блока управления. Выход счетчика второй. цепи подключен к второму входу вычиё- лительного устройства и к второму .входу первого блока сравнения кодову выход которого подключен к счетному входу триггера каждой цепи, R-вход триггера первой из которых присреди- нен к первому выходу блока управления, а S-вход и R-вход триггера второй цепи подключены, соответственно- к второму и четвертому выходам блока управления, ВТОРОЙ ВЫХОД КОТОРОГО

присоединен к входу Сброс счетчика второй цепи, в которой свободный вход ключа присоединен к выходу элемента совпадения, а выход ключа -;-- к свободному входу ключа первой цепи. Между двумя входами Аормирователя подключена линия задержки.

Использование новых блоков позволяет осуществить преобразование частота-фазовый сдвиг-интервал вре- мени и провести измерения максимали- ных значений базовых: сдвигов вместо измерения минимальных и максимальных значений частоты при преобразовании частота-интервал времени. На- личие максимальных фазовых сдвигов значительно повышает точность измерения пикового значения девиации частоты даже при условии ДОЭц ф ЛСОВ .

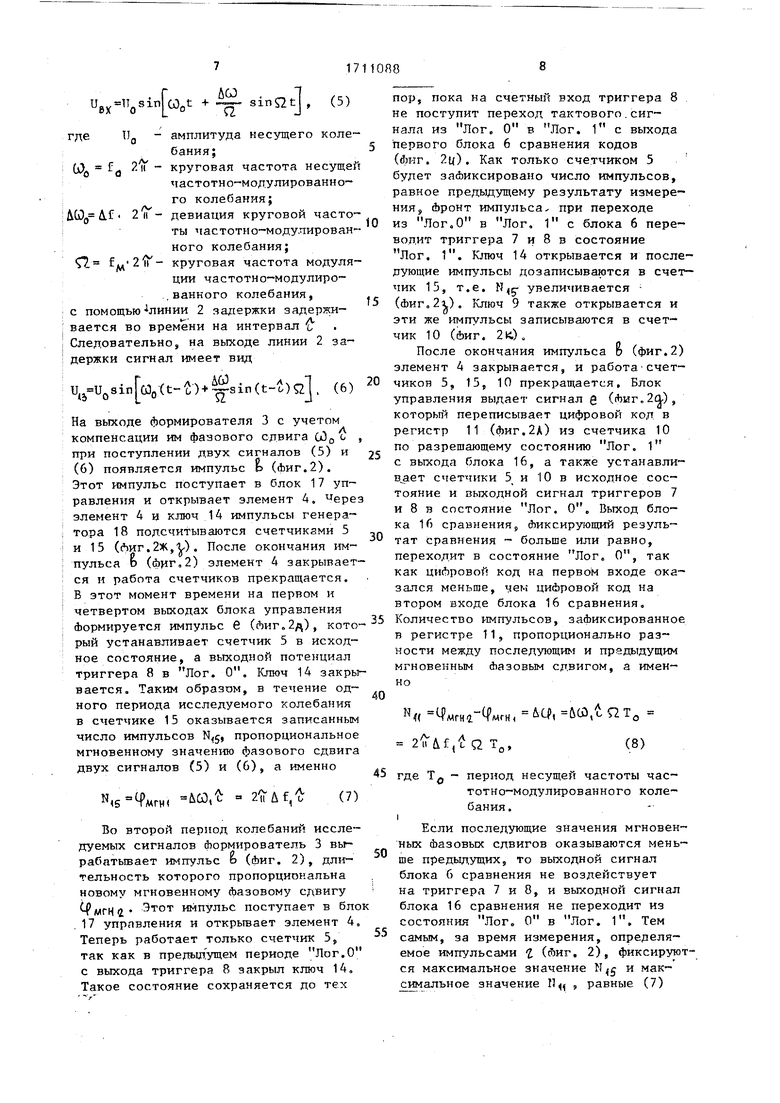

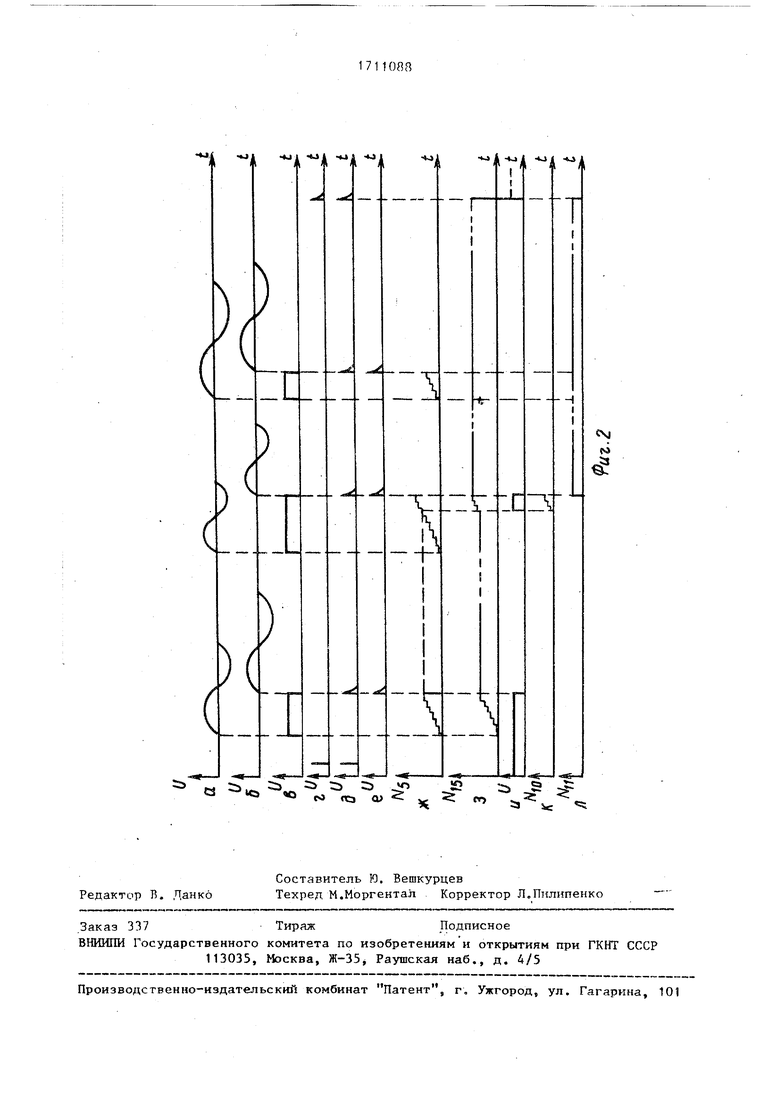

На йшг. 1 представлена структур- ная схема измерителя девиации частоты; на фиг. 2 - временные диаграммы, поясняющие работу измерителя.

Измеритель, девиации частоты содержит включенные последовательно вход 1, линию 2 задержки, формирова- тель 3, элемент 4 совпадения, счётчик 5 импульсов, nepBbtfi блок 6 сравнения кодов, выход которого подключен

к счетному входу триггеров 7 и 8, кроме того, линия 2 задержки включен между первым и вторым входами формирователя 3, Триггер 7, ключ 9 и счетчик 10 образуют первую .цепь, выход которой подключен к последовательному соединению регистра 11, блока 12 деления и блока 13. индикации. Выход второй цепи, образованной триггером 8, ключом 14 и счетчикрет 15, присоединен к второму входу первого блока 6 сравнения кодов и второму входу блока 12 деления. К второму входу ключа 9 присоединён выход ключа 14, у которого второй вход подключен к выходу элемента -4 совпадения. К первому входу регистра 11 подключен выход блока 16 сравнения кодов, первый и второй входы которого присоединены .соответственно, к второму входу и выходу регистра И. Выход формирова- теля 3 подключен к первому входу блока 17 управления, второй вход которого подключен к второму входу элемента 4 совпадения.и выходу генератора 18 опорной частоты. Первый выход блока 17 управления подключен к R-входу триггера 7, входам сброса счетчиков 5 и 10, регистра 11, второй выход - к 5-входу триггера 8, входам сброса счетчика 15 и блока 12 деления, третий выход - к второму входу блока 13 индикации, а четвертый выход - к R-входу триггера 8.

С целью четкого изложения последующего материала обозначим низкий потенциал - логическим нулем - (Лог.0),а высокий потенциал - логической единицей (Лог. 1).

Измеритель работает следующим образом.

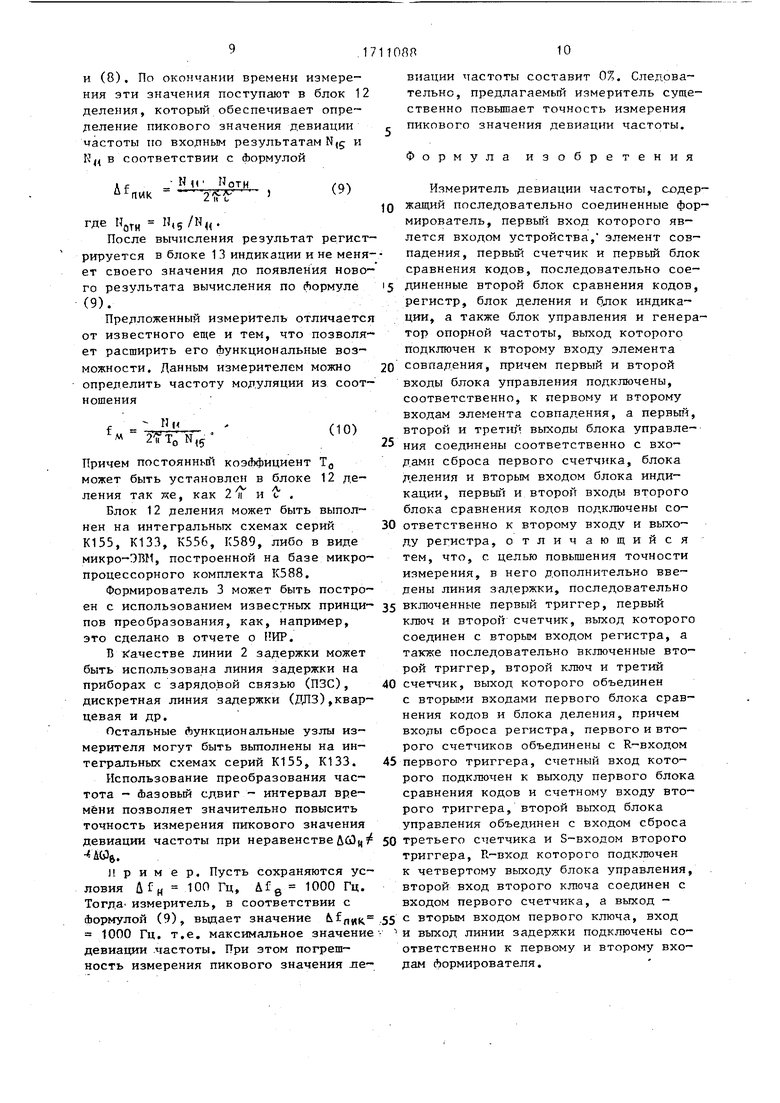

Момент начала измерения фиксируется импульсом с первого и второго выходов блока 1.7 управления (фиг. 22 ). Этот импульс является установочным для счетчиков 5, 10, 15, регистра . 1 1 , триггера 7, блока 12 деления, на информационных выходах которых присутствует Лог, 0. При этом выходной сигнал триггера 8, блоков 6 и 16 сравнения кодов равен Лог.1.. В этот же момент времени в блоке 12 деления формируются постоянные коэф- фициенты -21Г и t- , гдеЈ - постоянная времени линии 2 задержки.

Поступающее на вход 1 частотно- модулированное колебание а (фиг.2), например, вида

,,sin|cortt +

UCO

о.

sinQt

WA

Ш,- Af 2Ггде U0 - амплитуда несущего колебания;

2( - круговая частота несущей час тотно-модулированн о- го колебания; девиация круговой частоты частотно-модулированного колебания; круговая частота модуляции частотно-модулиро- ,,ванного колебания, с помощью ;линии 2 задержки задерживается во времени на интервал Ј . Следовательно, на выходе линии 2 задержки сигнал имеет вид

С1- Јм 21Гм

15

VUosin

in(,)(t-Ј)Ј(

Ha выходе формирователя 3 с учетом компенсации им фазового сдвига (00 о , при поступлении двух сигналов (5) и 25 (6) появляется импульс f (фиг.2). Этот импульс поступает в блок 17 управления и открывает элемент 4. иерез элемент 4 и ключ 14 импульсы генератора 18 подсчитываются счетчиками 5 ,Q и 15 (Аит.2ж,г.). После окончания импульса Ь (фиг.2) элемент 4 закрывается и работа счетчиков прекращается. В этот момент времени на первом и четвертом выходах блока управления Формируется импульс 6 (Фиг.2д), кото-35 рый устанавливает счетчик 5 в исходное состояние, а выходной потенциал триггера 8 в Лог. О. Ключ 14 закрывается. Таким образом, ъ течение одного периода исследуемого колебания в счетчике 15 оказывается записанным число импульсов N,5, пропорциональное мгновенному значению фазового сдвига двух сигналов (5) и (6), а именно

(5)пор, пока на счетный вход триггера 8 не поступит переход тактового.сигнала из Лог. О в Лог, 1 с выхода

5 первого блока 6 сравнения кодов

(фиг. 2ц). Как только счетчиком 5 будет зафиксировано число импульсов, равное предыдущему результату измерения, фронт импульса, при переходе

10 из Лог.О в Лог. 1 с блока 6 переводит триггера 7 и 8 в состояние Лог. 1. Ключ 14 открывается и последующие импульсы дозаписываются в счетчик 15, т.е. N увеличивается ; (Фиг.2О. Ключ 9 также открывается и эти же импульсы записываются в счетчик 10 (Фиг. 2),

После окончания импульса & (фиг.2) элемент 4 закрывается, и работа счет(6) чиков 5, 15, 10 прекращается. Блок

управления выдает сигнал Q (Фиг.2д), который переписывает цифровой код в регистр 11 (фиг.2А) из счетчика 10 по разрешающему состоянию Лог. 1 с выхода блока 16, а также устанавли- в,ает счетчики 5 и 10 в исходное состояние и выходной сигнал триггеров 7 и 8 в состояние Лог. О. Выход блока 16 сравнения, Фиксирующий результат сравнения - больше или равно, переходит в состояние Лог. О, так как цифровой код на первом входе оказался меньше, чем цифровой код на втором входе блока 16 сравнения. Количество импульсов, зафиксированное в регистре 11, пропорционально разности между последующим и предыдущим мгновенным Фазовым сдвигом, а именно

40

N« -MW-tpMn,, ь& ,t я.т,

-.А 2 и ЛЈ,Јй Т0,

(8)

45

где Т0 - период несущей частоты частотно-модулированного колебания.

UCOtt

л.

(7)

Во второй период колебаний исследуемых сигналов Формирователь 3 вы- рабатывает импульс о (фиг. 2), длительность которого пропорциональна новому мгновенному фазовому сдвигу РмгНй- Этот импульс поступает в бло 17 управления и открывает элемент 4. Теперь работает только счетчик 5, так как в предыдущем периоде Лог.О с выхода триггера 8 закрыл ключ 14. Такое состояние сохраняется до тех

N« -MW-tpMn,, ь& ,t я.т,

-.А 2 и ЛЈ,Јй Т0,

(8)

где Т0 - период несущей частоты частотно-модулированного колебания.

Если последующие значения мгновенных фазовых сдвигов оказываются меньше предыдущих, то выходной сигнал блока 6 сравнения не воздействует на триггера 7 и 8, и выходной сигнал блока 16 сравнения не переходит из состояния Лог. О в Лог. 1. Тем самым, за время измерения, определяемое импульсами 1 (Фиг. 2), фиксируются максимальное значение N и мак- симальное значение П , равные (7)

и (8), По окончании времени измерения эти значения поступают в блок 1.2 деления, который обеспечивает определение пикового значения девиации частоты по входным результатам N,g и Кц в соответствии с формулой

N

оти

(9)

10

где NQTH ,5/N«После вычисления результат регистрируется в блоке 13 индикации и не меня-- ет своего значения до появления ново го результата вычисления по Лормуле tj (9).

Предложенный измеритель отличается от известного еще и тем, что позволя ет расширить его функциональные возможности. Данным измерителем можно 20 определить частоту модуляции из соотношения

f.. н« ,

м 2ТТ« N,

(Ю)

Ао 15 .-..-/ Причем постоянный коэффициент Т0 может быть установлен в блоке 12 де-г ления так же, как 2/п/ и Ј .

Блок 12 деления может быть выполнен на интегральных схемах серий К155, К133, К556, К589, либо в виде микро-ЭВМ, построенной на базе микропроцессорного комплекта К588.

Формирователь 3 может быть построен с использованием известных принцип пов преобразования, как, например, это сделано в отчете о НИР.

В Качестве линии 2 задержки может быть использована линия задержки на приборах с зарядовой связью (ПЗС), ; дискретная линия задержки (ДПЗ),кварцевая и др.

Остальные функциональные узлы измерителя могут быть выполнены на интегральных схемах серий К155, К133.

Использование преобразования частота - фазовьй сдвиг - интервал времени позволяет значительно повысить точность измерения пикового значения девиации частоты при неравенстве ДОЗ ц

.

I р и м е р. Пусть сохраняются условия ufH 100 Гц, if0 1000 Гц-«, Тогда- измеритель, в соответствии с . формулой (9), выдает значение A f лик5 1000 Гц. т.е. максимальное значение девиации частоты. При этом погреш- ность измерения пикового значения де0

j

0

5

0

5

0

5

0

5 л

виации частоты составит 0%. Следовательно, предлагаемый измеритель существенно повышает точность измерения пикового значения девиации частоты.

Формула изобретения

Измеритель девиации частоты, содержащий последовательно соединенные формирователь, первый вход которого яв- лется входом устройства, элемент совпадения, первый счетчик и первый блок сравнения кодов, последовательно соединенные второй блок сравнения кодов, регистр, блок деления и блок индикации,, а также блок управления и генератор опорной частоты, выход которого подключен к второму входу элемента совпадения, причем первый и второй входы блока управления подк-лючены, соответственно, к первому и второму входам элемента совпадения, а первый, второй и третий выходы блока управления соединены соответственно с входами сброса первого счетчика, блока деления и вторым входом блока индикации, первый и второй входы второго блока сравнения кодов подключены соответственно к второму входу и выходу регистра, о т ли ч а ю щи и с я - тем, что, с целью повышения точности измерения, в него дополнительно введены линия задержки, последовательно включенные первый триггер, первый ключ и второй счетчик, выход которого соединен с вторьм входом регистра, а также последовательно включенные второй триггер, второй ключ и третий счетчик, выход которого объединен с вторыми входами первого блока сравнения кодов и блока деления, причем входы сброса регистра, первого и второго счетчиков объединены с R-входом первого триггера, счетный вход которого подключен к выходу первого блока сравнения кодов и счетному входу второго триггера, второй выход блока управления объединен с входом сброса третьего счетчик а и S-входом второго триггера, R-вход которого подключен к четвертому выходу блока управления, второй вход второго ключа соединен с входом первого счетчика, а выход - с вторым входом первого ключа, вход и выход, линии задержки подключены соответственно к первому и второму входам формирователя.

| Устройство для измерения девиации частоты ЧМ-сигналов | 1985 |

|

SU1337796A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Измеритель девиации частоты | 1976 |

|

SU575578A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-02-07—Публикация

1990-01-02—Подача