Изобретение относится к вычислительной технике и может быть использовано при построении многопроцессорных, вычислительных систем.

Известно устройство для распределения заданий процессорам.

Однако известное устройство не обеспечивает приоритетную обработку входят щих заданий.

Наиболее близким к изобретению по технической сущности является устройство для распределения заданий процессорам, содержащее группу входов приоритета задания, группу сигнальных входов/группу входов номера задания, запросный вход, регистр готовности процессоров, регистр приоритета задания, регистр адреса записи приоритета задания, блок памяти приоритетов заданий, блок памяти упорядоченных приоритетов заданий, блок памяти номеров заданий, узел сортировки информации, два блока управления, дешифратор,

шифратор, группы элементов И, блоки элементов И, группы элементов ИЛИ, элементы ИЛИ, схемы сравнения, генератор импульсов, элементы И, триггер, элементы задержки, блок элементов задержки, сигнальный выход устройства.

Однако данное устройство обладает недостаточным быстродействием.

Недостаточное быстродействие обусловлено тем, что независимо от прочих обстоятельств (например, готовности процессоров) при очередном распределении всегда осуществляется обход процессоров, начиная с первого.

Цель изобретения - увеличение быстродействия устройства за счет обхода только готовых к работе процессоров и исключения необходимости составления списка упорядоченных приоритетов.

Поставленная цель достигается тем, что в устройство для распределения заданий процессорам, содержащее регистр готовно(Л

С

о

ю

сти процессоров, регистр приоритета заданий, регистр номера задания, дешифратор, блок памяти номеров процессоров, блок памяти приоритетов заданий, блок памяти списков заданий процессоров, схему сравнения, группу блоков элементов И, группу элементов задержки, генератор импульсов, два элемента ИЛИ, элемент задержки, элемент И, причем группа информационных входов регистра готовности процессоров соединена с группой сигнальных входов устройства, группа входов номера задания устройства соединена с информационными входами регистра номера задания, выходы которого соединены с информационными входами дешифратора и блоков элементов И группы, группа входов приоритета заданий устройства соединена с информационными входами регистра приоритета заданий, выходы которого соединены с второй-группой входов схемы сравнения, первая группа входов которой соединена с информационным выходом блока памяти приоритетов заданий, выход генератора импульсов соединен с вторым входом элемента И, введены группа элементов И-НЕ, группа элементов НЕ, группа триггеров, группа схем сравнения, мультиплексор, первый и второй блоки элементов И, элемент ИЛИ-НЕ, второй элемент И, элемент НЕ, причем входы 1-го элемента И-НЕ соединены соответственно с 1-м выходом регистра готовности процессоров, с выходом элемента И и с входом управления схемы сравнения, с выходом 1-го элемента задер-. жки, с выходами всех предшествующих элементов И-НЕ группы, вход 1-го элемента НЕ группы соединен с выходом 1-го элемента И-НЕ, выход 1-го эг .мента НЕ группы соединен с входом установки в 1 1-го триггера, сН-м адресным входом блока памяти списков заданий процессорам, с соответствующим входом первой группы информационных входов мультиплексора, с информационным входом соответствующего элемента И первого блока, с соответствующим входом элемента ИЛИ-НЕ, выход которого соединен с входами установки в О триггеров группы и с вторым входом второго элемента И, первый вход которого соединен с выходом элемента НЕ, вход которого соединен с выходом первого элемента ИЛИ и с первыми управляющими входами мультиплексора и элементов И первого и второго блоков, инверсный выход 1-го триггера соединен с входом 1-го элемента задержки группы, входы первого элемента ИЛИ соедйнены с выходами схем сравнения группы, первые и вторые группы информационных входов которых соединены с определенными информационными выходами блока памяти списков заданий и процессора и с информационными выходами регистра номера задания соответственно, третий вход второго элемента И- соединен с первым выходом схемы сравнения, второй выход которой соединен с вторыми управляющими входами элементов И первого и второго блоков, информацион0 ные входы второго блока элементов И соединены с выходом регистра приоритета заданий, выходы первого и второго блоков элементов И соединены с входами записи блока памяти номеров процессоров и блока

5 памяти приоритетов заданий соответственно, первый выход дешифратора соединен с первым входом элемента И, другие выходы дешифратора соединены с соответствующими адресными входами блока памяти но0 меров процессоров и блока памяти приоритетов заданий, выход второго элемента И соединен с вторым управляющим, входом мультиплексора, вторая группа информационных входов которого соединена.

5 с информационными выходами блока памяти номеров процессоров, выходы мультиплексора являются сигнальными выходами устройства и соединены соответственно с управляющими входами блоков элементов

0 И группы и с входами второго элемента ИЛИ, выход которого соединен с входом элемента задержки, выход которого соединен с входами установки в О регистра приоритета заданий и регистра номера

5 заданий, входы установки в О разрядов регистра готовности процессоров соединены с соответствующими входами группы ответных входов устройства, выходы блоков элементов И группы являются информаци0 онными выходами устройства.

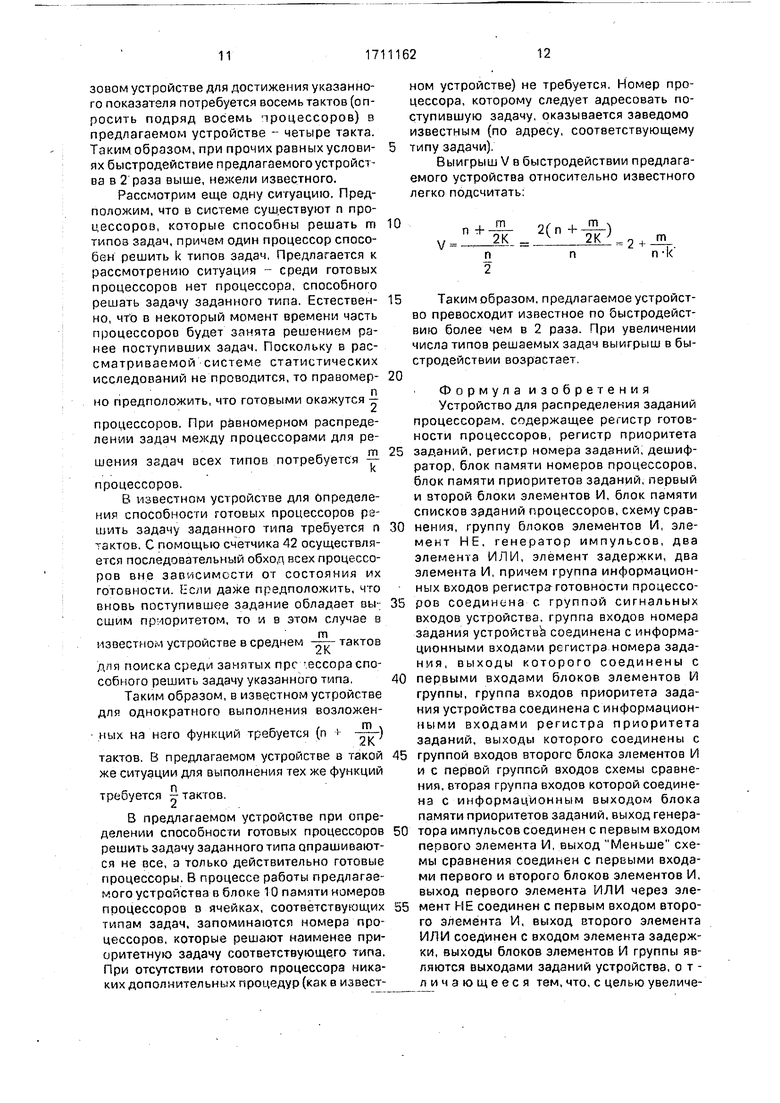

На чертеже представлена функциональная схема предлагаемого устройства для распределения заданий процессорам. Устройство содержит группу 1 сйгналь5 ных входов устройства, группу 2 входов приоритета заданий устройства, группу 3 входов номера задания устройства, регистр А готовности процессоров, регистр 5 приоритета заданий, рёгистрб номера задания.

0 дешифратор 7, генератор 8 импульсов, элемент И 9, блок 10 памяти номеров процессоров, блок 11 памяти приоритетов заданий, схему 12 сравнения, группу элементов И-НЕ 13, группу элементов НЕ

5 14, группу триггеров 15, блок 16 памяти списков заданий процессорам, группу схем 17 сравнения, первый элемент ИЛИ 18, мультиплексор 19, группу 20 сигнальных выходов устройства, группу блоков 21 элементов И, группы 22 информационных выходов

устройства, первый 23 и второй 24 блоки элементов И, второй элемент ИЛИ 25, элемент ИЛИ-НЕ 26, элемент НЕ 27. второй элемент И 28, группу элементов 29 задержки, элемент 30 задержки, группу 31 ответ- ных входов устройства.

Сущность изобретения заключается в следующем.

Введение групп элементов И-НЕ, НЕ и группы триггеров позволяет избежать при очередном распределении перебора всех (включая и занятые) процессоров, начиная с первого. В предлагаемом устройстве анализируются возможности только готовых (свободных от решения задач) процессоррв. Изменение порядка хранения информации о приоритетах, номерах заданий и номерах процессоров в блоках памяти и введение группы схем сравнения ускоряет процесс снятия задания с малым приоритетом с об- служивания с последующей передачей освобожденного процессора для реализации более приоритетного задания.

Устройство работает следующим образом.

В исходном состоянии регистры 4-6 и триггеры 15 обнулены; в блок 16 памяти списков заданий процессорам в каждую из строк занесен список номеров заданий, выполняемых соответствующим процес- сором, во все разряды всех строк блока 11 памяти приоритетов заданий занесены 1 (цепи установки в исходное состояние не показаны).. - ,

По входам 1 по мере выполнения ранее принятых на обработку заданий от процессоров поступают сигналы готовности и записываются в соответствующие разряды регистра 4,

От пользователей по входам 3 поступа- ет информация о номере задания. Данная информация состоит как бы из двух групп разрядов: первая группа указывает номер пользователя (абонента), вторая - нрмер задачи, характеризующий ее тип (один поль- зователь обладает правом на решение задач нескольких типов). По входам 2 одновременно с номером задания пользователь выставляет приоритет задания (задачи одного типа у разных пользователей при раз- личных условиях обстановки могут иметь различные приоритеты). Значение приоритета принимается в регистр 5. а номер задания - в регистр 6.

Как только в регистре 6 окажется инфор- мация, отличная от нулевой, на первом выходе дешифратора 7 сформируется сигнал единичного уровня, который поступает на первый вход элемента И 9. Тактовые импульсы с выхода генератора 8 через элемент

И 9 начинают поступать на управляющий вход схемы 12 сравнения и на соответствующие входы элементов И-НЕ 13 группы. Сигналы нулевого уровня могли бы появиться на выходе любого из элементов И- НЕ 13, которым соответствуют единичные значения разрядов регистра 4, с приходом очередного тактового импульса. Однако сигнал нулевого уровня появится на выходе только оДного элемента И-НЕ 13, которому соответствует младший из разрядов регистра 4, находящийся в единичном состоянии. Допустим, это i-й разряд. Сигнал нулевого уровня с выхода 1-го элемента И- НЕ 13, поступая на входы всех последующих элементов И-НЕ 13 группы, блокирует возможность появления на их выходах сигналов нулевого уровня. Сигнал нулевого уровня с выхода 1-го элемента И-НЕ 13 поступает на вход 1-го элемента НЕ 14. Сигнал единичного уровня с выхода 1-го элемента

14НЕ поступает на соответствующий адресный вход блока 16 памяти списков заданий и на вход установки в 1 1-го триггера 15, С переходом i-ro триггера 15 в 1 сигнал нулевого уровня с его инверсного выхода поступает на вход i-ro элемента 29 задержки группы и через него на один из входов 1-го элемента И-НЕ 13, где блокирует возможность повторного появления сигнала нулевого уровня на его выходе. Задержка элементов 29 выбирается достаточной для выполнения устройством своих функций, но меньшей, нежели период следования тактовых импульсов генератора 8. С приходом сигнала единичного уровня на адресный вход блока 16 производится считывание строки информации, содержащей список типов задач, выполняемых i-м процессором. Размер строки определяется максимальным количеством типов задач, решаемых одним процессором. (Например, процессор способен решать задачи

15типов. Строка должна содержать 15 групп по четыре разряда - 60 разрядов). Если какой-то из процессоров решает меньший круг задач, то соответствующие группы разрядов строки должны содержать нулевую информацию. Информация считанной строки по группам разрядов передается на первые входы соответствующих схем 17 сравнения группы. На вторые входы всех схем 17 сравнения группы поступает информация о типе задачи с выхода регистра 6 номера задания.

Сигналы с выходов элементов НЕ 14 группы поступают на первую группу информационных входов мультиплексора 1.9 и на информационные входы первого 23 блока элементов И. Данные сигналы образуют

унитарный распределенный код, который является номером процессора, опрашиваемого в данном такте. Код приоритета с выхода регистра 5 приоритета заданий поступает на. информационные входы второго блока 24 элементов И и на вторую группу информационных входов схемы 12 сравнения. Информация о номере задачи с выхода регистра 6 поступает на вход дешифратора 7.

Сигналы с выхода дешифратора 7 поступают на адресные входы блока 10 памяти номеров процессоров и блока 11 памяти приоритетов заданий. Происходит обращение к ячейкам памяти, соответствующим номеру задачи. Из блока 11 памяти приоритетов заданий считывается информация о. приоритете задачи данного типа, решаемой ранее, и передается на первую группу информационных входов схемы 12 сравнения. Если приоритет вновь поступившей задачи меньше приоритета задачи, решаемой ранее, то сигнал единичного уровня формируется на первом выходе схрмы 12 сравнения.

Если i-й процессор не приспособлен к решению задачи, указанного пользователем типа, то с приходом очередного тактового импульса с генератора 8 аналогичным образом проверяются возможности следующего из готовых к работе процессоров.

Если же t-й процессор приспособлен к решению задачи указанного пользователем типа (в его списке заданий присутствует соответствующий номер задачи), то на выходе одной из схем 17 сравнения группы формируется сигнал единичного уровня, который через первый элемент ИЛИ 18 поступает на первый управляющий вход мультиплексора 19 и на первые управляющие входы первого 23 и второго 24 блоков элементов И. С приходом сигнала единичного уровня на первый управляющий вход мультиплек- . сора 19 на его выход передается информация с первой группы информационных входов. На одном из выходов группы 20 сигнальных выходов устройства появляется сигнал единичного уровня.

Сигнал единичного уровня на соответствующем выходе группы 2р означает, что одноименный процессор избран для выполнения задания очередного пользовате- ля. Этот же сигнал поступает на управляющий вход одноименного блока 21 элементов И группы и на соответствующий вход второго элемента ИЛИ 25. С поступлением сигнала единичного уровня на управляющий вход соответствующего блока 21 элементов И группы через него на выходы 22 группы информационных выходов устройства передается информация с выхода регистра б номера задания номер пользователя (абонента) и номер (тип) задачи. Таким образом, готовый к работе процессор

получает сигнал (по выходу 20) на начало работы и уведомление (по выходам 22) о том, что он занимается для решения задачи соответствующего типа в интересах определенного пользователя (абонента).

0 Приступив к выполнению задачи процессор посылает сигнал на ответный вход группы 31 устройства, с помощью которого обнуляется соответствующий разряд регистра 4 готовности процессора (процессор

5 занят). Если окажется, что вновь поступившая задача обладает меньшим приоритетом, нежели задача такого же типа, но принятая на обслуживание ранее, то происходит следующее. На первых управляю0 щих входах первого 23 и второго 24 блоков элементов И сигнал единичного уровня с выхода первого элемента ИЛИ 18 (есть процессор для решения ), на втррых управляющих входах первого 23 и второго 24

5 блоков элементов И сигнал единичного уровня с первого выхода схемы 12 сравнения (вновь поступившая задача имеет меньший приоритет). Информация о номере процессора, выбранного для решения зада0 чи, с входа первого 23 блока элементов И передается для записи в блок 10 памяти номеров процессоров по адресу, соответствующему номеру (типу) задачи. Информация о приоритете задачи, принимаемой для ре5 ализации, с входа второго 24 блока элементов И передается для записи в блок 11 памяти приоритетов заданий.

Блоки 10 и 11 памяти имеют число ячеек, соответствующее количеству типов (номе0 ров) задач, которые могут поступить на обработку. По ходу работы в ячейках памяти, соответствующих определенному типу задачи, содержится следующая информация: в блоке 10 - номер процессора, который

5 выполняет задачу данного типа, имеющего наименьший приоритет из всех поступивших; в блоке 11 - значение приоритета этой задачи.

Сигнал единичного уровня с выхода вто0 рого элемента ИЛИ 25 поступает через элемент 30 задержки на входы установки в О регистров 5 и 6. Обнуление регистров должно быть задержано на время, достаточное для устойчивой записи информации в бло5 ки 10 и 11 памяти и выдачи на информационные 22 выходы устройства, но должно осуществиться до формирования очередного импульса на выходе генератора 8. После обнуления регистра б номера заданий на первом выходе дешифратора 7 сигнал

нулеврго уровня, который поступает на первый вход элемента И 9 и запрещает прохождение очередного тактового импульса с выхода генератора 8.

Очередной цикл функционирования ус- тройства начинается с поступления информации очередного задания: приоритета задания в регистр 5 и номера задания в регистр 6. На нулевое состояние регистра 6 предопределяет появление сигнала еди- ничного уровня на первом выходе дешифт ратора 7 - снятие блокировки прохождения импульсов генератора 8 через элемент И 9.

Может сложиться следующая ситуация. Ни один из готовых процессоров не приспо- соблен для решения задачи, указанной в очередном задании (ее способны решить другие, но они заняты). То, что все готовые процессоры опрошены, подтверждается сигналом единичного уровня на выходе эле- мента ИЛИ-НЕ 26. Опрос i-ro процессора сопровождается установлением i-ro триггера 15 в состояние 1, что блокирует возможность появления сигнала единичного уровня на выходе i-ro элемента НЕ 14. То, что ни один из процессоров не решает задач данного типа, подтверждается сигналом нулевого уровня на выходе первого элемента ИЛИ 18 - сигналом единичного уровня на выходе элемента НЕ 27. Сигнал единичного уровня с выхода элемента НЕ 27 поступает на первый вход второго элемента И 28. Сигнал единичного уровня с выхода элемента ИЛИ-НЕ 26 поступает на входы обнуления триггеров 15 группы и на второй вход второго элемента И 28. Обнуление триггеров 15 группы приводит к снятию (через время задержки элемента 29) блокировки повторного опроса процессоров, готовых к работе. По адресу, соответст- вующему типу задачи очередного задания (с выходов дешифратора 7), в блоке 10 памяти номеров процессоров считывается информация о номере процессора и передается на вторую группу информационных вы- ходов мультиплексора, а в блоке 11 памяти приоритетов заданий считывается информация о приоритете и передается на вторую группу информационных входов схемы 12 сравнения.

Таким образом, к моменту окончания безуспешного поиска свободного процессора известен процессор, заведомо приспособленный к решению задач соответствующего типа, решающий задачу, обладающую нам- меньшим приоритетом среди всех ранее поступавших задач данного типа, и приоритет решаемой задачи.

Возможзны два варианта. Если приоритет вновь поступившего задания меньше

или равен приоритету решаемой задачи, то для вновь поступившего задания процессор не назначается. Задание будет выполнено при освобождении одного из процессоров, приспособленных к решению задач заданного типа. Если приоритет вновь поступившего задания превышает приоритет решаемой задачи, то на втором выходе схемы 12 сравнения формируется сигнал единичного уровня. Этот сигнал поступает на третий вход второго элемента И 28. Сигнал единичного уровня с выхода второго элемента И 28 поступает на второй управляющий вход мультиплексора 19. По этому сигналу на сигнальные выходы устройства 20 передается информация с второй группы информационных входов мультиплексора 19. Сигнал единичного уровня будет на выходе, соответствующем процессору, который решает задачу заданного типа, имеющую наименьший приоритет среди всех ранее поступивших. Этот сигнал поступает также на управляющий вход соответствующего блока 21 элементов И группы и на соответствующий вход второго элемента ИЛИ 25. На соответствующую группу информационных выходов 22 устройства выдается (с выхода регистра 6) информация о задании, для исполнения которого назначен процессор. Регистры 5 и 6 обнуляются.

Таким образом, процессор, выполняющий задачу типа, совпадающего с типом задачи вновь поступившего задания, но имеющую меньший приоритет, получает новое задание (по выходам 22) и сигнал (по выходу 20), предписывающий приступить к исполнению вновь поступившего задания.

Прерывание ранее решаемой задачи и возврат к ее исполнению выполняются средствами, предусмотренными для процессоров данного типа.

Технические преимущества предлагаемого устройства относительно известного могут быть определены следующим образом.

Предположим, что любой из процессоров с вероятностью 0,5 может оказаться занятым, а если свободен, то с вероятностью 0,5 способен решать задачу заданного типа. Тогда при обращении к первому из опрашиваемых процессоров в известном устройстве с вероятностью 0,25 обнаруживают искомый процессор, а в предлагаемом устройстве - вероятность 0,5 (так как опрашиваются только готовые процессоры). Задают некоторую вероятность обнаружения процессора, способность решить задачу заданного типа, например, 0,9. В баовом устройстве для достижения указанноо показателя потребуется восемь тактов (опосить подряд восемь процессоров) в редлагаемом устройстве - четыре такта. аким образом, при прочих р авных услових быстродействие предлагаемого устройства в 2 раза выше, нежели известного.

Рассмотрим еще одну ситуацию, Пред- гЪоложим, что в системе существуют п процессоров, которые способны решать m ипов задач, причем один процессор спосоен решить k типов задач. Предлагается к рассмотрению ситуация - среди готовых процессоров нет процессора, способного решать задачу заданного типа. Естественно, что в некоторый момент времени часть процессоров будет занята решением ранее поступивших задач, Поскольку в рассматриваемой системе статистических исследований не проводится, то правомерно предположить, что готовыми окажутся -

процессоров. При равномерном распределении задач между процессорами для решения задач всех типов потребуется .-К

процессоров.

В известном устройстве для Определения способности готовых процессоров решить задачу заданного типа требуется п тактов. С помощью счетчика 42 осуществляется последовательный обход всех процессоров вне зависимости от состояния их готовности. Если даже предположить, что вновь поступившее задание обладает высшим приоритетом, то и в этом случае в

известном устройстве в среднем тактов

ii

для поиска среди занятых профессора способного решить задачу указанного типа.

Таким образом, в известном устройстве для однократного выполнения возложенных на него функций требуется (п. + --)

к

тактов. В предлагаемом устройстве в такой же ситуации для выполнения тех же функций

требуется ;г тактов.

В предлагаемом устройстве при определении способности готовых процессоров решить задачу заданного типа опрашиваются не все, а только действительно готовые процессоры. В процессе работы предлагаемого устройства в блоке 10 памяти номеров процессоров о ячейках, соответствующих типам задач, запоминаются номера процессоров, которые решают наименее приоритетную задачу соответствующего типа. При отсутствии готового процессора никаких дополнительных процедур (как в известном устройстве) не требуется. Номер процессора, которому следует адресовать поступившую задачу, оказывается заведомо известным (по адресу, соответствующему типу задачи),

Выигрыш V в быстродействии предлагаемого устройства относительно известного легко подсчитать:

0

п

V

m 2К

m

2(n+-Јr)

п 2

, m

Ј. | .

n-k

Таким образом, предлагаемое устройство превосходит известное по быстродействию более чем в 2 раза, При увеличении числа типов решаемых задач выигрыш в быстродействии возрастает.

Формула изобретения

Устройство для распределения заданий процессорам, содержащее регистр готовности процессоров, регистр приоритета

заданий, регистр номера заданий; дешифратор, блок памяти номеров процессоров, блок памяти приоритетов заданий, первый и второй блоки элементов И, блок памяти списков заданий процессоров, схему сравнения, группу блоков элементов И, элемент НЕ. генератор импульсов, два элемента ИЛИ. элемент задержки, два элемента И, причем группа информационных входов регистра-готовности процессоров соединена с группой сигнальных входов устройства, группа входов номера задания устройства соединена с информационными входами регистра номера задания, выходы которого соединены с

первыми входами блоков элементов И группы, группа входов приоритета задания устройства соединена с информационными входами регистра приоритета заданий, выходы которого соединены с

группой входов второго блока элементов И и с первой группой входов схемы сравнения, вторая группа входов которой соединена с информационным выходом блока памяти приоритетов заданий, выход генератора импульсов соединен с первым входом первого элемента И, выход Меньше схемы сравнения соединен с первыми входами первого и второго блоков элементов И, выход первого элемента ИЛИ через элемент НЕ соединен с первым входом второго элемента И, выход второго элемента ИЛИ соединен с входом элемента задержки, выходы блоков элементов И группы являются выходами заданий устройства, о т л ичающееся тем,что, с цельюувеличения быстродействия устройства, в него введены группа элементов И-НЕ. группа элементов НЕ, группа триггеров, группа элементов задержки, группа схем сравнения, мультиплексор, элемент ИЛИ-НЕ, причем первый вход 1-го элемента И-НЁ группы соединен с i-м (I 1,...,n, n - число процессоров) выходом регистра готовности процессоров, вторые входы всех элементов И-НЕ группы соединены с выходом первого элемента И и с входом управления схемы сравнения, третий вход f-ro элемента И-НЁ группы соединен с выходом 1-го элемента задержки группы, вход 1-го элемента НЕ группы соединен с выхо- дом 1-го элемента И-НЕ группы и с соответствующими входами всех последующих элементов И-НЕ группы, выход 1-го элемента НЕ группы соединен с входом установки в 1 1-го триггера группы, с i-м адресным входом блока памяти списков заданий процессоров, с соответствующим входом первой группы информационных входов мультиплексора, с соответствующим входом группы входов первого блока злемен- тов И и с соответствующим входом элемента ИЛИ-НЕ, выход которого соединен с входами установки в О триггеров группы и с вторым входом второго элемента И. выход первого элемента ИЛИ соедй- нен с первым управляющим входом мультиплексора и с вторыми входами пер вого и второго блоков элементов И, инверсный выход 1-го триггера группы соединен с входом 1-го элемента задержки группы, вхо-

ды первого элемента ИЛИ соединены с выходами соответствующих схем сравнения группы, первые и вторые группы входов которых соединены с группой выходов блока памяти списков заданий процессоров и с группой выходов регистра номера задания соответственно, третий вход второго элемента И соединен с выходом Больше схемы сравнения, выходы первого и второго блоков элементов И соединены с входами записи блока памяти номеров процессоров и блока памяти приоритетов заданий соответственно, первый выход дешифратора соединен с вторым входом первого элемента И, другие выходы дешифратора соединены с.соответствующими адресными входами блока памяти номеров npouec- еоров и блока памяти приоритетов заданий, выход второго элемента И соединен с вторым управляющим входом мультиплексора, вторая группа информационных входов которого соединена с информационными выходами блока памяти номеров процессоров, выходы мультиплексора являются сигнальными выходами устройства и соединены с вторыми входами соответствующих блоков элементов И группы и с входами вторрго элемента ИЛИ, выход элемента задержки соединен с входами установки в О регистра приоритета заданий и регистра номера заданий, входы установки в О разрядов регистра готовности процессоров соединены с соответствующими входами группы ответных входов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования очереди | 1986 |

|

SU1446626A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1524050A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1476466A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1441399A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1196866A1 |

| Микропрограммный диспетчер многопроцессорной вычислительной системы | 1987 |

|

SU1532926A1 |

| Устройство для распределения заявок по процессорам | 1982 |

|

SU1121671A1 |

| Устройство для сопряжения многопроцессорной вычислительной системы с внешними устройствами | 1984 |

|

SU1241245A2 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1453406A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении многопроцессорных вычислительных систем. Цель изобретения - увеличение быстродействия устройства. Цель достигается введением в устройство групп элементов И-НЕ, НЕ. триггеров, элементов задержки, схем сравнения, мультиплексора, элемента ИЛИ-НЕ. Устройство позволяет при поиске процессора для решения задачи определенного типа исключить необходимость начинать обход всегда с первого и обходить все (включая и занятые) процессоры, а также обеспечивает возможность по ходу работы (без дополнительных процедур) выявлять номер процессора, решающего наименее приоритетную задачу определенного типа. 1 ил.

| Авторское свидетельство СССР | |||

| № 913377 | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-02-07—Публикация

1990-01-29—Подача