Изобретение относится к вычислительной технике и может быть использовано D качестве аппаратного диспетчера программ, готовых к выполнению, для их распределения по процессорам многопроцессорной системы.

Цель - повышение быстродействия.

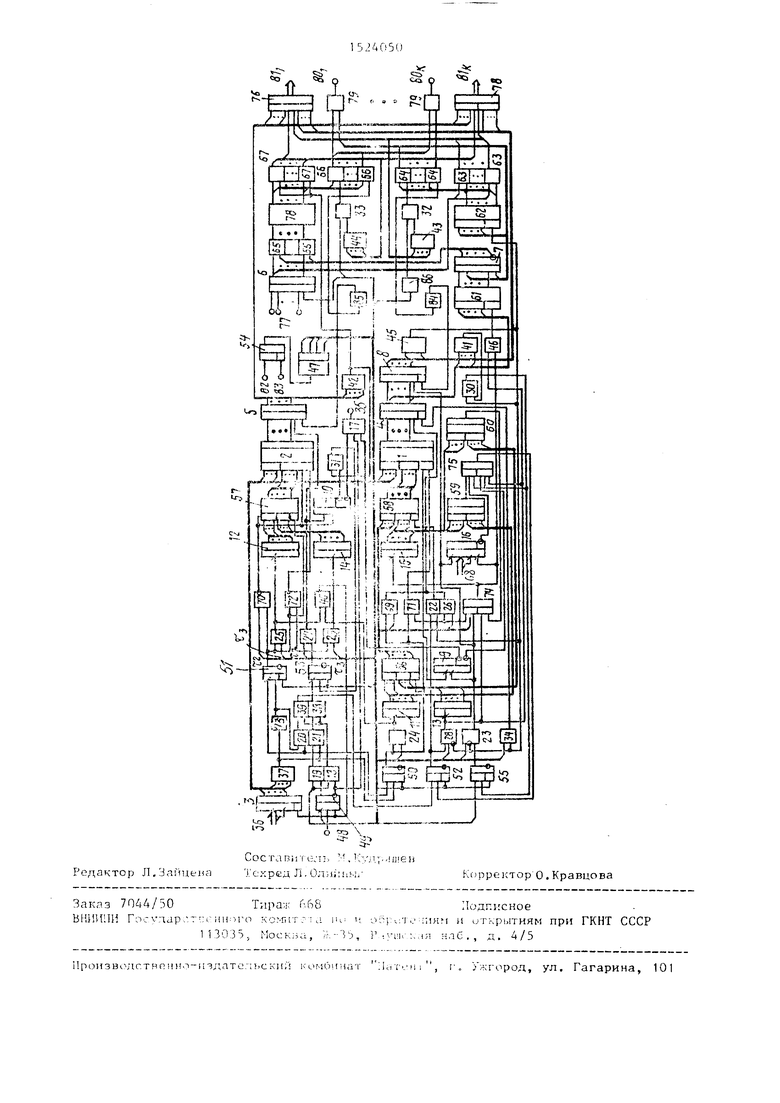

На чертеже приведена структурная схема устройства.

Устройство содержит блоки 1 и 2 памяти, регистры 3-8, счетчики 9-16, элементы И 17-34, сигнальный выход

35устройства, группу кодовых входов

36устройства, элементы ИЛИ 37-46, генератор 47 импульсов, сигнальный вход 48 устройства, триггеры 49-55, мультиплексоры 56-58, схемы 59-60

сравнения, дешифраторы 61 и 62, группы элементов И 63-67, группу кодовых входов 68 устройства, элементы И-НЕ 69-70, элементы ШШ-НЕ 7 и 72, эле-i мент НЕ 73, элементы И-ШП 74 и 75, группу коммутаторов 76, группу входов 77 готовности устройства, узел 78 приоритета, группу элементов 1ШИ 79, группу информационных выходов 80 устройства, группу кодовых выходов 81 устройства, вход 82 запуска устройства, вход 83 останова устройства элементы 84-86 задержки.

Устройство работает следующим образом.

В начальном состоянии устройства регистры 3-8 и счетч1 ки 9-16 имеют

СЛ N5

4 О СЛ

нулевое содержимое, триггеры 49-55 сброшены в нуль, блоки I и 2 памяти очищены (цепи перевода устройства в исходное состояние не показаны).При этом на выходе 35 устройства установлен единичньй сигнал, разрешаклиш подачу на устройство кодов запроса на распределение, а на выходах 80 группы и выходах 81 нулевые уровни сиг- палов.

Перед началом работы устройства через входы 68 в счетчик 16 заносится код глубины просмотра очереди заданий на конкретный процессор систе- мы.

Работа устройства начинается с приходом импульсного сигнала пуска на вход 82 устройства, по которому триггер 54 переводится в единичное сое- тояние и высоким уровнем сигнала на своем прямом выходе разрешает работу генератора 47 импульсов.

Работа устройства состоит в приеме от источника запросов кода запро- са на распределение задания, занесении запроса по признаку в одну из очередей и последующей выдачи по признаку на один из процессоров многопроцессорной системы. Параллельно с оаспределением заданий; идет процесс уп- реадающего просмотра на заданную глубину очереди заданий на конкретный процессор системь. В процессе просмот

дов разрядов регистра 3 поступают на одноименные входы элемента ШШ 37, К11тпрый анализирует признак посту- гшвшего запроса и совместно с зле- ментами НЕ 73, И 18-21, ИЛИ 38 и 39 вырабатывает условия для перехода устройства по следующему синхроимпульсу к вьпюлнению, соответствующей операции.

Если, например, поступает запрос с заданием,требутощим для своего исполнения конкретный процессор, тогда единичные уровни сигналов на прямом выходе Tpvirrepa 49 и выходе элемента ИЛИ 37 открывают для синхроимпульса элементы И 19 и И 21 и coздaFoт условия для перехода в единичное состояние триггера 50, соответствующего операции формирования очереди заданий на конкретньв процессор системь. Синхроимпульс поступает также через элемен l-inH 38 на синхровход триггер 53 и проверяет наличие условий для совмещения операций.

По отрицательному фронту синхроимпульса триггер 50 переводится в единичное состояние и открывает элементы И 24, И-НЕ 69, а также разрешает подачу на входы -т. льтиплексора 58 через мультиплексор 56 адреса верхней границы очереди заданий на конкретный процессор системы, отслеживаемого с помощью счетчика i1, Ну

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1987 |

|

SU1476466A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1441399A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1444770A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство микропрограммного управления | 1987 |

|

SU1539776A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2023295C1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1984 |

|

SU1180911A1 |

| Устройство для распределения заданий процессорам | 1990 |

|

SU1756889A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве аппаратного диспетчера программ, готовых к выполнению, для их распределения по процессорам многопроцессорной системы. Целью изобретения является повышение быстродействия. Устройство содержит шесть регистров, восемь счетчиков, восемнадцать элементов И, три мультиплексора, семь триггеров, десять элементов ИЛИ, две схемы сравнения, два дешифратора, пять групп элементов И, два элемента И-НЕ, три элемента ИЛМ-НЕ, два элемента И-ИЛИ, группу коммутаторов, узел приоритета, группу элементов ИЛИ, элемент задержки. В устройстве имеется возможность распределения конкретного задания на заданный процессор с параллельным просмотром очереди заданий и блокировкой распределения на этом процессоре заданий, допускающих исполнение на любом процессоре системы. 1 ил.

ра формируются сигналы блокировки рас- левой сигнал на адресном входе ьгульпределения на выбранные процессоры, заданий из очереди заданий на любой процессор системы.

Прием запроса состоит в фиксации в приемном регистре 3 кода запроса с последующим формированием условий для протекания операции занесения запроса в очередь. Условием для поступления нового запроса в устройство является

типлексора 58 разрешает прохождение на ад;;есный вход блока 1 памяти информации с входов. Единичный сигнал с прямого выхода триггера 50 лосту- 40 пает также через элемент ИПИ-НЕ 71 на вход разрешения доступа блока 1 памяти и создает условия для модификации очереди. Синхроимпульс проходит через элемент И-НЕ 69 и формируналичие высокого уровня сигнала на вы-дз «т команду Запись, по которой в

ходе 35 устройства, означающего, что приемный регистр 3 свободен и есть место в очередях запросов. Источник запросов через входы 36 устройства заносит в приег-шьй регистр 3 код запроса и выставляет на вход 48 устройства единичный сигнал, который по отрицательному фронту синхроимпульса запоминается в триггере 49. Перевод в единичное состояние триггера 49 вызывает появление на выходе 35 нулевого сигнала, получив который, источник запросов снимает единичный сигнал с входа 48 устройства. Сигналы с выхолевой сигнал на адресном входе ьгультиплексора 58 разрешает прохождение на ад;;есный вход блока 1 памяти информации с входов. Единичный сигнал с прямого выхода триггера 50 лосту- пает также через элемент ИПИ-НЕ 71 на вход разрешения доступа блока 1 памяти и создает условия для модификации очереди. Синхроимпульс проходит через элемент И-НЕ 69 и формиру0

5

блоке 1 памяти запоминается содержимое регистра 3, а в счетчике 9 корректируется заполнение очереди Следующий синхроимпульс проходит через элемент И 24 на счетный вход счетчика 11 и корректирует верхнюйз границу очереди. Этот сигнал через элемент ИЛИ 40 осуществляет сброс триггера 49 и очистку приемного регистра 3. По следующему синхроикшульсу срабатывается триггер 50 и анализируется поступление новых запросов.

Прием и занесение запроса -в очередь заданий на любой процессор сиетемы осуществляется аналогично, с той лишь разницей, что в блоке 2 памяти запоминается содержимое других разрядов регистра 3,

По мере накопления заданий в блок 1 памяти в работу включается механизм упреждающего просмотра очереди. Суть которого заключается в том, что очередь просматривается на заданную глубину и формируются сигналы блокировки распределения на процессоры, требуемые выбранным заданиям, заданий из очереди заданий на любой процессор системы. Для запуска операции просмотра необходимо выполнение следующих условий: глубина просмотра не достигнута (на сигнальном выходе счетчика 16 един}гчный сигнал) ; текущая граница просг-ютра не достигла верхней границы очереди (нулевой сигнал на выходе схемы 59 сравнения); текущее задание ожидает в регистре 8 освобождение требуемого процессора (нулевой сигнал на выходе элемента И 30).

В результате этого на выходе элемента И-ИЛИ 75 формируется единттчньш сигнал, которьй поступает на информационный вход триггера 52 и по отрицательному фронту синхроимпульса переводит его в единичное состояние (если на предыдущем такте новых згоданий не поступило или поступило задание на любой процессор системы), соответствующее состоянию выборки задания из очереди. На выходе элемента И 22 формируется единичньп сигнал, которьп поступает на адресный вход мл,шьтиплек сора 58 и разрешает выдачу на адресный вход блока 1 памяти текутдего адреса просмотра очереди, формируемого в счетчике 15. На выходе элемента ИЛИ-НЕ 71 формируется нулевой сигнал, который поступает на вход разрешения доступа блока 1 памяти и разрешает работу с очередью заданий. По следующему синхроимпульсу на выходе элемента И 26 формируется единичньш сигнал, по которому запрос с выходов блока 1 памяти заносится в регистр 4 По следующему синхроимпульсу на выходе элемента И-ИЛИ 74 формируется единичный сигнал, который поступает на счетный вход счетчика 15 и корректирует текущий адрес просмотра очереди, а также поступает через элемент ИЛИ 46 на управляющей вход дешифра-

тора 61. По этому сигналу на выходе дешифратора 62, соответствующем уни- TapHo fy коду номера процессора, требуемого данному заданию, формируется единичный сигнал, который поступает на одноименный единичный вход разряда регистра 7 и устанавливает его в 1. Сигнал с инверсного выхода данO ного разряда поступает на вход одноименного элемента И 65 группы и блокирует тем самым участие данного процессора в распределении за-даний из очереди задан1ш на любой процес5 сор системы. Сигнал с выхода элемента И-ИЛИ 74 поступает также на вычи- таюпнй вход счетчика I6 и корректирует достигнутую глубину просмотра очереди. По следующему синхроимпульсу

0 на выходе элемента И 34 фор№1руется единичньм сигнал, который поступает на вход сброса регистра 4 и очищает его, после чего в устройстве формируются условия для выполнения следую5 щей onepamiH.

Для запуска операции выдачи зада- 1ГИЯ из очереди необходимо выполнение следующих условий: очередь не пуста (едциичцья сигнал на втором сигналь0 ном выходе счетчик 9 (0)); свободен регистр выдачи задания (нулевой сигнал на выходе элемента ИЛИ 45 (42)).

При этом, выдача задания из очере ди задания на любой процессор завершается за один такт, а для выдачи задания из очереди заданий на конкретный процессор требуется два такта работы устройства.

0 На первом такте осуществляется выборка задания в регистр 4, а на втором такте содержимое регистра 4 перезаписывается в регистр 8. При выполнении указанных условий на выхо5 де элемента И-ИЛИ 75 (И 31) формируется единичный сигнал, которьй поступает на информациошцд вход триггера 52 (53) и по отрицательному фронту синхроимпульса переводит его

0 в единичное состояние (если на предыдущем такте в устройство не поступило новых запросов). Нулевые сигналы на адресных входах ьгульти- плексоров 58 (57) и 56 разрешают по5 дачу на адресный вход блока 1 (2) памяти адреса нижней границы очереди, формируемой в счетчике 13 (14). На выходе элемента ИЛИ-НЕ 71 (72)

формируется нулевой сигнал, которьш поступает на вход разрешения доступа блока 1 (2) памяти и разрешает работу с очередью заданий. По следующему синхроимпульсу на выходе элемента И 26 (27) формируется сигнал, по которому запрос с выходов блока 1 (2) памяти заносится в регистр 4 (5). Кроме того, для очереди заданий на любой процессор системы этот сигнал корректирует заполнение очереди. По следующему синхроимпульсу на выходе элемента И 28 (29) формируется единичный сигнал, который корректирует адрес границы очереди в счетчике 13 (14). По следующему синхроимпульсу триггер 52 (53) сбрасывается в исходное нулевое состояние. Для очереди заданий на любой процессор операция выдачи задания из очереди на этом завершается и задание в регистре 3 ожидает распределения ему свободного процессора. Для очереди заданий ча конкретный процессор на следующем такте осуществляется второй этап операции выдачи задания, условиями для которого являются наличие задания Б регистре 4 (единичиьй сигнал па иы- ходе элемента Ш1И А1); регистр 8 г.во боден (нулевой сигнал на выходе мента ИЛИ 45).

В результате этого на выходе элемента И 30 формируется единичньй сигнал, который поступает на информаи,и- онный вход триггера 55 и по отрицательному фронту синхроимпульса переводит его в единичное состояние (если на предыдущем такте не поступил новый запрос или поступил запрос с заданием на любой процессор). По следующему синхроимпульсу на выходе элемента И 23 формируется единичный сигнал, который поступает на синхровход регистра 8 и заносит в него информа- ЦИК) с выхода регистра 4, Этот сигнал поступает также на счетный вход счетчика 16 и вычитающий вход счетчика 9, корректируя тем самым глубину просмотра очереди и ее заполнение. Занесение в регистр 8 вызывает появление единичного сигнала.на выходе элемента ИЛИ 45, который поступает на вход элемента И 34 и отпирает«его По следующему синхроимпульсу на выхо де элемента И 34 формируется единичный сигнал, который поступает на вхо сброса регистра 4 и очищает его, после чего в устройстве формируются ус

ловия дли ныполнения следующей операции .

запуска операции распределения задани; на процессоры необходимо выполнение следующих условий: задание занесено в регистр выдачи 8 (5) (единичньй сигнал на выходе элемента ИЛИ 45 (42)); требуемый процессор свободен (единичный сигнал на выходе соответствующего элемента И 63).

В результате этого формируется единичный сигнал на вь ходе элемента ИЛИ 49 (50). При этом единичный сигнал н выходе соответствующего элемента И 63 (67) группы pa3peii aei выдачу на требуемый процессор через од}Юименный коммутатор /6 группы кода номера задания с выхода регистра 8 (5), По синхроимпульсу на выходе соответствующего элемента И 64 (66) группы формируется едШ1ичньш сигнал., который через одноименный элемент ИШ1 79 группы проходит на сигнальный выход ВО и стробирует прием процессором кода номера задания с выхода 81 группы. Устройство допускает выдачу на одном такте заданий: из обеих очередей, однако выдача задания и т очереди заданий на конкретньм процессор осуществляется задержанным (на элементе задержки 86) синхро1 мнульсом с целью устранить возможные колебания уровней сигнал 5в на выходе узла приоритета, вызванные сСросом разряда регистра 7. После выдачи задания на процессор регистр 8 (5) очищается задержанным на элементе 84 (85) сигналом с выхода элемента И 32 (33), после чего Е устройстве формируются условия для перехода к выполнению следующей операции.

В работе устройства соблюдается следующая приоритетность операций: операция приема запроса и постановки его в очередь; операция выборки запроса из очереди и передача его на распределение; операция упреждающего просмотра очереди заданий на кан-- кретный процессор системы.

Однако организация очередей позволяет совмещать в пределах одного такта такие операции, как, например, занесение запроса в очередь заданий на любой процессор cиcтe a)I и упреждающий просмотр очереди заданий па конкретный процессор системы или занесение запроса в очередь, заданий на конкретньй процессор cиcтe ы и

выдачу текущего залання из этой очереди, ожидавшего в регистре 8 освобождения требуемого процессора.

В дальнейшем устройство работает аналогично описанному.

Формула изобретения

Устройство для распределения заданий процессорам, содержащее первый и второй блоки памяти, первый и второй регистры, nepBbrfi и второй счетчики, первьй дешифратор, первый элемент И, генератор тактовых импульсов, 15 выход четвертого элемента И соединен

с вторым входом третьего элемента КЧИ, выход которого соединен с синх- ровходок четвертого триггера, выход пятого элемента И соединен с вторым

20 вхс дом второго элемента ИЛИ, выход которого соединен с сннхровходом пятого триггера, группа выходов третьего счетчика соединена с первой группоП информационных входов перво25 го мультиплексора и с первой группой входов первой схемы сравнения, группа выходов четвертого счётчика соединена с первой группой информационных входов второго мультиплексора,

30 группа пыходор которого соединена с адресными входами второго блока памяти, группа выходов пятого счетчика соединена с второй группой информа- LUiOHfa.ix входов первого мультиплек35 сора и с первой группой входов второй схемы срлвнения, группа выходов шестого счетчика соединена с второй группой информационных входов второго м льтиплексора, группа выходов перпервый мультиплексор, первый и второй элементы задержки, нервьй и второй элементы ИЛИ, причем информационные выходы первого блока памяти соединены с информационными входаьш первого регистра, выход переноса первого счетчика соединен с первым входом -первого элемента И, отличающееся тем, что, с целью повьшения быстродействия, оно содержит третий, четвертый, пятый и шестой регистры, третий, четвертьш и пятьй, шестой, седьмой и восьмой счетчики, с второго по восемнадцатый элементы И, с третьего по десятьм элементы ИЛИ, первый и второй элементы И-НЕ, первый :i второй элементы l-LTH-HE, с первого по седьмой триггеры, узел приоритета, первую и вторую cxeNuj сравнения , пер- BbD i и второй элементы Я-ИЛИ, второй и третий мультиплексоры, элемент НЕ, ггретий элемент задержки, с первого по пятую группы элементов li, группу элементов ИЛИ, второй дешифратор и

группу коммутаторов, причем выход пе- 40 вого мультиплексора соединена с перренос.а второго счетчика соединен с вторым входом первого элемента И, вьгход которого является сигнальным выходом устройства, первая группа кодовых входов устройства соединена с группой информационных входов синхро- входом второго регистра, первая группа выходов которого соединена с входами данных первого блока памяти.

вторая и третья группы выходов перво- ,„ первого дешифратора соединены с едиго регистра соединены соответственно с входами первого элемента ИЛИ и с входами данных второго блока памяти, выходы которого соединены с информационными входами третьего регистра, первый выход генератора тактовых импульсов соединен с первыми входами второго и третьего элементов И и синхровходом четвертого регистра.

55

ничными входами разрядов пятого регистра, выходы второго дешифратора соединены с первыми входами элементов И первой и второй групп, выход шестого элемента И соединен с адресным входом третьего fyльтиплeкcopa, выход седьмого элемента И соединен с вычитающим входом первого счетчика, с сум шрук1шим входом восьмого

сигнальный вход устройства соединен . с информационным входом первого триггера, инверсггый выход которого соединен с третьим входом первого и вторым входом второго элементов И, выход второго элемента И соединен с первыми входами второго и третьего элементов ИЛИ, прямой выход первого триггера соединен с вторым входом третьего элемента И, выход которого соединен с первыми входами четвертого и пятого элементов И и с синхро- входами второго и третьего триггеров.

5

вой группой информационных входов третьего мультиплексора, группа выходов которого соединена с адресны- ми рходами первого блока памяти, группа вмходор седьмого счетчика сое- динет5а с второй группой информационных входов третьего мультиплексора и с вторыми группами входов первой и второй схем сравнения, выходы

5

ничными входами разрядов пятого регистра, выходы второго дешифратора соединены с первыми входами элементов И первой и второй групп, выход шестого элемента И соединен с адресным входом третьего fyльтиплeкcopa, выход седьмого элемента И соединен с вычитающим входом первого счетчика, с сум шрук1шим входом восьмого

счетчика и синхровходом шестого регистра, прямой выход второго триггер соединен с адресным входом первого мультиплексора и с первыми входами восьмого элемента И, первого элемента И-НЕ и первого элемента ИЛИ-НЕ, выход восьмого элемента И соединен со счетным входом третьего счетчика и первым входом четвертого элемента ИЛИ, выход первого элемента И-НЕ соединен с суммирующим входом первого счетчика и входом разрешения записи первого блока памяти, выход первого элемента ШШ-НЕ соединен с входом разрешения доступа первого блока памяти, прямой выход третьего триггера соединен с адресным входом второго мультиплексора и с первыми входаг-ш девятого элемента И, второго элемента И-НЕ и второго элемента tUTM-HR, выход девятого элемента И соединен со счетным входом четвертого счетчика и вторым входом четвертого элемента ИЛИ, выход которого соединен с нулевым в:{одом первого триггера и входом сброса второго регистра, выход второго элемента И-ЧЕ соеду1нен с oyMMipyiouutM входом второго счетчика и входом разрешения, записи второго блока памяти, выход второго элемента ИПИ-НЕ соединен с входом разрешения доступа BTOpoi o блока памяти, выход первого элемента ИЛИ соединен с )зторы11 ьходом пятого элемента И, с ипфпрмациоин1л 1 сходом второго триггера и с входом элемента НЕ, выход которого соединен с вторым входом четвертого элемента И и информационным входом третьего триггера, второй выход генератора тактовых импульсов соединен с первыми входами седьмого, десятого и одиннадцатого злемо.атов И и с вторыми входами первого и второго элементов И--НЕ, трети выход генератора тактовых импульсов соединен с BTOIJUMH гходами восьмого и девятого элементов И, с первыми входами двенадцатого и гринадц атого элементоп Ии с первым входом первого :элсмента И-ИЛИ,первая группа выходов первого регистра соедклен.а с информационными входаш шестого регистра, вторая группа выходов второго регистра соединена с входами пятого элемента ИШ и с входами первого дешифратора выходы третьего регистра соединены с входами шестого элемента ИЛИ и пе вымIi группами информационных входов

5

0

5

0

5

0

5

0

5

коммутаторов группы, группа входов готовности устройства соединена с группой информационных входов четвертого регистра, выходы которого соединены с вторыми входами соответствующих элементов И первой группы и первыми входами соответствую1цих элементов И третьей группы, выходы которых соединены с входами узла приоритета, выходы узла приоритета соединены с первыми входами соответствующих элементов И четвертой и пятой групп, прямой выход четвертого триггера соединен с первым входом шестого элемента И, с вторыми входами десятого элемента И, первого элемента ИЛИ-НЕ, первого элемента И-ИЛИ и с вторым прямым входом двеиадцатого элемента И, прямой выход пятого триггера соединен с вторыми входами второго элемента ИЛИ-НЕ, одиннадцатого и трин- надцатого элементов И, выход десятого элемента И соединен с синхровходом первого регистра, выход одиннадцатого элемента И соединен с синхровходом третьего регистра и вычитающим входом второго счетчика, выходы элементов И первой группы соединены с первыми управляющими входами соответ- ствутощих коммутаторов группы и с соответствующими входами седьмого элемента ИЛИ, выходы элементов И второй группы соединены с нулевыми входами соответствующих разрядов пятого регистра и первыми входами соответствующих элементов ИЛИ группы, выходы элементов И четвертой группы соединены соответственно с вторыми входами элементов ИЛИ группы, выходы которых являются группой информационных выходов устройства, выходы элементов И пятой группы соединены с соответствующими входами восьмого элемента ИЛИ и вторыми управляющими входами соответствующих коммутаторов группы, выходы которых являются группами кодовых выходов устройства, первая группа выходов шестого регистра соединена с входами второго дешифратора и входами девятого элемента ИЛИ, вторая группа выходов шестого регистра соединена с вторыми группами информационных входов коммутаторов группы, выход двенадцатого элемента И соединен со счетным входом пятого счетчика, с третьим входом первого элемента И-ИЛИ и с первым входом десятого элемента ИЛИ, гаыход тринад

цатого элемента И соединен со счетным входом шестого счетчика, вторая Группа кодовых входов устройства сое динена с информационными входами и синхровходом восьмого счетчика, выход равенства нулю которого соединен с первым прямым входом второго элемента И-ИЛИ, выход равенства нулю первого счетчика соединен с вторым прямым входом второго элемента И-ИЛИ вход запуска устройства соединен с единичньш входом шестого триггера, вход останова устройства соединен с нулевым входом шестого триггера, пря мой выход которого соединен с управляющим входом генератора тактовых импульсов, первый выход которого соединен с синхровходом седьмого триггера, прямой выход которого соединен с вторым прямым входом седьмого элемента И, выход пятого элемента ИЛИ соединен с прямым входом четырнадцатого элемента И, выход которого соединен с информационным входом седьмого триггера и с первым и вторым инверсными входами второго элемента И-ИЛИ, выход шестого элемента ИЛИ соединен с инверсным входом пятнадцатого элемента И и с вторыми входами элементов И пятой группы, выход равенства нулю второго счетчика соединен с прямым входом пятнадцатого элемента И, выход которого соединен с информационным входом пятого триггера, выход седьмого элемента ИЛИ соединен с первым входом шестнадцатого элемента И, выход котброго соединен с вторыми входами элементов И второй группы, и через первый элемент за-

0

0

5 0

держки с входом сброса шестого регистра, выход восьмого элемента ИЛИ соединен с первым входом семнадцатого элемента И, выход которого соединен с вторыми входами элементов И четвертой группы и через второй элемент задержки с входом сброса третьего регистра, выход девятого элемента-, ИЛИ соединен с инверсными входами седьмого, двенадцатого и четьфнадца- того элементов И, с вторым входом шестого элемента И с первым входом восемнадцатого элемента И, с четвертым входом первого и третьим входом второго элементов ИЛИ-И и с управляющим входом второго дешифратора, выход первой схемы сравнения соединен с четвертым инверсным входом второго элемента И-ИЛИ, выход которого соединен с информационным входом четвертого триггера, выход второй схемы сравнения соединен с пятым входом первого элемента И-ИЛИ, выход которого соединен со счетным входом седьмого счетчика, с вычитающим входом росьмого счетчика и с вторым входом десятого элемента ИЛИ, выход которого соединен с управляющим входом первого дешифратора, четвертый выход генератора тактовых импульсов соединен с сиихровыходом первого триггера, с нулевыми входами второго, третьего, четвертого, пятого и седьмого триг- 5 геров, с вторыми входами семнадцатого и восемнадцатого элементов И и через третий элемент задержки с вторым входом шестнадцатого элемента И, выход восемнадцатого элемента И соединен с входом сброса первого регистра.

5

0

«о

S--:

1-01 г

О .

о W3

;j

ЗО

| Устройство для распределения заданий процессорам | 1985 |

|

SU1290320A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-23—Публикация

1988-03-02—Подача