управления, блок 21 оперативной памяти, счетчик 22, второй блок 23 сравнения, формирователь 24 задержек. Устройство позволяет наиболее полно использовать канал связи. Оно работоспособно даже в том случае, когда уровень загрузки моноканала превышает критические значения, т.е. этим обеспечивается полная загрузка оборудования и программ независимо от ритма работы вычислительных центров. 1 з.п. ф-лы, 6 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи информации | 1988 |

|

SU1509970A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1983 |

|

SU1142825A1 |

| Устройство для поиска информации | 1989 |

|

SU1675906A1 |

| Устройство для измерения временных параметров станции | 1987 |

|

SU1429119A1 |

| Устройство для передачи информации в кольцевом канале связи | 1982 |

|

SU1043715A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Устройство для синтаксического контроля | 1987 |

|

SU1474679A1 |

| Процессор | 1981 |

|

SU962964A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Стоковое запоминающее устройство | 1988 |

|

SU1520597A1 |

Изобретение относится к устройствам, применяемым в системах передачи данных, например в локальных вычислительных сетях. Цель изобретения - повышение информативности устройства. Устройство содержит приемник 1, переключатель 2 канала, передатчик 3, второй элемент И 4. первый триггер 5, распределитель 6 импульсов, преобразователь 7 параллельного кода в последовательный, первый элемент И 8, накопитель 9 информации, второй 10 и третий 11 триггеры, третий элемент И 12, элемент 13 задержки, пятый элемент И 14, селектор 15 адреса, четвертый элементИ16, источник 17 информации, блок Т|В стековой .памяти, первый блок 19 сравнения, блок 20

Изобретение относится к устройствам, применяемым в области систем передачи информации, например в локальных вычислительных сетях.

Известно устройство для передачи информации в кольцевом канале связи, содержащее приемник,выход которого соединен с информационным входом переключателя, выход которого соединен с первым входом передатчика, распределитель импульсов, первый выход которого соединен с первым входом преобразователя параллельного кода в последовательный и входом первого триггера/выход которого соединен с первым входом первого элемента И. второй выход распределителя импульсов соединен с вторым входом преобразователя параллельного кода в последовательный, третий вход которого соединен с источником информации, выход-с вторым входом первого элемента И, третий выход распределителя импульсов соединен с третьим входом первого элемента И, выход которого соединен с вторым входом передатчика, причем выход первого триггера и третий выход распределителя импульсов соединены соответственно с первыми и вторыми входами второго и третьего элементов И, третий вход второго элемента И соединен с выходом приёмника, выход-с первыми; входами второго и третьего триггеров и входом накопителя информации, выход которого соединен непосредственно с вторым входом второго триггера и через последовательно соединенные счетчик, дешифратор и группу элементов задержки с вторым входом третьего триггера, выход которого соединен с четвертым входом первого элемента И, выход второго триггера - с первым управляющим входом переключателя и третьим входом третьего элемента И, выход которого через элемент задержки соединен с вторым управляющим входом переключателя..

Недостатком данного устройства является то, что с возрастанием нагрузки на систему передачи данных (локальную вычислительную сеть) интенсивность передач от отдельных устройств системы (сети) резко падает.

Наиболее близким по технической сущности к изобретению является устройство для передачи информации, содержащее распределитель импульсов, первый выход

которого соединен с первым входом преобразователя параллельного кода в последовательный и с входом первого триггера, выход которого соединен с первыми входами соответственно первого, второго и

третьего элементов И, второй выход распределителя импульсов - с вторым входом преобразователя параллельного кода в последовательный, третий вход которого соединен с источником информации, третий

выход распределителя импульсов -с вторыми входами соответственно первого, второго и третьего элементов И, приемник, вход которого является входом, устройства, выход приемника соединен с

селектором адреса, третьим входом второго элемента И и первыми входами блока управления в режиме повышенной нагрузки каналам переключателя каналов, выход которого соединен с первым входом передатчика, выход которого является выходом устройства, выход преобразователя параллельного кода в последовательный соединен с третьим входом первого элемента И, выход которого подключен к второму входу передатчика и четвертому входу блока управления в режиме повышенной нагрузки канала, первый выход которого подключен к первому входу четвертого элемента И, второй вход которого подключен к выходу селектора адреса, выход четвертого элемента И - к первому входу блока стековой памяти, другой вход которого подключен к второму выходу блока управления в режиме повышенной нагрузки канала, второй, третий и пятый входы которого подключены соответственно К выходу блока сравнения, первому выходу блока стековой памятник выходу блока задержек и второму входу третьего триггера, выход которого подключен к четвертому входу первого элемента И, пятый вход которого подключен к третьему выходу блока управления в режиме повышенной нагрузки канала и первым входам шестого и пятого элементов И, выход пятого

элемента подключен к второму входу переключателя каналов, третий вход которого подключен к выходу второго триггера и третьему входу третьего элемента И, выход которого через элемент задержки подключен к другому входу пятого элемента И, причем выход второго элемента И соединен с первыми входами соответственно второго и третьего триггеров и входом накопителя информации, выход которого соединен с вторым входом второго триггера и с входом счетчика, выход которого Соединен с входом дешифратора, выход которого подключен к второму входу шестого элемента И. выход которого подключен к первому входу блока задержек другому входу которого подключен четвертый выход блока управления в режиме повышенной нагрузки канала.

Недостатком известного устройства является то, что в режиме повышенной нагрузки на локальную сеть может возникнуть ситуация, когда станции после предельного количества неудавшихся попыток передачи информации сняли свои решения передать данные, хотя в стеках устройств их адреса записаны и должны анализироваться после окончательного заполнения стека. В этом случае целесообразно заранее учесть этот факт, так как устройство будет ожидать передачу от этих станций (хотя заведомо их передач не будет) какое-то значение времени задержки г. которое выбирается случайным образом и может иметь наибольшее значение из набора значений в блоке задержек, тем самым снижается информативность устройства. Кроме тога, известное и предлагаемое устройства обладают одним и тем же недостатком: если две и более станций получат столкновения в начале работы сети или в процессе работы (в случае, если у станций до этого момента было одинаковое количество столкновений), то станции одновременно предпримут попытку повторной передачи информации, так как получат одинаковую задержку, и снова столкнутся, затем опять получат одинаковую задержку, и снова столкнутся, и т.д., пока не снимут свои передачи по достижению предельного количества попыток передачи информации, установленного согласно протоколам передачи информации. Организация задержек на повторные передачи происходит линейно, т.е. при первом столкновении Т, при втором 2 г, при третьем Зги т.д. до 16 г. В этом случае случайный выбор задержек в этих пределах был бы благоприятным для работы сети.

Цель изобретения - повышение информативности устройства.

Указанная цель достигается тем/что в устройство для передачи информации, содержащее распределитель импульсов, первый выход которого соединен с первым 5 входом преобразователя параллельного кода в последовательный и с входом первого триггера, выход которого соединен с первыми входами соответственно первого, второго и третьего элементов Л, второй выход

0 распределителя импульсов соединен с вторым входом преобразователя параллельного кода в последовательный, третий вход которого соединен с источником информации, третий выход распределителя импуль5 сов - с вторыми входами соответственно первого, второго и третьего элементов И. приемник, вход которого является входом устройства, выход приемника соединен с селектором адреса, третьим входом второ0 го элемента И и первыми входами блока управления в режиме повышенной нагрузки канала и переключателя каналов, выход которого соединен с первым входом передатчика, выход которого является выходом

5 устройства, выход преобразователя параллельного кода в последовательный соединен с третьим входом первого элемента И, выход которого подключён к второму входу передатчика и четвертому входу блока

0 управления в режиме повышенной нагрузки канала, первый выход которого подключен к первому входу четвертого элемента И, второй вход которого подключен к выходу селектора адреса, выход четвертого

5 элемента И - к первому входу блока стековой памяти, другой вход которого подклюУ чен к второму выходу блока управления в режиме повышенной нагрузки канала, второй, третий и пятый входы которого под0 ключены соответственно к выходу первой схемы сравнения, к первому выходу блока стековой памяти, второму входу третьего триггера, выход которого подключён к пятому входу первого элемента И, четвертый

5 вход которого подключен к третьему выходу блока управления в режиме повышенной нагрузки канала и первому входу пятого элемента И, выход которого подключен к второму входу переключателя каналов, третий

0 вход которого подключен к выходу второго триггера и третьему входу третьего элемента И, выход которого через элемент задержки подключен к другому входу пятого элемента И, причем выход второго элемента

5 И подключен к первым входам второго, третьего триггеров и входу накопителя информации, выход которого подключен к второму входу второго триггера, а второй выход блока стековой памяти подключен к первому входу первой схемы срэпнения.

введены формирователь задержек, вторая схема сравнения, счетчик попыток передачи, блок памяти, входы которого подключены соответственно к восьмому выходу блока управления в режиме повышенной нагрузки канала, третьему выходу блока стековой памяти, выход счетчика попыток передачи, первый вход которого подключен к выходу блока памяти и первому входу второй схемы сравнения; выход которой подключен к шестому входу блока управления в режиме повышенной нагрузки канала, четвертый - седьмой выходы которого подключены соответственно к вторым входам формирователя задержек, второй схемы сравнения, счетчика попыток передачи, первой схемы сравнения, третий вход которой подключен к выходу селектора адреса и второму входу четвертого элемента И, а первый вход формирователя задержек подключен к выходу накопителя информации и второму входу второго триггера, выход формирователя задержек.- к второму входу третьего триггера и пятому входу блока управления в режиме повышенной нагрузки канала.

Существенные отличия предлагаемого устройства от известного заключаются в том, что при возникновении ситуации, когда станции после предельного количества неудавшихся попыток сняли свое решение передать данные,в блоке стековой памяти устройств их адреса записаны и должны быть проанализированы после полного заполнения стека. Учитывая тот факт, что устройство будет ожидать передачуот станций, снявших свою передачу, какое-то значение т, которое выбирается случайным образом и может иметь наибольшее значение, адреса этих станций выбрасываются из стека и устройство переходит к обработке следующего адреса в стеке. Однако при анализе количества попыток передачи каждой станции .можно заранее исключить станции, достигшие предельного количества попыток передачи, при этом время задержки на повторную передачу сокращается, тем самым повышается информативность устройства для передачи информации.

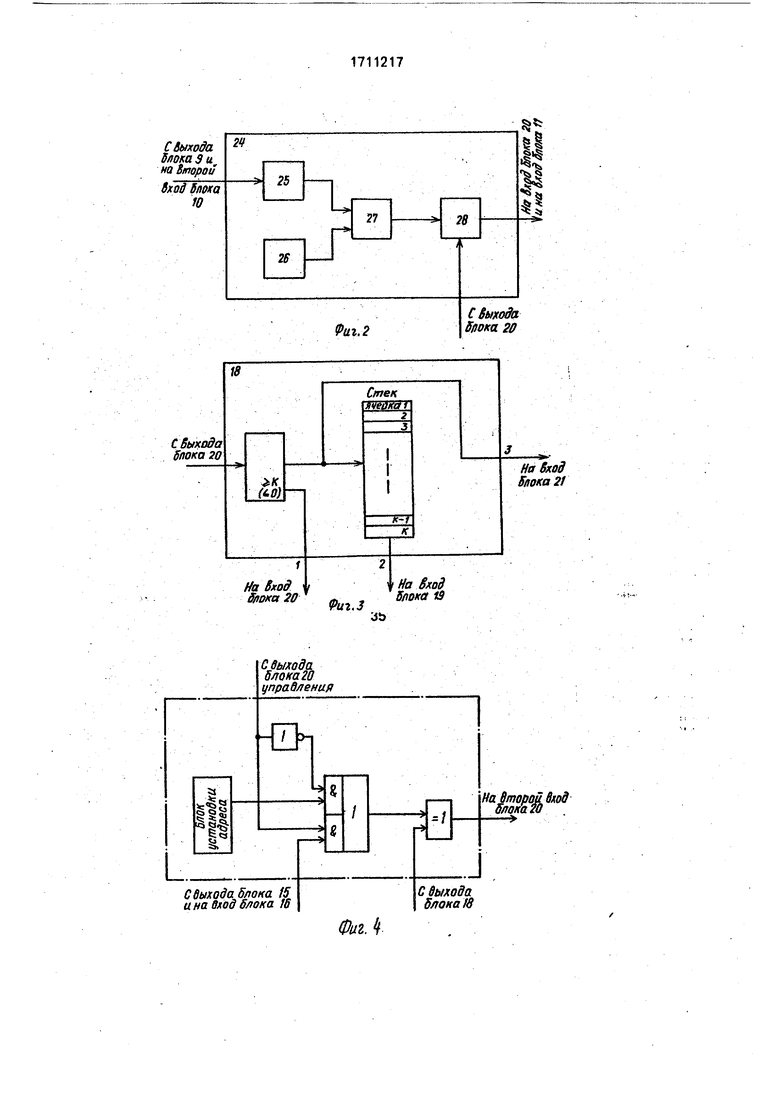

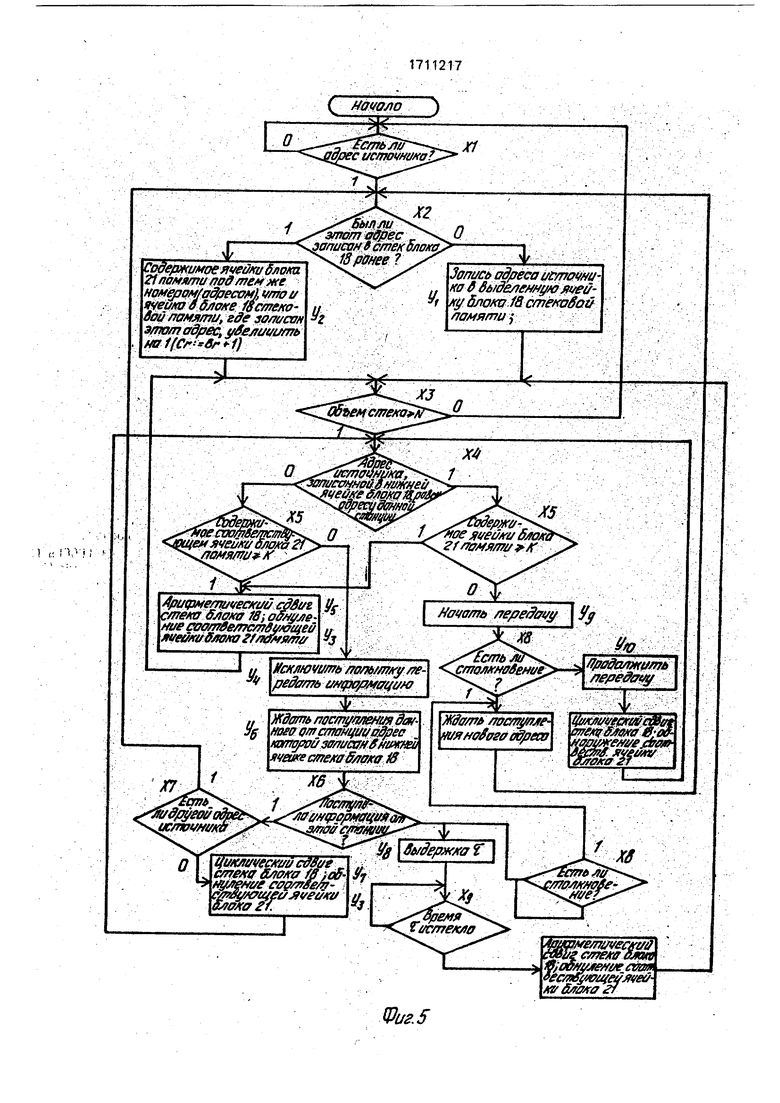

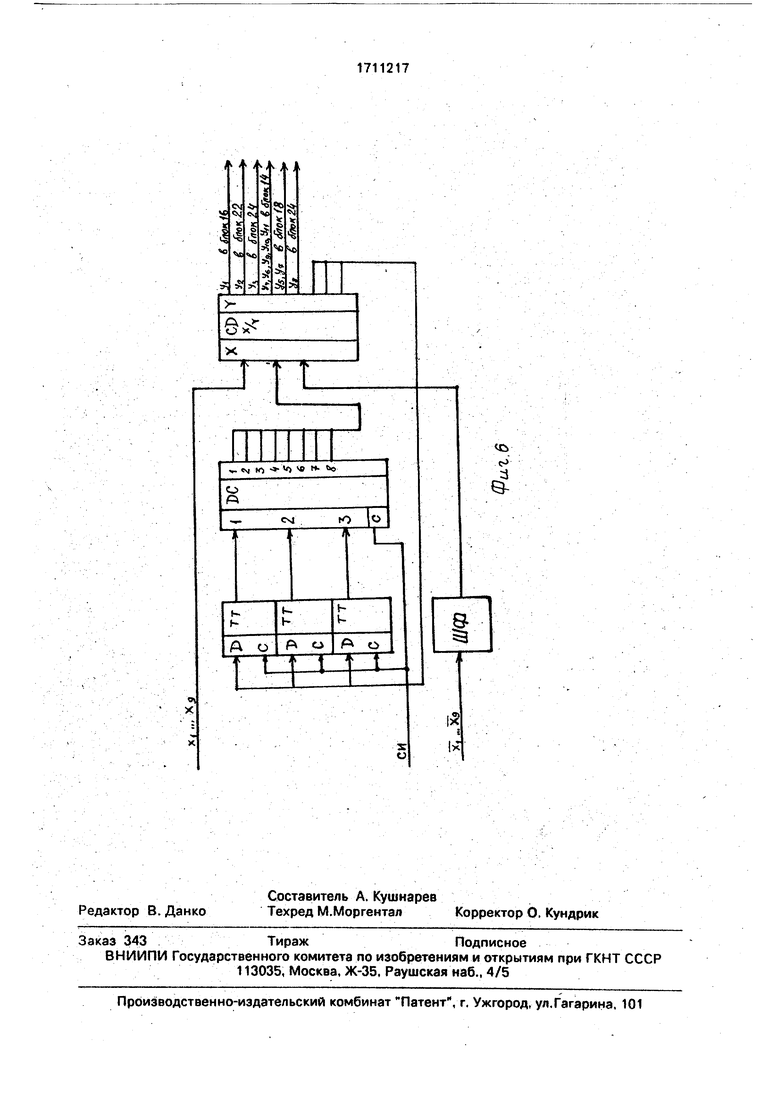

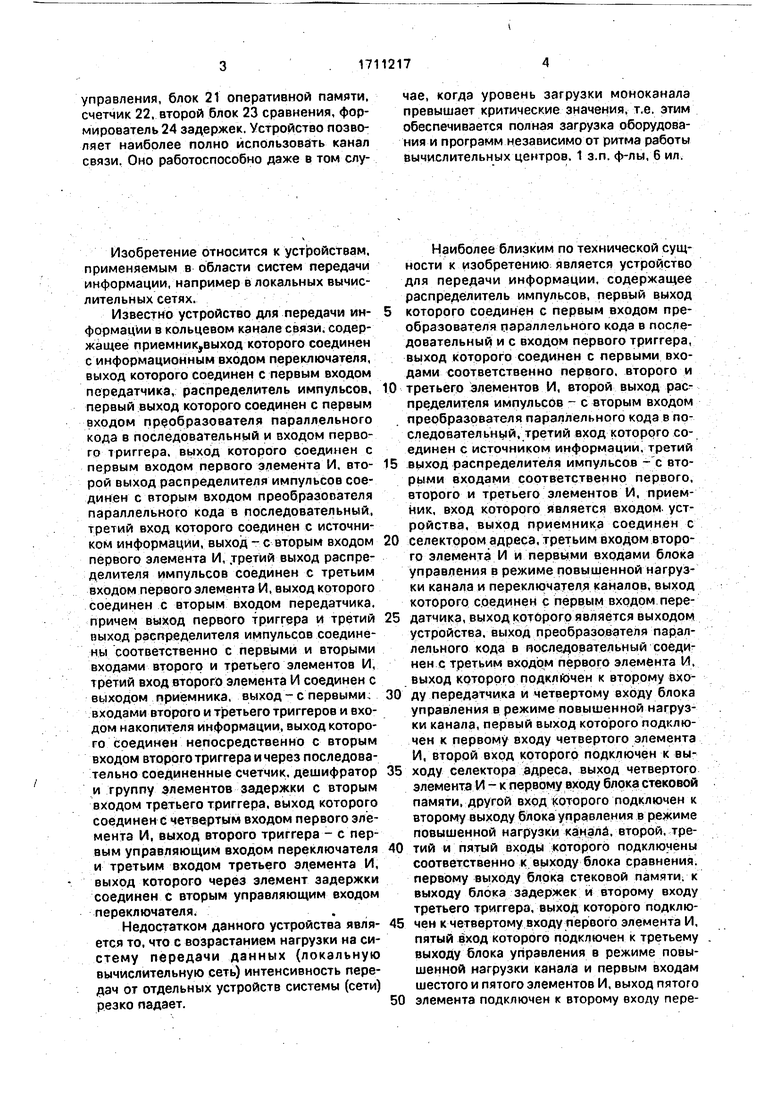

На фиг. 1 представлена блок-схема устройства для передачи информации; на фиг. 2 - блок-схема формирователя задержек; на фиг. 3 - блок-схема блока стековой памяти; на фиг, 4 - блок-схема первой схемы сравнения; на фиг. 5 - граф-схема алгоритма работы блока управления в режиме повышенной нагрузки канала; на фиг. 6 - функциональная схема блока управления, реализованная на автомате Мили с входными сигналами xi-xg и выходными

У.1-У11.

Устройство для передачи информации (фиг. 1) содержит приемник 1, переключатель 2 каналов, передатчик 3, второй элемент И 4, первый триггер 5, распределитель б

импульсов, преобразователь 7 параллельного кода в последовательный, первый элемент И8, накопитель 9 информации, второй 10 и третий 11 триггеры, третий элемент И 12, элемент 13 задержки, пятый

0 элемент И 14, селектор 15 адреса, четвертый элемент И 16, источник 17 информации, блок 18 стековой памяти, первый блок 19 сравнения, блок 20 управления, блок 21 памяти, счетчик 22, второй блок 23 сравне5 ния, формирователь 24 задержек, состоящий (фиг. 2) из генератора 25 случайных чисел, генератора 26 импульсов, делителя 27 частоты, элемента И 28.

Устройство работает в четырех режи0 мах: нормальной работы, блокирования столкновений, изъятия переданного кадра из сети, повышенной нагрузки в сети.

В режиме нормальной работы устройство работает только в том случае, когда уро5 вень загрузки -моноканала не превышает критического значения и стековая память неполная.

Распределитель 6 импульсов по первому выходу выдает управляющие сигналы,

0 разрешающие запись в параллельном коде информации в преобразователь 7 параллельногокода в последовательный (регистр сдвига). Запись производится по управляющему сигналу выхода преобразо5 вателя 7. В преобразователь 7 информация записывается из источника 17 информации в упакованном виде (кадра) стандартного формата в соответствии с протоколом управления каналами передачи данных. Од0 повременно управляющим сигналом с выхода преобразователя 6 импульсов первый триггер 5 готовности устанавливается в состояние с высоким уровнем сигнала логической единицы, означающее, что запись

5 информации в преобразователь 7 уже произведена.

Передача начинается в Том случае когда триггеры 5 и 11 находятся в состоянии логической единицы, а распределитель 6

0 импульсов формирует на своем выходе тактирующий сигнал начала передачи информации через элемент И 4 на передатчик 3.

Передача осуществляется в непоследо5 вательном коде (разряд за разрядом). Если на какой-либо позиции двоичного кода кадра происходит столкновение с другим кадром, передаваемым другим узлом (передатчиком), то устройство автоматически с помощью элемента И 4 и триггера 10,

фиксирующих передачу чужого кадра, устанавливает триггер 11 в уровень логического нуля, тем самым запрещая передачу кадра./

В режиме блокирования столкновений перед каждой передачей устройство прослушивает моноканал с помощью элемента И 4, который анализирует все столкновения. При появлении хотя бы одного сигнала с высоким уровнем логической единицы на входе, а следовательно, и на выходе приемника 1, свидетельствующего о ведущейся передаче информации в виде последова тельности кадров соседним или другим узлом сети, данный факт отражается поступлением этого сигнала на вход элемента И 4. На другой вход элемента И 4 от первого триггера 5 поступает сигнал логической единицы, свидетельствующий О готовности преобразователя 7 к передаче соответствующего кадра дискретной информации в моноканал. На второй вход элемента И 4 поступает сигнал логической единицы от распределителя 6 импульсов, разрешающий передачу информации. При совпадении этих событий происхрдит столкновение в моноканале Двух кадров информации, и элемент И 4 переключается в положение логической единицы, устанавливая триггер 10 в положение логического нуля. Триггер 10 своим выходным сигналом блокировки воздействует на управля- ющий вход переключателя 2 и разъединяет моноканал, препятствуя дальнейшему распространению передаваемых другим передатчиком сигналов.

Одновременно первым сигналом чужого флага кадра передатчика запускается накопитель 9 информации, который запоминает копию переданного другим передатчик ком кадра сообщения и переключает триггер 11 в состояние логического нуля, блокирующего своим выходом с помощью первого элемента И 8 передачу дискретной информации через передатчик 3. Совокупность сигналов, переданных другой станцией локальной вычислительной сети, записывается в накопитель 9 (регистр сдвига), размер которого соответствует размеру переданного полного сообщения (в соответствии с выбранным протоколом}/ Когда сообщение полностью принято, выходным сигналом завершающего флага переданного кадра информации в накопитель 9 осуществляется сброс триггера 10 в исходное состояние, т.е. снова соединяется моноканал. Одновременно выходной сигнал последнего разряда накопителя 9 информации формирует сигнал разрешения передачи, который поступает в формирователь 24

задержек, случайным образом определяющий задержку, длительность которой получается путем деления частоты импульров минимальной задержки (fa, мин), поетупаю- 5 щих с генератора 26 импульсов, на ное число, определяемое генератором 25 случайных чисел. Поэтому сигнал разрешения начала передачи от накопителя 9 информации приходит с соответствующей

10 задержкой иебрасывает триггер 11 в исходное состояние, разрешая передачу информации из преобразователя 7.

Таким образом, устройство блокирует передатчик только на время столкновения

15 плюс время задержки, зависимое от числа столкновений.

В режиме изъятия переданного кадра из сети после формирования тактирующего сигнала начала передачи на выходе распре0 делителя 6 импульсов, соединенного с вхо- дом элемента И 12, последний формирует сигнал логической единицы в том случае, если триггеры 5 и 10 находятся в состоянии логической единицы,, т.е. кадр находится в

5 преобразователе 7 и отсутствует столкновение в сети (это полностью соответствует режиму нормальной работы передатчика). Входной сигнал элемента И 12 запускает элемент 13 задержки, время задержки рав0 но времени возвращения по кольцу сети переданного передатчиком 3 кадра в приемник 1 устройства.

Таким образом, в момент, когда переданный кадр, обойдя все кольцо локальной

5 вычислительной сети, возвратится в приемник 1, выходной сигнал элемента 13 задержки разъединит канал с помощью переключателя 2 канала и кадр исчезнет. Если возникаетстолкновение(режим блоки

0 ровки столкновений сигналов) или преобразователь 7 не готов к передаче, то элемент И 12 формировать сигнал разъединения канала не будет.

В режиме повышенной нагрузки в сети

5 блок 20 управления работает параллельно с остальной частью устройства, что позволяет устройству работать во многих режимах. ;

При каждом обращении в сеть станций

их адреса (адреса источников) после пред0 верительной селекции пакета селектором 15 адреса записываются в блок 18 стеко- . вой памяти каждой станции сети. Запись

адресов в стек блока 18 производится после того, как будет установлено, были ли эти

5 адреса записаны ранее в стеке 18. Адресе выхода селектора 15 поступает на третий вход первой схемы 19 сравнения, на первый вход которой поступает адрес из стека блока 18, при этом управляющий сиг- -нал с шестого выхода блока 20 управления

разрешает выполнение операции сравнения адресов. Если поступивший адрес не был ранее записан в стек блока 1.8, то производится его запись. Если же этот адрес был ранее записан в стеке, то он в стек не записывается, а в блок 21 памяти подтем же адресом, что ив стеке блока. 18, где был ранее записан этот адрес, записывается содержимое счетчика 22 попыток передачи, на первый информационный вход которого поступает содержимое ячейки блока 21 памяти, а на другой (суммирующий) вход счетчика 22 - сигнал логической единицы из блока 20 управления. Адрес для выбора ячейки в блоке 21 памяти определяется указателем стека блока 18, в ячейке стека блока 18 хранится адрес станции, а в ячейке блока 21 памяти под тем же адресом (памяти) - количество попыток передачи информации соответствующей станцией.

Предварительно перед записью адреса источника проверяется объем стека блока 18. Объем блока 18 стековой памяти выбирается для каждой сети свой исходя из ее критической нагрузочной способности. Как только стек блока 18 достигает своего объема, первый блок 19 сравнения начинает проверку на соответствие адреса, хранящегося в нижней ячейке стека блока 18, адресу данной станции. Если адреса не совпадают, то исключаются все попытки захватить сеть-сигнал с блока 20 управления который поступает на вход элемента И 14. При этом вторым блоком 23 сравнения проверяется, сколько раз станция, адрес которой записан в нижней ячейке стека блока 18, предприняла попыток передать информацию. Если количество попыток станции равно предельно установленному значению, то ее адрес исключается из стека блока 18, т.е. происходит арифметический сдвиг стека и обнуляется соответствующая ячейка в блоке 21 памяти. Далее устройство переходит к анализу следующего адреса, хранящегося в следующей ячейке стека блока 18. Если же количество попыток пе- редачи станции меньше предельного/то необходимо дождаться поступления информации от станции под этим адресом. Если информация поступила от этой станции, то проверяется наличие другого адреса источника. Если его нет, то производится циклический сдвиг стека блока 18, а содержимое соответствующей ячейки блока 21 памяти обнуляется. Если есть другой адрес источника, то он после проверки его на новизну в стеке через элемент И 16 записывается в стек блока 18. Первым блоком 19 сравнения снова производится проверка на соответствие адреса ц нижней ячейке

стека блока 18 адресу данной станции. Далее работа аналогична изложенному.

Если информация не поступила от данной станции, то одновременно с выдержкой

времени задержки г, которая вырабатывается в формирователе 24 задержек, проверяется наличие столкновения в моноканале сети. Если по истечении времени г столкновения не было, то из стека

исключается адрес этой станции, т.е. происходит арифметический сдвиг стека блока 18. После сдвига стека проверяется его обьем- еслион равен установленному значению, то первый блок 19 сравнения продолжает

сравнение адресов, записанных в ячейках стека, с адресом данной станции. Далее работа устройства аналогична изложенной части алгоритма.

Если же столкновение произошло, то

необходимо дождаться нового адреса источника из приемника 1, проверить, есть ли он в стеке, и если нет, то записать в стек блока 18. Если объем стека неполный, то необходимо записать недостающие адреса источников.

В случае, когда адрес, записанный в нижней ячейке стека блока 18, совпадает с адресом данной станции, то блок 20 управления вырабатывает управляющий сигнал,

разрешающий данной11 станции передать информацию в моноканал/При этом необходимо постоянно проверять наличие столкновений в моноканале. .

Если в этот момент столкновение не

произошло, то необходимо продолжить передачу информации от этой станции и по ее успешному окончанию произвести циклический сдвиг стека блока 18. При помощи первого блока 19 сравнения продолжают

: проверку на совпадение адреса, записанного в нижней ячейке стекла, с адресом данной станции.V

Если же во время передачи произошло столкновение, то необходимо дождаться поступления следующего адреса источника и после его проверки на новизну в стеке блока 18 записать его в стек. Далее при помощи первого блока 19 сравнения производится проверка на соответствие адреса, записанного в нижней ячейке стека, с адресом данной станции, и процесс работы устройства повторяется.

Техническое преимущество изобретения заключается в наиболее полном использовании канала связи, т.е. исключаются потери информации.

ФОрмул а изо бретени я 1, Устройство для передачи информации, содержащее распределитель импульсов, первый выход которого соединен с первым входом преобразователя параллельного кода в последовательный и вхо- дсУм первого триггера, выход которого соединен с первыми входами первого, вто- рого и третьего элементов И, второй выход распределителя импульсов подключен к второму входу преобразователя параллельного кода в последовательный, третий вход которого является первым входом устройст- ва, третий выход распределителя импульсов подключен к вторым входам первого, второго и третьего элементов И, приемник, вход которого является вторым входом устройства, выход соединен с входом селектора адреса, третьим входом второго элемента И и первыми входами блока управления и переключателя каналов, выход которого подключен к первому входу передатчика, выход которого является выходом устройства/выход преобразователя параллельного кода в последовательный соединен с третьим входом первого элемента И, выход которого подключен к второму входу передатчика и второму входу блока управле- ния, первый выход которого подключен к первому входу-четвертого элемента И, второй вход которого соединен с выходом лектора-адреса, выход четвертого элемента И соединён с первым входом блока стеко- вой памяти, второй вход которого соединен с вторым выходом б.тзка управления, пер вый, второй и третий триггеры/третий вход блока управления подключен к выходу пер- вого блока сравнения, четвертый вход CQ&- динен с первым выходом блока стековой памяти, пятый вход объединен с R-входом третьего триггера, выход которого подключен к четвертому входу первого элемента И, пятый вход которого объединен с первым входом пятого элемента И и подключен к третьему выходу блока управле ния, выход второго триггера соединен с вторым входоМ переключателя каналов и третьим входом третьего элемента VI, выход которого соединен с входом ч элемента задержки; выход второго элемента И подключен к S-входам второго и третьего триггеров и входу накопителя информации, выход которого соединен с R-входом второго тригге-

ра, второй выход первого блока стековой памяти подключен к первому входу первого блока сравнения, о т л и ч а ю щ е е с я тем, что, с целью повышения информативности устройства, в него введены формирователь задержек, второй блок сравнения, счетчик и блок оперативной памяти, первый вход формирователя задержек подключен к четвертому выходу блока управления, второй вход формирователя задержек объединен с R-входом второго триггера, пятый выход блока управления подключен к первому входу второго блока сравнения, второй вход которого объединен с первым входом счетчика и соединен е выходом блока оперативной памяти, шестой выход блока уп- равления подключен к второму входу счетчика, выход которого соединен с информационным входом блока оперативной памяти, седьмой выход блока управления соединен с вторым входом первого блока сравнения, третий вход которого подключен к выходу селектора адреса, управляющий вход блока оперативной памяти подключен к восьмому выходу блока управления, адресный вход блока оперативной памяти соединен с третьим выходом блока стековой памяти, выход второго блока сравнения подключен к шестому входу блока управления, выход элемента задержки соединен с вторым входом пятого элемента И, выход которого подключен к третьему входу переключателя каналов, выход формирователя задержек подключен к R-входу третьего триггера.

С Выхода йаока 3 и на Второй

бход блока Ю

Фиг.2

С выхода 5/гока20 управ/гения

-Eh

ill

§И I

С выхода блока fS и на Вход блока IS

Фиг. 4

С Выхода S/toxa 20

На второй вход

С выхода 5лока/8

(j мауола )

ш

Содержимое ячейки блока ZlriaMWUffodmeMMte номером/адресом, что и щецфяд/го/еефслгма- бой памяти, где зо/к/сан этот адрес, убемшть нв1()

стеке блока 18; o&a/jie- fa/e со0л70е/гтс/ядул щей tvet/xt/ff/roKOZf/Tafostmy

J

f

Исключить дрщ/флуле- редсг/яь t/HtpqpMffquto

Ж

ЖЯят

faspO/ncfmMtfiti/etS ec

wnqp0U3ffrtvcafftttuxHw

ячеихестетб/юкаЮ

Запись адресаи&пами- ко 6 fotde/tfwtpojweu /у 5лот1&сгпёкаваг/ ламяггШ)

Hava/пь / etfot/y | Уу

т

ffp0cta/iwt/aib л&ёдяу

Фиг.5

| Устройство для передачи информации | 1988 |

|

SU1509970A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1992-02-07—Публикация

1990-03-05—Подача