задержки соединен с первыми входами элементов И третьей и шестой групп, выход четвертого элемента задержки через пятый элемент задержки соединен с первыми входами элементов И седьмой группы, выходы которых соединены соответственно с первыми входами элементов ИЛИ четвертой группы, выходы последних соединены соответственно с входами синхронизации регистров кодов операций, информационные входы которых подключены к информационному входу устройства,вход установки нулевого состояния каждого регистра.кодов операций соединен с выходом соответствующего элемента ИЛИ сброса регистров кодов операций, первый вход которого соединен с выходом элементов ИЛИ второй группы, вторые входы которых соединены соответственно с выходами элементов И шестой группы, второй вход j-го элемента сброса регистров кодов операций С j 2-1) соединен с выходом (J-1)-го элемента ИЛИ сброса регистров кодов операций, второй вход первого элемента ИЛИ сброса регистров кодов операций через шестой элемент задержки соединен с четвертым выходом формирователя управляющих сигналов, шестой выход последнего соединен с первыми входами элементов И восьмой группы, выходы которых соединены соответственно с вторыми вхоДс1Ми элементов ИЛИ четвертой группы, вторые входы элементов И с первой по восьмую групп соединены с выходом дешифратора, вход которого соединен с выходом счетчика операндов, информационный вход которого соединен с выходом блока стековой памяти, седьмой выход формирователя управляющих сигналов соединен с третьим входом второго элемента ИЛИ; восьмой и девятый выходы формирователя управляющих сигналов являются соответственно выходом синхронизации и выходом сяиибки устройства, выход первого элемента ИЛИ соединен с первыми вхоДс1ми трехвходовых элементов И 1 груп вторые входы которых соединены с выходами соответствующих блоков выполнения операций преобразования данных, выходы соединены соответст венно с первыми входами элементов ИЛ пятой группы, вторые входы которых соединены с входом данных устройства, выходы «соединены соответственно с информацй6н$1ьпда входёот р егистров операндов, входы синхронизации: к;ото-, рых и третьи входы трехвходовых элементов И 1 групп соединены с -выходами элементов ИЛИ третьей группы, входы установки нулевого состояния регистров операндов соединены с выходами соответствующих элементов ИЛИ сброса регистров операндов, второй вход j-ro элемента ИЛИ сброса регист

ров операндов (j 2т(1+1)) соединен с выходом (j-l)-ro элемента ИЛИ, второй вход первого элемента ИЛИ сброса регистров операндов соединен с выходом uiecToro элемента задержки, выходы (2-1 ) регистров операндов соединены с первыми входами соответствующих блоков выполнения операций преобразования данных, второй вход j-ro блока выполнения операций преобразования данных (j 1г(1-1) соединен с выходом (J+1 )-го блока выполнения операций преобразования данных третьи входы блоков выполнения операций преобразования данных соединены с выходами соответствующих регистров кодов операций, второй вход 1-го блока выполнения операций преобразования данных соединен с выходом (l-i-l)-ro регистра операндов, четвертые входы блоков выполнения операций преобразования данных соединены соответственно с управляющими выходами распределителя импульсов, первый вход которого соединен с входом синхронизации устройства, второй вход соединен с выходом счетчика операндов , третий и четвертый входы соеди.нены соответственно с пятым и первым выходами формирователя управляющих сигналов, выход установки соединен с входом второго элемента задержки. 2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что распределитель импульсов содержит элементы И, ИЛИ, задержки, триггер, одновибраторы, счетчик, регистр, дешифратор , блок сравнения, причем вход первого элемента з адержки, первые входы первого и второго элементов И соединены с первым входом распределителя, второй вход которого соедине с информационными входами счетчика и регистра, третий вход распределителя подключен к первому входу элемента ИЛИ, второй вход которого и входы первого и второго одновибраторов соединены с четвертым входом распределителя, выходы элемента ИЛИ и первого элемента задержки соединены соответственно с входами третьего элемента И,выход которого через третий одновибратор подключен к управляющему входу дешифратора, выходы которого являются управляющими выходами распределителя, выход первого одновибратора подключен к первсялу входу триггера и второму входу второго элемента И, третий вход которого соединен с первым выходом триггера,выход второго/элемента И подключен к вычитающему входу счетчика, синхронизирующий вход которого и вход второго элемента задержки соединены с вторым выходом триггера, выход второго одновибратора соединен с синхронизирующим входом регистра, выходы счетчика соединены с первой группой

входов блока сравнения и с информационными входами дешифратора, выходы регистра соединены с второй группой входов блока сравнения, выход блока сравнения соединен с первым входом четвертого элемента И и с вторым вхбдом триггера, первый выход которого через третий элемент задержки соединен с вторым входом четвёртого элемента И, выход которого является выходом установки распределителя, выход второго элемента задержки соединен с вторым входом первого элемента И, вцход которого является выходом синхронизации распределителя,

3,Устройство по п.1, отличаю щ е е с я тем, что формирователь управляющих сигналов содержит элемент НЕ, шифратор и дешифратор, входы которого являются входами формирователя, а выходы соединены с входами шифратора, выходы которого

с первого по седьмой являются с первого по седьмой выходами формирователя, восьмой выход шифратора является выходом синхронизации формирователя, девятый выход шифратора через элемент НЕ соединен с выходом ошибки формирователя.

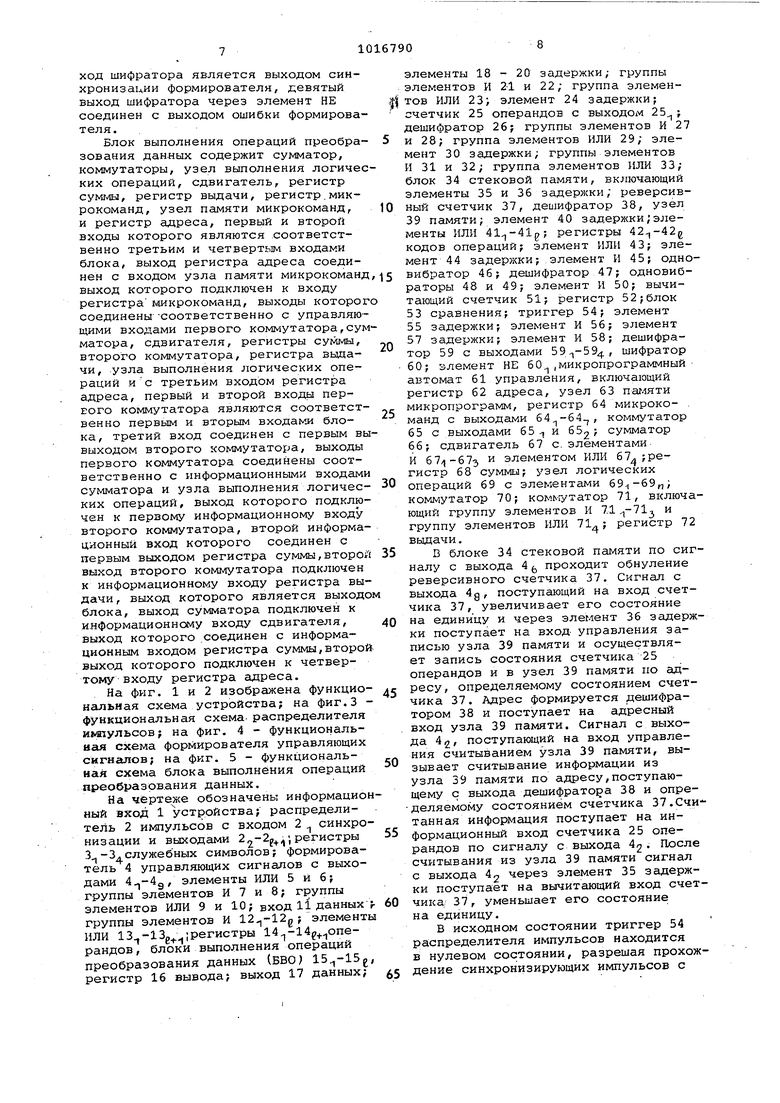

4.Устройство по П.1, о т л и ч а ю щ ее с я тем, что блок выполнения операций преобразования данных содержит сумматор, коммутаторы, узел выполнения логических операций, сдвигатель, регистр суммы регистр выдачи, регистр микрокоманд

узел памяти микрокоманд и регистр адреса, первый и второй входы которого являются соответственно третьим и четвертым входами блока, выход регистра адреса соединен с входом узла памяти микрокоманд, выход которого подключен к входу регистра микрокоманд, выходы которого соединены соответственно с управляющими входами первого коммутатора, сумматора, сдвигателя, регистра сукмы, второго коммутатора, регистра выдачи, узла выполнения логических операций, с третьим входом регистра адреса, первый « второй входы первого кЬммутаттора йтвляю-тся соответственно первым и вторым входами блока, третий вход соединен с первым выходом второго коммутатора, вькоды первого коммутатора соединены соответственно с информационными входами cyivwaTopa и узла выполнения логических операций, выход которого подключен к первому информационному входу второго коммутатора, второй информационный вход .которого соединен с аервым выходом регистра суммы, второй выход второго коммутатора подключен к информационному входу регистра вьщачи, выход которого является выходсм блока, выход сукматора подключен кинформационному входу сдвигателя, выход которого соединен с информационным входом регистра.суммы, второй выход которого подключен к четвертому входу регистра адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для интерпретации выражений языков программирования | 1982 |

|

SU1078432A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для съема координат с экрана электроннолучевой трубки | 1983 |

|

SU1144128A1 |

| Адаптивная система передачи дискретных сообщений | 1986 |

|

SU1497755A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство для контроля хода программ | 1988 |

|

SU1539785A1 |

| Устройство для управления параллельным выполнением команд в стековой электронной вычислительной машине | 1976 |

|

SU556440A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

1- Изобретение относится к вычислительной технике и может быть использовано в быстродействующих операционных системах обработки информации , в частности в системах с .диалоговым режимом разработки,отладки и выполнения программ, а такж в ЭВМ с языком высокого уровня. Известен процессор/ содержащий арифметико-логический блок, регистр дешифратор, блок стековой памяти, блок анализа символов, регистр кода операции, формирователь управляющих сигналов . ., „К недос.таткам процессора относят сязначитеАьнь1езатрат{$1 времени на Трайсляцйю С; языков выс,окрго уровня .на внутренний язык, пр01шес±вмощую вычислениям. , . Известен интерпретатор алгоритми ческого языка, содержащий регистр кодов служебных символов, регистр данных, регистр операций, счетчик дешифратор, формирователь управляющих символов, арифметико-логический блок, блок памяти С 2. Недостатком указанного интерпретатора является бо.льшая сложность процесса интерпретации, а также низкое быстродействие устройства.. Наиболее близким по технической сущности к предла.гаекюму является устройство для обработки выражений языков: пpoгpa 4миp6вaния, содержшцее вход кодов служебных символов,вход синхронизации, вход данных, первый и второй регистры операндов, формирователь управляющих сигналов, первый выход которого соединен с входом управления считыванием блока стековой памяти, входом синхронииации счетчиKia, операндов, счетный вход которого соедийёй с BTOpi4 вьесоДом фррмирователя управляквдих сигналов, третий выход которого соединен с входом управления записью блока стековой памяти, ш)фО1илационный вход которого соединен с выходом счетчика операндов, вход установки нулевого состояния которого с входом установки нулевого состояния указателя блока стековой памяти и входом синхронизации выходного регистра подключены к четвертому выходу формирователя упра ляющих сигналов; выход первого регистра операндов подключен к первому входу арифметико-логического блока, выход которого соединен с информационными входами выходного регистра выход которого соединен: с выходом данных СЗЗНедостатком известного устройства является низкая скорость обработки арифметико-логических выражений, поскольку в нем выражения предваритель но преобразуются в польскую инверсну запись (ПОЛИЗ) и только после этого вычисляются. Система имеет низкую скорость трансляции программ, так как основные ее элементы и связи меж ду ними выполнены программно в виде инструкций. Трансляция осуществляется методом ПОЛИЗа, основанного на прямом просмотре формулы исходного текста программы, вычислений проме жуточных результатов, загрузки формулы в стек в инверсном ее представлении с последующей выгрузкой формулы из стека и вычислении результата. По этому методу в стек загружается ,вся формула вместе с операциями. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем .что в устройство, содержащее первый и второй регистры операндов, формирователь управляющих сигналов, первый выход которого соединен с входом управления считыванием блока стеково памяти,йходом синхронизации счетчика оперантов, счетный вход которого соединен с вторым выходом формирователя управляющих сигналов, третий выход которого соединен с входом управления записью; блока стековой памяти, информационный вход которого соединен с выходом счетчика операндов, вход установки нулевого состояния которого и вход синхронизации регистра вывода подключены к четвертому выходу формирователя управляющи сигналов, выход первого регистра опе рандов подключен к первому входу пер вого блока выполнения и операций пре образования данных, выход которого соединен с информационным входом регистра вывода, выход которого соединен с выходом устройства,, внедрены эл элементы задержки, элементы ИЛИ И, дешифратор, (1-1) регистров операндов, 1 регистров кодов операндов, (1-1) блоков выполнения операций преобразования данных, (l+l) элементов ИЛИ сброса регистров операндов, 1 элементов ИЛИ сброса регистров кодов операций, распределитель им :. пульсов и четыре регистра служебных символов, входы синхронизации которых соединены с выходом синхронизации распределителя импульсов, информационные входы первого регистра служебных символов подключены к информационному входу устройства, выход i-ro (i 1-3) регистра служебных символов соединен с информационными входами (i+1)-ro регистра служебных символов и i-M входом формирователя управляющих сигналов, четвертый вход которого соединен с выходом четвертого регистра служебных символов, первый выход формирователя управляющих сигналов через первый элемент задержки соединен с первыми входами первого и второго элементов ИЛИ, выход второго элемента задержки, соединен с первыми входами элементов И первой и второй групп, выходы которых соединены соответственно с первыми входами элементов ИЛИ первой и второй групп, вторые входы элементов ИЛИпервой группы соединены с выходами элементов И третьей группы, а выходы соединены с первыми входами (1+1) элементов ИЛИ сброса регистров операндов, второй выход формирователя управляющих сигналов через третий элемент задержки соединен с вторым входом второго элемента ИЛИ, выход которого соединен с первыми входами элементов И четвертой группы, выходы которых соединены соответственно с первыми входами элементов ИЛИ третьей группы, вторые входы последних соединены соответственно с выходами элементов И пятой группы, первые входы которых,второй вход первого элемента ИЛИ и вход . четвертого Элемента задержки соединены с пятым выходом формирователя управляющих сигналов, выход четвертого элемента задержки соединен с первыми входами элементов И третьей и шестой групп, выход четвертого элемента задержки через пятый элемент задержки соединен с первыми входами элементов и седьмой группы, выходы которых соединены соответственно с первым входами элементов ИЛИ четвертой группы, выходы последних соединены соответственно с входами синхронизации регистров кодов операций, информационные входы которых подключены к информационному входу устройства, вход установки нулевого состояния каждого регистра кодов операций соединен с В :; 1ходом соответствующего элемента ИЛИ сброса регистров кодов операций, первый вход которого соединен с выходом элементов ИЛИ второй группы, вторые входы которых соединены соответственно с выходами элементов И шесой группы, второй вход j-ro эл.емента броса регистров кодов опергщий

(j 2т1) соединен с выходом (j-l)-ro элемента ИЛИ сброса регистров кодов операций, второй вход первого элемента ИЛИ сброса регистров кодов операций через шестой элемент задержки соединен с четвертым выходом формиро вателя управляющих сигналов, шестой выход последнего соединен с первыми входами элементов И восьмой группы, выходы которых соединены соответственно с вторыми входами элементов ИЛИ четвертой труппы, вторые входы элементов И с первой по восьмую группу соединены с выходом дешифратора, вход которого соединен с выходом счетчика опёрандог, информациейный вход которого соединен с выходом блока стековой памяти, седьмой выход формирователя управляющих сигналов соединен с третьим йходом второго элемента ИЛИ, восьмой и девятый выходы формирователя управляющих сигналов являются соответственно выходом синхронизации и выходом ошибки устройства, выход первого элемента ИЛИ соединен с первыми входами трехвходо вых элементов И 1 групп, вторые входы которых соединены с выходами COOT ве ствуюцих блоков выполнения операций преобразования данных, выходы соединены соответственно с первыми входагчШ эле ментов ИЛИ пятой группы вторые входы которых соединены с . входом данных устройства, выходы соединены соответственно с информационными входами регистров операндов, . входы синхронизации которых и третьи входы трехвходовых элементов И 1 груп соединены с выходами элементовИШ , третьей группы, входы установки нулевого состояния регистров операндов соединены с выходагли соответствующих элементов ИЛИ сброса регистров операндов, второй вход j-ro элемента ИЛИ cfippca регистров операндов. (J 2f(1 + 1 j) соединен с выходом (J-1)-го элемента ИЛИ, второй вход перврго элемента ИЛИ сброса регистров операндов с выходом шестого элемента задержки, выходы (2-1) регистров операндов соединены с . первыми входами сбответствуквдих блоков выполнения операций преобразования данных, второй вход j-ro блока выполнения операций преобразования данных (J 1т(1-1)) соединен с выходом (5+1 )-го блока выполнения операций преобразования данных,треть входы блоков выполнений операций преобразования данных соединены с выходами сЬответствуювщх регистров кодов операций, . второй вхо 1-го блока выполнення операций преобразования данных соединен с выходом (1+1)-го регистра Операндов,четвертые входы блоков выполнения операций преобразования данных соединены соответственно с управляющими выходами распределителя импульсов, первый вход которого соединен с входом синхронизации устройства,второй вход соединен с выходом счетчика операндов, третий и четвертый входы соединены соответственно с пятым и первым Выходами формирователя управляющих сигналов, выход установки соединен с входом второго элемента задержки. .

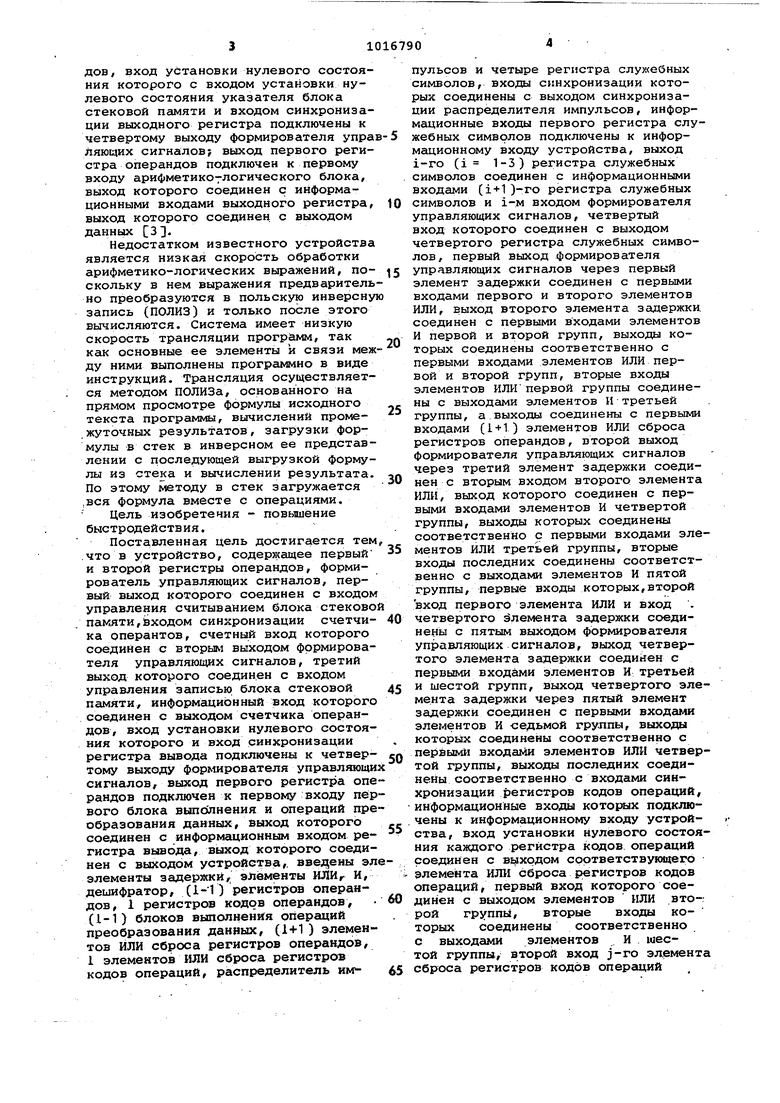

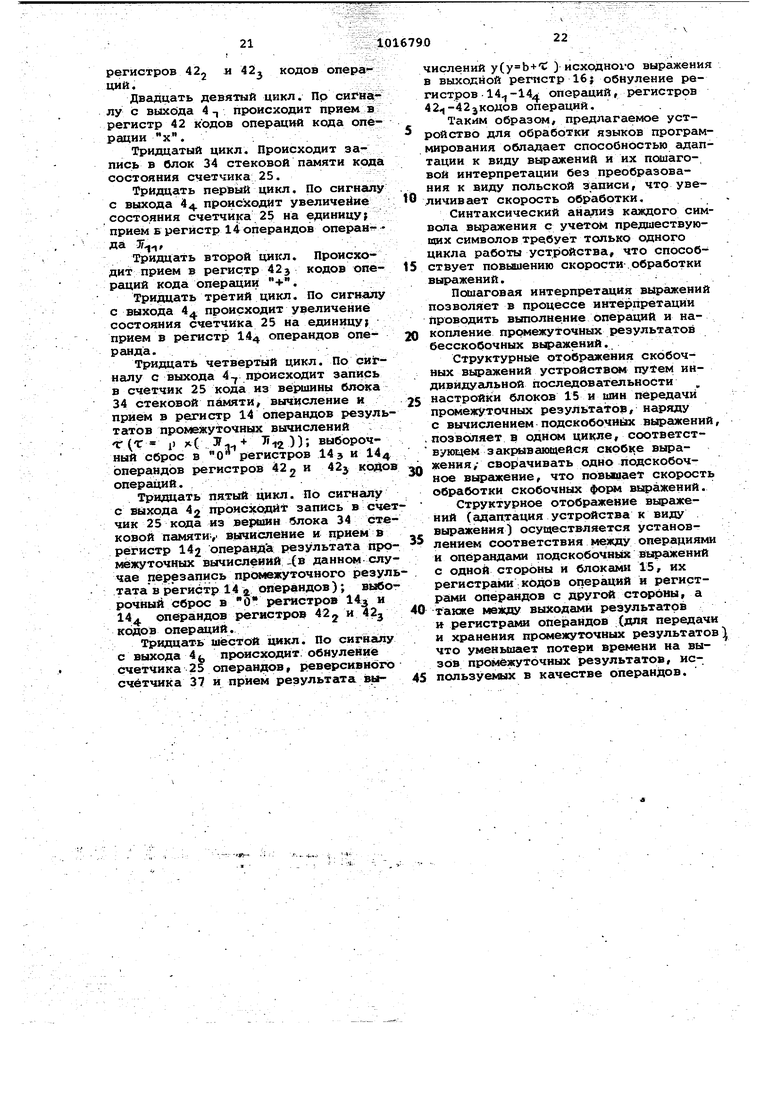

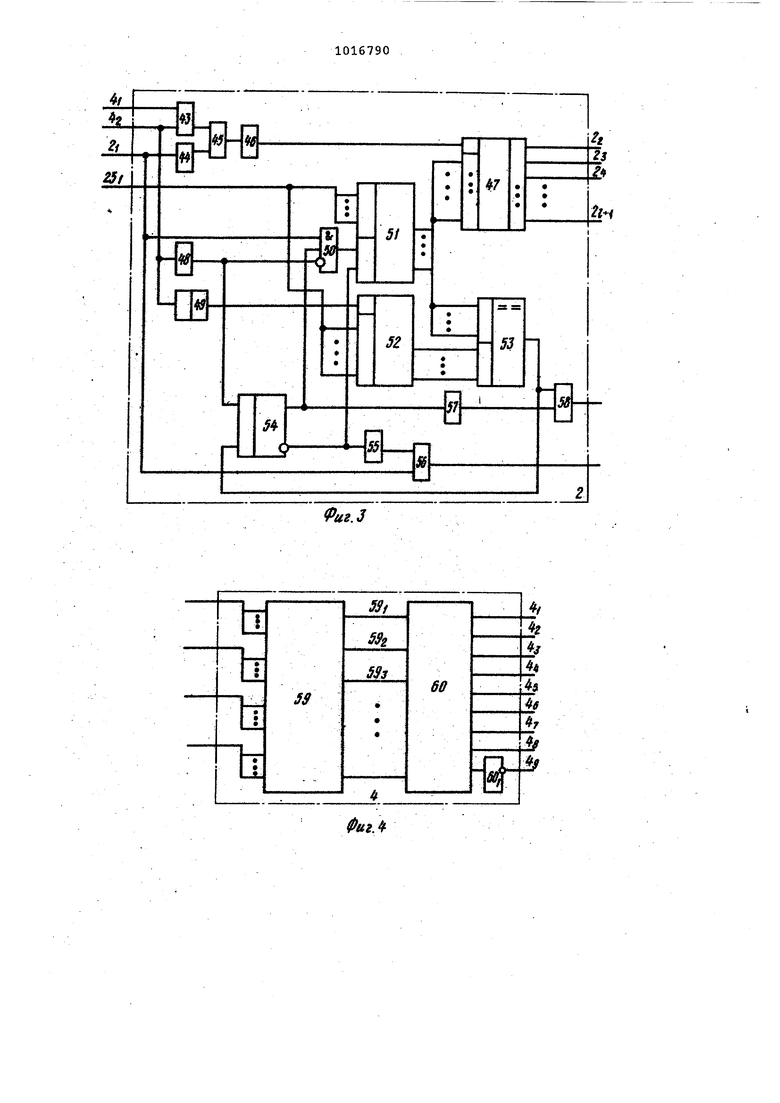

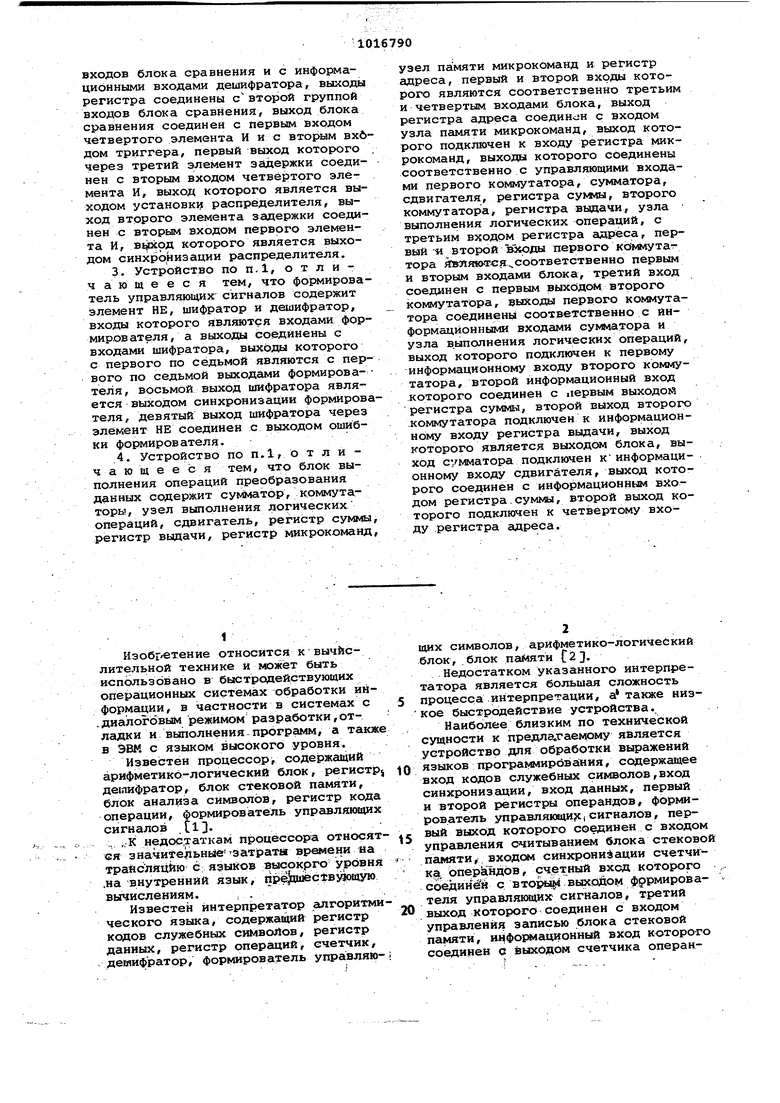

Распределитель импульсов в устройстве содержит элементы И, ИЛИ, задержки, триггер, одновибраторы, счетчик, регистр, деши ратор, блок сравнения, причем вход первого элемента задержки, первые входы первого и второго элементов И соединены с первым ВХОДО1Й распределителя,второй вход которого соединен с информационными входами счетчика и регистра, третий вход распределителя подключен к первому входу элемента ИЛИ, второй вход которого и входы первого и второго одновибраторов соединены с четвертым входом распределителя, выходы элемента ИЛИ и первого элемента задержки соединены соответственно с входами третьего элемента И, выход которого через третий одновибратор подключен к управлякмцему входу дешифратора, выходы которого являются управляющими выходами распределителя, выход первого одновибратора подподключен к первому входу триггера и второму входу второго элемента И, третий вход которого соединен с первым выходом триггера, выход второго элемента И подключен к вычитающему входу счетчика, синхронизирующий вход которого и вход второго элемента задер жки роединены с вторым выходом триггера, выход второго одновибратора соединен с синхронизирующим входом регистра, выходы счетчика соединены; с первой группой входов блока сравнени) и с информационными входами дааифратора, выходы регистра соединены с второй группой входов блока сравнения, ьыход блока сравнения соединен с первым входом четвертого элемента И и с вторым входом тригге15|а, первый выход которого чере третий элемент задержки соединен с вторьйл входом четвертого элемента И, выход которого является выходом установки распределителя, выход второго элемента задержки, соединен с вторым входом первого элемента И,выход которого является выходом синхронизации распределителя.

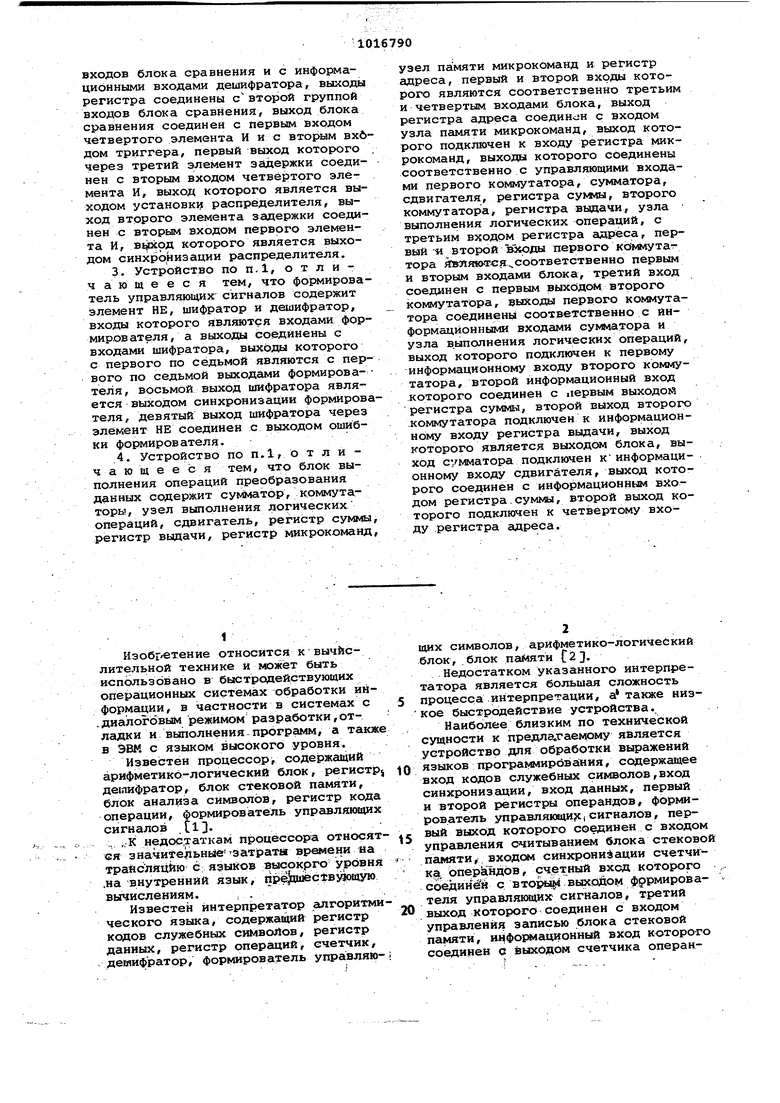

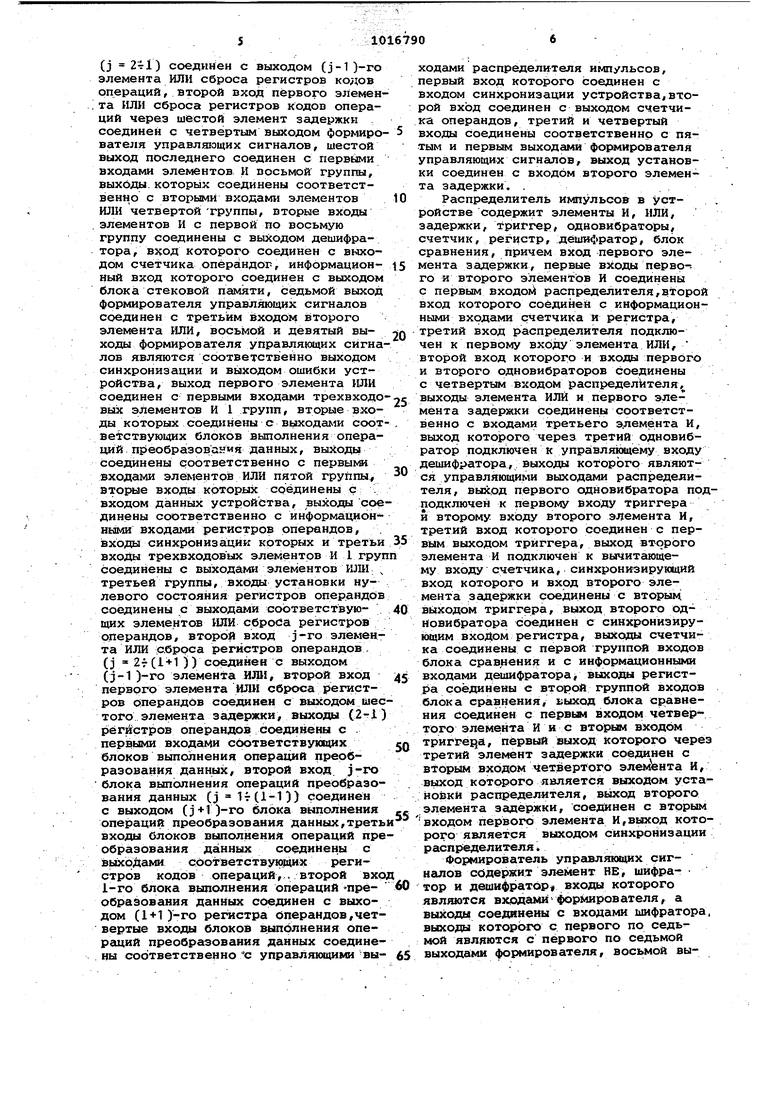

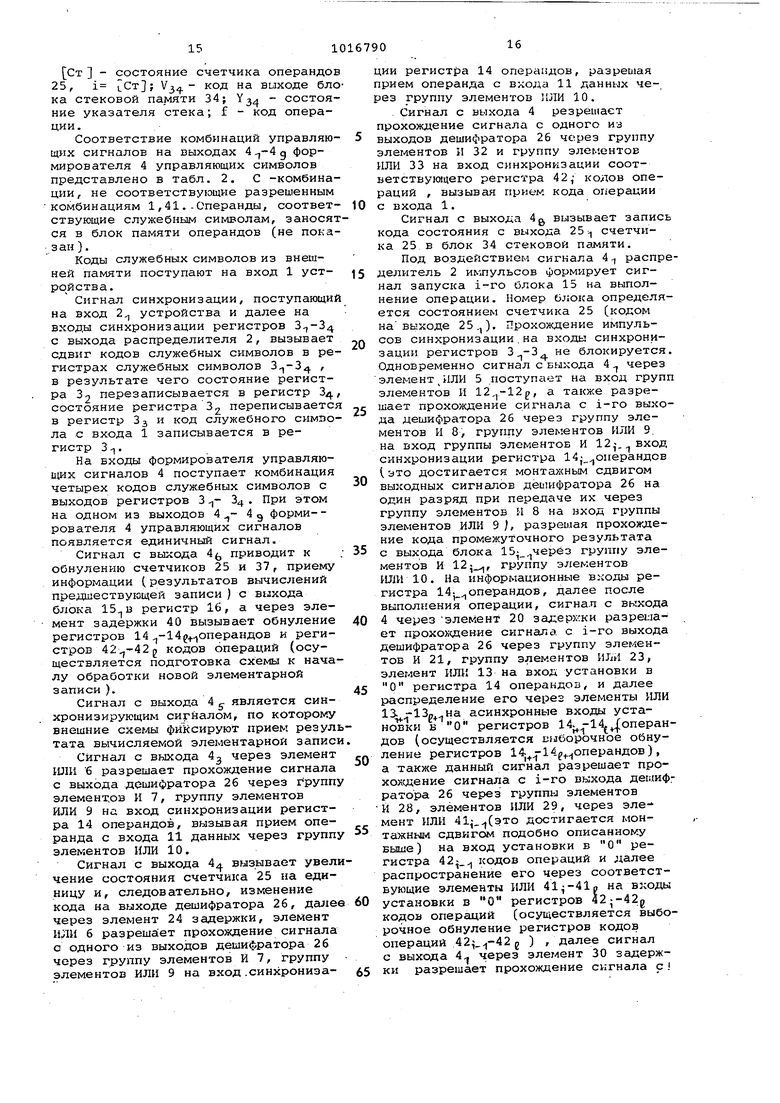

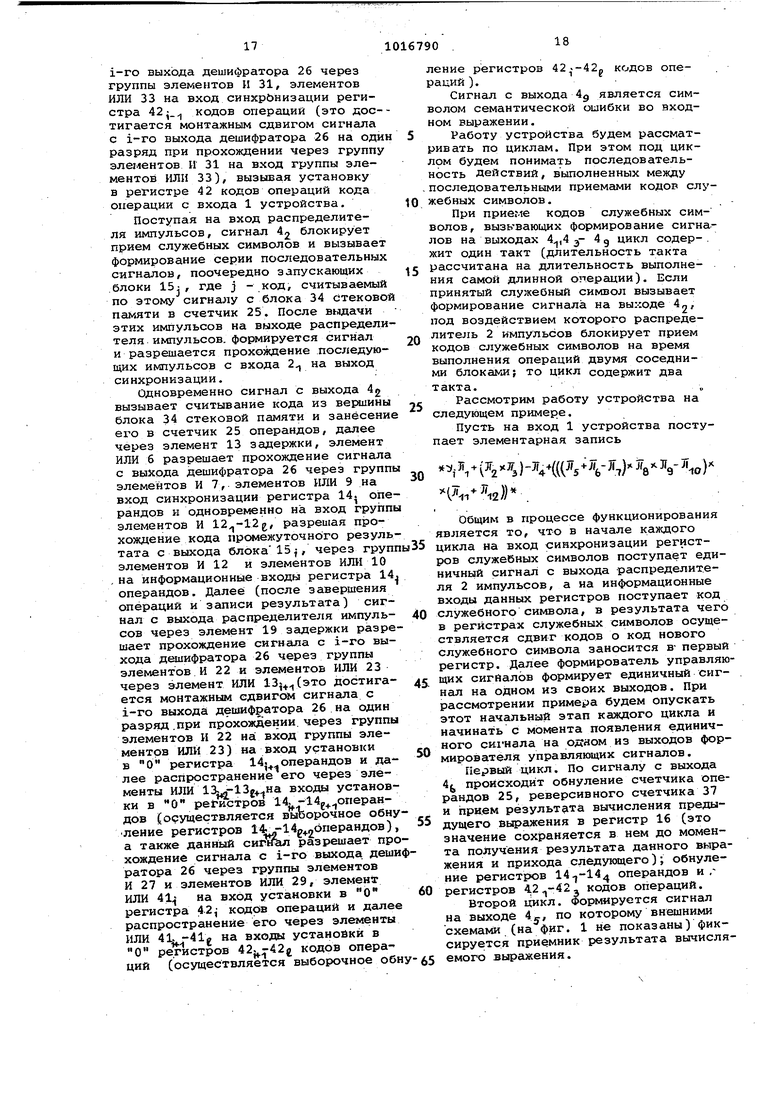

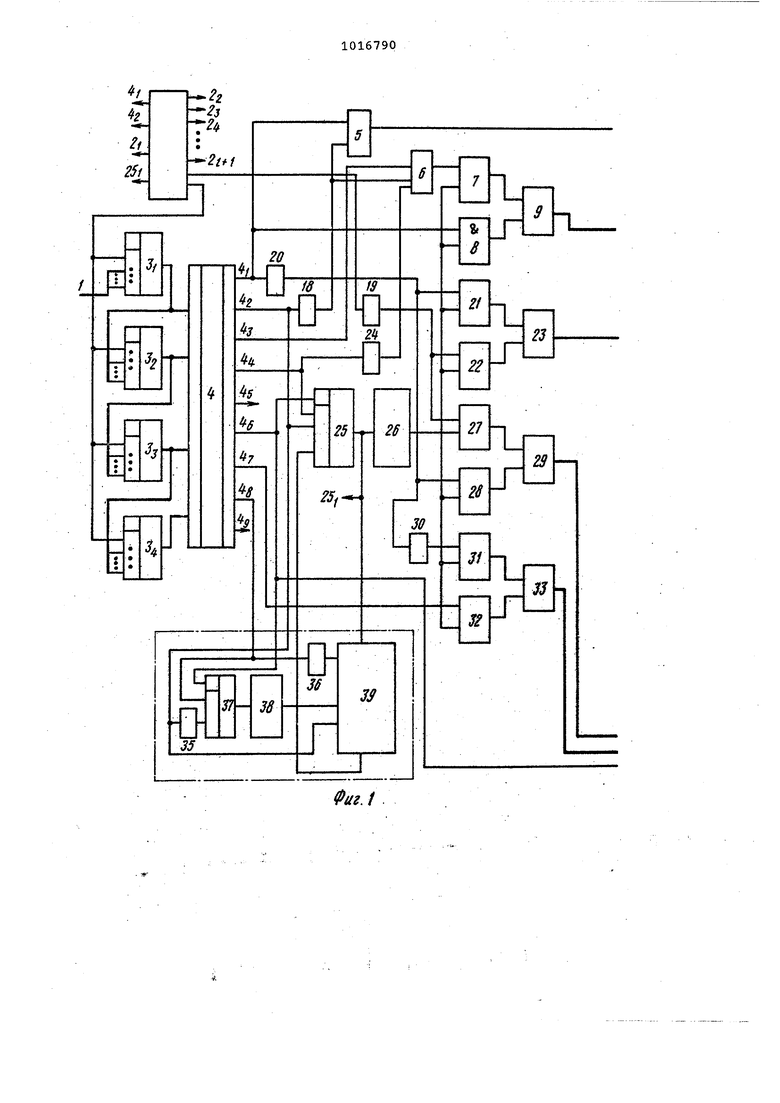

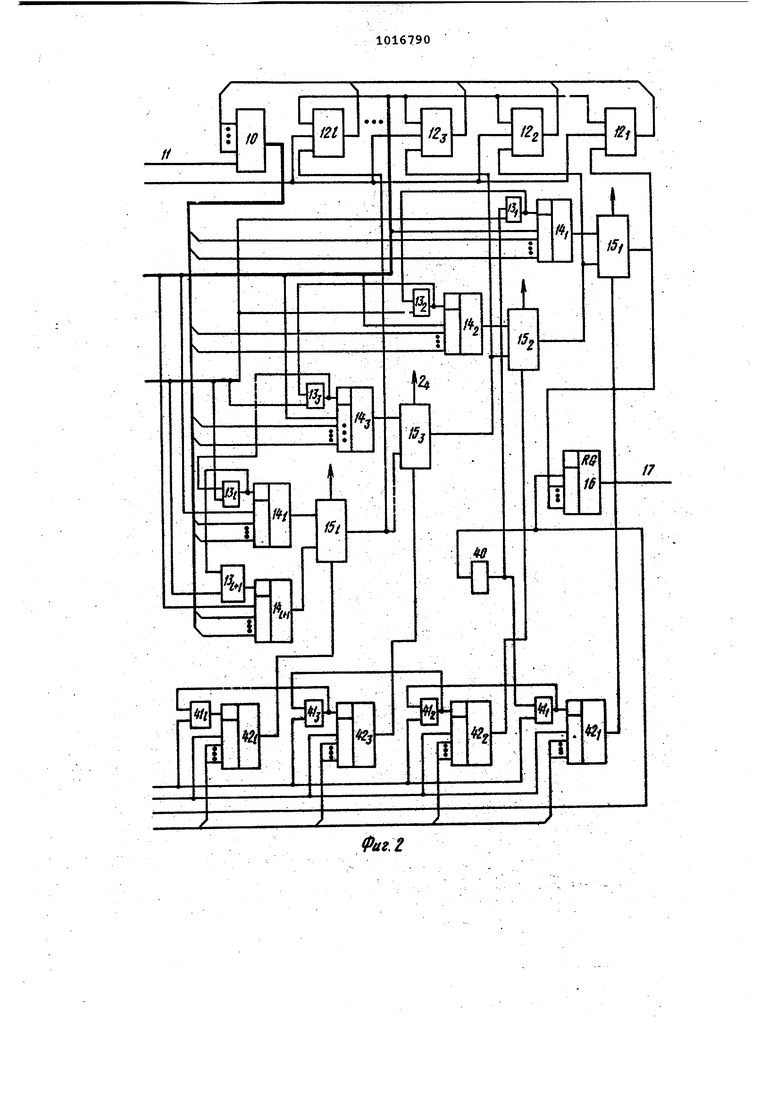

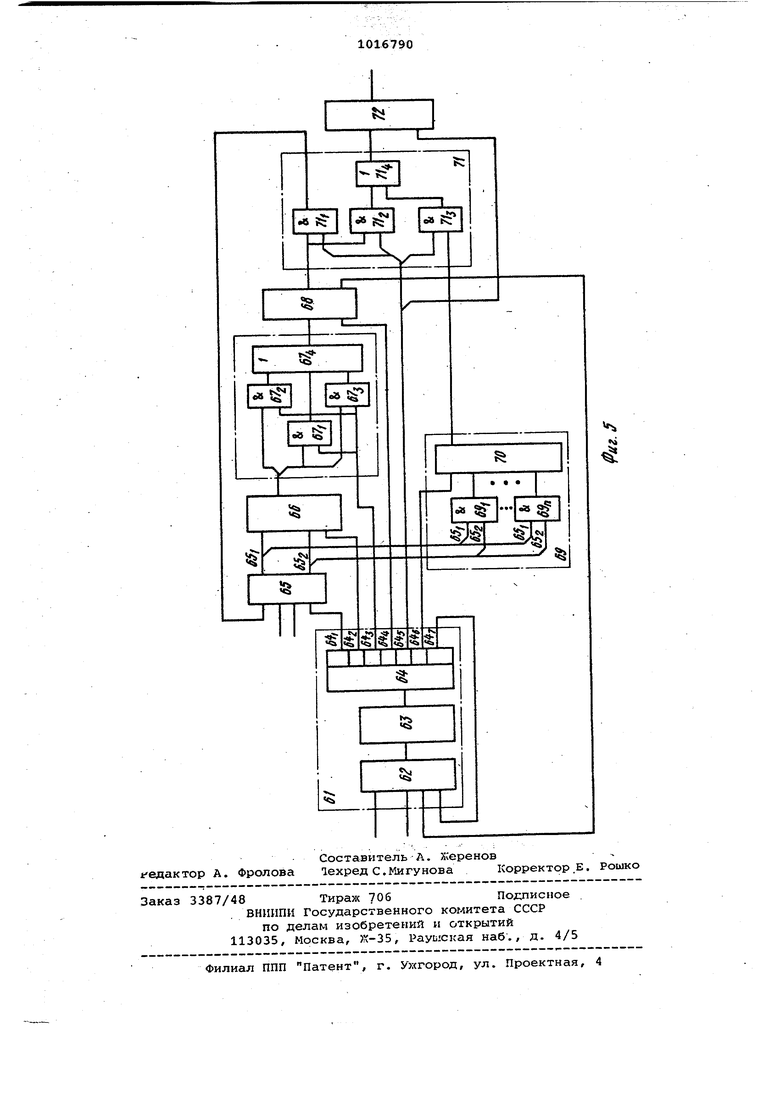

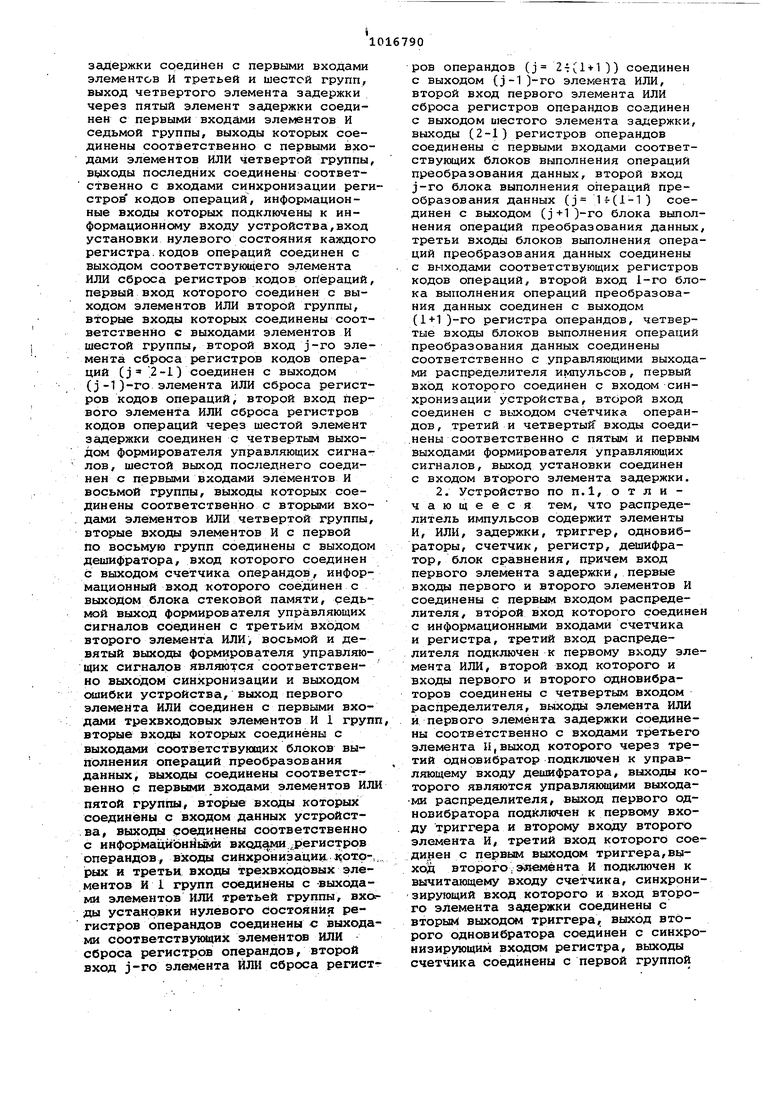

Формирователь управлякнцих сигналов содержит элемент НЕ, шифра- тор и дешифраторf входы которого являются входамиформирователя, а выходы соединены с входами шифратора выходы которого с. первого по седьмой являются с первого по седьмой выходами формирователя, восьмой выход шифратора является выходом синхронизации формирователя, девятый выход шифратора через элемент НЕ соединен с выходом ошибки формирова теля. Блок выполнения операций преобра зования данных содержит сумматор, коммутаторы, узел выполнения логиче ких операций, сдвигатель, регистр cyMTvttJ, регистр выдачи, регистр.микрокоманд, узел памяти микрокоманд, и регистр адреса, первый и второй входы которого являются соответственно третьим и четвертым входами блока, выход регистра адреса соединен с входом узла паг1яти микрокоманд выход которого подключен к входу регистра микрокоманд, выходы которо соединены-соответственно с управляю щими входами первого коммутатора,су матора, сдвигателя, регистры суммы, второго коммутатора, регистра выдачи, узла выполнения логических операций и с третьим входом регистра адреса, первый и второй входы первого коммутатора являются соответст венно первым и вторым входами блока, третий вход соединен с первым вы выходом второго коммутатора, выходы первого коммутатора соединены соответственно с информационными входами сумматора и узла выполнения логических операций, выход которого подключен к первому информационному входу второго коммутатора, второй информационный вход которого соединен с первым выходом регистра суммы,второй выход второго коммутатора подключен к информационному входу регистра выдачи , выход которого является выходо блока, выход сумматора подключен к информационному входу сдвигателя, выход которого соединен с информационным входом регистра суммы,второй выход которого подключен к четвертому входу регистра адреса. На фиг. 1 и 2 изображена функциоНсШЬНая схема устройства; на фиг.З функциональная схема- распределителя импульсов; на фиг. 4 - функциональиая схема формирователя управляющих сигналов; на фиг. 5 - функциональная схема блока выполнения операций преобразования данных. На чертеже обозначены информацион ный вход 1 Vcтppйcтвa; распределитель 2 импульсов с входом 2 синхронизации и выходами регистры 3 -Здслужебных символов; формирователь 4 управляющих сигналов с выходами , элементы ИЛИ 5 и 6; группы элементов И 7 и 8; группы элементов ИЛИ 9 и 10; вход 11 данных группы элементов И 12 -12g; элементы ИЛИ 13 -13g ;perHCTpH .операндов, блоки выполнения операций преобразования данных (БВО) регистр 16 вывода; выход 17 данных; элементы 18 - 20 задержки; группы элементов И 21 и 22; группа элементов ИЛИ 23; элемент 24 задержки; счетчик 25 операндов с выходом дешифратор 26; группы элементов И 27 и 28; группа элементов ИЛИ 29; элемент 30 задержки; группы элементов И 31 и 32; группа элементов ИЛИ 33; блок 34 стековой памяти, включающий элементы 35 и 36 задержки; реверсивный счетчик 37, дешифратор 38, узел 39 памяти; элемент 40 задержки;элементы ИЛИ 41 -41g; регистры кодов операций; элемент ИЛИ 43; элемент 44 задержки;,элемент И 45; одновибратор 46; дешифратор 47; одновибраторы 48 и 49; элемент И 50; вычитающий счетчик 51; регистр 52;блок 53 сравнения; триггер 54; элемент 55 задержки; элемент И 56; элемент 57 задержки; элемент И 58; дешифратор 59 с выходами , шифратор 60; элемент НЕ 60. ,микропрограммный автомат 61 управления, включающий регистр 62 адреса, узел 63 паг-мти микропрограмм, регистр 64 микроко- , манд с выходами ., коммутатор 65 с выходами 65 . и 652; сумматор 66; сдвигатель 67 с. элементами И 67/)-67з и элементом ИЛИ 6 7 ; регистр 68 суммы; узел логических операций 69 с элементами 69 -69„; коммутатор 70; кoм ryтaтop 71, включающий группу элементов И 7. и группу элементов ИЛИ регистр 72 выдачи. В блоке 34 стековой памяти по сигналу с выхода 4 проходит обнуление реверсивного счетчика 37. Сигнал с выхода 4д, поступающий на вход счетчика 37, увеличивает его состояние на единицу и через элемент 36 эадержки поступает на вход управления записью узла 39 памяти и осуществляет запись состояния счетчика 25 операндов и в узел 39 памяти по адресу, определяемому состоянием счетчика 37. Адрес формируется дешифратором 38 и поступает на адресный вход узла 39 памяти. Сигнал с выхода 4, поступающий на вход управления считыванием узла 39 памяти, вызывает считывание информации из узла 39 памяти по адресу,поступающему с выхода дешифратора 38 и определяемому состоянием счетчика 37.Считанная информация поступает на информационный вход счетчика 25 операндов по сигналу с выхода 2 После считывания из узла 39 памяти сигнал с выхода 2 ерез элемент 35 задержки поступает на вычитающий вход счетчика 37, уменьшает его состояние на единицу. В исходном состоянии триггер 54 распределителя импульсов находится в нулевом состоянии, разрешая прохождение синхронизирующих импульсов с

входа 2 на выход через элемент И 56. На входах 4 и 4, нулевые . В счетчик 51 переписывается состояние счетчика 25 по связи 25. Запись этого состояния в регистр 52 блокироЕажа.

При поступлении сигнала на вход 4 и окончании переходных процессов на выходе элемента И 45 появляется положительный перепад напряжения по которому одновибратор 46 вырабатывает импульс, разрешаюций формирование дешифратором 47 им1ульса запуска блока, номер которого (номер выхода деишфратора с единичным, сигналом) определяется сос: оянйем счетчика 51. Состояние счетчика при этом не меняется .

При поступлении сигнала на вход 42 аналогично формируется сигнал на одном и выходов дешифратора.47.Одновременнр одновибратор 48 выдает импульс, блокирующийИзменение состояния счетчика 51 в текущем такте и устанавливающий в единичное состояние триггер 54..Благодаря задержке 55 синхронизирующий импульс с входа 2 полностью поступает на выход через элемент И 56. Затем элемент 49 выдает импульс (nocaje считывания код и зсшиси его в счетчик 257, разрешающий запись кода с входа 25 в регистр 52. В каждом последукядем такте состояние счетчика 51 уменьшается на единицу и формируется им, -

f,

О

34

- - |l

«,

У .

H

-,«. 11

Ka шине 45- RG : - J

«. CT . Л 33.. Ktt .

пульс йа соответствующем выходе дешифратора 47. При совпадении состояний счетчика 51 и регистра 52 на выходе блока 53 сравнения появл;я ется единичный сигнал, устанавливающий триггер 54 в нулевое состояние.Это влечет за собой разрешение поступления последующих синхронизирщощих импульсов на выход.

Пссл@ формирования необходимого числа синхронизнрукацих импульсов по сигналу 42 единичный сигнал с выхода блока 53 сравнения препятствует формированию этого сигнала в момент поступления кода 42, когда в регистр 52t &яе не записано состояние счетчика 25, а триггер 54 уже установлен в единичное состояние. Сигнал с выхода синхронизаххии распределителя 2 импульсов может Сыть использован внешними схемами (не рассмотрены) для подготовки очередного кода служебного символа после записи очередного кода в регистр 3,,.

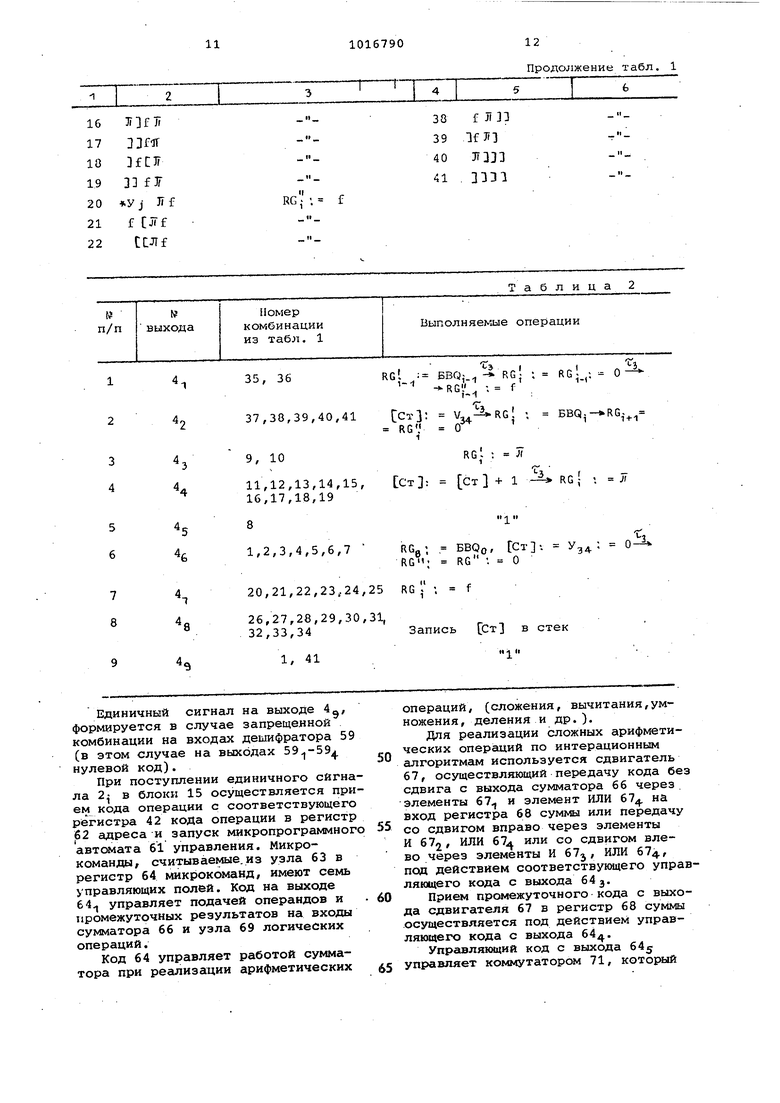

Коды служебных символов с регистров служебных символов поступают На входы дешифратора 59 формирователя 4, на одном из его выходов 59 -59ц формируется единичный сигнал (унитарный код), если комбинация кодов -служебных символов на входе соответствует одной из разрешенных (табл. 1). Унитарный код, поступая на вход шифратора 60, вызывает формрование унитарного кода на его выходах (табл. 2).

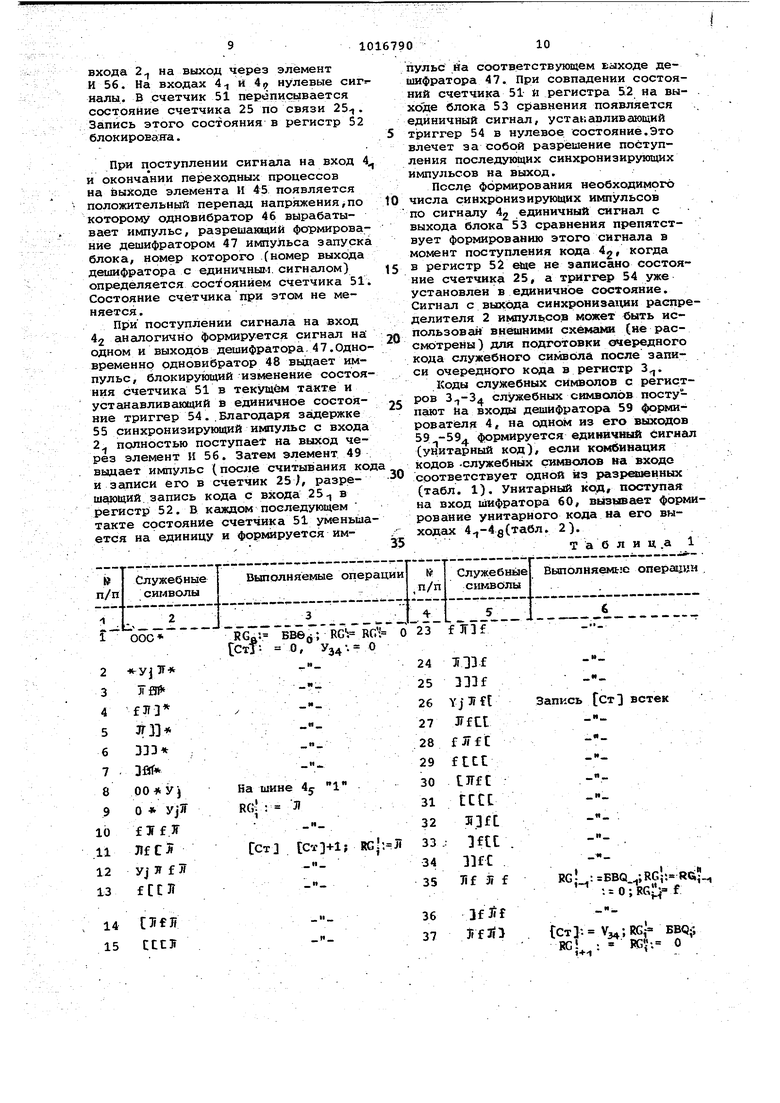

Т а б л и ц .а 1

113f

M 333f

Запись tCT встек

Yjl€

JlfCt

и fjTft

«

M ftCL

tlTfC

n

tccc

34 31fC lif 3 f Jflff 1ff3fl RG,.,;RG;: R : 0;RG; -f BBQ l.

Единичный сигнал на выходе 4, формируется в случае запрещенной комбинации на входах дешифратора 59 (в этом случае на выходах нулевой код).

При поступлении единичного сигнала 2 в блоки 15 осуществляется прием кода операции с соответствующего регистра 42 кода операции в регистр 62 адреса и запуск микропрограммного автомата 61 управления. Микрокоманды, считываемые, из узла 63 в регистр 64 микрокоманд, имеют семь управляющих полей. Код на выходе 64 управляет подачей операндов и промежуточных результатов на входы сумматора 66 и узла 69 логических операций.

Код 64 управляет работой сумматора при реализации арифметических

Продолжение табл. 1

операций, (сложения, вычитания,умножения, деления и др.).

Для реализации сложных арифметических операций по интерационным алгоритмам используется сдвигатель 67, осуществляющий передачу кода без сдвига с выхода сумматора 66 через. элементы 67 и элемент ИЛИ 67 на вход регистра 68 суммы или передачу со сдвигом вправо через элементы И 672 ИЛИ 674 ° сдвигом влево через элементы И 67j, ИЛИ 674, под действием соответствующего управляющего кода с выхода 64 д.

Прием промежуточного кода с выхода сдвигателя 67 в регистр 68 суммы осуществляется под действием управляющего кода с выхода 64.

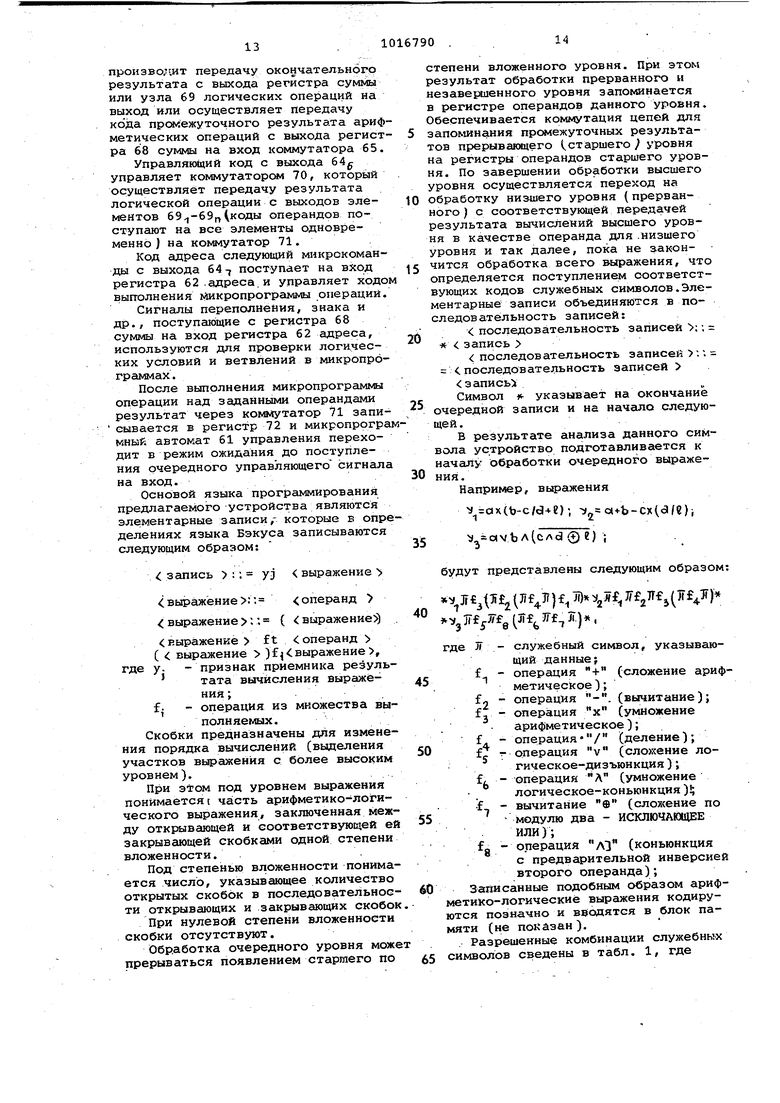

Управляющий код с выхода 64 5 управляет коммутатором 71, который производит передачу окончательного результата с выхода регистра cyMiia или узла 69 логических операций на выход или осуществляет передачу кода промежуточного результата ариф метических операций с выхода регист ра 68 суммы на вход коммутатора 65. Управляющий код с выхода 64 управляет коммутатором 70, который осуществляет передачу результата логической операции с выходов элементов , коды операндов поступают на все элементы одновременно ) на коммутатор 71. Код адреса следующий микрокоманды с выхода 64-J поступает на вхо;Д регистра 62.адреса.и управляет ходо выполнения микропрограммы операций. Сигналы переполнения, знака и др., поступа1ощие с регистра 68 суммы на вход регистра 62 адреса, используются для проверки логических условий и ветвлений в микропрограммах. После выполнения микропрогргшмы операции над заданными операндами результат через коммутатор 71 записывается в регистр 72 и микропрогра мный автомат 61 управления переходит в режим ожидания до поступления очередного управляющего сигнала на вход. Основой языка программирования предлагаемого устройства являются элементарные записи,- которые в опре делениях языка Бэкуса записываются следующим образом: запись :: yj выражение выражение .. операнд выражение :; ( выражение) Еыраженке ft операнд ( выражение )f выражение, где у- - признак приемника резуль тата вычисления выраокёния; . f- - операция из множества вы полняемых. Скобки предназначены для изменения порядка вычислений (выделения участков выражения с более высоким уровнем). При этом под уровнем выражения понимается t часть арифметико-логического выражения, заключенная меж ду откряывсиощей и соответствующей е закрывающей скобками одной степени вложенности. Под степенью вложенности понима ется число, указывающее количество открытых скобок в последовательное ти открывающих и закрывающих скобо При нулевой степени вложенности скобки отсутствуют. Обработка очередного уровня мож прерываться появлением старшего по степени вложенного уровня. При этом езультат обработки прерванного и незаве пленного уровчя запоминается в регистре операндов данного уровня. беспечивается коммутация цепей для запоминания промежуточных результатов прерывающего (.старшего } уровня на регистры операндов старшего уровня. По завершении обработки высшего уровня осуществляется переход на обработку низшего уровня (прерванного ) с соответствукмдёй передачей результата вычислений высшего уровня в качестве операнда для .низшего уровня и так далее, пока не закончится обработка всего выражения, что определяется поступлением соответствующих кодов служебных символов.Элементарные записи объединяются в последовательность записей: последовательность записей ;; запись последовательность записей , последовательность записей запись Символ (- указывает на окончание очередной записи и на начало следующей . В результате анализа данного символа устройство подготавливается к началу обработки очередного выражения. Например, выражения с1х(Ь-с/«3+е)-, (ol/)i о1чЬл() ; будут представлены следующим образом: , 1 V) f Ji) Vjiff (If ) «Л() где JT - служебный символ, указывающий данные; - операция + (сложение арифметическое ); fj - операция -. (вычитание); f, - операция х (умножение арифметическое); f. - опе:рация« / (деление ) ; fj г- операция v (сложение логическое-дизъюнкция); f/ - операция Л (умножение логическое-коньюнкция ); f - вычитание Ф (сложение по - модулю два - ИСКЛЮЧАЮЩЕЕ ИЛИ); fg - операция лЗ (коньюнкция с предварительной инверсией второго операнда); Записанные подобным образом арифметико-логические выражения кодируются позначно и вводятся в блок памяти (не показан). Разрешенные комбинации служебных символов сведены в табл. 1, где Ст - состояние счетчика операндо 25, i УЗ - код на виходе бл ка стековой памяти 34; Y - состоя ние указателя стека; f - код операции. Соответствие комбинаций управляю дих сигналов на выходах 4 -4 g формирователя 4 управляющих символов представлено в табл. 2. С -комбина ции, не соответствующие разрешенным комбинациям 1,41.-Операнды, соответ ствующие служебным сиг«1волам, занося ся в блок памяти операндов (не пока зан). Коды служебных символов из внешней памяти поступают на вход 1 устро йства. Сигнал синхронизации, поступающи на вход 2 устройства и далее на входы синхронизации регистров с выхода распределителя 2, вызывает сдвиг кодов служебных символов в ре гистрах служебных символов , в результате чего состояние регистра 32 перезаписывается в регистр 3 состояние регистра 32 переписываетс в регистр Зз и код служебного симэо ла с входа 1 записывается в регистр 3 -,. На входы формирователя управляющих сигналов 4 поступает комбинация четырех кодов служебных символов с выходов регистров 3 -,- 34 . При этом на одном из выходов 4 - 4 g форми- рователя 4 управляющих сигналов появляется единичный сигнал. Сигнал с выхода 4 приводит к обнулению счетчиков 25 и 37, приему информации (результатов вычислений предшествующей записи ) с выхода блока регистр 16, а через элемент задержки 40 вызывает обнуление регистров 14 -14 операндов и регистров кодов операций (осуществляется подготовка схемы к нача лу обработки новой элементарной записи ). Сигнал с выхода 4 является синхронизирующим сирйалом, по которому внешние схеглы фйКсируют прием резуль тата вычисляемой элементарной записи Сигнал с выхода 4 через элемент ШШ б разрешает прохождение сигнала с выхода дешифратора 26 через г руппу элементов И 7, группу элементов ИЛИ 9 на вход синхронизации регистра 14 операндов, вызывая прием операнда с входа 11 данных через группу элементов ИЛИ 10. Сигнал с выхода 4 вызывает увели чение состояния счетчика 25 на единицу и, следовательно, изменение кода на выходе дешифратора 26, далее через элемент 24 задержки, элемент ИЛИ 6 разрешагет прохождение сигнала с одного из выходов дешифратора 26 через группу элементов И 7, группу элементов ИЛИ 9 на вход .синхронизации регистра 14 операндов, разреишя прием операнда с входа 11 данных че-. рез группу элементов ИЛИ 10. Сигнал с выхода 4 резрешает прохождение сигнала с одного из выходов дешифратора 26 группу элементов И 32 и группу элементов ИЛИ 33 на вход синхронизации соответствую1иего регистра 42, кодов операций , вызывая прием кода операции с входа 1. Сигнал с выхода 4 вызывает запись кода состояния с выхода 25 счетчика 25 в блок 34 стековой памяти. Под воздействием сигнала 4 -, распределитель 2 иьшульсов формирует сигнал запуска i-го блока 15 на выполнение операции. Номер блока определяется состоянием счетчика 25 кодом навыходе 25.). Прохонодение импульсов синхронизации.на входы синхронизации регистров 3-3 не блокируется. Одновременно сигнал с выхода 4 через элемент ИЛИ 5 поступгизт на вход групп элементов И 12,-12р, а также разрешает прохождение сигнала с i-ro выхода дешифратора 26 через группу элементов И 8, группу элементов ИЛИ 9. на вход группы элементов И 12,-, вход синхронизации регистра 14} операндов 1 это достигается монтажным сдвигом выходных сигналов дешифратора 26 на один разряд при передаче их через группу элементов И 8 на вход группы элементов ИЛИ 9 , разрешая прохождение кода промежуточного результата с выхода блока 15,черёз группу элементов И 12 j, группу элементов ИЛИ 10. На информационные входы регистра 14- операндов, далее после выполнения операции, сигнал с выхода 4 через элемент 20 задерхгки разреишет прохоходение сигнала, с i-ro выхода дешифратора 26 через группу элементов И 21, группу элементов ИЛИ 23, элемент ИЛИ 13 на вход установки в О регистра 14 операндов, и далее распределение его через элементы ИЛИ асинхронные входы установки Б О регистров 14. -14 Доперандов (осуществляется выборочное обнуление регистров 14J 14g oпepaндoв), а также данный сигнал разрешает прохоксдение сигнала с i-ro выхода дешифратора 26 через группы элементов И 28, элементов ИЛИ 29, через элемент ИЛИ (это достигается монтажны1«1 сдвигсял подобно описанному выше) на вход установки в О регистра 42 кодов операций и далее распространение его через соответствующие элементы ИЛИ 41-41р на взсоды установки в 0 регистров 42--422 кодов операций (осуществляется выборочное обнуление регистров кодов операций 42,(-42 g ) , далее сигнал с выхода 4 через элемент 30 задержки разрешает прохождение сигнала с J

i-го выхода дешифратора 26 через группы элементов И 31, элементов ИЛИ 33 на вход синхронизации регистра 42- кодов операций (это дос-тигается монтажным сдвигом сигнгша с i-ro выхода дешифратора 26 на один разряд при прохождении через группу элементов И 31 на вход группы элементов ИЛИ 33), вызывая установку в регистре 42 кодов операций кода операции с входа 1 устройства.

Поступая на вход распределителя импульсов, сигнал 4/ блокирует прием служебных символов и вызывает формирование серии последовательных сигналов, поочередно запускающих .блоки 15j, где j - код, считываемый по этому сигналу с блока 34 стековой памяти в счетчик 25, После выдачи этих импульсов на выходе распределителя импульсов, формируется сигнал и разрешается прохождение последующих импульсов с входа 2 на выход синхронизации.

Одновременно сигнал с выхода вызывает считывание кода из вершины блока 34 стековой памяти и занесение его в счетчик 25 операндов, далее через элемент 13 задержки, элемент ИЛИ б разрешает прохождение сигнала с выхода дешифратора 26 через группы элементов И 7, элементов ИЛИ 9 на вход синхронизации регистра 14. операндов и одновременно на вход группы элементов И g, разрешая njjoхождение кода промежуточного результата с выхода блока 15, через групп элементов И 12 и элементов ИЛИ 10 , на информационные входы регистра 14, операндов. Далее (после завершения операций и записи результата) сигнал с выхода распределителя импульсов через элемент 19 задержки разрешает прохождение сигнала с i-ro выхода дешифратора 26 через группы элементов И 22 и элементов ИЛИ 23 через элемент ИЛИ 135+(это достигается монтажным сдвигом сигнала с i-ro выхода дешифратора 26 на один разряд .при прохождении, через группы элементов И 22 на вход группы элементов ИЛИ 23) на вход установки в О регистра 14. операндов и далее распространение его через элементы ИЛИ 13j-rl3 Ha входил установки в О регистров 14.-14g onepaHдов (осуществляется выборочное обну ление регистров 14 -14р 2 перандов), а также данный сипгал разрешает прохождение сигнала с i-ro выхода, деширатора 26 через группы элементов И 27 и элементов ИЛИ 29, элемент ИЛИ 41.| на вход установки в О регистра 42,- кедов операций и далее распространение его через элементы ИЛИ 41 -41g на входы устанойкй в О регистров кодов операций (осуществляется выборочное обн

ление регистров 42.-42„ кодов операций).

Сигнал с выхода 4д является символом семантической ошибки во входном выражении.

Работу устройства будем рассматривать по циклам. При этом под циклрм будем понимать последовательность действий, выполненных между последовательными приемами КОДОР служебных символов.

При приеме кодов служебных символов, вызывающих формирование сигналов на выходах 4,4 3- 4д цикл содер-, жит один такт (длительность такта рассчитана на длительность выполнения самой длинной операции). Если принятый служебный символ вызывает формирование сигнала на выходе 4„, под воздействием которого распределитель 2 импульсов блокирует прием кодов служебных символов на время выполнения операций двумя соседними блоками; то цикл содержит два такта.

Рассмотрим работу устройства на следующем примере.

Пусть на вход 1 устройства поступает элементарная запись

)))r

,)) .

Общим в процессе функционирования является то, что в начале каждого цикла на вход синхронизации регистров служебных символов поступает единичный сигнал с выхода -распределителя 2 импульсов, а на информационные входы данных регистров поступает код служебного символа, в результата чег в регистрах служебных символов осуществляется сдвиг кодов о код нового служебного символа заносится в- первы регистр. Далее формирователь управлящих сигналов формирует единичный сигнал на одном из своих выходов. При рассмотрении upKMeiia будем опускать этот начальный этап каждого цикла и начинать с момента появления единичного си1нала на одном из выходов формировател:я; управляющих сигналов.

Первый цикл. По сигналу с выхода 4 происходит обнуление счетчика операндов 25, реверсивного счетчика 37 и при.ем результата вычисления предыдущего вьфгикения в регистр 16 (это значение сохраняется в нем до момента получения результата данного выражения и прихода следующего); обнуление регистров операндов и ,регистров 4.2 -42 3 кодов операций.

Второй цикл. Формируется сигнал на выходе 4j, по которому внешними схемами (на фиг. 1 не показаны) фиксируется приемник результата вычисляемого выражения.

Третий-цикл. Посигналу с выхода 4 осуществляется прием в рзгистр 14 операнда Л, поступившего на вход 11

Четвертый цикл. По сигналу с выхода 4-, происходит прием в регистр 42 кодов операций кода операции +

Пятый цикл. По сигналу с выхода 48 производится запись в блок 34 стековой памяти кода состояния счетчика 25.

Шестой цикл. По сигналу с выхода 4ц. происходит увеличение состояния счетчика 25 на единицу; прием в регистр 142 операндов операнда Ну поступившего на вход 11.

Седьмой . По сигналу с выхода 4 происходит прием в регистр 422 кодов операций кода операции х.

Восьмой цикл. По сигналу с выхода 4 происходит увеличение состояния счетчика 25 на единицу, прием в регистр 14зоперандов операнда ТГ , поступившего на вход 11.

Девятый цикл. По сигналу с выхода 4 происходит запись в счетчик 25 кода из вершины блока 34 стековой памяти; вычисление и прием в регистр 14 операндов результата промежуточных вычислений о(.(о. 7F,-« )), пocлe выполнения, указанных операций выборочный сброс,, в О регистров 142-144. операндов, регистров 42.-42, кодов операций.

Десятый цикл. По сигналу с выхода 4 происходит прием в регистр 42-, кодов операций кода операции -V

Одиннадцатый цикл. По сигналу с выхода 4 происходит увеличение состояния счетчика 25 на единицу; прием в регистр 142 операндов операнда ц .

Двенадцатый цикл. По сигналу с выхода 4 происходит вычисление и прием в регистр 14 операндов результата проме5(суточных вычислений b (Ь cL - 4) выборочный сброс в О регист;ров операндов, регистр 42-j-42a кодов операций/ прием в регистр 42 кодов операций кода операции .

Тринадцатый цикл. По сигналу с выхода 4g происходит запись в блок 34 стековой памяти кода состояния счетчика 25.

Четырнадцатый и пятнадцатый циклы аналогичны циклу 13.

Шестнадцатый цикл. По сигналу с выхода 4л происходит увеличение состояния счетчика 25 на единицу; прием в регистр 14 операндов операнда %, поступившего на вход 11.

Семнадцатый цикл. По сигналу с выхода 4 происходит прием в регистр 42д кодов операций кода операции +.

Восемнадцатый цикл. По сигнгшу с выхода 44 происходит увеличение счетчика 25 на единицу; прием в регистр 14ц операндов операнда 7 , поступившего на вход 11.

Девятнадцатый цикл. По сигналу с выхода 4-, происходит вычисление и прием в регистр 14 операндов результата промежуточных вычислений с (с F); выборочный сброс в О регистра 14 операндов, регистра 42 кодов операций; прием в регистр 42зкодов операций кода

0 операции -.

Двадцатый цикл. По сигналу с еыхода 4 2 происходит прием в регистр 14 операндов операнда J, поступившего на вход 11.

5 Двадцать первый .цикл. По сигналу с выхода 42 происходит запись в счетчик 25 кода из вершины блока 34 стековой памяти, вычисление и прием в регистр 142 операндов результата промежуточных вычислений d(d ,);

выборочный сброс в О регистров 14j14, операндов регистров 422,42 кодов операций.

Двадцать второй цикл. По сигналу

с выхода 4-J происходит прием в регистр 422 операций кода операции х.

Двадцать третий цикл. По сигналу с выхода 4 происходит увеличение состояния счетчика 25 на единицу;

0 прием в регистр 14 операндов операнда }7g , поступившего на вход 11 данных.

Двадцать четвертый цикл. По сигналу с выхода 4 происходит вычис5 ленйе и прием в регистр 14 операндов резул ьтата промежуточных вычислений dxJ/g ; прием в регистр 14ц операндов операнда f прием в регистр 422 кодов операций кода опеQ рации х.

Двадцать пятый цикл. По сигналу . с выхода 4з происходит прием-в регистр 14 операндов операнда Jg, пог ступившего на вход 11.

Двадцать шестой цикл. По сигналу с выхода 4. ПРОИСХОДИТ вычисление и прием в регистр 14 операндов результата промежуточных вычислений 1(1 ot. Л9) выборочный сброс в О регистров 14з и 144. операндов регистров 422 3 кодов операций; прием в регистр 422 кодов

г гтЛ1 я11ггй wOTia лгт аг лттИ1Т - операций кода операции

По сигналу Двадцать седьмой цикл,

с выхода 4j происходит прием в регистр 14 з операндов операнда , поступившего на вход il. , Двадца1ть восьмой цикл. По сигналу с выхода 42 происходит запись

0 в счетчик 25 кода из вершины блока 34 стековой памяти, вычисление и прием в регистр 142 операндов результата промежуточных вычислений р(р 1 - Ж.д).; выборочный сброс в

5 О регистров 14} и 144 операндов регистров 42, я 42, кодов oneрзций. Двадцать девятый цикл. Пр сигналу с выхода 4 -, происходит прием в регистр 42 кодов операций кода операции х. Тридцатый цикл. Происходит запись в блок 34 стековой памяти кода состояния счетчика 25. Тридцать первый цикл. По сигналу с выхода 4ц. происходит увеличение состояния счетчика 25 на единицу; прием Б регистр 14 операндов операнд да Тридцать второй цикл. Происходит прием в регистр 42з кодов операций кода операции +. Тридцать третий цикл. По сигналу с выхода 4 происходит увеличение состояния счетчика 25 на единицу; прием в регистр 144 операндов операнда. Тридцать четвертый цикл. По сиipналу с выхода 4 происходит запись в счетчик 25 кода из вё ниины блока 34 стековой памяти, вычисление и прием в регистр 14 операндов резуль татов прОА4ежу очных вычислений -f (т i ;( ЗГ..+ Л; выборочный сброс в О регистров 14з и 14 операндов регистров; 42 операций. Тридцать пятый цикл. По сигналу с выхода 42 происходит запись в сче чик 25 кода из вершин влока 34 сте ковой памятиу вычисление и прием в регистр 142 операнда результата про межуточных вычиспеййй.(в данном слу чае перезапись пр(С 1ежуточного резул тата в регистр 14 i операндов ); вьй5о рочный сброс в О регистров 14з и 144 операндов регистров 42 и i ксщов операций. Тридцать шестой цикл. По сигналу с выхода 4 происходит, обнуление счетчика 25 операндов, реверсивного счётчика 37 и прием результата вычислений у( + С ) исходного выражения в выходной регистр 16} обнуление регистров 14 операций, регистров 42 -42зкодов операций. . Таким образсм, предлагаемое устройство для обработки языков программирования обладает способностью адаптации к виду выражений и их пошаговой интерпретации без преобразования к виду польской записи, что увеличивает скорость обработки. Синтаксический анализ каждого символа выражения с учетом предшествующих символов требует только одного цикла работы устройства, что способствует повьвиению скорости обработки выражений.- Псшаговая интерпретация выражений позволяет в процессе интерпретации проводить выполнение операций и накопление промежуточных результатов бесскобочных вьфажений. Структурные отображения скобочных вьражений устройстве) путем индивидугшьной последовательности настройки блоков 15 и шин передачи промежуточных результатов, наряду с вычислением подскобочных выражений, позволяет в одном цикле, соответствующем заксшвающейся скобке выражения,- свор ачивать одно подскобочное выражение, что повьшает скорость обработки скобочных выражений. Структурное отображение вьфажений (адаптация устройства к виду выражения осуществляется установлением соответствия между операциями и операндами подскобочных вьфажений с одной сторбны и блокаш 15, их регистрами кодов операций и регистрами операндов с другой сторбны, а также между выходами результатов регистраьш операндов ;(для передачи и хранения промежуточных результатов что уменьшает потери времени на вызов промежуточных результатов, используемых в качестве операндов.

ш J

to

//

ЗИ

12, J

f2c

t

f5

U

/I,

tSt

KS 16

17

/.

«

4ff

m

-J

Фиг I

Фиг.З

Авторы

Даты

1983-05-07—Публикация

1981-09-22—Подача