Изобретение относится к вычислительной технике, и может быть использовано в процессорах, в которых прИ меняются языки высокого уровня. Известен процессор, позволяющий вычислять арифметические выражения, представленные в польской записи, и содержащий регистр команд, блок режима работы, де1иифратор адреса и дешифратор кода операции, используемые для управления стековой памятью. С помсчдью этих блоков осуществляется загрузка операндов в стековую память и выполнение операций над ними в арифметическом устройстве ij. Недостаток этого процессора - низ кое быстродействие. Наиболее близким к предлагаемому является процессор, который предназначен для вычисления выражений, пред ставленных в инверсной польской записи . Процессор содержит оперативное запоминающее устройство, стек резуль татов, стек адресов операндов, регистр адреса, счетчик адреса стека результатов, счетчик операндов, ре-i гистр команд и два регистра арифмети ческого устройства. Командная информация состоит из слогов, содержащих коды операций и адреса операндов, уп кованных в непрерывную строку, поступающую на вход регистра команд. Адреса неиспользованных в данный момент операндов погружаются в стек адресов, а используемые операнды извлекаются из оперативного запоминающего устройства и пересылаются в регистры арифметического устройства. Промежуточные результаты сохраняются в стеке результатов 2. Недостатком известного процессора является низкое быстродействие, обусловленное последовательным характером обработки входной строки - подготовкой операндов и выполнением операций . Цель изобретения - повьхиение быстродействия процессора. Поставленная цель достигается тем, что в -процессор, содержавши накапливающий сумматор, блок стековой памяти результатов, .регистр команд и блок управления, причем выход регистра команд соединен с первым входом блока управления и входом кода операции наКапливающего сумматора, информационный вход накап ливающего сумматора подключен к выходу блока стековой памяти результатов, а выход накапливающего сумматора - к первому входу блока стековой памяти результатов, введены Спок стековой памяти операндов триггер операнда и триггер операции,пр этом первый вход блока стековой памя-ти операндов соединен с выходом регистра команд, а первый выход - с информационным входом накапливающего сумматора, управляющие вход и выход блока стековой памяти операндов подключены соответственно к первому выходу и второму входу блока управления, третий и четвертый входы кото рого соединены с выходами соответственно триггера операнда и триггера операции, второй, третий, четвертый и пятый выходы блока управления подключены соответственно к нулевому и единичному входам триггера операнда и нулевому и единичному входам триггера операции, шестой и седьмой выходы блока управления соединены соответственно с входами, разрешения приема и выдачи блока стеко,вой памяти результатов, восьмой и девятый вы ходы - соответственно с входами разрешения приема операнда и приема кода операции сумматора, десятый и одиннадцатый выходы - соответственно с входами разрегиения приема и выдачи информации блока стековой памяти операндов, а двенадцатый и тринадцатый выходы блока управления подключены соответственно к входам разрешения выдачи и сдвига информации регистра команд, причем вход управления суммированием процессора соединен с пятым входом блока управления, вход управления записью процессора подключен к шестому входу блока управления, четырнадца тыйи пятнадцатый выходц блока управления соединены соответственно с выходом разрешения вьщачи адреса про цессора и выходом разрешения выдачи информации процессора, а вход и выход -блока стековой памяти операндов являются информационными входом и выходом процессора. Кроме того, блок управления содержит триггер готовности сумматора триггер готовности памяти, счетный триггер, дешифратор признака записи элементы И, элементы ИЛИ, элементы НЕ и элемент И-НЕ при этом счетные входы триггеров готовности сумматора и готовности памяти и первый вход первого элемента И подключены к выходу генератора тактовых импульсов, первые входы триггера готовности сумм тора и триггера готовности памяти соединены соответственно с пятым и шестым входами бло,ка.а входы дешифратора при нака записи . с первым входом блока первый и второй входы элемента И-НЕ подключены соответственно к прямому выходу триггера готовности сумматора и первому выходу дешифратора признака записи, а выход этого элемента к второму входу первого элемента И, третий вход которого соединен с прямым выходом триггера готовности памяти, а выход - ,со счетным входом счетного триггера и первыми входами второго, третьего, шестого и седьмого элементов И, прямой выход счетного триггера подключен к в торому входу второго элемента И, а инверсный выход - к второму входу третьего элемента И и информационному входу счетного триггера, инверсный выход триггера готовности сумматора соединен с первыми входами четвертого и пятого элементов И, вторые входы которых подключены к первому выходу ешифратора признака записи, выход второго элемента И соединен с третьим входом пятого элемента И и вторыми ходами шестого и седьмого элементов И, выход третьего элемента И подклюен к третьему входу четвертого эле-, мента И и первым входам восьмого и девятого элементов И, второй выход дешифратора признака записи соединен с третьим входом шестого элемента И и вторым входом девятого элемента И, третий выход дешифратора признака записи подключен к третьему входу седьмого элемента И и второму входу восьмого элемента И, выход четвертого элемента И соединен с вторым вхо--, дом триггера готовности сумматора, первыми входами десятого, одиннадцатого и двенадцатого элементов И, с третьим, четвертым и двенадцатым выходами блока, выход пятого элемента И подключен к первым входам тринадцатого и четырнадцатого элементов И, четвертого элемента ИЛИ и восьмому выходу блока, вход первого элемента НЕ соединен с вторым входом блока и вторым входом десятого элемента И, а выход первого элемента НЕ - с вторым входом двенадцатого элемента И, вход второго элемента НЕ подключен к четвертому входу блока и вторым входам одиннадцатого и четырнадцатого элементов И, а выход второго элемента НЕ - к третьим входам десятого и двенадцатого элементов И и второму входу тринадцатого элемента И, выход десятого элемента И соединен с первыми входами первого и второго элементов ИЛИ, выход одиннадца того элемента И - с вторым входом первого элемента ИЛИ и первым входом . третьего элемента ИЛИ, выход двенадцатого элемента И - с третьим входом первого элемента ИЛИ и вторым входом третьего элемента ИЛИ, выход тринадцатого элемента И - с четвертьлм входом первого элемента ИЛИ и вторым входом второго элемента ИЛИ, выход четырнадцатого элемента И - с пятым входом первого элемента ИЛИ и третьим входом третьего элемента ИЛИ, выходы первого, второго, третьего и

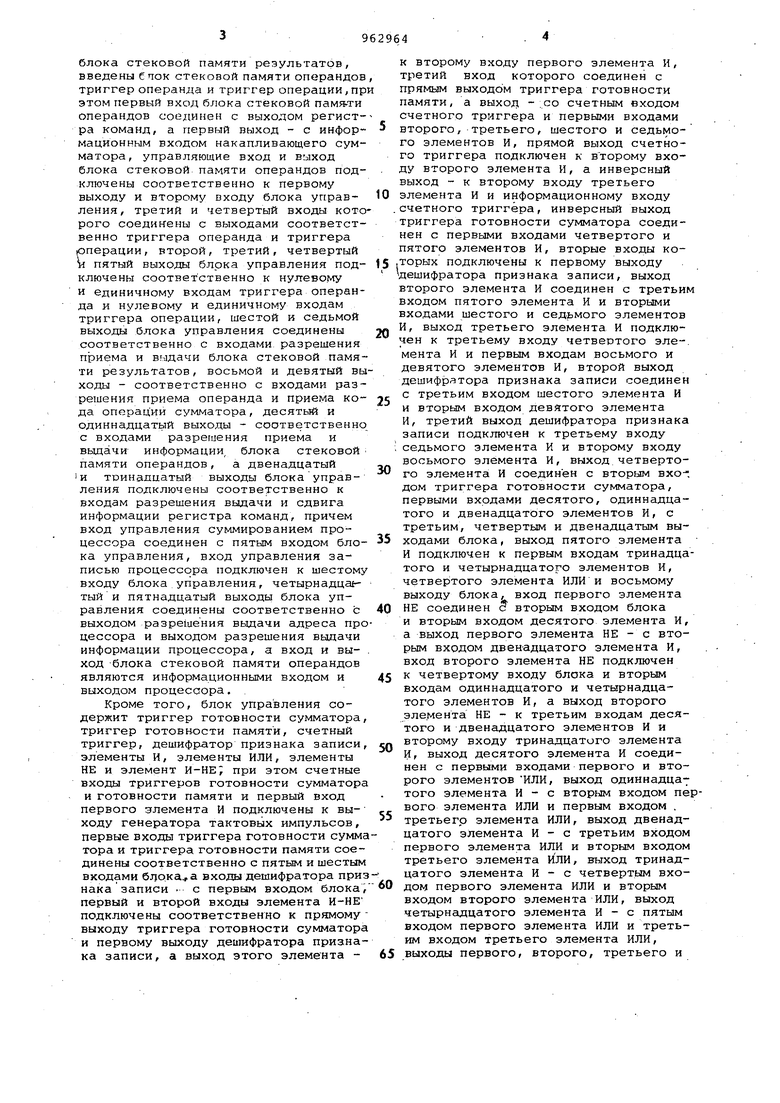

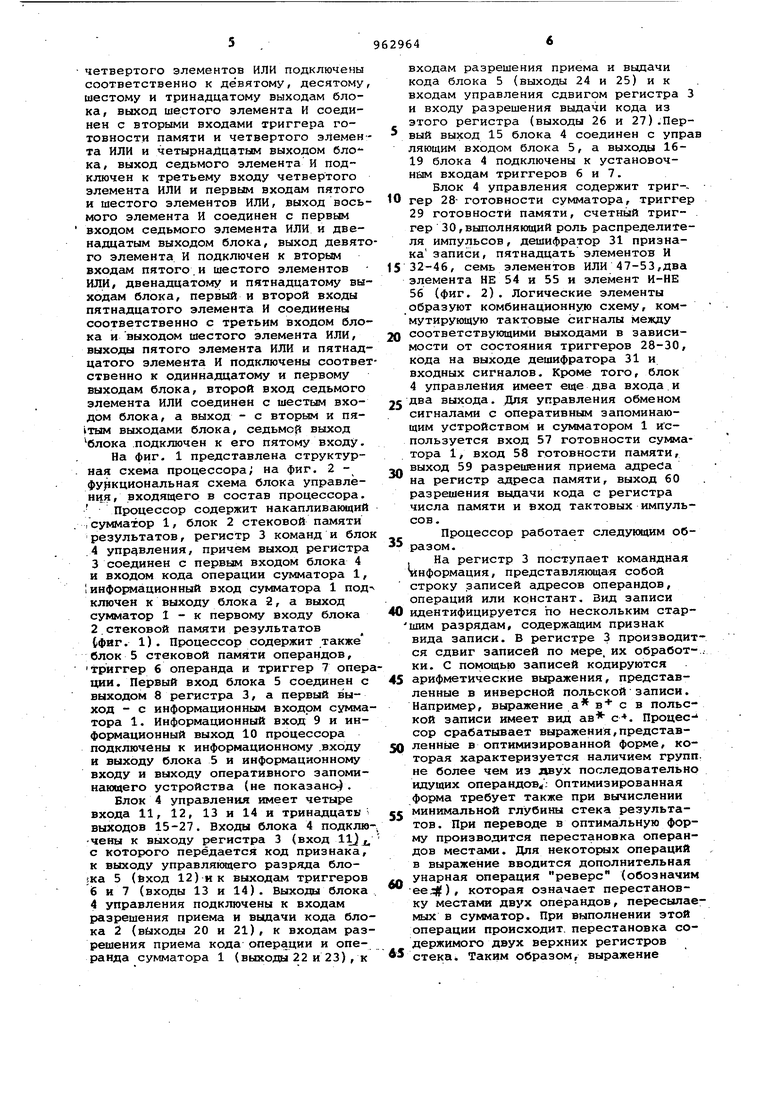

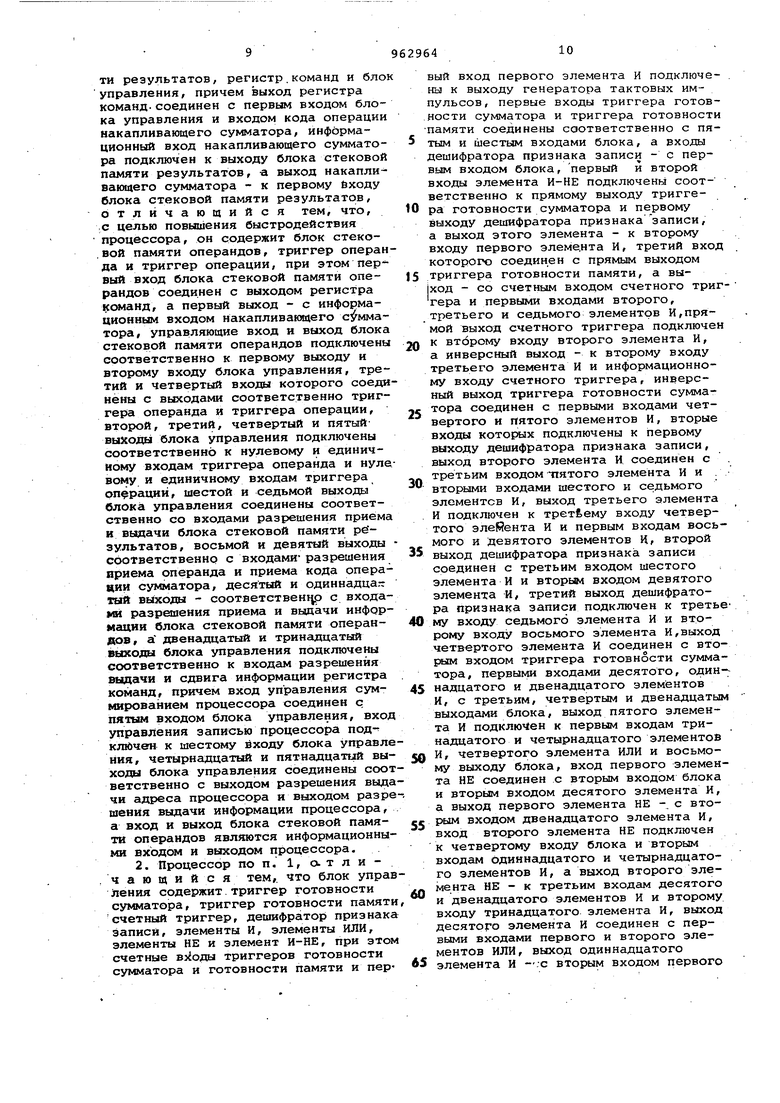

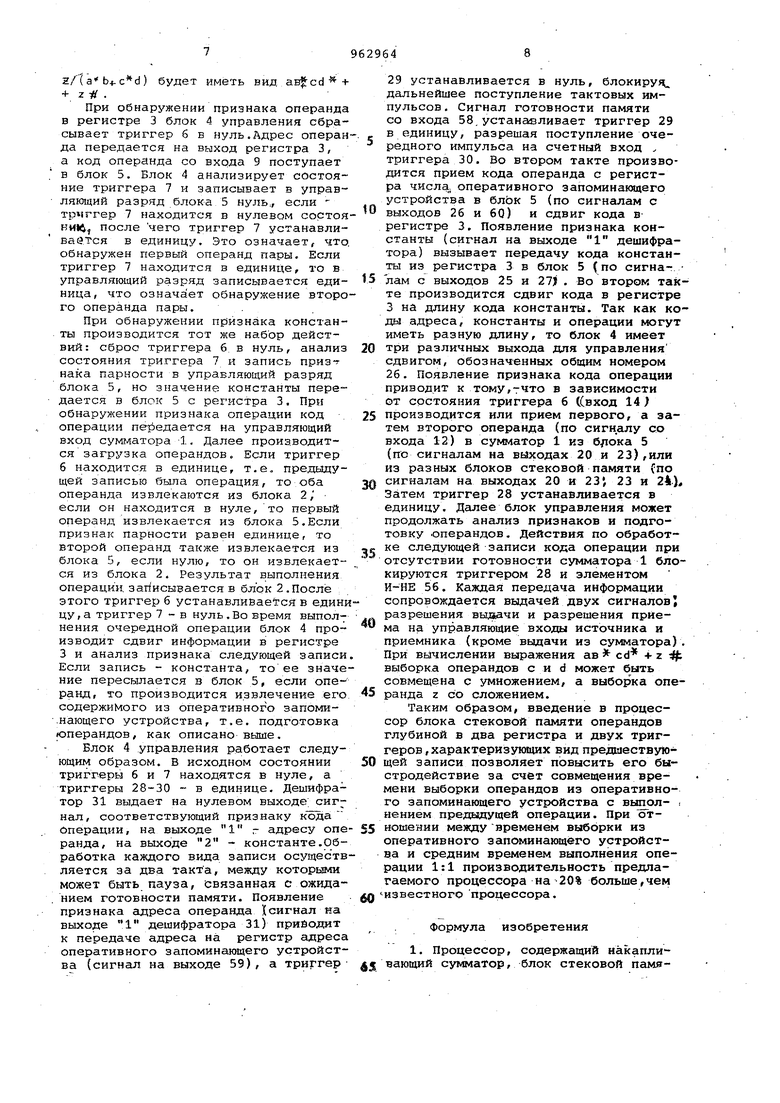

четвертого элементов ИЛИ подключены соответственно к девятому, десятому, шестому и тринадцатому выходам блока, выход шестого элемента И соединен с вторыми входами триггера готовности памяти и четвертого элемента ИЛИ и четырнадцатым выходом блока, выход седьмого элемента И подключен к третьему входу четвертого элемента ИЛИ и первым входам пятого и шестого элементов ИЛИ, выход восьмого элемента И соединен с первым входом седьмого элемента ИЛИ и двенадцатым выходом блока, выход девятого элемента И подключен к вторым входам пятого.и шестого элементов ИЛИ, двенадцатому и пятнадцатому выходам блока, первый и второй входы пятнадцатого элемента И соединены соответственно с третьим входом блока и выходом шестого элемента ИЛИ, выходы пятого элемента ИЛИ и пятнадцатого элемента И подключены соответственно к одиннадцатому и первому выходам блока, второй вход седьмого элемента ИЛИ соединен с шестым входом блока, а выход - с вторым и пятым выходами блока, седьмой выход блока подключен к его ПЯТОМУ входу. На фиг. 1 представлена структурная схема процессора; на фиг. 2 функциональная схема блока управления, входящего в состав процессора. Процессор содержит накапливающий сумматор 1, блок 2 стековой памяти результатов, регистр 3 команд и блок 4 управления, причем выход регистра 3 соединен с первым входом блока 4 и входом кода операции сумматора 1, информационный вход сумматора 1 под ключей к выходу блока 2, а выход сумматор 1 - к первому входу блока 2.стековой памяти результатов (фйг. 1). Процессор содержит также блок 5 стековой памяти операндов, триггер б операнда и триггер 7 операции. Первый вход блока 5 соединен с выходом 8 регистра 3, а первый выход - с информационным входом сумматора 1. Информационный вход 9 и информационный выход 10 процессора подключены к информационному .входу и выходу блока 5 и информационному входу и выходу оперативного запоминающего устрюйства (не показано) . Блок 4 управления имеет четыре входа 11, 12, 13 и 14 и тринадцати выходов 15-27. Входы блока 4 подклю-. чены к выходу регистра 3 (вход 11}j, с которого передается код признака, к выходу управляющего разряда блока 5 (йход 12) и к выходс1м триггеров 6 и 7 (входы 13 и 14). Выходы блока 4 управления подключены к входам разрешения приема и выдачи кода блока 2 ( 20 и 21), к входам разрешения приема кода операции и операнда сумматора 1 (выходы 22 и 23) , к

входам разращения приема и выдачи кода блока 5 (выходы 24 и 25) и к входам управления сдвигом регистра 3 и входу разрешения выдачи кода из этого регистра (выходы 26 и 27).Первый выход 15 блока 4 соединен с управ ляющим входом блока 5, а выходы 1619 блока 4 подключены к установочным входам триггеров 6 и 7.

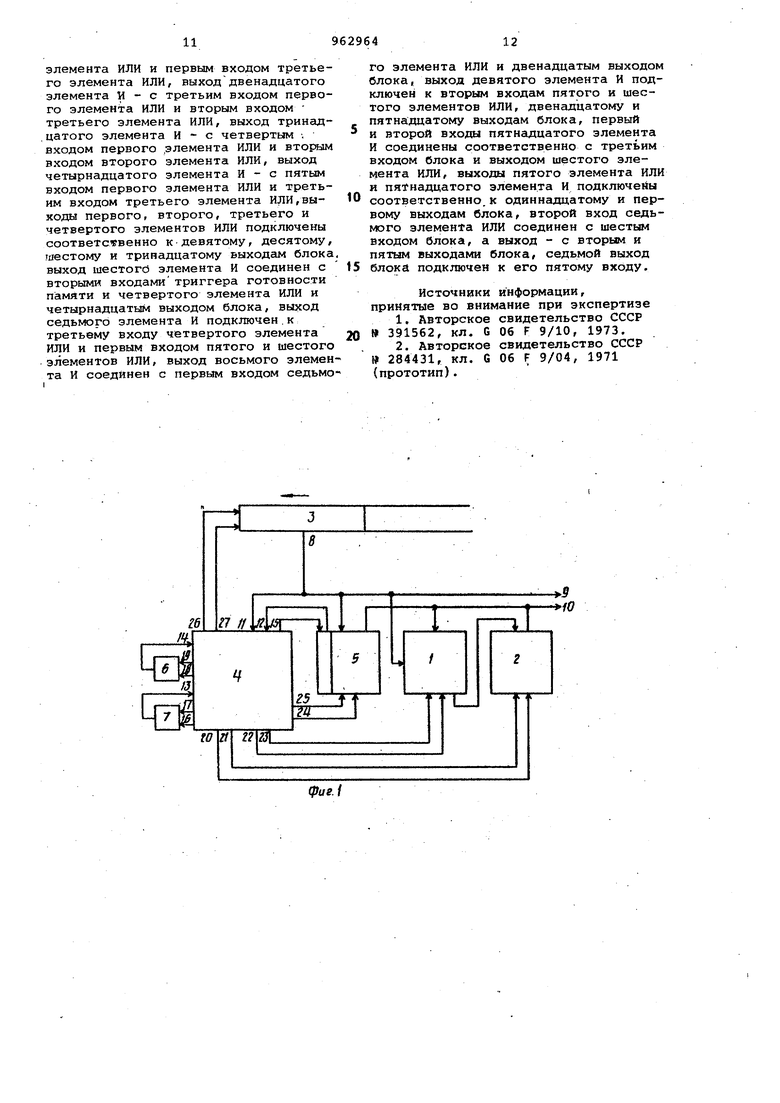

Блок 4 управления содержит триг-0 гер 28- готовности сумматора, триггер 29 готовности памяти, счетный триггер 30,выполняющий роль распределителя импульсов, дешифратор 31 признака записи, пятнадцать элементов И

5 32-46, семь элементов ИЛИ 47-53,два элемента НЕ 54 и 55 и элемент И-НЕ 56 (фиг. 2). Логические элементы образуют комбинационную схему, коммутирующую тактовые сигналы между

0 соответствующими выходами в зависимости от состояния триггеров 28-30, кода на выходе дешифратора 31 и входных сигналов. Кроме того, блок 4 управления имеет еще два входа и

5 два выхода. Для управления обменом сигналами с оперативным запоминающим устройством и сумматором 1 используется вход 57 готовности сумматора Ij вход 58 готовности памяти,

выход 59 разрешения приема адреса на регистр адреса памяти, выход 60 разрешения выдачи кода с регистра числа памяти и вход тактовых импульсов .

Процессор работает следующим образом.

. На регистр 3 поступает командная информация, представляющая собой строку записей адресов операндов, операций или констант. Вид записи

0 идентифицируется по нескольким стар шим разрядам, содержащим признак вида записи. В регистре 3 производится сдвиг записей по мере, их обработ- . ки. С помощью записей кодируются

5 арифметические выражения, представленные в инверсной польскойзаписи. Например, выражение а в с в польской записи имеет вид ав с-. Процес- сор срабатывает выражения,представленные в оптимизированной форме, которая характеризуется наличием групП: не более чем из двух последовательно идущих операндов ; Оптимизированная форма требует также при вычислении

е минимальной глубины стека результатов. При переводе в оптимальную форму производится перестановка операндов местами. Для некотора:1Х операций в выражение вводится дополнительная

д унарная операция реверс (обозначим ее;:), которая означает перестановку местами двух операндов, пересылаемых в сумматор. При выполнении этой операции происходит, перестановка содержимого двух верхних регистров

стека Таким образом, выражение

) будет иметь вид -f + zH .

При обнаружении признака операнда в регистре 3 блок 4 управления сбрасывает триггер 6 в нуль.Адрес операн-. да передается на выход регистра 3, а код операнда со входа 9 поступает в блок 5. Блок 4 анализирует состояние триггера 7 и записывает в управляющий разряд блока 5 нуль,, если триггер 7 находится в нулевом состояви1й, после чего триггер 7 устанавливается в единицу. Это означает, что. обнаружен первый операнд пары. Если триггер 7 находится в единице, то в управляющий разряд записывается единица, что означает обнаружение второго операнда пары.

При обнаружении признака константы производится тот же набор действий: сброс триггера 6, в нуль, анализ состояния триггера 7 и запись приз-г нака парности в управляющий разряд блока 5, но значение константы переается в блок 5 с регистра 3. При обнаружении признака операции код операции передается на управляющий вход сумматора -1. Далее производится загрузка операндов. Если триггер б находится в единице, т.е. предыдущей записью была операция, то оба операнда извлекаются из блока 2, если он находится в нуле,то первый операнд извлекается из блока 5.Если признак парности равен единице, то второй операнд также извлекается из блока 5, если нулю, то он извлекается из блока 2. Результат выполнения операции, зайисы ается в блок 2.После этого триггер б устанавливается в единицу, а триггер 7 - в нуль.Во время выпол нения очередной операции блок 4 производит сдвиг информации в регистре 3 и анализ признака следующей записи, Если запись - константа, то ее значение пересылается в блок 5, если операнд, то производится и.звлечение его содержимого из оперативного запоминающего устройства, т.е. подготовка перандов, как описано выше.

Блок 4 управления работает следующим образом. В исходном состоянии триггеры 6 и 7 находятся в нуле, а триггеры 28-30 - в единице. Дешифратор 31 выдает на нулевом выходе сиг нал, соответствующий признаку кода Операции, на выходе 1 г адресу операнда, на выходе 2 - константе.Обработка каждого вида записи осуществляется за два такта, между которыми может быть пауза, связанная с ожида нием готовности памяти. Появление признака адреса операнда Ксигнал на выходе 1 дешифратора 31) приводит к передаче адреса на регистр адреса оперативного запоминающего устройства (сигнал на выходе 59), а триггер

29 устанавливается в нуль, блoкиpy. дальнейшее поступление тактовых импульсов . Сигнал готовности памяти со входа 58.устанавливает триггер 29 в единицу, разрешая поступление очередного импульса на счетный вход . триггера 30. Во втором такте производится прием кода операнда с регистра числа оперативного запоминающего устройства в блок 5 (по сигналам с

o выходов 26 и 6Q) и сдвиг кода врегистре 3. Появление признака константы (сигнал на выходе 1 дешифратора) вызывает передачу кода константы из регистра 3 в блок 5 (по сигна-

S лам с выходов 25 и 27J . Во втором такте производится сдвиг кода в регистре 3 на длину кода константы. Так как коды адреса, константы и операции могут иметь разную длину, то блок 4 имеет

0 три различных выхода для управления сдвигом, обозначенных общим номером 26. Появление признака кода операции приводит к тому,-что в зависимости от состояния триггера б ((вход 14)

5 производится или прием первого, а затем второго операнда (по сигналу со входа 12) в сумматор 1 из б/юка 5 (по сигналам на выходах 20 и 23),или из разных блоков стековой памяти (по

0 сигналам на выходах 20 и 23, 23 и 24Ь Затем триггер 28 устанавливается в единицу. Дсшее блок управления может продолжать анализ признаков и подготовку операндов. Действия по обработке следующей записи кода операции при отсутствии готовности сумматора 1 блокируются триггером 28 и элементом И-НЕ 56. Каждая передача информации сопровождается выдачей двух сигналов разрешения выдачи и разрешения прИе® ма на управляющие входы источника и приемника (кроме выдачи из сумматора). При вьзчислении выражения ав cd 2 выборка операндов с и d может быть совмещена с умножением, а выборка операнда z со сложением.

Таким образом, введение в процессор блока стековой памяти операндов глубиной в два регистра и двух триггеров, характеризующих вид предшествующей записи позволяет повысить его быстродействие за счет совмещения времени выборки операндов из оперативного запоминающего устройства с вьшрл- . нением предевдущей операции. При отношении между временем выборки из оперативного запоминающего устройства и средним временем выполнения операции 1:1 производительность предлагаемого процессора на 20% больше,чем

известного процессора.

Формула изобретения

1. Процессор, содержащий накапливающий сумматор, блок стековой памяти результатов, регистр.команд и бло управления, причем выход регистра команд.соединен с первым входом блока управления и входом кода операции накапливающего сумматора, информационный вход накапливающего сумматора подключен к выходу блока стековой памяти результатов, а выход накапливающего сумматора - к первому бходу блока стековой памяти результатов, отличающийся тем, что, ;с целью повышения быстродействия процессора, он содержит блок стеко.вой памяти операндов, триггер операн да и триггер операции, при этом первый вход блока стековой памяти oneрандов соединен с выходом регистра команд, а первый выход - с информационным входом накапливающего с мматора, управляющие вход и выход блока стековой памяти операндов подключены соответственно к первому выходу и второму входу блока управления, третий и четвертый входы которого соеди нены с выходами соответственно триггера операнда и триггера операции, второй, третий, четвертый и пятый выходы блока управления подключены соответственно к нулевому и единичному входам триггера операнда и нуле вому и единичному входам триггера операций, шестой и седьмой выходы блока управления соединены соответственно со входами разрешения приема и выдачи блока стековой памяти результатов, восьмой и девятый выходы соответственно с входами- разрешения приема операнда и приема кода операции сумматора, десятый и одиннадца.т дай выходы - соответствен1р с входами разрешения приема и выдачи информации блока стековой памяти операндов, а двенадцатый и тринадцатый выходы блока управления подключены соответственно к входам разрешения вьщачи и сдвига информации регистра команд, причем вход управления суммированием процессора соединен с пятым входом блока управления, вход управления записью процессора подкличей к шестому входу блока управле ния, четырнадцатый и пятнгщцатый выходы блока управления соединены соот ветственно с выходом разрешения выда чи адреса процессора и выходом разре шения выдачи информации процессора, а вход и выход блока стековой памяти операндов являются информационными входом и выходом процессора. 2. Процессор поп, l,o.тлич а ю щ и и с я тем,, что блок управ ления содержит триггер готовности сумматора, триггер готовности памяти счетный триггер, дешифратор признака записи, элементы И, элементы ИЛИ, элементы НЕ и элемент И-НЕ, при этом счетные триггеров готовности сумматора и готовности памяти и пер вый вход первого элемента И подключены к выходу генератора тактовых импульсов, первые входы триггера готовности сумматора и триггера готовности памяти соединены соответственно с пятым и шестым входами блока, а входы дешифратора признака записи - с первьам входом блока, первый и второй входы элемента И-НЕ подключены соответственно к прямому выходу триггера готовности сумматора и первому выходу дешифратора признака записи, а выход этого элемента - к второму входу первого элеме.нта И, третий вход которого соединен с прямым выходом триггера готовности памяти, а вы|ход - со счетным входом счетного триггера и первыми входами второго, третьего и седьмого элементов И,прямой выход счетного триггера подключен к второму входу второго элемента И, а инверсный выход - к второму входу третьего элемента И и информационному входу счетного триггера, инверсный выход триггера готовности сумматора соединен с первыми входами четвертого и пятого элементов И, вторые входы которых подключены к первому выходу дешифратора признака записи, выход второго элемента И соединен с третьим входом пятого элемента И и . вторыми входами шестого и седьмого элементов И, выход третьего элемента И подключен к третьему входу четвертого элеЙента И и первым входам восьмого и девятого элементов К, второй выход дешифратора признака записи соединен с третьим входом шестого элемента И и вторым входом девятого элемента И, третий выход дешифратора признака записи подключен к третье му входу седьмого элемента И и второму входу восьмого элемента И,выход четвертого элемента И соединен с вторьпл входом триггера готовности сумматора, первыми входами десятого, одиннадцатого и двенадцатого элементов И, с третьим, четвертым и двенадцатым выходами блока, выход пятого элемента И подключен к первым входам тринадцатого и четырнадцатого элементов И, четвертого элемента ИЛИ и восьмому выходу блока, вход первого элемента НЕ соединен с вторым входом блока и вторым входом десятого элемента И, а выход первого элемента НЕ -, с вторым входом двенсшцатого элемента И, вход второго элемента НЕ подключен к четвертому входу блока и вторым входам одиннадцатого и четырнадцатого элементов И, а выход второго элемента НЕ - к третьим входам десятого и двенадцатого элементов И и второму входу тринадцатого элемента И, выход десятого элемента и соединен с первыми входами первого и второго элементов ИЛИ, выход одиннадцатого элемента И --.-с вторым входом первого элемента ИЛИ и первым входом третьего элемента ИЛИ, выходдвенадцатого элемента И - с третьим входом первого элемента ИЛИ и вторым входом третьего элемента ИЛИ, выход тринадцатого элемента И - с четвертым . входом первого .элемента ИЛИ и вторим входом второго элемента ИЛИ, выход четырнадцатого элемента И - с пятым входом первого элемента ИЛИ и третьим входом третьего элемента ИЛИ,выходы первого, второго, третьего и четвертого элементов ИЛИ подключены соответственно к девятому, десятому, шестому и тринадцатому выходам блока выход mecTord элемента И соединен с вторыми входами триггера готовности памяти и четвертого элемента ИЛИ и четырнадцатым выходом блока, выход седыжэго элемента И подключен.к третьему входу четвертого элемента ИЛИ и первым входом пятого и шестого элементов ИЛИ, выход восьмого элемен та И соединен с первым входом седьмо го элемента ИЛИ и двенадцатым выходом блока, выход девятого элемента И подключен к вторым входам пятого и шестого элементов ИЛИ, двенадцатому и пятнадцатому выходам блока, первый и второй входы пятнадцатого элемента И соединены соответственно с третьим входом блока и выходом шестого элемента ИЛИ, выходы пятого элемента ИЛИ и пятнадцатого элемента И подключены соответственно.к одиннадцатому и первому выходам блока, второй вход седьмого элемента ИЛИ соединен с шестым входом блока, а выход - с вторым и пятым выходами блока, седьмой выход блока подключен к его пятому входу. Источники информации, примятые во внимание при экспертизе 1.Авторское свидетельство СССР 391562, кл. G Об F 9/10, 1973. 2.Авторское свидетельство СССР 284431, кл. G 06 F 9/04, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для интерпретации выражений языков программирования | 1982 |

|

SU1078432A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Процессор быстрых дискретных преобразований | 1989 |

|

SU1725227A1 |

/f

фиг.

Авторы

Даты

1982-09-30—Публикация

1981-01-04—Подача