Изобретение относится к автоматике и вычислительной технике и может быть использовано для синхронизации по циклам устройств, принимающих информацию от различных датчиков, ЦВЭМ,; синтезаторов речи и многоканальной связи.

Цель изобретения - повышение помехоустойчивости.

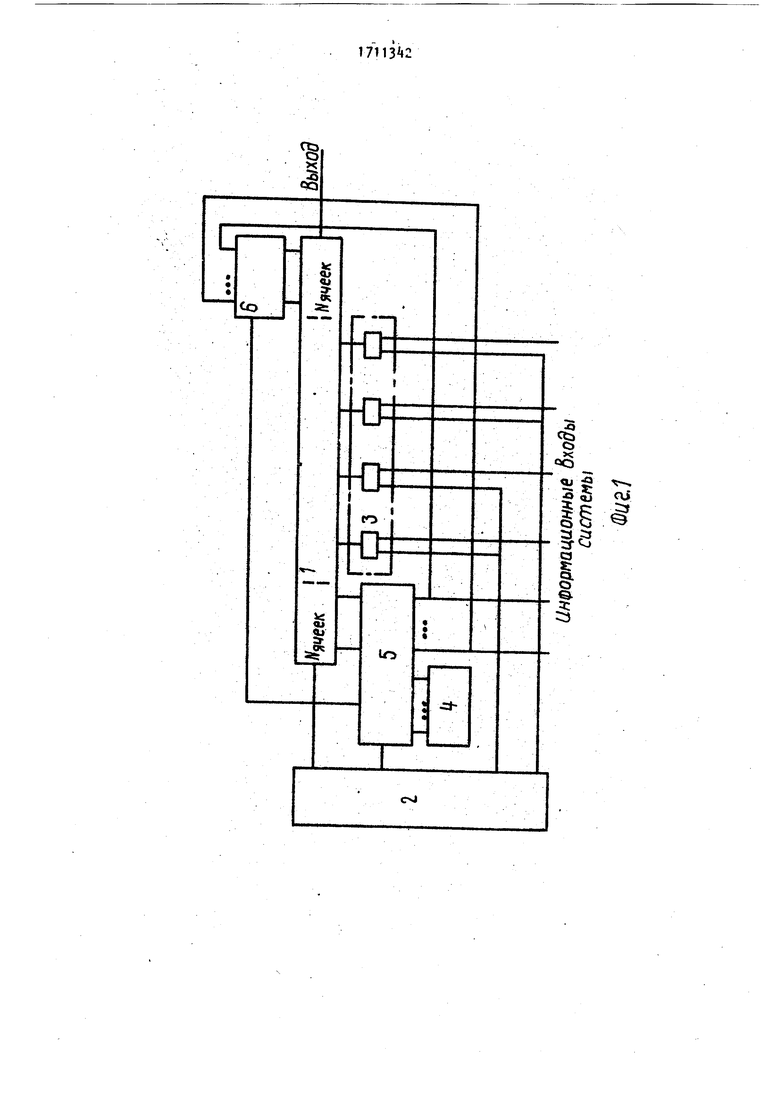

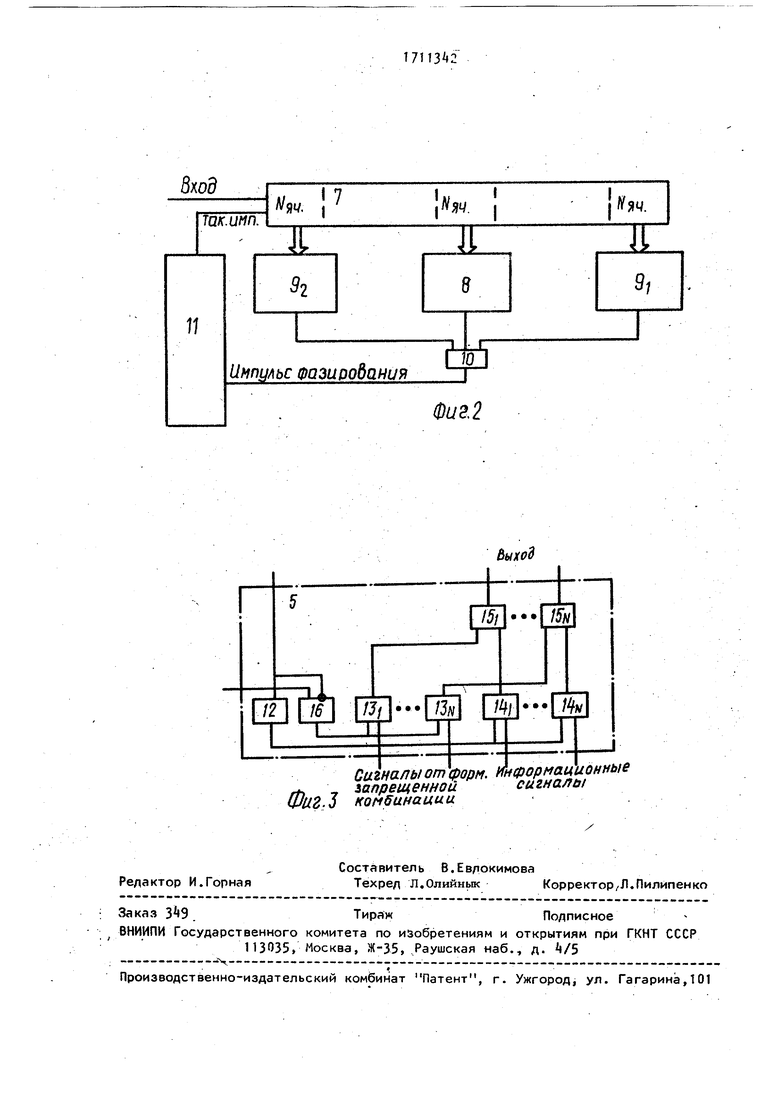

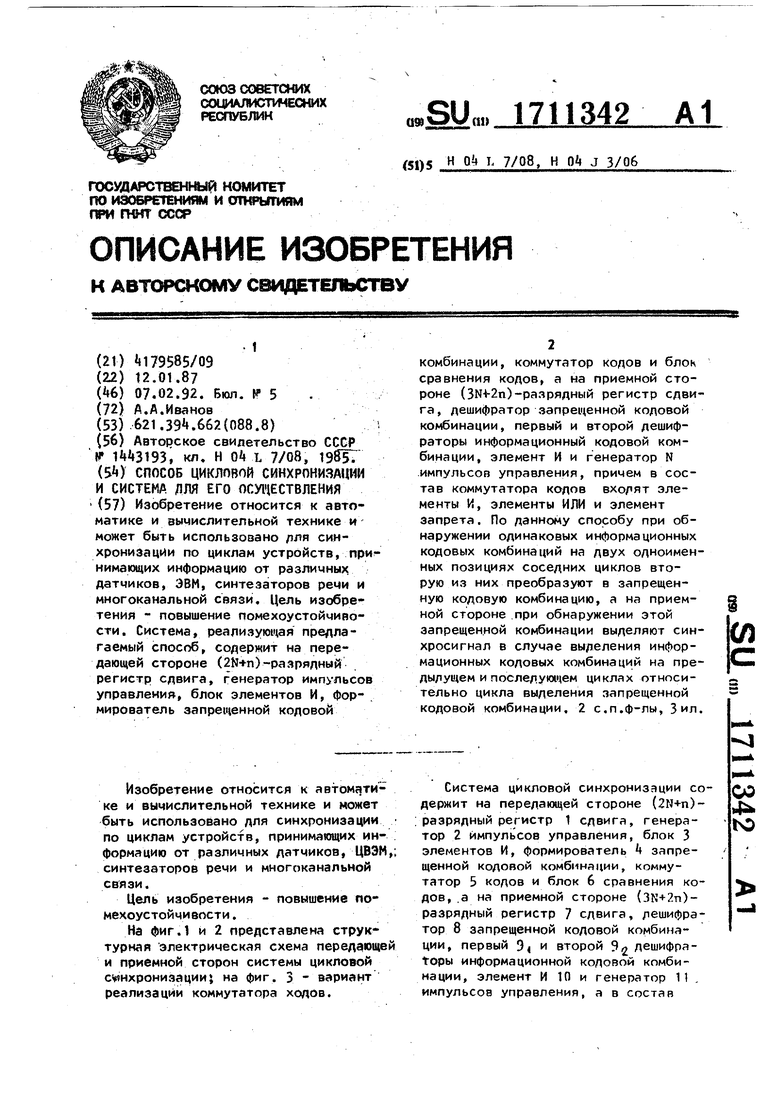

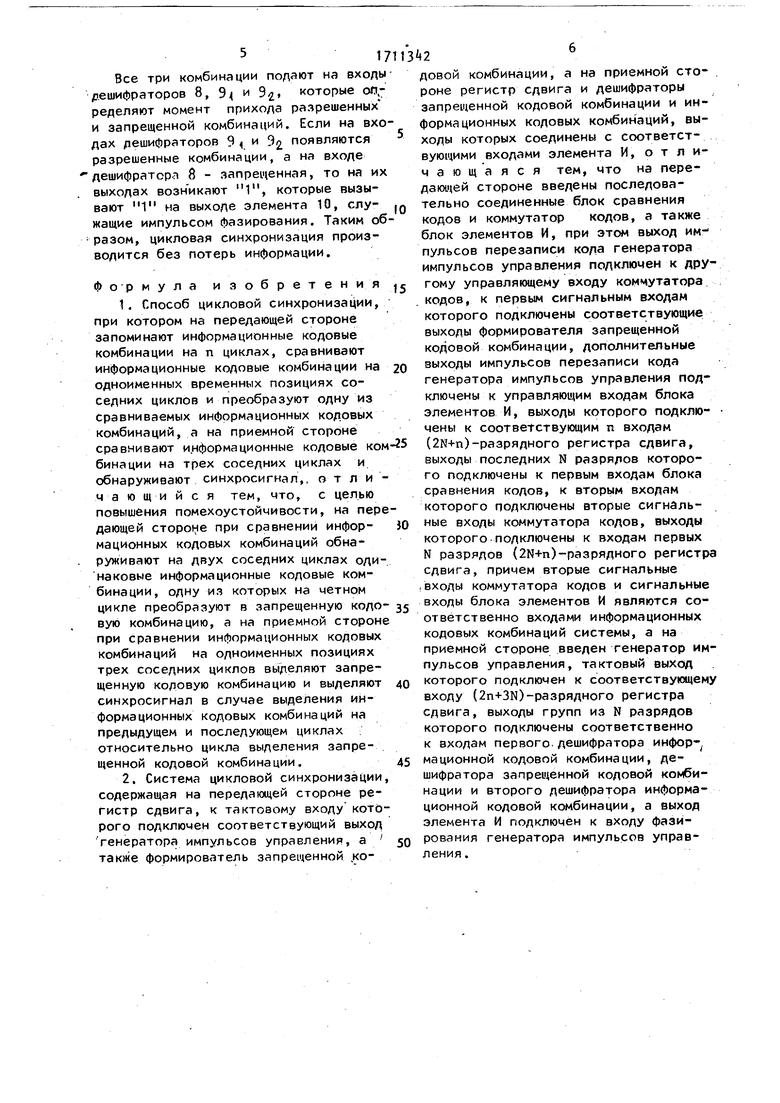

На фиг.1 и 2 представлена структурная электрическая схема передающей и приемной сторон системы цикловой синхронизации; на фиг. 3 - вариант реализации коммутатора ходов.

Система цикловой синхронизации содержит на передающей стороне (2N+n)- ; разрядный регистр 1 сдвига, генератор 2 импульсов управления, блок 3 элементов И, формирователь 4 запрещенной кодовой комбинации, коммутатор 5 кодов и блок 6 сравнения кодов, .а на приемной стороне (3N+2n)- разрядный регистр 7 сдвига, дешифратор 8 запрещенной кодовой комбинации, первый 9t и второй Э% дешифраторы информационной кодовой комбинации, элемент И 10 и генератор 11 импульсов управления, а в состав

со

4

к

коммутатора 5 кодов входят элементы И 12, 13| - 13 N , элементы ИЛИ Т5{-15м и элемент 16 запрета.

Сущность способа заключается в следующем.

На перелающей стороне формируют запрещенную кодовую комбинацию, запоминают информационную кодовую кобинацию, сравнивают две последовательно пришедшие информационные кодовые комбинации на заданных одноименных позициях соседних циклов, при их равенстве вторую информационную кодовую комбинацию преобразуют в запрещенную кодовую комбинацию, а на приемной стороне фиксируют момент приема запрещенной кодовой комбинации путем определения моментов приема запрещенной кодовой комбинации и двух информационных кодовых комбинаций, принятых до И после запрещенной кодовой комбинации на тех же временных позициях на предыдущем и последующем циклах относительно цикла выделения запрещенной кодовой комбинации.

Система цикловой синхронизации работает следующим образом.

Работа системы основана на использовании избыточности информационного сигнала двух видов: число уровней квантования сигнала менее двух и есть возможность из остальных уровней сформировать запрещенную кодовую комбинацию; возможны случаи повторения сигнала одного уровня на двух соседних циклах.

Если на передающей стороне определить моменты появления одинаковых величин сигнала на соседних отсчетах то достаточно передать величину только первого отсчета, а второй отсчет преобразовать в запрещенный сигнал (кодовую комбинацию) по этому сигналу в сочетании с разрешенными, причем величину предыдущего отсчета- записать в память и оставить это значение до момента прихода запрещенной кодовой комбинации, исключив тем самым потерю информации.

На информационные входы регистра 1 сдвига через блок 3 элементов И по дают информационные сигналы каналов, последовательность подключения ,которых определяют последователь- ностью импульсов перезаписи кода, поступающей на управляющие входы блока 3 элементов И с выходов гене0

5

0

5

0

5

0

5

0

5

ратора 2. Исключением является импульс перезаписи кода канала, используемого для передачи синхронизации. Этот импульс подают на управляющий вход коммутатора 5, с помощью которого производят запись в первые ячейки регистра 1 сдвига через коммутатор 5 либо информационного сигнала (при 1 на другом управляющем входе), либо запрещенной кодовой комбинации (при О на другом управляющем входе).

Если комбинации выбранного канала и снимаемая с последних ячеек регистра 1 сдвига различны, то на выходе блока 6 сравнения, устанавливается 1, позволяющая переписать входную кодовую комбинацию через коммутатор 5 в первые ячейки регистра 1 сдвига. Через цикл эта комбинация записывается в последние ячейки регистра 1 сдвига. Если в это время на входе на передающей стороне появляется такая же комбинация, то при равенстве комбинаций на выходе блока 6 сравнения кодов появляется О, который переключает выходы коммутатора 5 на запрещенную комбинацию, снимаемую с формирователя k, которая вписывается в первые ячейки регистра 1 сдвига.

Через цикл запрещенная комбинация появляется на последних ячейках регистра 1 сдвига. Так как на первые входы блока 6 сравнения всегда поступает разрешенная комбинация, то на его выходе появляется 1, которая коммутирует на вход регистра 1 сдвига информационную комбинацию независимо от того, одинакова она с предыдущей или нет. Если через цикл появляется следующая комбинация, отличная от предыдущей, то она вписывается в регистр 1 сдвига, если она одинакова с ней, то вновь вписывается запрещенная комбинация. Таким образом на входе регистра 1 сдвига появляется запрещенная комбинация только если величина отсчета повторяется, но появление двух запрещенных комбинаций подряд исключено, т.е. до и после запрещенной комбинации должны быть обязательно любые разрешенные.

На приемной стороне необходимо опознать момент появления запрещенной кодовой комбинации. С этой целью в регистре 7 сдвига запоминают три комбинации, прошедшие последовательно через цикл.

51

Все три комбинации подают на вхолы дешифраторов 8, 9 и 9, которые определяют момент прихода разрешенных и запрещенной комбинаций. Если на входах дешифраторов Я и 9Ј появляются разрешенные комбинации, а на входе

дешифратора 8 - запрещенная, то на их выходах возникают 1, которые вызывают 1 на выходе элемента 10, слу- жащие импульсом фазирования. Таким об;разом, цикловая синхронизация производится без потерь информации.

Ф о р мула изобретен и я

1.Способ цикловой синхронизации, при котором на передающей стороне запоминают информационные кодовые комбинации на п циклах, сравнивают информационные кодовые комбинации на одноименных временных позициях соседних циклов и преобразуют одну из сравниваемых информационных кодовых комбинаций, а на приемной стороне сравнивают информационные кодовые ком бинации на трех соседних циклах и обнаруживают синхросигнал,, о т л и ч а ю щи и с я тем, что, с целью повышения помехоустойчивости, на передающей стороне при сравнений инфор- мационных кодовых комбинаций обнаруживают на двух соседних циклах одинаковые информационные кодовые комбинации, одну из которых на четном цикле преобразуют в запрещенную кодо- вую комбинацию, а на приемной стороне при сравнении информационных кодовых комбинаций на одноименных позициях трех соседних циклов выделяют запрещенную кодовую комбинацию и выделяют синхросигнал в случае выделения информационных кодовых комбинаций на предыдущем и последующем циклах : относительно цикла выделения запре- . щенной кодовой комбинации.

2.Система цикловой синхронизации, содержащая на передающей стороне регистр сдвига, к тактовому входу которого подключен соответствующий выход генератора импульсов управления, а также формирователь запрещенной ,коЬ2b

довой комбинации, а на приемной стороне регистр сдвига и дешифраторы запрещенной кодовой комбинации и информационных кодовых комбинаций, выходы которых соединены с соответствующими входами элемента И, отличающаяся тем, что на передающей стороне введены последовательно соединенные блок сравнения кодов и коммутатор кодов, а также блок элементов И, при этом выход им-1 пульсов перезаписи кода генератора импульсов управления подключен к другому управляющему входу коммутатора кодов, к первым сигнальным входам которого подключены соответствующие выходы формирователя запрещенной кодовой комбинации, дополнительные выходы импульсов перезаписи кода генератора импульсов управления подключены к управляющим входам блока элементов И, выходы которого подклю- чены к соответствующим и входам (2N+n)-разрядного регистра сдвига, выходы последних N разрядов которого подключены к первым входам блока сравнения кодов, к вторым входам которого подключены вторые сигнальные входы коммутатора кодов, выходы которого подключены к входам первых N разрядов (2Ы+п)-разрядного регистра сдвига, причем вторые сигнальные .входы коммутатора кодов и сигнальные входы блока элементов И являются соответственно входами информационных кодовых комбинаций системы, а на приемной стороне введен генератор импульсов управления, тактовый выход которого подключен к соответствующему входу (2n+3N)-разрядного регистра сдвига, выходы групп из N разрядов которого подключены соответственно к входам первого.дешифратора информационной кодовой комбинации, дешифратора запрещенной кодовой комбинации и второго дешифратора информационной кодовой комбинации, а выход элемента И подключен к входу фазирования генератора импульсов управления.

%ее/с

t i

i N ячеек

Выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ передачи и приема цифровой информации и устройство для его осуществления | 1988 |

|

SU1534481A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1287296A1 |

| Устройство синхронизации по циклам | 1983 |

|

SU1172053A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Способ цикловой синхронизации с динамической адресацией получателя | 2016 |

|

RU2621181C1 |

| Способ цикловой синхронизации | 1975 |

|

SU664304A1 |

| Устройство для передачи и приема самосинхронизирующихся кодограмм | 1986 |

|

SU1403379A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для синхронизации по циклам устройств, приг- нимеющих информацию от различных датчиков, ЭВМ, синтезаторов речи и многоканальной связи. Цель изобретения - повышение помехоустойчивости. Система, реализующая предлагаемый способ, содержит на передающей стороне (2N+n)-разрядный регистр сдвига, генератор импульсов управления, блок элементов И, формирователь запрещенной кодовой комбинации, коммутатор кодов и блок сравнения кодов, а на приемной стороне (3Nf2n)-разрядный регистр сдвига, дешифратор запрещенной кодовой комбинации, первый и второй дешифраторы информационный кодовой комбинации, элемент И и генератор N импульсов управления, причем в состав коммутатора кодов входят элементы И, элементы ИЛИ и элемент запрета. По данному способу при обнаружении одинаковых информационных кодовых комбинаций на двух одноименных позициях соседних циклов вторую из них преобразуют в запрещенную кодовую комбинацию, а на приемной стороне при обнаружении этой запрещенной комбинации выделяют синхросигнал в случае выделения информационных кодовых комбинаций на предыдущем и последующем циклах относительно цикла выделения запрещенной кодовой комбинации. 2 с.п.ф-лы, Зил. Л С

KZI

информационные 8ходы системы

Que.1

| Авторское свидетельство СССР , кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-02-07—Публикация

1987-01-12—Подача