довательно соединенные первый блок ключей, первый регистр сдвига, второй блок ключей, второй регистр сдвига и дешифратор, последовательно соединенные первый элемент И, элемент ИЖ и счетчик, последовательно соединенные первый элемент НЕ и -второй элемент И, а также третий регистр сдвига, первьй и второй элементы запрета, второй и третий элементы НЕ и третий элемент И, причем тактовый вход третьего регистра сдвига подключен к объединенным первым входам первого элемента И и первого элемента запрета и второму входу второго элемента И, выходы первых М разрядов третьего регистра сдвига подсоедииены соответственно к М информационным входам первого блока ключей,вы ход (М+1)-го разряда третьего регистра сдвига подсоединен к входу второго элемента НЕ и к второму входу первого элемента И, выход (2М+1)-го разряда третьего регистра сдвига подсоединен к входу первого элемента НЕ и к третьему входу первого элемента И, вход третьего элемента

НЕ и четвертьй вход первого элемента И подключены к выходу первого разряда третьего регистра сдвига, выходы второго и третьего элементов НЕ подсоединены соответственно к второму и третьему входам второго элемента И, выход которого подсоединен к другому входу элемента ИЛИ, второй вХод и выход первого элемента запрета подключены соответственно к выходу элемента ИЖ и входу Сброс счетчика, выход которого подсоединен к управляющему входу первого блока ключей, управляющие входы nepiBoro регистра сдвига и второго блока ключей подключены соответственно к выходам третьего элемента И и второго элемента запрета,при этом объединенные первые входы и объединенные вторые входы третьего элемента И и второго элемента запрета являются соответственно первым и вторым управляющими входами анализатора,тактовый и информационный входы третьего регистра сдвига являются соответственно тактовым и инфорЬ1ационным входами анализатора,а выходы дешифратора являются выходами анализатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1982 |

|

SU1184105A1 |

| Устройство для сбора и передачи информации о подвижных объектах | 1988 |

|

SU1543432A1 |

| Устройство приема и передачи дискретных сигналов | 1979 |

|

SU856031A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство для формирования имитостойких последовательностей сигналов сложной формы | 1984 |

|

SU1203533A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство для регистрации телеграфных посылок | 1983 |

|

SU1234977A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство групповой тактовой синхронизации (его варианты) | 1982 |

|

SU1096760A1 |

1. УСТРОЙСТВО СИНХРОНИЗАЦИИ ПО ЦИКЛАМ, содержащее последовательно соединенные анализатор кода и первый элемент И, последовательно соединенные первьм делитель частоты, первый элемент запрета и первый счетчик, последовательно соединенные второй элемент И, второй, делитель частбты, второй элемент запрета и второй счетчик, последовательно соединенные генератор тактовых импульсов и распределитель, причем выход генератора тактовых импульсов подсоединен к тактовым входам первого и второго делителей частоты,а информационный вход анализатора кода является входом устройства, о т л ич. а ю щ е е с я тем,что с целью уменьшения времени вхождения в синхронизм в него введены анализатор служебной посыпки,первый и второй триггеры,первый и второй дополнительные элементы И и элемент ИЛИ,при этом выход анализатора кода подсоединен к первому управляющему входу анализатора служебной посылки, к объединенным первым входам второго элемента И и первого и второго дополнительных элементов И и к объединенным запрещающим входам первого и второго элементов запрета, тактовый и второй управляющий входы анализатора служебной посыпки подключены соответственно к выходам генератора тактовых импульсов и распределителя, а информационный вход анализатора служебной посьшки под- ключей к информационному входу анализатора кода, выход анализатора служебной посыпки подсоединен к объединенным установочным входам распределителя, анализатора кода и первого и второго делителей частоты, выход первого делителя частоты под-, соединен к второму входу первого дополнительного элемента И, выход которого через первый счетчик и эле& мент ИЛИ подсоединен к разрешающему (Л С входу распределителя, выход второго делителя частоты подсоединен к второму входу второго дополнительного элемента И,выход которого через второй счетчик подсоединен к другому входу элемента ИЛИ, выходы первого и второго элементов запрета подсоединены соответственно к входам Установка 1 первого и второго триггеров, входы Установка О которых подключены соответственно к дополнительным выходам первого и второго делителей частоты, прямые выходы первого и второго триггеров подсоединены соответственно к вторым входам первого и второго элементов И, инверсный выход первого триггера подсоединен к ; третьему входу второго элемента И, а выход первого элемента И подсоединен к разрешающему входу первого делителя частоты. 2. Устройство по п. 1, отличающееся тем, что анализатор служебной посылки содержит после

Изобретение относится к электросвязи и может быть использовано в системах передачи данных для обеспечения синхронизации по циклам.

Цель изобретения - уменьшение . времени вхождения в синхронизм.

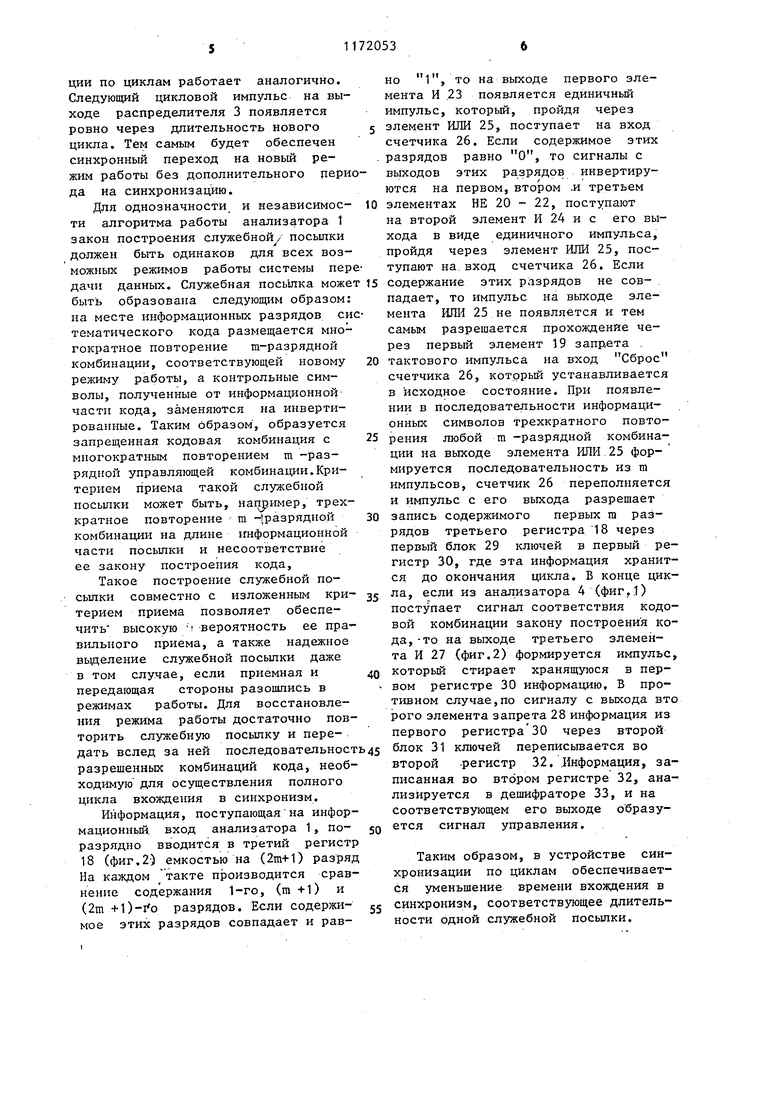

На фиг. 1 представлена структурная электрическая схема устройства для синхронизации по циклам; на фиг . 2 - структурная электрическая схема .анализатора служебной посып-7 кн. .

Устройство для синхронизации по . циклам содержит анализатор 1 служебной посылки, генератор 2.тактовых импульсов, распределитель 3, анализатор 4 кода, первый элемент И 5, второй элемент И б, первый триггер 7, второй триггер 8., первый делитель 9 частоты, второй делитель 10 час-. тоты, первый элемент 11 запрета, второй элемент 12 запрета, первый, дополнительный элемент И 13, второй

дополнительный элемент И 14, первый счетчик 15, второй счетчик 16 и элемент ИЛИ 17.

Анализатор служебной посылки содержит третий регистр 18 сдвига, первый элемент 19 запрета, первый, второй и третий элементы запрета 20 - 22, первый и второй элементы И 23 и 24, элемент ИЛИ 25, счетчик 26, третий элемент И 27, второй элемент 28 запрета, первьй блок 29 ключей, первый регистр 30 сдвига, второй блок 31 ключей, второй регистр 32 сдвига, дешифратор 33,

Устройство для синхронизации по циклам работает следующим образом.

В соответствии с ранее установленным режимом работы анализатор 1 (фиг.1) выдает управляющий сигнал в распределитель 3, анализатор 4, первый 9 и второй делитель 10, которые по этому сигналу- устанавливаются для работы с соответствую цим блочным кодом. Информация, поступающая на информационный вход устройства синхронизации по циклам поразрядно вводится в анализатор4, на выходе которого с тактовой час- тотой появляются сигналы 1 при соответствии и О при несоответствии п-разрядной последовательности двоичных символов закону построения кода. Если на момент поступления очередного импульса соответствия с выхода анализатора 4 синхронизм в работе устройства сннхронизации по ци лам отсутствует, то первьй и второй .триггеры 7 и 8 находятся в состоянии, в которое они будут пере ведены сигналом с выходов первого и в торого элементов 11 и 12 запрета при несовпадении по времени предьщущего импульса соответствия с импульсом на выходе первого и второго делителей 9 и 10. Тогда очередной импульс соответствия с выхода анализатора 4. при наличии разрешающего i сигнала с первого выхода первого триггера 7 проходит через первый элемент И 5 и запускает первый дели- тель 9,которьй с этого момента начин ет делить в п раз тактовую частоту |д1оступающую с генератора 2.Через один такт после запуска на дополнительном выходе первого делителя 9 появляется сигнал,который поступает на вход Установка О первого тригге ра 7 и устанавливает его в нулевое состояние , при этом снимается разрешающий сигнал на втором вхо |де первого элемента И 5 и исключаетс повторный запуск первого делител; 9 на время анализа периодичности появления импульсов соответствия с установленной в первом делителе 9 начальной фазой. Одновременно с инверсного выхода первого триггера 7 на третий вход второго элемента И 6 подается разрешающий сигнал для пропуска через этот элемент следующего импульса соответствия, которьй может появиться на последующих тактах входной последовательности. Если импульс, запустивший первый делитель 9, соответствует истинной фазе, то через п тактов на выходе первого делителя 9 появляется импульс, который совпадает во времени с импульсом соответствия на выходе анализатора А и проходит через первый дополнительный элемент И 13 на счетчик 15. Через заданное количество циклов, если сигнал соответствия с выхода анализатора 4 появляется регулярно в каждом цикле, происходит переполнение счетчика 15, и импульс с его выхода, пройдя через элемент ИЛИ 17, запускает распределитель 3. Если же в каком-либо цикле сигнал соответствия на выходе анализатора 4 отсутствует, то импульс с выхода первого делителя 9 проходит через первый элемент 11 запрета, сбросит в исходно., состояние счетчик 15 и установит в первое состояние первьй триггер 7, подготовив устройство синхронизации по циклам к новому циклу анализа. Если же в течение одного цикла на выходе анализатора 4 появляется второй импульс соответствия, то он при наличии разрешающего сигнала с инверсного выхода первого триг- repa 7 и разрешающего сигнала с прямого выхода второго триггера 8 проходит через второй элемент. . И 6 и запускает второй делитель 10. В дальнейшем работа второго делителя 10, второго элемента 12 запрета, второго дополнительного элемента И 14, второго триггера 8 и второго счетчика 16 аналогична работе первого канала устройства синхронизации по циклам, содержащего первьй элемент И 5, первый делитель 9, первьй элемент 11 запрета, первый дополнительный элемент И 13, первый триггер 7 и первый счетчик 15. Параллельно анализатор 1 в конце каждого истинного цикла при получении сигнала несоответствия принятой кодовой комбинации закону построения кода из анализатора 4 производит проверку поступившей комбинации на принадлежность ее к служебной посылке. Если полученная комбинация будет отнесена к служебной, то на основании информацииJзаключенной в ней, формируется соответствующий сигнал управления в распределитель 3, анализатор 4 и первый и второй делители 9 и 10, подготавливающий данные элементы для работы с новым кодом. При этом в распределителе 3, первом и втором делителях 9 и 10 изменяется коэффициент . деления. В дальнейшем устройство синхронизации по циклам работает аналогично. Следующий цикловой импульс на выходе распределителя 3 появляется ровно через длительность нового цикла. Тем самым будет обеспечен синхронный переход на новый режим работы без дополнительного церида на синхронизацию.

Для однозначности и независимоети алгоритма работы анализатора 1 закон построения служебной/ посыпки должен быть одинаков для всех возможных режимов работы системы пердачи данных. Служебная посьшка може быть образована следующим образом: на месте информационных разрядов ситематического кода размещается многократное повторение т-разрядной комбинации, соответствующей новому режиму работы, а контрольные символы, полученные от информационной части кода, заменяются на инвертированные. Таким образом , образуется запрещенная кодовая комбинация с многократным повторением m -разрядной управляющей комбинации.Критерием приема такой служебной посылки может быть, например, трехкратное повторение m - разрядной комбинации на длине информационной части посылки и несоответствие ее закону построения кода.

Такое построение служебной посыпки совместно с изложенным критерием приема позволяет обеспечить высокую вероятность ее правильного приема, а также надежное выделение служебной посылки даже в том случае, если приемная и передающая стороны разошлись в режимах работы. Для восстановления режима работы достаточно повторить служебную посылку и передать вслед за ней последовательност разрешенных комбинаций кода, необходимую для осуществления полного цикла вхождения в синхронизм.

Информация, поступающаяна информационный, вход анализатора 1, поразрядно вводится в третий регистр 18 (фиг.2) емкостью на (2т+1) разряд На каждом такте производится сравнение содержания 1-го, (т +1) и (2т +l)-io разрядов. Если содержимое этих разрядов совпадает и равно 1, то на выходе первого элемента И .23 появляется единичньш импульс, которьш, пройдя через элемент ИЛИ 25, поступает на вход счетчика 26. Если содержимое этих разрядов равно О, то сигналы с выходов этих разрядов инвертируются на первом, втором .и третьем элементах НЕ 20 - 22, поступают на второй элемент И 24 и с его выхода в виде единичного импульса, пройдя через элемент ИЛИ 25, поступают на. вход счетчика 26. Если Содержание этих разрядов не совпадает, то импульс на выходе элемента ИЛИ 25 не появляется и тем самым разрешается прохождение через первый элемент 19 запрета . тактового импульса на вход Сброс счетчика 26, который устанавливается в исходное состояние. При появлении в последовательности информационных символов трехкратного повторения любой m -разрядной комбинации на выходе элемента ИЛИ 25 формируется последовательность из m импульсов, счетчик 26 переполняется и импульс с его выхода разрешает запись содержимого первых m разрядов третьего регистра 18 через первый блок 29 ключей в первый регистр 30, где эта информация хранится до окончания цикла. В конце цикла, если из анализатора 4 (фиг..1) поступает сигнал соответствия кодовой комбинации закону построения кода, -то на выходе третьего элемента И 27 (фиг.2) формируется импульс который стирает хранящуюся в первом регистре 30 информацию, В противном случае,по сигналу с выхода вто рого элемента запрета 28 информация из первого регистра30 через второй блок 31 ключей переписывается во второй .регистр 32. .Информация, записанная во втором регистре 32, анализируется в дешифраторе 33, и на соответствующем его выходе образуется сигнал управления.

Таким образом, в устройстве синхронизации по циклам обеспечивается уменьшение времени вхождения в синхронизм, соответствующее длительности одной служебной посылки.

| Устройство синхронизации по циклам | 1978 |

|

SU684758A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-08-07—Публикация

1983-11-21—Подача