ю

00

о

01

ашз

ч

Изобретение относится к дискриминаторам разности фаз двух сигналов и может быть использовано в различных системах автоматики для допускового контроля разности фаз входных сигналов..

Цель изобретения - повышение функциональной надежности устройства при допусковом контроле сдвига фаз.

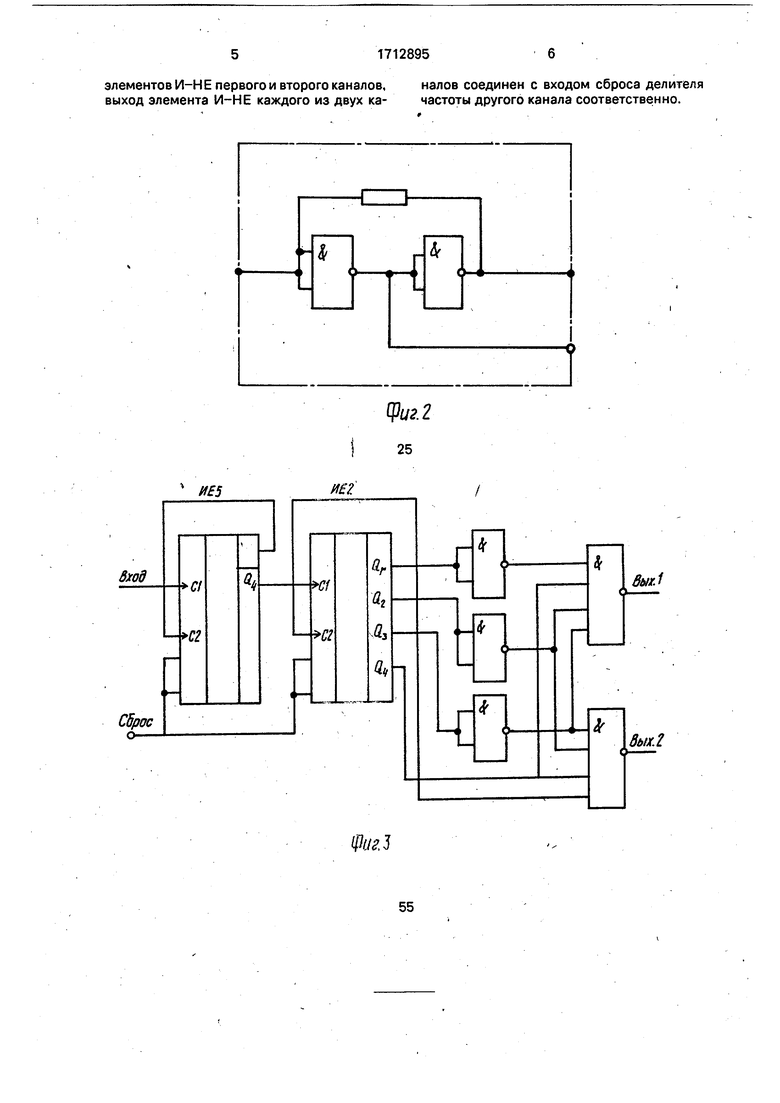

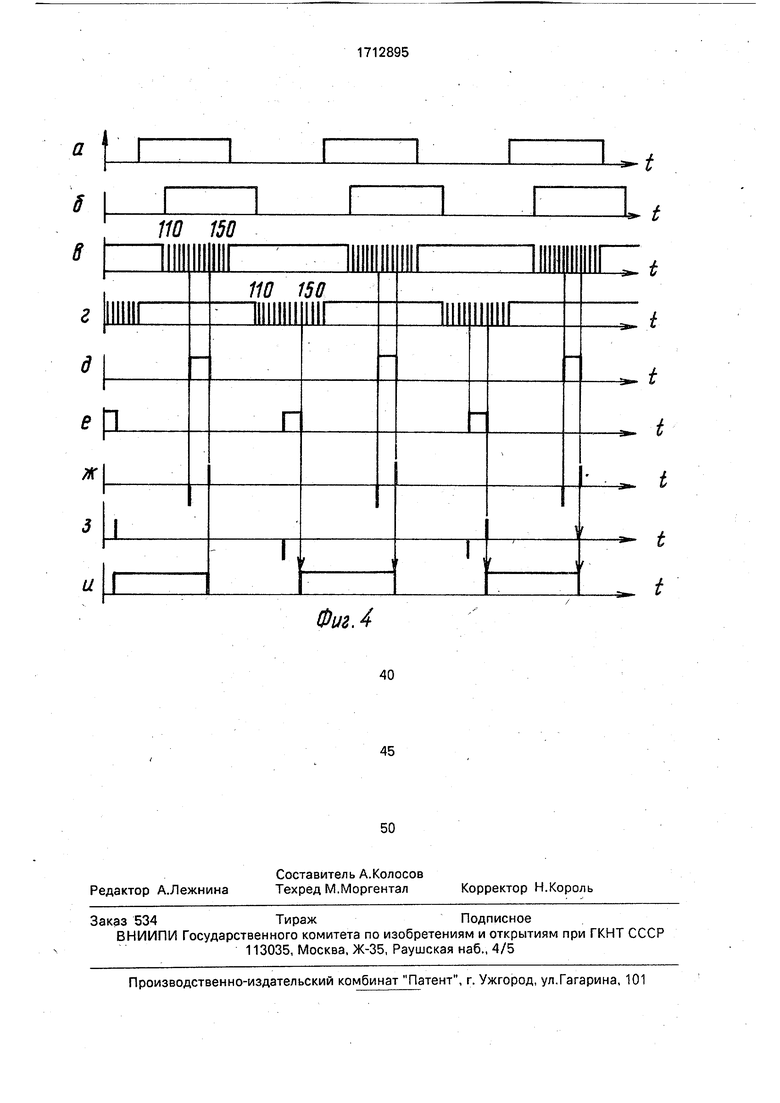

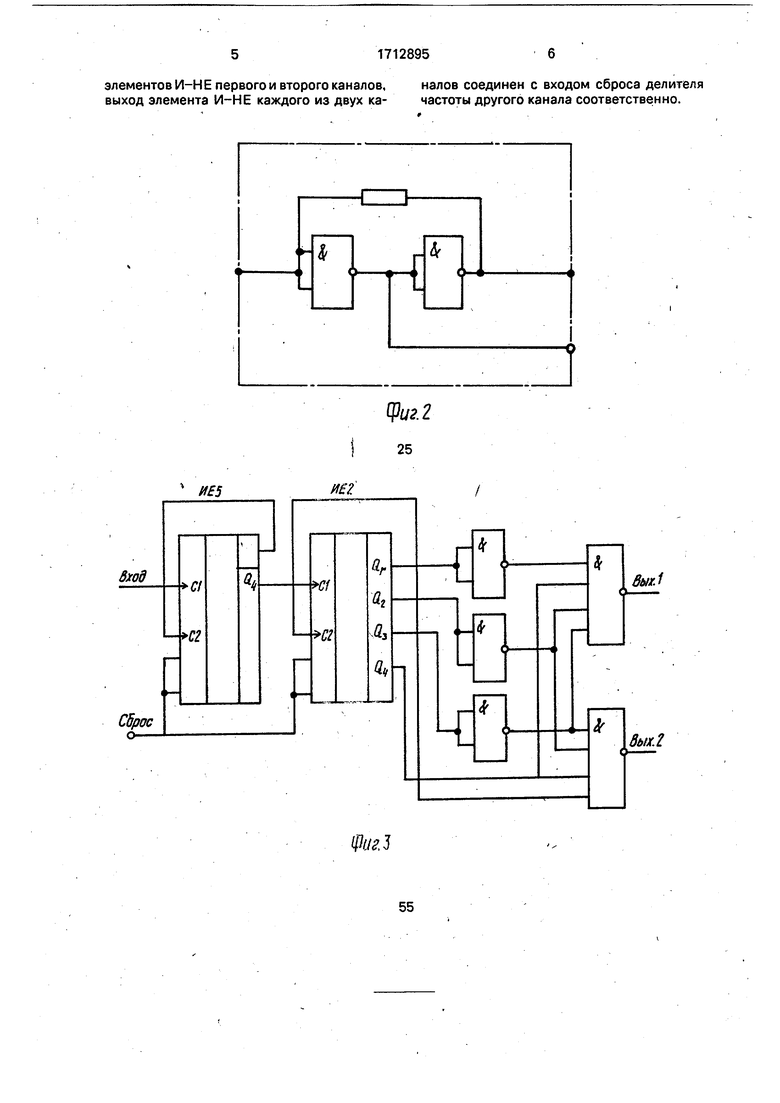

На фиг. 1 приведена структурная электрическая схема устройства контроля сдвига фаз двух сигналов; на фиг. 2 - электрическая схема формирователя импульсов; на фиг. 3 - электрическая схема делителя частоты; на фиг. 4 - временные диаграммы, поясняющие принцип работы устройства.

Устройство контроля сдвига фаз двух сигналов .содержит первый и второй каналы 1 и 2, формирователь 3 импульсов, делитель 4 частоты, триггер 5, генератор 6 опорной частоты, элемент И 7, элемент И-НЕ 8, первую, вторую и третью дифференцирующие цепочки 9, 10 и 11 и выходной триггер 12.

Устройство контроля сдвига фаз двух сигналов работает следующим образом.

На входы формирователей 3 импульсов первого и второго каналов 1 и 2 поступают два сигнала (фиг. 4а, б), а на их выходах имеются прямоугольники прямого и инвертированного сигналов. На выходах элементов И 7 первого и второго каналов 1 и 2 формируются импульсы, равные времени совпадения импульсов на входах этих элементов. На элементах И-НЕ 8 собраны схемы, которые производят заполнение последних прямоугольными импульсами высокой частоты от генератора 6 опорной частоты (фиг. 4 в, г). Таким образом, количество импульсов на выходе элемента И-НЕ 8 пропорционально времени совпадения импульсов на входах элементов И 7 первого и второго каналов 1 и 2. Эти импульсы заполнения подаются на счетный вход делителя 4 частоты каждого канала и на вход сброса делителя 4 частоты другого канала.

Это обеспечивает сброс делителя 4 частоты во время приема каждого импульса и подготовку его к последующей работе, а также исключает одновременную работу обоих делителей 4 частоты в случае непрерывных последовательностей счетных импульсов и помех.

При достижении делителем, 4 частоты номера импульса начальной установки, например 110, на одном из выходов дешифратора делителя 4 частоты появляется импульс (фиг. 4Д), который проходит через первую дифференцирующую цепочку 9 и переводит триггер 5 в единичное состояние. При достижениу1 делителем 4 частоты номера контрольного импульса, например 150, появляется импульс на втором выходе делителя 4 частоты, который производит сброс триггера 5 в нулевое состояние, который, проходя через третью дифференцирующую цепочку 11 (фиК 4ж), переключает в единичное состояние выходной триггер 12 (фиг. 4и).По окончании происходящего в 1-м канале счета сорпадения импульсов происходит аналогичный счет во втором канале (фиг. 4е, з). В результате происходит сброс выходного триггера 12 в нулевое состояние (фиг. 4и). Таким образом, по завершении цикла работы устройства на выходе появляется последовательность импульсов сигнальной частоты.

Если разность фаз больше наперед заданного значения (нормы) делитель 4 частоты следования импульсов не достигает номера контрольного импульса, переключений триггеров 5 не происходит, на выходе устройства последовательность импульсов отсутствует.

Точность контроля разности фаз зависит только от частоты импульсов заполнения, быстродействия и разрядности счетчика. Норма разности фаз устанавливается либр подключением соответствующих выводов дешифраторов и счетчикрв делителя 4 частоты, либо изменением частоты заполнения генератора 6 опорной частоты.

Формула изобретения

V

Устройство контроля сдвига фаз двух сигналов, содержащее два канала, каждый из которых состоит из формирователя импульсов, делителя частоты и триггера, а также генератор опорной частоты, о т л и ч а-ющ е е с я тем, что с целью повышения функциональной надежности устройства при допусковом контроле сдвига фаз, в каждый канал устройства введень элемент И, элемент И-НЕ и три дифференцирующие цепочки, а также выходной триггер, причем первый выход формирователя каждого канала соединен через элемент И с первым входом элемента И-НЕ, выход которого соединен со счетным входом делителя частоты, первый и второй выходы которого через первую и вторую дифференцирующие цепочки соединены с первым и вторым входами триггера соответственно, выход которого через третью дифференцирующую цепочку соединеас одним из двух входов выходного триггера, причем второй выход формирователя импульсов каждого канала соединен с вторым входом элемента И другого канала, выход генератора опорной частоты соединен с вторыми входами

517128956

элементов И-НЕ первого и второго каналов, налов соединен с входом сброса делителя выход элемента И-НЕ каждого из двух ка- частоты другого канала соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор | 1980 |

|

SU920835A1 |

| РАДИОЛУЧЕВОЙ ДАТЧИК ОХРАНЫ | 1992 |

|

RU2079889C1 |

| Устройство для измерения и регулирования соотношения скоростей | 1985 |

|

SU1364993A1 |

| Устройство для генерирования многофазного напряжения | 1980 |

|

SU959257A1 |

| УСТРОЙСТВО КОНТРОЛЯ РАБОТОСПОСОБНОСТИ ЭЛЕКТРОДВИГАТЕЛЯ ПОСТОЯННОГО ТОКА | 2013 |

|

RU2526500C1 |

| Шифратор | 1985 |

|

SU1298802A2 |

| Устройство контроля амплитуды переменного напряжения | 1986 |

|

SU1354122A1 |

| Аналого-цифровой низкочастотный фазометр | 1990 |

|

SU1780042A1 |

| Устройство для счета движущихся объектов | 1985 |

|

SU1312623A1 |

| Устройство для контроля и учета количества отдозированного материала | 1987 |

|

SU1506461A1 |

Изобретение относится к автоматике и может использоваться для допускового контроля разности фаз входных сигналов. Цель изобретения— повышение функциональнойнадежности устройства при допусковом контроле сдвига фаз. Устройство контроля сдвига фаз двух сигналов содержит первый и второй каналы 1 и 2, формирователь 3 импульсов, делитель 4 частоты, триггер 5, генератор 6 опорной частоты, элемент И 7, злемент И-НЕ 8, первую, вторую и третью дифференцирующие цепочки 9, 10 и 11 и выходной триггер 12. Введение элементов И 7, И-НЕ 8, а также трех дифференцирующих цепочек 9, 10, 11 и выходного триггера 12 позволяет повысить функциональную надежность устройства при допусковом контроле сдвига фаз двух сигналов пут м получения более достоверной информации о разности фаз входных сигналов. 4 ил.

/ftf

CPU2.2

Фиг. 4

| Преобразователь фазового сдвига в интервал времени | 1980 |

|

SU924609A1 |

| G,01 R 25/00, 1980. | |||

Авторы

Даты

1992-02-15—Публикация

1989-07-27—Подача