Предлагаемый способ защиты от сбоев и отказов электронного блока космического аппарата, вызываемых внешними воздействующими факторами, и устройство для его осуществления могут быть применены при управлении спутников, космических станций и других космических аппаратов (КА).

В состав бортового радиоэлектронного оборудования (БРЭО) космического аппарата, как правило, входят система управления КА, включающая, в свою очередь, бортовые цифровые вычислительные комплексы (БЦВК), а также электронные блоки (ЭБ), при помощи которых осуществляется управление бортовыми системами (БС).

БЦВК осуществляет формирование управляющих кодов в соответствии с программой полета, обеспечивает управление положением КА, контроль и управление бортовыми системами (БС) в соответствии с их состоянием и логикой управления, заложенной в программное обеспечение.

Во время функционирования на борту КА в БЦВК решаются две основные функциональные задачи:

- управление движением и навигацией,

- управление бортовыми системами, обеспечивающими жизнедеятельность КА.

Первая задача решается при помощи программного обеспечения (ПО) системы управления движением и навигацией (СУДН), а вторая - при помощи ПО системы диагностического контроля и управления (СДКУ).

ЭБ конструктивно представляют собой герметичные контейнеры, в которых устанавливаются модули, выполненные, например, в виде печатных плат с установленными на них электронными микросхемами, резисторами, индуктивными и другими элементами. Внутри герметичного контейнера ЭБ печатные платы соединяются между собой при помощи контактных соединителей. В то же время межблочные связи выполняются в виде бортовой кабельной сети, содержащей разъемы с механическими контактами. ЭБ, как правило, реализуются на базе микропроцессоров с «жестко» реализованной логикой. Функционально, на печатных платах ЭБ размещаются устройства обмена для связи с БЦВК, преобразователи кодов в импульсы различной длительности, буферные регистры, счетчики, широтно-импульсные, цифро-аналоговые и аналого-цифровые преобразователи, элементы гальванической развязки, усилительные элементы, вторичные источники питания и другие элементы. Взаимодействие ЭБ с БЦВМ и БС осуществляют при помощи резервированных каналов.

СДКУ реализуется, как правило, в виде бортового цифрового вычислительного комплекса с соответствующим программным обеспечением. Источники питания, при помощи которых осуществляется питание соответствующих каналов ЭБ, являются гальванически развязанными и независимыми.

ЭБ, как правило, состоит их нескольких идентичных и независимых каналов резервирования, например, трех, и проектируется с таким расчетом, чтобы отказ, как минимум, одного из них не влиял на управление подключенной к нему бортовой системы. Питание в первый, второй и третий каналы подается при помощи соответствующих коммутаторов тока. Каждый канал содержит вторичный источник питания, датчик тока, аналого-цифровой преобразователь и выходной регистр контроля тока потребления. Вторичный источник питания, установленный в каждом канале ЭБ, обеспечивает стабилизацию и преобразование уровней подаваемого напряжения из источников питания каналов, то есть от бортовой сети электроснабжения. Измеренные значения токов потребления каждым каналом ЭБ с выхода датчика тока передается в соответствующие аналого-цифровые, преобразователи и преобразуется в код, который поступает в регистр и далее с его выхода передается в СДКУ. Кроме того, каждый канал содержит входной и выходной регистры, через которые осуществляется обмен информацией с СДКУ. Поступивший из СДКУ в выходной регистр код при помощи соответствующих элементов преобразования, преобразуется в команды управления бортовыми системами. При помощи элементов усиления осуществляется гальваническая развязка и усиление указанных команд, которые поступают на соответствующие входы исполнительных устройств бортовой системы. Исполнительные устройства исполняют поступившую команду от ЭБ, например, по схеме «ИЛИ», то есть если она формируется на выходе, хотя бы одного из каналов ЭБ.

Контроль состояния БС осуществляется при помощи дискретных и аналоговых датчиков, информация из которых поступает через соответствующие элементы согласования в аналогово-цифровые преобразователи, которые преобразуют полученные сигналы в коды, поступающие через выходные регистры каналов в СДКУ.

Бортовая система включает различные исполнительные устройства. Например, в газореактивной двигательной установке исполнительными устройствами являются электропневмоклапаны, с помощью которых осуществляется дозированная подача компонентов топлива в соответствующие магистрали и камеры, а также нагревательные элементы, обеспечивающие предварительный подогрев газореактивной смеси. Датчики обеспечивают формирование сигналов положения электропневмоклапанов, а при помощи аналоговых датчиков осуществляется измерение температуры, давления в магистралях и камерах двигателей.

В процессе полета на бортовое оборудование КА воздействует множество внешних воздействующих факторов, которые могут вызвать отказные ситуации, которые необходимо автоматически парировать. Отказные ситуации могут быть разделены на два типа: необратимые, вызванные не восстанавливаемыми отказами оборудования и обратимые, возникающие в результате сбоев оборудования. В результате отказных ситуаций в радиоэлектронном оборудовании КА может происходить недостоверное преобразование информации, получаемой от подключенных к нему бортовых систем (БС).

К основным факторам, влияющим на работоспособность радиоэлектронного оборудования КА, относятся, например, различные виды излучений, включающее воздействие частиц высокой энергии, температурные воздействия, статические разряды, ударные перегрузки и вибрация. Указанные факторы различаются по характеру и длительности воздействия. Например, время статического разряда, возникающего в результате накопления на поверхности приборов статического электричества, составляет несколько секунд, а продолжительность излучения, возникающего в результате солнечной вспышки, может составлять несколько минут. Следствиями данных воздействий являются сбои и отказы БРЭО, в том числе, тиристорный эффект, вызывающий эффект перегрузки электронных элементов по току.

Сбои информации и перегрузки по току в канале ЭБ могут носить временный характер и не вызывать необратимых отказов, если произвести немедленное отключение, а затем повторное включение соответствующего канала ЭБ, в котором они возникают. Обеспечить немедленное отключение отказавшего канала ЭБ средствами наземного комплекса управления (НКУ) не представляется возможным, так как для выявления перегрузки требуется анализ телеметрической информации, передаваемой в НКУ от КА, после чего необходимо сформировать и выдать соответствующие команды.

В течение времени, необходимого для принятия решения в НКУ и последующих действий в электронных блоках, в которых возникает перегрузка, могут возникнуть катастрофические необратимые отказы. Проблема решается путем автоматизации действий по парированию указанных перегрузок.

Временные сбои в электронном блоке (ЭБ) могут возникать из-за нарушения контактных соединений из-за вибрации, периодически возникающей на борту КА в результате работы двигателей, либо изменения положения подвижных элементов конструкции КА (панелей солнечных батарей, антенн, телескопов и т.п.).

Неравномерный нагрев ЭБ под воздействием инфракрасного излучения Солнца, изменения температуры в результате изменения режимов работы элементов, входящих в состав ЭБ, а также попадание конструктивных элементов КА в теневую зону от других объектов, в том числе, например, в теневую часть орбиты Земли, могут приводить к значительным изменениям температуры в ЭБ. В результате нагрева и охлаждения плат и разъемных соединений в ЭБ появляются температурные градиенты, приводящие к возникновению термомеханических напряжений, в результате чего может происходить деформация разъемных соединений в ЭБ. В конечном итоге это может привести к отказу ЭБ, обусловленному прерыванием, либо замыканием в нем контактных соединений.

Если отказ произошел из-за температурных воздействий, попытку восстановления работоспособности отказавшего ЭБ необходимо производить после обеспечения стабилизации температуры и равномерного ее распределения по всем элементам указанного ЭБ. Температурные нарушения могут сохраняться до нескольких десятков минут, устраняются, например, после изменения положения отказавшего блока ЭБ, расположенного в определенном месте на борту КА, относительно направления на Солнце, либо изменения температурных режимов системой терморегулирования КА.

Поскольку во время работы ЭБ может происходить неравномерный нагрев элементов, входящих в его состав, который может приводить к отказам, например, из-за деформации разъемных соединений. Для уравнивания температуры указанных элементов целесообразно отключать канал резервирования указанного ЭБ, в котором произошел отказ.

В результате воздействия тяжелых заряженных частиц и высокоэнергетических протонов космического пространства на интегральные микросхемы, входящие в состав аппаратуры каналов ЭБ, их потребление может резко увеличиваться из-за возникновения тиристорного эффекта. Тиристорный эффект (ТЭ) сопровождается, как правило, протеканием больших токов по цепи питания и сопровождается разогревом интегральных микросхем ЭБ. В результате это может привести к необратимому отказу аппаратуры ЭБ. Полное восстановление работоспособности аппаратуры, в которой произошел ТЭ, происходит после своевременного отключения питания, при этом тиристорная структура отключается, температура и напряжение на выводах интегральных микросхем уменьшаются до уровня прекращения указанного эффекта.

Отказы, возникающие в каналах ЭБ в результате вибрации, либо статического разряда, могут носить временный характер, при этом при отключении и последующем повторном включении ЭБ после прекращения внешнего воздействия отказ, как правило, устраняется. С другой стороны, повторное включение соответствующего канала ЭБ после отключения не приводит к устранению отказа, если он имеет необратимый характер, поэтому число указанных повторных включений необходимо ограничить.

Длительность отключенного состояния канала ЭБ, после которого допускается его включение, зависит от характера внешнего воздействия, из-за которого произошел отказ. Учитывая различную природу внешних воздействий, а также их продолжительность, отключенное состояние канала ЭБ должно минимально влиять на выполнение задач КА.

Минимальное время, на которое необходимо отключать ЭБ перед повторным включением, как правило, оговаривается в паспортных данных. Вместе с тем в случае тиристорного эффекта, повторное включение необходимо производить после полной разрядки емкостно-индуктивных связей на элементах ЭБ, в результате чего тиристорный эффект полностью пропадает. Длительность отключенного состояния канала ЭБ в этом случае увеличивается в несколько раз по сравнению с паспортными данными на ЭБ. Время, необходимое для полной разрядки может быть определено по результатам расчетов и отработки на стендах.

Сбой информации в каналах ЭБ обусловлен, как правило, помехами и не приводит к немедленному отказу элементов, поскольку токи, формируемые на элементах каналов ЭБ, имеют ограничения, поэтому снятие питания с канала ЭБ может выполняться с небольшой задержкой. При сбоях информации происходит искажение информации, поступающей от БС через каналы ЭБ. Как правило, при сбоях, может происходить «зависание», либо «залипание» информации. Питание микросхем, в которых может произойти сбой информации, осуществляется небольшими номиналами напряжений, при этом токи, формируемые на элементах ЭБ, как правило, ограничены. Таким образом, сбой информации не приводит к их необратимым отказам. Указанный сбой обычно устраняется при повторном включении канала после его отключения. Для повторного включения канала ЭБ после указанного сбоя информации, требуется меньше времени, чем при повторном включении канала после перегрузки по току, обусловленной тиристорным эффектом, так как во втором случае требуется более «глубокий» разряд на емкостно-индуктивных элементах канала ЭБ и время для снижения температуры на элементах, на которых он произошел.

Необходимо отметить, что нарушение на длительный интервал времени управления системами, которые обеспечивают, ориентацию и стабилизацию положения КА может приводить к нарушению выполнения задачи К А в целом.

Внешние воздействующие факторы, включая тиристорный эффект, как правило, не воздействуют, либо оказывают минимальное воздействие на отключенные каналы ЭБ. Таким образом, устойчивость к внешним воздействиям на аппаратуру ЭБ в системе, в которой один из каналов отключен, выше, чем в системе, в которых одновременно включены все каналы резервирования.

Известен способ парирования перегрузок по току в электронном блоке космического аппарата, принятый за прототип, суть которого заключается в том, что, измеряют ток потребления каждым каналом электронного блока. Определяют допустимый короткий интервал времени, перед повторным включением канала после его отключения при перегрузках по току, а также длительный интервал времени ожидания, как часть периода вращения космического аппарата вокруг Земли, задают допустимое количество повторных включений канала на длительном интервале времени. На каждом длительном интервале времени при перегрузках по току отключают канал электронного блока, затем через короткий интервал времени его включают. Если количество включений канала электронного блока на одном длительном интервале не превышает порогового значения, отсчитывают короткий интервал времени ожидания с момента отключения. Одновременно, после первого отключения канала, отсчитывают длительный интервал времени ожидания. После отсчета короткого интервала включают канал и увеличивают количество включений канала на единицу. Сбрасывают количество включений канала, если оно не превышает порогового значения, в момент окончания длительного интервала времени. Отключают ток и прекращают управление парированием отказов канала, количество включений которого достигает порогового значения [1].

Наиболее близким устройством, принятым за прототип, является устройство парирования перегрузок по току трехканального электронного блока космического аппарата, обусловленных внешними воздействующими факторами, включая тиристорный эффект, каждый канал которого содержит коммутатор тока, первый вход которого является первым входом устройства, а выход соединен со входом датчика тока, первый выход которого является выходом устройства, а второй выход соединен через аналого-цифровой преобразователь с первым входом первого элемента сравнения, второй вход которого является вторым входом устройства, при этом его выход соединен с первым входом первого элемента «И», второй вход которого соединен с первым входом второго элемента «И» и является третьим входом устройства, а выход соединен через формирователь коротких импульсов с первыми входами, третьего и четвертого элементов «И», а также с первым входом сброса запоминающего элемента, выход которого, в свою очередь, соединен со вторым входом управления коммутатора токов, при этом второй установочный вход запоминающего элемента соединен с выходом элемента ИЛИ, первый вход которого является четвертым входом устройства, а его второй вход через элемент короткой задержки соединен с выходом четвертого элемента «И», а также с первым счетным входом счетчика, выход которого соединен с первым входом второго элемента сравнения, второй вход которого является пятым входом устройства, а инверсный выход соединен со вторым входом четвертого элемента «И», при этом второй вход сброса счетчика соединен с выходом элемента длительной задержки, через второй вход второго элемента «И» соединен с третьим входом элемента «ИЛИ», а также первым входом сброса триггера, инверсный выход которого соединен со вторым входом третьего элемента «И», выход которого, в свою очередь соединен со вторым счетным входом триггера и входом элемента длительной задержки [1].

Недостатками известных способа и устройства являются следующие:

- парируются отказные ситуации, связанные только с перегрузками по току в каналах ЭБ, при этом не учитываются сбои и отказы в информационных цепях ЭБ, возникающие в результате нарушения в работе отдельных элементов ЭБ,

- внешним воздействующим факторам подвергаются одновременно все каналы электронного блока, так как они включены.

Технической задачей предлагаемого изобретения является повышение устойчивости к отказам и надежности, а также расширение функциональных возможностей бортового радиоэлектронного оборудования КА.

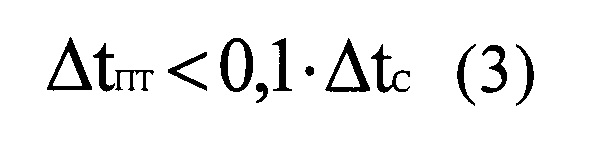

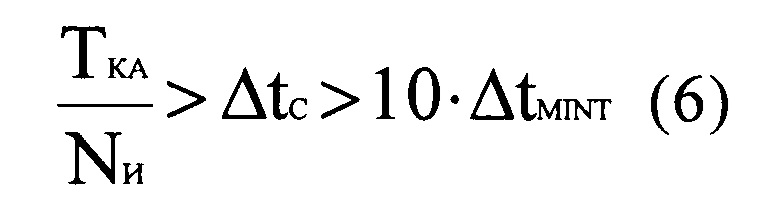

Технический результат достигается тем, что в способ защиты от сбоев и отказов ЭБ космического аппарата, вызываемых внешними воздействующими факторами, заключающийся в том, что производят сбор информации о состоянии каналов трехканального резервированного электронного блока системой диагностического контроля космического аппарата, определяют максимально возможный ток, который может потреблять каждый канал трехканального резервированного электронного блока, а также допустимое количество повторных включений электронного блока, при котором он сохраняет работоспособность, задают пороговое значение тока одного канала электронного блока, измеряют токи потребления каждым каналом электронного блока, отключают канал, ток потребления которого превышает пороговое значение тока, при этом начинают отсчет задержки на включение при перегрузке по току, определяют период вращения космического аппарата вокруг Земли, разбивают его на фиксированные интервалы времени, которые определяются ориентацией космического аппарата относительно Солнца и планет, как:

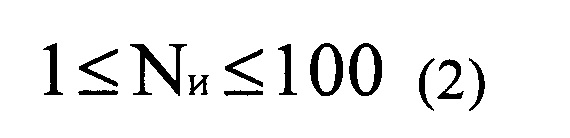

1≤NИ≤100

где: NИ - количество интервалов времени, на которые разбивают период вращения космического аппарата вокруг Земли,

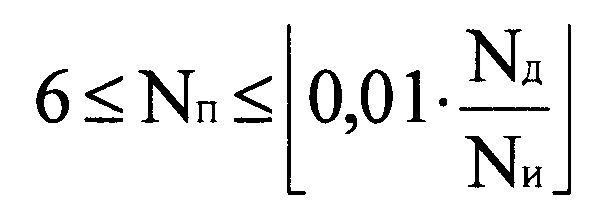

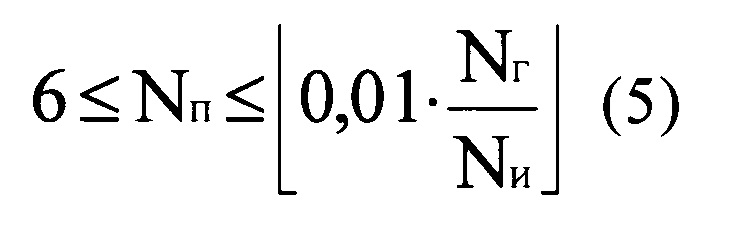

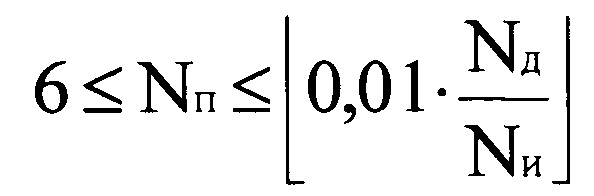

задают интервал времени сброса, задают пороговое значение количества включений каналов электронного блока на одном интервале времени сброса, кратное трем, округленное в меньшую сторону до целого числа, в диапазоне:

где: NП - пороговое значение количества включений всех каналов на одном интервале времени сброса,

NД - допустимое количество повторных включений электронного блока, при котором он сохраняет работоспособность,

- знак округления в меньшую сторону до целого числа, задают пороговое значение задержки на включение канала при перегрузке по току, задают пороговое значение количества включений каналов электронного блока на одном интервале времени сброса, дополнительно определяют предельные токи, при которых каналы электронного блока сохраняют работоспособность, задают пороговое значение тока перегрузки одного канала электронного блока в диапазоне:

- знак округления в меньшую сторону до целого числа, задают пороговое значение задержки на включение канала при перегрузке по току, задают пороговое значение количества включений каналов электронного блока на одном интервале времени сброса, дополнительно определяют предельные токи, при которых каналы электронного блока сохраняют работоспособность, задают пороговое значение тока перегрузки одного канала электронного блока в диапазоне:

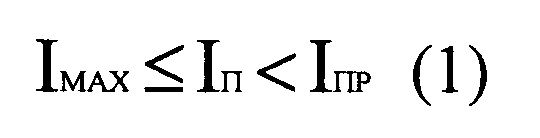

IМАХ≤IП<IПР

где: IМАХ - максимально возможный ток, который может потреблять каждый канал электронного блока во время функционирования в составе космического аппарата,

IПР - предельный ток, при котором каналы электронного блока сохраняют работоспособность,

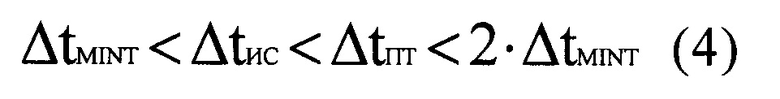

IП - пороговое значение тока в канале электронного блока, определяют минимальные времена задержек, по окончанию которых допускается включение канала электронного блока после его отключения в случае отсутствия и наличия перегрузки по току, при этом задают соответствующие значения задержек на включение в диапазонах:

ΔtMINT<ΔtПT<2⋅ΔtMINT,

ΔtMIN<ΔtИC<ΔtПT,

где: ΔtMINT - минимальное время, при котором допускается включение канала электронного блока после его отключения при наличии перегрузки по току,

ΔtПT - задержки на включение канала при перегрузке по току,

ΔtMIN _ минимальное время, при котором допускается включение канала

электронного блока после его отключения при отсутствии перегрузок по

току,

ΔtИС - задержка на включение канала при информационном сбое, задают интервал времени сброса в диапазоне:

где ΔtС - интервал времени сброса,

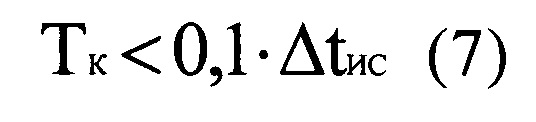

ТКА - период оборота космического аппарата вокруг Земли, в каналах электронного блока осуществляют преобразование кодов, поступающих из системы диагностического контроля и управления, в соответствующие команды управления бортовой системой, задают период контроля, как:

TK<0,l⋅ΔtИС,

где: ТК - период контроля,

кроме того, в каналах электронного блока одновременно осуществляют преобразование сигналов формируемых бортовой системой в коды, которые опрашивают на каждом периоде контроля, в случае, если сигнал отказа отсутствует и включены два канала, сравнивают опрашиваемые коды, поступающие от первого и второго, второго и третьего или третьего и первого каналов электронного блока, и если они отличаются, отключают, соответственно, первый, второй или третий канал, начиная с момента отключения канала, отсчитывают для него задержку на включение канала при информационном сбое, при этом в момент отключения канала увеличивают на единицу подсчитываемое количество включений каналов, если сигнал отказа отсутствует и число включенных каналов не более одного, а при наличии сигнала отказа - не более двух, включают на текущем или последующих периодах контроля канал, для которого отсутствует отсчет обеих задержек, сбрасывают в момент окончания интервала времени сброса подсчитанное количество включений каналов электронного блока, если оно не достигает порогового значения, а в случае достижения порогового значения формируют сигнал отказа системы, прекращают отключение каналов по отсутствию сравнению опрашиваемых кодов.

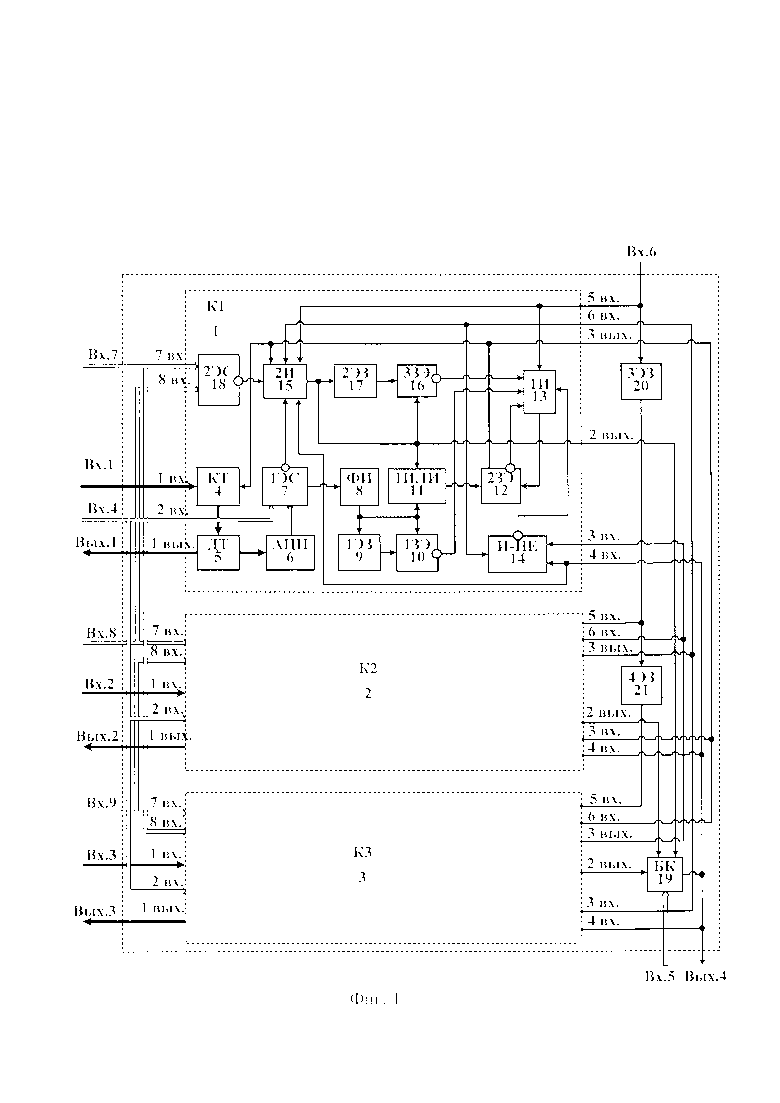

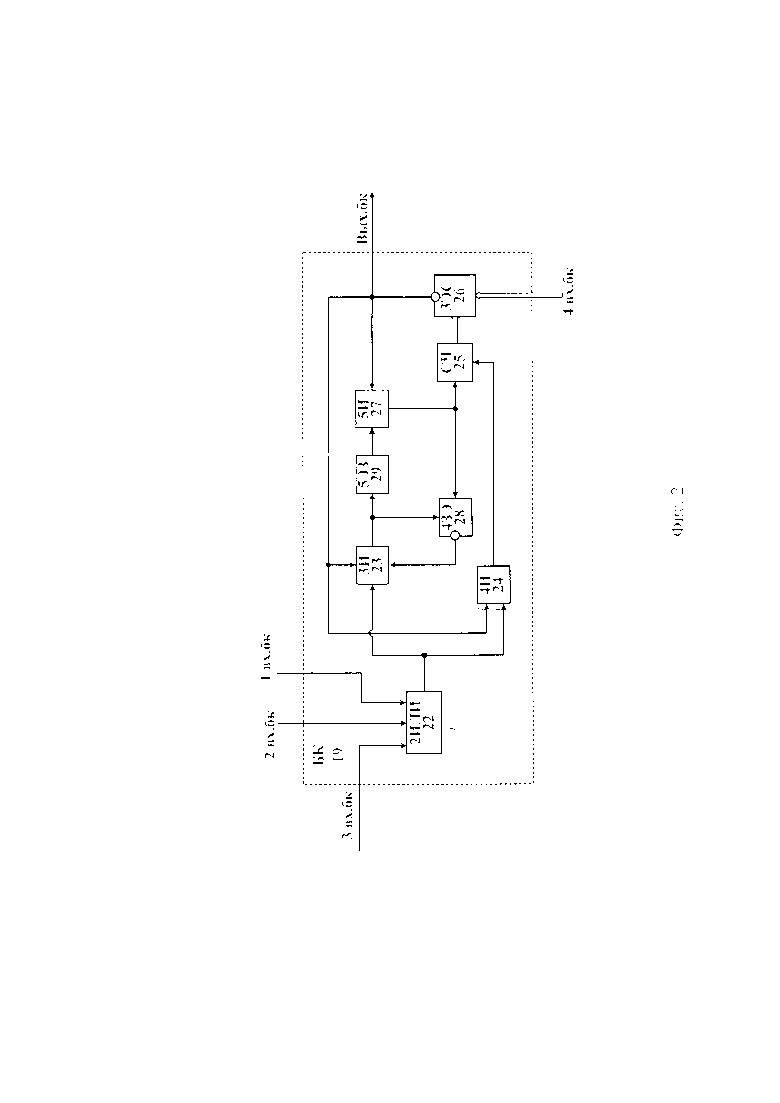

Технический результат от применения устройства защиты от сбоев и отказов электронного блока космического аппарата вызываемых внешними воздействующими факторами достигается за счет того, что устройство содержит первый, второй и третий каналы, которые идентичны, при этом каждый канал содержит коммутатор тока, первый вход которого является первым входом канала, а выход соединен со входом датчика тока, первый выход которого является первым выходом канала, а второй выход соединен через аналого-цифровой преобразователь с первым входом первого элемента сравнения, второй вход которого является вторым входом канала, отличающееся тем, что первый прямой выход первого элемента сравнения соединен со входом формирователя импульсов, выход которого соединен через первый элемент задержки с первым входом сброса первого запоминающего элемента, а также напрямую с его вторым установочным входом и с первым входом первого элемента «ИЛИ», выход которого, соединен с первым входом сброса второго запоминающего элемента, первый инверсный выход и второй вход установки которого соединены, соответственно, с первым входом и выходом первого элемента, второй и третий входы которого, в свою очередь, соединены, соответственно, с инверсным выходом первого запоминающего элемента и выходом элемента «И-НЕ», первый вход которого являются третьим, а второй вход четвертым входом канала и соединен с первым входом второго элемента «И», выход которого является вторым выходом канала и соединен со вторым входом первого элемента «ИЛИ», с первым установочным входом, а через второй элемент задержки со вторым входом сброса третьего запоминающего элемента, инверсный выход которого соединен с четвертым входом первого элемента «И», пятый вход которого является пятым входом канала и соединен со вторым входом второго элемента «И», третий вход которого является шестым входом канала и соединен с третьим входом элемента «И-НЕ», четвертый вход второго элемента «И» является третьим выходом канала, а также соединен со вторым прямым выходом второго запоминающего элемента и соединен со вторым входом коммутатора тока, пятый и шестой входы второго элемента «И» соединены, соответственно, со вторым инверсным выходом первого элемента сравнения и с инверсным выходом второго элемента сравнения, первый и второй входы которого являются, соответственно, седьмым и восьмым входами канала, при этом первые входы и первые выходы первого, второго и третьего каналов являются, соответственно, первым, вторым и третьим входами и первым, вторым, третьим выходами устройства, вторые входы всех указанных каналов соединены между собой и являются четвертым входом устройства, а вторые выходы первого, второго и третьего каналов связаны, соответственно, с первым, вторым и третьим входами блока контроля, четвертый вход которого является пятым входом устройства, а выход связан с четвертыми, связанными между собой, входами всех указанных каналов и является четвертым выходом устройства, при этом третий вход первого канала связан с шестым входом второго канала и третьим выходом третьего канала, третий вход которого связан с шестым входом первого канала, и третьим выходом второго канала, третий вход которого связан с шестым входом третьего канала и третьим выходом первого канала, пятый вход которого является шестым входом устройства, и связан через третий элемент задержки с пятым входом второго канала и входом четвертого элемента задержки, выход которого, в свою очередь, связан с пятым входом третьего канала, при этом седьмой вход первого канала является седьмым входом устройства и связан, при этом, с восьмым входом третьего канала, седьмой вход которого является девятым входом устройства и связан с восьмым входом второго канала, седьмой вход которого связан с восьмым входом первого канала и является восьмым входом устройства.

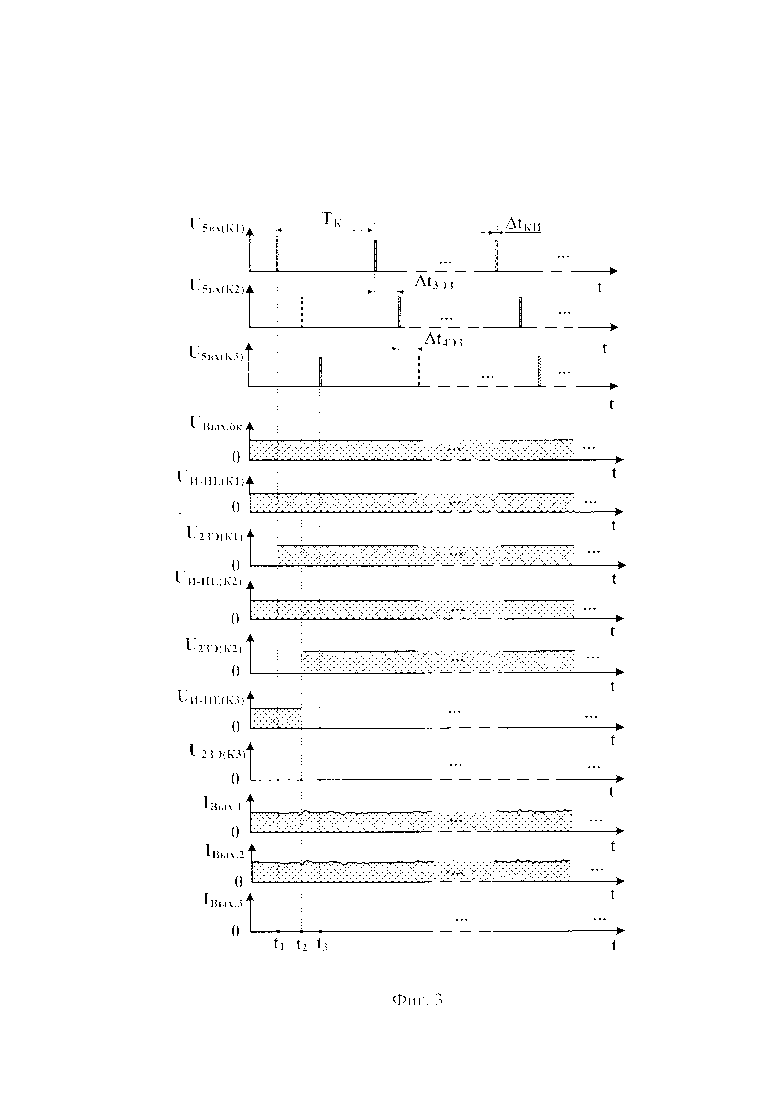

Блок контроля содержит второй элемент ИЛИ, первый, второй и третий входы которого являются, соответственно, первым, вторым и третьим входами блока контроля, а его выход связан с первыми входами третьего и четвертого элементов «И», выход последнего связан с первым счетным входом счетчика, выход которого, в свою очередь, соединен с первым входом третьего элемента сравнения, второй вход которого является четвертым входом блока контроля, а инверсный выход, который является выходом блока контроля соединен со вторыми входами третьего и четвертого элементов «И», а также первым входом пятого элемента, выход которого, в свою очередь, соединен со вторым входом сброса счетчика и первым входом сброса четвертого запоминающего элемента, инверсный выход которого, соединен с третьим входом третьего элемента «И», а второй вход соединен с выходом третьего элемента «И», и через пятый элемент задержки - со вторым входом пятого элемента «И».

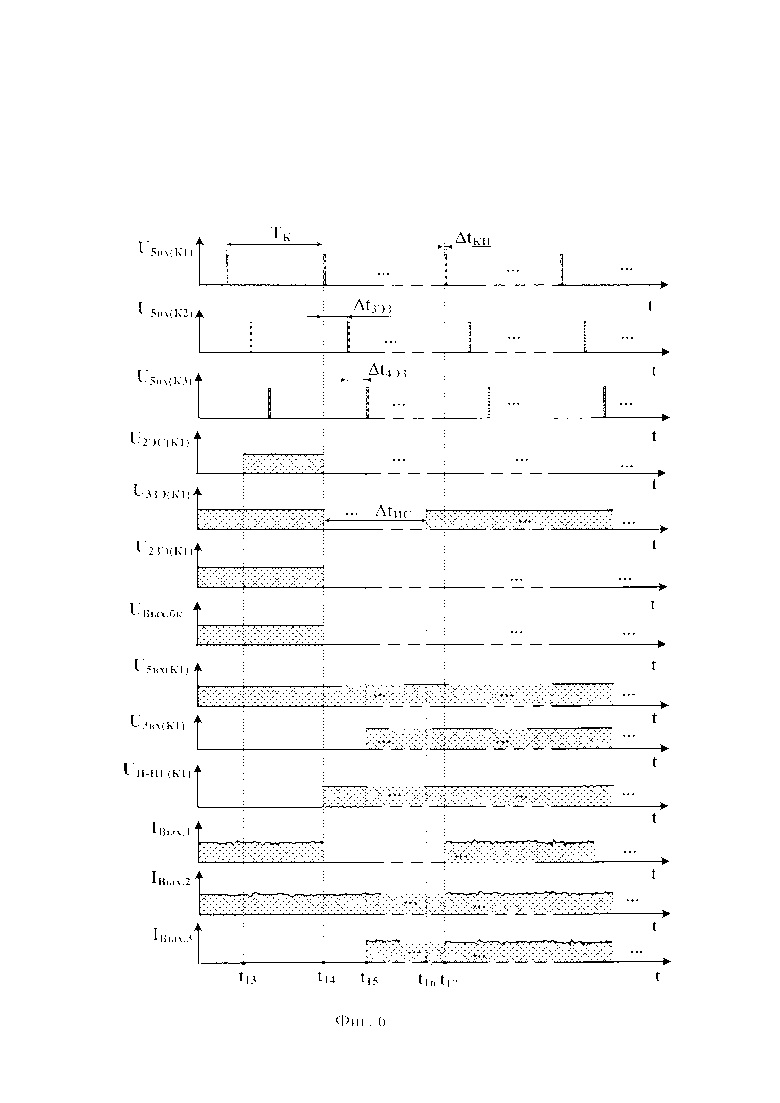

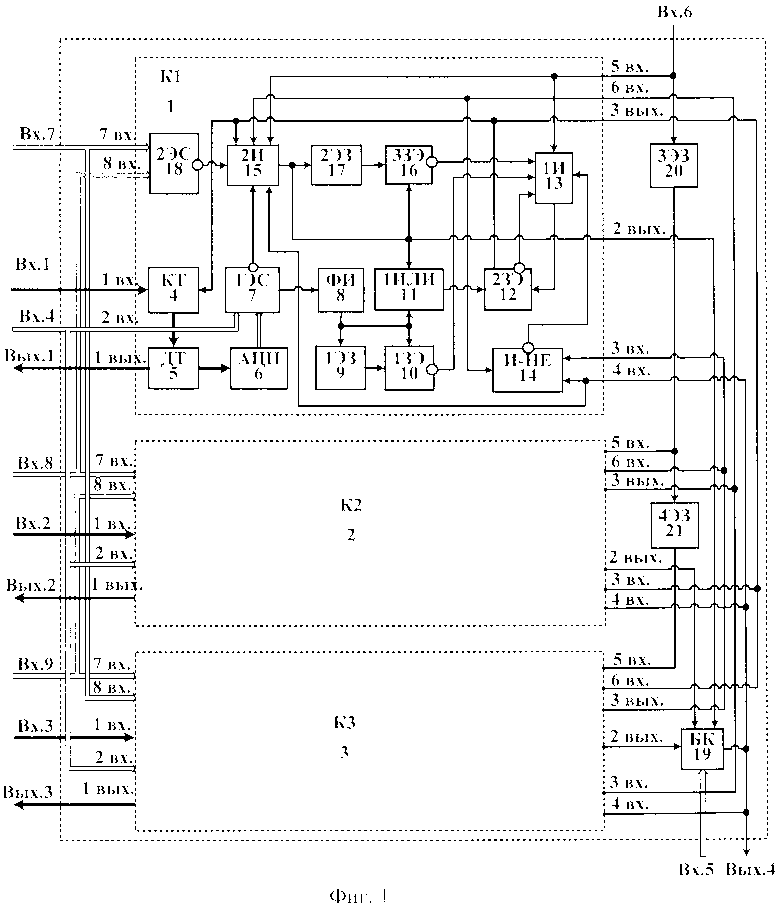

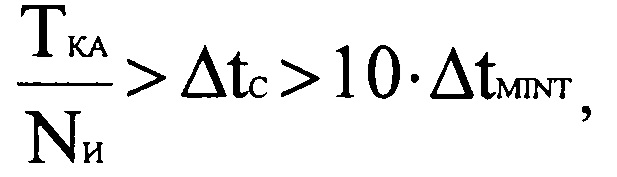

На фиг. 1 - представлена функциональная схема устройства защиты от сбоев и отказов ЭБ космического аппарата, на фиг. 2 - функциональная схема блока контроля, на фиг. 3-циклограмма функционирования устройства при первом включении, на фиг. 4 - циклограмма парирования перегрузки по току в первом канале ЭБ, на фиг. 5 - циклограмма парирования отказов каналов электронного блока, в случае прекращения сравнения информации, поступающей на седьмой и восьмой входы устройства, на фиг. 6 - циклограмма функционирования устройства при превышении счетчиком блока контроля порогового значения.

Предлагаемый способ защиты от сбоев и отказов электронного блока космического аппарата, вызываемых внешними воздействующими факторами реализуется следующим образом.

Перед полетом космического аппарата, по паспортным данным или по результатам экспериментов определяют предельные токи, при которых каналы электронного блока сохраняют работоспособность. Кроме того, определяют максимально возможный ток, который может потреблять каждый канал электронного блока во время функционирования в составе космического аппарата, а также допустимое гарантированное количество повторных включений электронного блока, при котором он сохраняет работоспособность.

После этого в СДКУ, реализованной в виде программного обеспечения БЦВК, задают пороговое значение тока перегрузки одного канала электронного блока в диапазоне:

где: IМАХ - максимально возможный ток, который может потреблять каждый канал электронного блока во время функционирования в составе космического аппарата,

- предельный ток, при котором каналы ЭБ сохраняют работоспособность,

- предельный ток, при котором каналы ЭБ сохраняют работоспособность,

- пороговое значение тока перегрузки в канале ЭБ.

- пороговое значение тока перегрузки в канале ЭБ.

Определяют период вращения космического аппарата по орбите вокруг Земли, на которой он должен функционировать. Далее анализируют характер возможных внешних воздействий на различных участках орбиты, в том числе, возможные излучения, нагрев элементов ЭБ в зависимости от ориентации КА относительно направления на Солнце. В соответствии с данными анализа разбивают период оборота космического аппарата вокруг Земли на фиксированные интервалы времени, которые определяются ориентацией космического аппарата относительно Солнца и планет, как:

где: NИ - количество интервалов времени, на которые разбивают период вращения космического аппарата вокруг Земли.

Время, необходимое для снижения потенциалов на элементах ЭБ, обладающих емкостно-индуктивными связями, до уровня, при котором тиристорный эффект исчезает, всегда превышает в несколько раз время, через которое можно выполнять повторное включение после простого отключения блока, так как требуется более глубокий разряд потенциалов на указанных элементах ЭБ. Время, через которое допускается повторное включение ЭБ, после отключения, обычно указывается в его паспортных данных. В то же время задержка на включение канала при перегрузке по току всегда на порядок и менее времени сброса, то есть:

Далее по паспортным данным, либо по результатам экспериментов определяют минимально допустимые времена, при которых допускается включение канала электронного блока после его отключения при отсутствии и при наличии перегрузки по току, вызванной тиристорным эффектом, при этом задают соответствующие пороговые значения задержек на включение, как:

где: ΔtMIN - минимальное время, при котором допускается включение канала электронного блока после его отключения при отсутствии перегрузок по току, ΔtПТ - пороговое значение задержки на включение канала при перегрузке по току, ΔtИС - пороговое значение задержки на включение канала при информационном сбое, ΔtMINT - минимальное время, при котором допускается включение канала электронного блока после его отключения при наличии перегрузки по току, вызванной тиристорным эффектом,

Задают пороговое значение количества включений каналов ЭБ на одном интервале времени сброса, кратное трем, округленное в меньшую сторону до целого числа, в диапазоне:

где: NП - пороговое значение количества включений всех каналов на одном интервале времени сброса,

NГ - гарантированное количество повторных включений ЭБ, при котором он сохраняет работоспособность,

- знак округления в меньшую сторону до целого числа. Задают интервал времени сброса, в диапазоне:

- знак округления в меньшую сторону до целого числа. Задают интервал времени сброса, в диапазоне:

где ΔtС - интервал времени сброса,

ТКА - период оборота космического аппарата вокруг Земли.

Задают период контроля, как:

где: ТК - период контроля.

Перед началом управления включают первый и второй каналы ЭБ. Во время функционирования КА измеряемые значения токов потребления каждым каналом ЭБ преобразуют в соответствующие коды и передают в СКДУ. Кроме того, в каналах ЭБ осуществляют преобразование управляющих кодов, поступающих из системы диагностического контроля и управления в команды управления бортовой системой. На каждом периоде контроля преобразуют поступающие из каналов ЭБ дискретные и аналоговые сигналы, формируемые бортовой системой в коды, которые поочередно опрашиваются системой диагностического контроля и управления.

Возникающие отказы парируются следующим образом. Отключают канал, ток потребления которого превышает пороговое значение, при этом начинают для него отсчет задержки на включение при перегрузке по току. На каждом периоде контроля при отсутствии сигнала отказа, если одновременно включены два канала, в порядке опроса, поочередно сравнивают поступающие из двух каналов ЭБ коды. Если указанные коды, из включенных первого и второго, или второго и третьего, или третьего и первого каналов ЭБ отличаются, отключают, соответственно, первый, второй или третий канал. Сбрасывают в момент окончания интервала времени сброса ΔtС подсчитанное количество включений каналов ЭБ, если оно не достигает порогового значения NП, а при достижении порогового значения NП формируют сигнал отказа системы. При наличии сигнала отказа прекращают отключение каналов по отсутствию сравнения кодов двух включенных каналов. Начиная с момента отключения канала, отсчитывают для него задержку на включение канала при информационном сбое, при этом в момент отключения канала увеличивают на единицу подсчитываемое количество включений каналов. Если при отсутствии сигнала отказа число включенных каналов не более одного, а при наличии указанного сигнала не более двух, включают на текущем или последующих периодах контроля в порядке опроса канал, для которого отсутствует отсчет интервалов времени задержки на включение канала при перегрузке по току и при информационном сбое.

Требуется отметить, что функциональные алгоритмы, реализованные в СДКУ, обеспечивая управление БС при сбоях и отказах, полученных в одном периоде контроля, не реагируют немедленно, так как в указанных алгоритмах решаются задачи прогнозирования, кроме того, для достоверности функциональный контроль может осуществляться по сигналам, получаемым от других систем. В связи с этим сбой в течение одного или двух периодах контроля не влияет на функционирование БС.

Устройство защиты от сбоев и отказов электронного блока космического аппарата, вызываемых внешними воздействующими факторами (фиг. 1), содержит первый 1 (1К), второй 2 (2К) и третий 3 (3К) каналы, которые идентичны, при этом каждый канал, содержит коммутатор тока 4 (КТ), первый вход которого является первым входом канала (1 вх.), а выход соединен со входом датчика тока 5 (ДТ), первый выход которого является первым выходом канала (1 вых.), а второй выход соединен через аналого-цифровой преобразователь 6 (АЦП) с первым входом первого элемента сравнения 7 (1ЭС), второй вход которого является вторым входом канала (2 вх.), при этом дополнительно первый, прямой выход первого элемента сравнения 7 (1ЭС) соединен со входом формирователя импульсов 8 (ФИ), выход которого соединен через первый элемент задержки 9 (1ЭЗ) с первым входом сброса первого запоминающего элемента 10 (1ЗЭ), а также напрямую с его вторым установочным входом и с первым входом первого элемента «ИЛИ» 11 (1ИЛИ), выход которого, соединен с первым входом сброса второго запоминающего элемента 12 (2ЗЭ), первый инверсный выход и второй вход установки которого соединены, соответственно, с первым входом и выходом первого элемента «И» 13 (1И), второй и третий входы которого, в свою очередь, соединены, соответственно, с инверсным выходом первого запоминающего элемента 10 (1ЗЭ) и выходом элемента «И-НЕ» 14 (И-НЕ), первый вход которого являются третьим (3 вх.), а второй вход четвертым входом канала (4 вх.) и соединен с первым входом второго элемента «И» 15 (2И), выход которого является вторым выходом канала (2 вых.) и соединен со вторым входом первого элемента «ИЛИ» 11 (1ИЛИ), с первым установочным входом, а через второй элемент задержки 17 (2ЭЗ) -со вторым входом сброса третьего запоминающего элемента 16 (3ЭЗ), инверсный выход которого соединен с четвертым входом первого элемента «И» 13 (1И), пятый вход которого является пятым входом канала (5 вх.) и соединен со вторым входом второго элемента «И» 15 (2И), третий вход которого является шестым входом канала (6 вх.) и соединен с третьим входом элемента «И-НЕ» 14 (И-НЕ), четвертый вход второго элемента «И» 15 (2И) является третьим выходом канала (3 вых.) и соединен со вторым прямым выходом второго запоминающего элемента 12 (2ЗЭ), а также соединен со вторым входом коммутатора тока 4 (КТ), пятый и шестой входы второго элемента «И» 15 (2И) соединены, соответственно, со вторым инверсным выходом первого элемента сравнения 7 (1ЭС) и с инверсным выходом второго элемента сравнения 18 (2ЭС), первый и второй входы которого являются, соответственно, седьмым (7 вх.) и восьмым (8 вх.) входами канала, при этом первые входы (1 вх.) и первые выходы (1 вых.) первого 1 (1К), второго 2 (2К) и третьего 3 (3К) каналов являются, соответственно, первым (Вх.1), вторым (Вх.2) и третьим (Вх.3) входами и первым (Вых.1), вторым (Вых.2), третьим (Вых.3) выходами устройства, вторые входы (2 вх.) всех указанных каналов соединены между собой и являются четвертым входом устройства (Вх.4.), а вторые выходы (2 вых.) первого 1 (1К), второго 2 (2К) и третьего 3 (3К) каналов связаны, соответственно, с первым, вторым и третьим входами блока контроля 19 (БК), четвертый вход которого является пятым входом устройства (Вх. 5), а выход связан с четвертыми (4 вх.), связанными между собой, входами всех указанных каналов и является четвертым выходом устройства (Вых. 4), при этом третий вход (3 вх.) первого канала 1(1К) связан с шестым входом (6 вх.) второго канала 2(2К) и третьим выходом (3 вых.) третьего канала 3 (3К), третий вход которого связан с шестым входом (6 вх.) первого канала 1(1К), и третьим выходом (3 вых.) второго канала 2 (2К), третий вход которого (3 вх.) связан с шестым входом (6 вх.) третьего канала 3(3К) и третьим выходом (3 вых.) первого канала 1 (1К), пятый вход (5 вх.) которого является шестым входом устройства (Вх. 6), и связан через третий элемент задержки 20 (3ЭЗ) с пятым входом (5 вх.) второго канала 2 (2К) и входом четвертого элемента задержки 21 (4ЭЗ), выход которого, в свою очередь, связан с пятым входом (5 вх.) третьего канала 3 (3К), при этом седьмой вход (7 вх.) первого канала 1(1К) является седьмым входом устройства (Вх. 7) и связан, при этом, с восьмым входом (8 вх.) третьего канала 3 (3К), седьмой вход (7 вх.) которого является девятым входом устройства (Вх. 9) и связан с восьмым входом (8 вх.) второго канала 2(2К), седьмой вход (7 вх.) которого связан с восьмым входом (8 вх.) первого канала 1 (1К) и является восьмым входом устройства (Вх. 8).

Блок контроля 19 (БК) (фиг. 2) содержит второй элемент «ИЛИ» 22 (2ИЛИ), первый, второй и третий входы которого являются, соответственно, первым (1 вх.бк), вторым (2 вх.бк) и третьим (3 вх.бк) входами блока контроля 19 (БК), а его выход связан с первыми входами третьего 23 (3И) и четвертого 24 (4И) элементов «И», выход последнего связан с первым счетным входом счетчика 25 (СЧ), выход которого, в свою очередь, соединен с первым входом третьего элемента сравнения 26 (3ЭС), второй вход которого является четвертым входом (4 вх.бк) блока контроля 19 (БК), а инверсный выход является выходом блока контроля 19(БК), соединен со вторыми входами третьего 23 (3И) и четвертого 24 (4И) элементов «И», а также с первым входом пятого элемента «И» 27 (5И), выход которого, в свою очередь, соединен со вторым входом сброса счетчика 25 (СЧ) и первым входом сброса четвертого запоминающего элемента 28 (4ЗЭ), инверсный выход которого, в свою очередь, соединен с третьим входом третьего элемента «И» 23 (3И), а второй вход соединен с выходом третьего элемента «И» 23 (3И) и через пятый элемент задержки 29 (5ЭЗ) - со вторым входом пятого элемента «И» 27 (5И).

Устройство, реализующее предложенный способ для одного канала электронного блока, представленное на фиг. 1 и фиг. 2 функционирует следующим образом.

Перед началом функционирования на седьмой (Вх.7), восьмой (Вх.8) и девятый (Вх.9.) входы устройства подаются токи питания, которые поступают, соответственно, на первые входы первого 1 (1К), второго 2(2К) и третьего 3(3К) каналов устройства.

На четвертый вход устройства (Вх.4) задают код, соответствующий пороговому значению тока перегрузки канала ЭБ, определенный по формуле (1), который поступает на вторые входы (2 вх.) всех указанных каналов.

На пятый вход устройства (Вх.5) подают код определенный по формуле (5), поступающий на четвертый вход блока контроля (4 вх.бк), соответствующий пороговому значению количества включений всех каналов на одном интервале времени сброса NП.

В исходном состоянии первые 10 (1ЗЭ), вторые 12 (2ЗЭ) и третьи 16 (3ЗЭ) запоминающие элементы первого 1(1К), второго 2(2К) и третьего 3(3К) каналов находятся в сброшенном состоянии, при этом на инверсных выходах указанных элементов, а также с выхода (Вых.бк) блока контроля 19(БК) формируются логические «1», а на вторых, прямых выходах первого запоминающего элемента 10 (1ЗЭ) во всех указанных каналах, формируются логические «0».

В каждом из каналов логический «0» с прямого выхода первого запоминающего элемента 10 (1ЗЭ) поступает на второй, управляющий вход коммутатора тока 4 (КТ), который соединен с датчиком тока (ДТ5). На первом выходе указанного датчика тока (ДТ) в каждом канале, который является первым его выходом, соответственно, на выходах первого 1(1К), второго 2(2К) и третьего 3(3К) каналов, и также, соответственно, на первом (Вых.1), втором (Вых.2) и третьем (Вых.3) выходах устройства, формируется нулевое значение тока.

На третий (3 вх.) и шестой (6 вх.) входы каждого канала, соответственно на первый и второй входы элементов «И-НЕ» (14) этих каналов поступают логические «0» с третьих выходов (3 вых.) двух других каналов, которые являются выходами вторых запоминающих элементов 12(2ЗЭ) указанных каналов.

На фиг. 2 представлена функциональная схема блока контроля.

Перед началом управления в блоке контроля 19(БК) (фиг. 2) четвертый запоминающий элемент 28 (4ЗЭ) находится в сброшенном состоянии, при этом на его инверсном выходе формируется логическая «1» а содержимое счетчика 25 (СЧ) равно нулю. На первый вход третьего элемента сравнения 26(3ЭС), поступает код равный нулю, соответствующий содержимому счетчика 25(СЧ). На четвертый вход (4 вх.бк) блока контроля 19 (БК), который связан со вторым входом указанного элемента поступает код, соответствующий допустимому количеству повторных включений всех каналов после их отключения, определенный по формуле (5) NП. При этом на инверсном выходе третьего элемента сравнения 26 (3ЭС), формируется логическая «1», которая поступает на вторые входы третьего 23 (3И) и четвертого 24 (4И) элементов «И» и соответственно на выход (Вых.бк) блока контроля 19 (БК), с которого поступает на четвертые входы (4 вх.) первого 1 (1К), второго 2 (2К) и третьего 3 (3К) каналов, соответственно на вторые входы элемента «И-НЕ» 14 (И-НЕ) каждого канала.

Во время управления импульс, сформированный на первом (1 вх. бк), втором (2 вх. бк) или третьем (3 вх. бк) входах блока контроля 19 (БК), поступает, соответственно, на первый, второй или третий входы второго элемента «ИЛИ» 22 (2ИЛИ). Далее с выхода указанного элемента импульс поступает на первые входы третьего 23 (3И) и четвертого 24 (4И) элементов «И». Поскольку на вторые входы данных элементов с выхода третьего элемента сравнения 26 (3ЭС) поступает логическая «1», на выходе третьего элемента «И» 23(3И) формируется импульс, поступающий на вход пятого элемента задержки 29 (5ЭЗ), длительность которой определена по формуле (6), и на второй вход четвертого запоминающего элемента 28 (4ЗЭ), который устанавливает на его инверсном выходе состояние логического «0», поступающий на третий вход третьего элемента «И» 23(3И) и, таким образом, блокирует формирование последующих импульсов на выходе данного элемента. Кроме того, поступивший на первый вход логического элемента «И» 24 (4И) импульс с его выхода далее поступает на первый, счетный вход счетчика 25 (СЧ), при этом содержимое счетчика увеличивается на единицу. С выхода пятого элемента задержки 29 (5ЭЗ) на второй вход пятого элемента «И» 27 (5И) импульс поступит через время задержки соответствующему интервалу времени сброса ΔtС,, определенному по формуле (6), при этом, если на первом входе имеется логическая «1», указанный импульс поступит далее с пятого элемента «И» 27 (5И) на первый вход сброса четвертого запоминающего элемента 28 (4ЗЭ) и установит на его инверсном выходе состояние логической «1». Одновременно, указанный импульс, поступит на второй вход счетчика 25 (СЧ) и сбросит его.

В случае, если поступивший на первый (1 вх. бк), второй (2 вх. бк) или третий (3 вх. бк) входы блока контроля 19 (БК) импульс, через второй элемент «ИЛИ» 22(2ИЛИ) и четвертый элемент «И» 24 (4И) поступает на первый вход счетчика 25 (СЧ) и устанавливает его значение равное коду, поступающему на четвертый вход (4 вх.бк) блока контроля 19 (БК), то на инверсном выходе третьего элемента сравнения 26 (3ЭС), формируется логический «0», который поступает на вторые входы третьего 23(3И) и четвертого 24 (4И) элементов «И», а также на первый вход пятого элемента «И» 27 (5И), при этом поступление импульсов на первый и второй входы счетчика 25 (СЧ), на вход пятого элемента задержки 29 (5ЭЗ), а также на установку в состояние логической «1» четвертого запоминающего элемента 28(4ЗЭ) блокируются. Сформированный на выходе (Вых.бк) блока контроля 19(БК) логический «0» далее поступает на четвертые входы (4 вх.) первого 1 (1К), второго 2 (2К) и третьего 3(3К) каналов устройства, при этом контроль по совпадению информации, поступающей на седьмые (7вх.) и восьмые (8вх.) входы всех каналов, соответственно, на первый второй входы вторых элементов сравнения 18 (2ЭС) блокируется на втором элементе «И» 15 (2И), так как на первый вход указанного элемента в каждом канале поступает логический «0» с соответствующего четвертого входа (4 вх.) каждого канала, сформированный на выходе блока контроля 19 (БК).

Одновременно, на выходе элемента «И-НЕ» 14 (И-НЕ) каждого канала формируется логическая «1», которая поступает на третий вход первого элемента «И» (1И), при этом, в случае отключения любого из каналов, при отсутствии задержки на включение при перегрузке по току ΔtПT, определенной по формуле (4) осуществляется его включение. То есть включаются все каналы, а отключение осуществляется только при перегрузках по току.

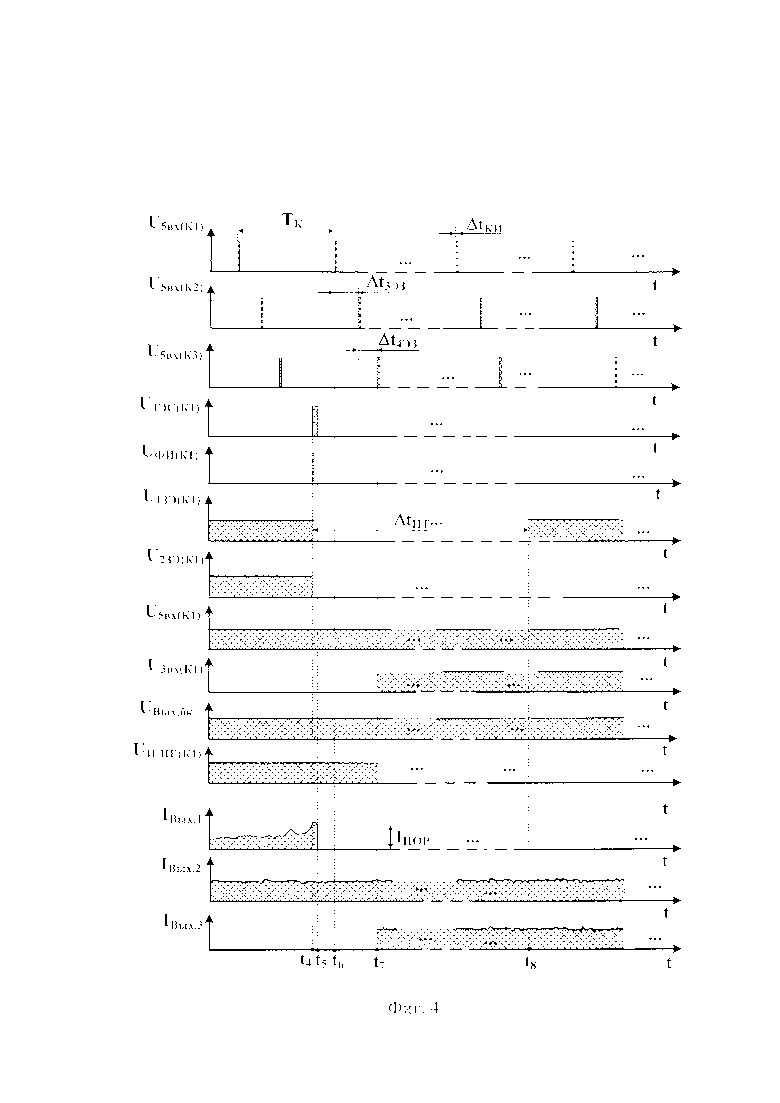

Циклограмма функционирования устройства при первом включении представлена на фиг. 3. Обозначения на фиг. 3:

t - время,

Тк - период контроля,

ΔtКИ - импульс контроля,

Δt3ЭЗ, Δt4ЭЗ - соответственно, длительности задержек на третьем 20 (3ЭЗ) и четвертом 21 (4ЭЗ) элементах задержки),

U5ВХ(К1), U5ВХ(К2),U5BX(K3) - оответственно, напряжения на пятых входах(5 вх.) первого 1 (1К), второго 2 (2К) и третьего 3 (3К) каналов устройства,

UВых..бк - напряжение на выходе блока контроля 19 (БК),

UИ-НЕ(К1), UИ-НЕ(К2), UИ-НЕ(К3) соответственно, напряжения на выходах элементов «И-НЕ» 14 (И-НЕ) первого 1 (1К), второго 2 (2К) и третьего второго 3 (3К) каналов устройства,

U2ЗЭ(К1), U2ЗЭ(К2), U2ЗЭ(К3) - соответственно, напряжение на выходах вторых запоминающих элементов 12 (2ЗЭ) первого 1 (1К), второго 2 (2К) и третьего 3 (3К) каналов устройства,

IВых..1, IВых..2, IВых.3 - соответственно, токи на первом (Вых.1), втором (Вых.2) и третьем (Вых.3) выходах устройства,

t1, t2, t3 - соответственно, моменты поступления импульсов контроля на пятые входы (5 вх.) первого 1(1К), второго 2(2К) и третьего 3(3К) каналов устройства.

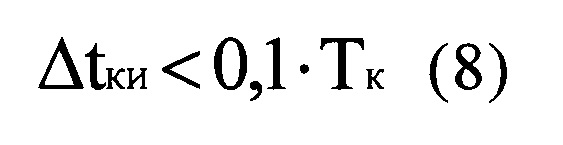

Функционирование устройства начинается с момента поступления импульсов из СДКУ на шестой вход (Вх.6) устройства с периодом контроля Тк длительностью на порядок и менее длительности периода контроля, то есть:

где ΔtКИ - длительность импульса контроля, Тк - период контроля,

Перед началом управления, до поступления импульса контроля в момент t1 на шестой вход устройства (Вх. 6), на первый вход первого элемента «И» 13 (1И) первого канала 1 (1К) поступает логическая «1» с первого, инверсного входа второго запоминающего элемента 12 (2ЗЭ), который находится в сброшенном состоянии. На второй и четвертый входы первого элемента «И» 13 (1И) первого канала 1(1К) поступает логическая «1» с инверсного выхода, соответственно, первого 10 (1ЗЭ) и третьего 16 (3ЗЭ) и запоминающих элементов указанного канала, так как они также находятся в сброшенном состоянии. На третий вход первого элемента «И» 13 (1И), с выхода элемента «И-НЕ» 14(И-НЕ) первого канала 1(1К) также поступает логическая «1», так как на первый и третий входы указанного логического элемента поступают логические «00» с третьего (3 вх.) и шестого (6 вх.) входов данного канала, которые формируются на вторых, прямых выходах вторых запоминающих элементов 12(2ЗЭ), поступающих, с третьих выходов (3 вых.) третьего 3 (3К) и второго 2 (2К) каналов соответственно.

На каждом цикле контроля импульс ТК задаваемый из СДКУ на шестой вход устройства (Вх.6) поступает на пятый вход (5 вх.) первого канала 1 (1К), далее, через третий элемент задержки 20 (3ЭЗ) поступает на пятый вход (5 вх.) второго канала 2 (2К), затем, через четвертый элемент задержки 21 (4ЭЗ) на пятый вход (5 вх.) третьего канала 3 (3К), при этом сумма длительностей третьего 20 (3ЭЗ) и четвертого 21 (4ЭЗ) элементов задержки составляет величину менее длительности периода контроля, то есть:

(Δt3ЭЭ+Δt4ЭЭ)<ТК (9)

где (Δt3ЭЗ, (Δt3ЭЗ - соответственно, длительности задержек импульсов на третьем 20 (3ЭЗ) и четвертом 21 (4ЭЗ) элементах задержки.

Поступивший в момент t1 из СДКУ на шестой вход (6 вх.) устройства импульс контроля длительностью ΔtКИ приходит на пятый вход (5 вх.) первого канала 1 (1К) и далее поступает на пятый вход второго элемента «И» 15 (2И) данного канала. Поскольку на входы второго элемента «И» 15 (2И) с первого по четвертый поступают логические «1», на его выходе формируется импульс, поступающий на второй вход установки второго запоминающего элемента 12 (2ЗЭ), который по переднему фронту импульса устанавливается в состояние логической «1».

Со второго, прямого выхода второго запоминающего элемента 12 (2ЗЭ) первого канала 1 (1К) логическая «1» поступает на второй, управляющий вход коммутатора токов 4(КТ) первого канала 1(1К), при этом ток, поступающий на первый вход указанного коммутатора, далее, через датчик тока 5 (ДТ) поступает на его выход и, соответственно, на первый выход (1 вых.) первого канала устройства 1(1К), который является первым выходом устройства (Вых.1). При этом осуществляется подача питания в первый канал ЭБ. Кроме того, логическая «1» со второго, прямого выхода второго запоминающего элемента 12 (2ЗЭ) первого канала 1(1К) поступает через третий выход (3 вых.) первого канала 1(1К) на третий вход (3 вх.) второго канала 2(2К) и шестой вход (6 вх.) третьего канала 3(3К) устройства.

До момента t2 на первый вход первого элемента «И» 13 (1И) второго канала 2 (2К) поступает логическая «1» с первого, инверсного входа второго запоминающего элемента 12 (2ЗЭ) этого канала, который находится в сброшенном состоянии. На второй и четвертый входы первого элемента «И» 13 (1И) второго канала 2(2К) логическая «1» поступает с инверсного выхода, соответственно, первого 10(1ЗЭ) и третьего 16 (3ЗЭ) и запоминающих элементов указанного канала, так как они также находятся в сброшенном состоянии. На третий вход первого элемента «И» 13 (1И) второго канала 2(2К) логическая «1» поступает с выхода элемента «И-НЕ» 14 (И-НЕ) данного канала, так как на третий входы указанного логического элемента поступает логический «0» с шестого входа (6 вх.) данного канала, которая формируются на третьем выхода (3 вых.) третьего 3 (3К) канала со второго, прямого выхода находящегося в состоянии логического «0» второго запоминающего элемента 12(2ЗЭ). В момент t2 импульс длительностью ΔtКИ, с выхода третьего элемента задержки 20 (3ЭЗ), поступает на пятый вход (5 вх.) второго канала 2 (2К) и, соответственно, на пятый вход второго элемента «И» 15 (2И) указанного канала. Поскольку на входах с первого по четвертый элемента «И» 15 (2И) второго канала 2 (2К) канала формируются логические «1», поступивший на его пятый вход импульс далее, с его выхода поступает на второй вход установки второго запоминающего элемента 12 (2ЗЭ) данного канала,. При этом по переднему фронту импульса второй запоминающий элемент 12 (2ЗЭ) устанавливается в состояние логической «1». Со второго, прямого выхода второго запоминающего элемента 12 (2ЗЭ) второго канала 2 (2К) сформированная логическая «1» поступает на второй, управляющий вход коммутатора токов 4 (КТ) второго канала 2(2К), в результате этого ток, поступающий на первый вход указанного коммутатора, через датчик тока 5 (ДТ) поступает на его выход и, далее на первый выход (1 вых.) второго канала устройства 2(2К), соответственно, на второй выход устройства (Вых.2). При этом осуществляется подача питания во второй канал ЭБ. Кроме того, логическая «1» со второго, прямого выхода второго запоминающего элемента 12 (2ЗЭ) данного канала поступает через его третий выход (3 вых.) на третий вход (3 вх.) третьего канала 3(3К) и шестой вход первого канала 1(1К) устройства.

В момент t3, с выхода четвертого элемента задержки 21 (4ЭЗ), импульс, поступает на пятый вход (5 вх.) третьего канала 3 (3К), соответственно, на четвертый вход второго элемента «И» 15 (2И) третьего канала 3 (3К). В момент t3 на прямых выходах вторых запоминающих элементов 12 (2ЗЭ) первого 1(1К) и второго 2(2К) каналов и на выходе (Вых. бк) блока контроля 19 (БК) формируются логические «1». Указанные логические «1» поступают, соответственно, на шестой (6 вх.), третий (3 вх.), четвертый (4 вх.) и входы третьего канала 3 (3К). При этом на выходе элемента «И-НЕ» 14 (И-НЕ) третьего канала 3(3К) формируется логический «0».

Сформированный логический «0» с выхода элемента «И-НЕ» 14 (И-НЕ) третьего канала 3(3К) поступает на второй вход первого элемента «И» 13 (1И) данного канала и блокирует приходящий в момент t3 импульс на установку второго запоминающего элемента 12 (2ЗЭ) третьего канала 3(3К), который остается в состоянии логического «0», при этом ток на первый выход (1 вых.) третьего канала 3 (3К), соответственно, на третий выход устройства (Вых.3) не поступает.

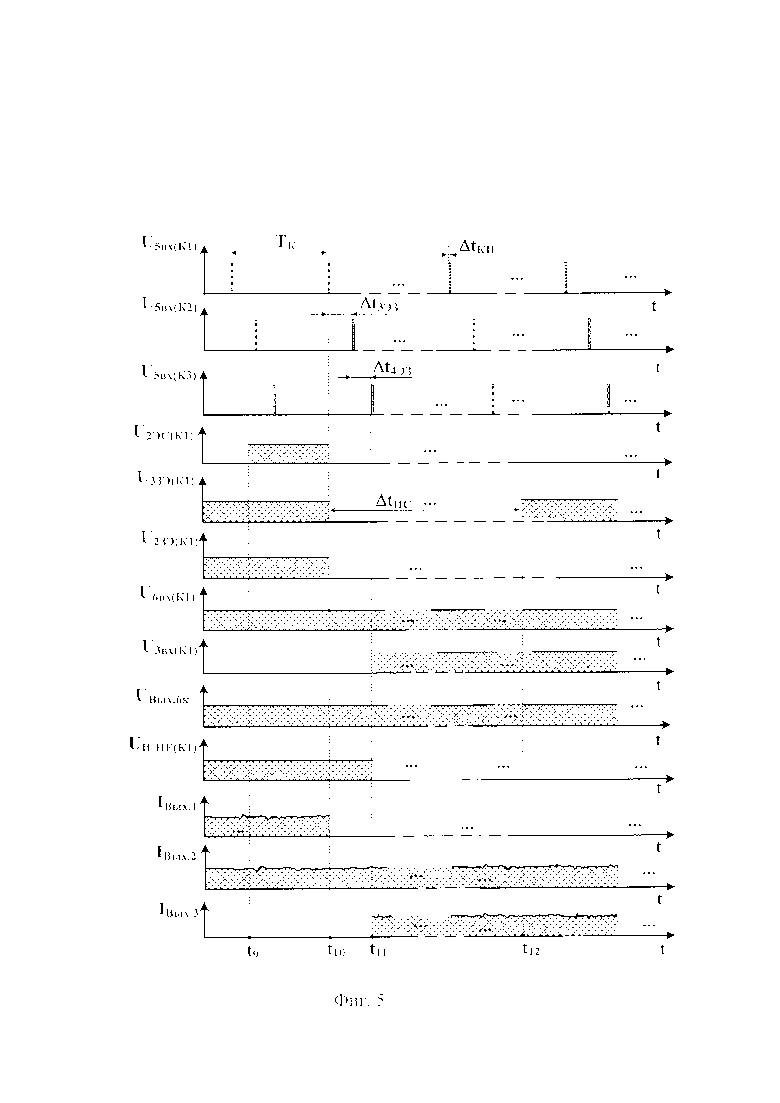

На фиг. 4 представлена циклограмма парирования перегрузки по току в первом канале ЭБ. Обозначения на фиг. 4:

1ПОР - пороговое значение тока, поступающего на первый вход первого канала,

U1ЭС(К1) - напряжение на прямом выходе первого элемента сравнения 7 (1ЭС) первого канала 1(1К),

UФИ(К1) - напряжение на выходе формирователя импульсов 8 первого элемента сравнения 7 (1ЭС) первого канала 1(1К),

U1ЗЭ(К1) напряжение на выходе первого запоминающего элемента 10 (1ЗЭ) первого канала 1(1К),

t4 - момент времени начала превышения током порогового значения IПОР в первом канале 1(1К),

t5 - момент отключения первого канала при перегрузке по току,

t6 - момент выключения первого канала,

t7 - момент включения третьего канала,

t8 - момент окончания первого интервала времени.

В первом канале 1(1К) формируемый на втором выходе датчика тока 5 (ДТ) ток IВых.1, при помощи аналого-цифрового преобразователя 6 (АЦП) преобразуется в код, который поступает на первый вход первого элемента сравнения 7(1ЭС). На второй вход указанного элемента поступает код, соответствующий пороговому значению тока со второго входа (2 вх.) первого 1 (1К) канала, соответственно, с четвертого входа устройства (Вх.4). До момента t4 первый 1(1К) и второй 2(2К) каналы устройства находятся во включенном состоянии, при этом токи с первого (Вх.1) и второго (Вх.2) устройства входов поступают, через коммутаторы 4 (КТ) и датчики тока 5 (ДТ) указанных каналов, соответственно, на первый (Вых. 1) и второй (Вых. 2) выходы устройства. В момент t4 поступающий на второй выход датчика тока 5 (ДТ) первого канала 1(1К) ток IВых.1. i достигает порогового значения IПОР, то есть возникает перегрузка по току первого канала 1(1К). Указанный ток преобразуется аналого-цифровым преобразователем 6 (АЦП) первого канала 1(1К) в код, который поступает на первый вход первого элемента сравнения 7(1ЭС) первого канала 1 (1К). Начиная с момента t4, до момента t5, на выходе аналого-цифрового преобразователя 6 (АЦП) формируется код, соответствующий превышающий пороговое значение, соответствующий измеренному датчиком 5 (ДТ) току. Поскольку код, поступивший с выхода аналого-цифрового преобразователя 6 (АЦП) первого канала 1(1К) на первый вход первого элемента сравнения 7(1 ЭС) данного канала превышает пороговое значение кода, поступающего на его второй вход, на первом, прямом выходе указанного элемента сравнения формируется логическая «1», соответственно, на втором, инверсном выходе - логический «0». Сформированный на втором, инверсном выходе первого элемента сравнения 7(1 ЭС) логический «0» поступает на пятый вход второго элемента «И» 15 (2И) первого канала 1(1К). При этом импульс контроля ΔtКИ, поступающий на второй вход второго элемента «И» 15 (2И) с пятого входа (5 вх.) первого канала 1 (1К), соответственно, с шестого входа устройства (Вх.6) не поступает на его выход начиная с момента перегрузки t4 до момента t5. Данная задержка обусловлена задержками на аналого-цифровом преобразователе 6 (АЦП) и коммутаторе 4 (КТ) первого канала 1(1К). В то же время, в момент t4 сформированная на первом, прямом выходе первого элемента сравнения 7 (1ЭС) первого канала 1 (1К) логическая «1» поступает на вход формирователя импульсов 8 (ФИ) первого канала 1 (1К), на выходе которого формируется короткий импульс, не превышающий ΔtКИ, который поступает на вход первого элемента задержки 9 (1ЭЗ), длительность которой ΔtПТ определена по формуле (4), на второй вход установки первого запоминающего элемента 10 (1ЗЭ), а также на первый вход первого элемента «ИЛИ» 11 (1ИЛИ). На инверсном выходе первого запоминающего элемента 10 (1ЗЭ) первого канала 1 (1К) формируется логический «0», который поступает на второй вход первого элемента «И» 13 (1И) первого канала 1 (1К), начиная с момента t4 сброса указанного первого запоминающего элемента 10 (1ЗЭ) до момента t8.

До момента t8 на втором входе первого элемента «И» 13 (1И) первого канала 1 (1К) формируется логический «0», который блокирует импульсы контроля поступающие на пятый вход указанного элемента, выход которого связан со вторым входом установки второго запоминающего элемента 12 (2ЗЭ). Таким образом, в течение времени задержки ΔtПТ, определенной по формуле (4), обусловленной перегрузками по току; включение первого канала 1(1К) блокируется, так как импульс контроля, длительностью ΔtКИ поступивший в момент t6 на шестой вход устройства (Вх.6), соответственно, на пятый вход (5 вх.) первого канала 1 (1К) и пятый вход первого элемента «И» 13 (1И) не поступает на второй вход установки второго запоминающего элемента 12 (2ЗЭ) первого канала 1(1К). Через время Δt3ЭЗ после поступления в момент t6 на вход устройства импульса контроля, с выхода третьего элемента задержки 20 (3ЭЗ) импульс поступает на пятый вход (5 вх.) второго канала 2 (2К), соответственно, на пятый вход первого элемента «И» 13 (1И) второго канала 2(2К). Формирование импульса на выходе второго элемента «И» 15 (2И) второго канала блокируется логическим «0» поступающим на его первый вход с первого, инверсного выхода второго запоминающего элемента 12 (2ЗЭ) второго канала 2(2К), так как указанный канал включен.

На первый вход второго элемента «И» 15 (2И) третьего канала 3 (3К) с первого, инверсного выхода второго запоминающего элемента 12 (2ЗЭ) третьего канала 3(3К) поступает логическая «1», так как канал отключен, при этом указанный запоминающий элемент находится в сброшенном состоянии.

Начиная с момента включения первого канала 1 (IK) t4 на третий вход элемента «И-НЕ» 14 (И-НЕ) данного канала с шестого входа (6 вх.) поступает сигнал логического «0», третьего канала 3 (1К), сформированный на третьем выходе (3 вых.) первого канала 1(1К), который является прямым выходом второго запоминающего элемента (2ЗЭ) первого канала 1(1К). При этом на выходе элемента «И-НЕ» 14 (И-НЕ), соответственно, на третьем входе второго элемента «И» 15 (2И) третьего канала 3 (3К) формируется логическая «1». На второй и четвертый входы второго элемента «И» 15 (2И) третьего канала 3 (3К) логические «1» поступают с инверсных выходов первого 10 (1ЗЭ) и третьего 16 (3ЗЭ) запоминающих элементов третьего канала 3 (3К) так как указанные элементы находятся в сброшенном состоянии. В момент t7 импульс, с выхода четвертого элемента задержки 21 (4ЭЗ) поступает на пятый вход (5 вх.) третьего канала 3 (3К), соответственно, на пятый вход первого элемента «И» 13 (1И) третьего канала 3(3К). Поскольку на входах с первого по четвертый второго элемента «И» 15 (2И) сформированы логические «1», импульс контроля длительностью ΔtКИ проходит на выход первого элемента «И» 13 (1И) третьего канала 3(3К) и далее на второй вход установки второго запоминающего элемента 12 (2ЗЭ) третьего канала 3(3К), в результате чего указанный запоминающий элемент устанавливается в состояние логической «1». Указанная логическая «1» поступает на второй, управляющий, вход коммутатора 4 (КТ), при этом ток поступающий на его первый вход с восьмого входа устройства (Вх.8), соответственно, с первого входа (1 вх.) третьего канала 3 (3К) далее поступает через датчик тока 5 (ДТ) на его выхода, соответственно, на первый выход (1 вых.) третьего канала 3 (3К) который является третьим выходом устройства (3 вых.).

Начиная с момента t4 до момента t8 с инверсного выхода первого запоминающего элемента 10 (1ЗЭ) первого канала 1(1К), в течение времени задержки обусловленной перегрузками по току ΔtПТ, логический «0» поступает на второй вход первого элемента 13 «И» (1И) первого канала 1(1К). При этом блокируются импульсы на установку второго запоминающего элемента 12 (2ЗЭ) первого канала 1(1К), в состояние логической «1», то есть включение коммутатора 4 (КТ) первого канала 1(1К). В момент t8 окончания задержки обусловленной перегрузками пои току ΔtПТ на выходе первого элемента задержки 9 (1ЭЗ) первого канала 1 (1К) формируется импульс, который поступает на первый вход сброса первого запоминающего элемента 10 (1ЗЭ) первого канала 1(1К), при этом на его инверсном выходе формируется логическая «1», которая разрешает формирование импульса на выходе первого элемента «И» 13 (1И) первого канала 1(1К), то есть разрешает включение первого канала 1(1К) в случае, если на его третьем входе будет сформирована логическая «1» в случае, например, отключения второго 2 (2К), или третьего 3(3К) канала.

На фиг. 5 представлена циклограмма парирования отказов каналов электронного блока, в случае прекращения сравнения информации поступающей на седьмой (Вх.7) и восьмой (Вх.8) входы устройства. Обозначения на фиг.5:

ΔtИС - длительность задержки обусловленной сбоем информации,

UВх.6(К1), напряжение на шестом входе первого канала (6 вх),

U3ЗЭ(К1), - напряжения на инверсном выходе третьего запоминающего элемента 3ЗЭ первого канала 1(1К),

UВых..бк - напряжения на выходе (Вых. бк) блока контроля (БК),

UВх.6(К1), UВх.3(К1 UВх.4(К1),) - соответственно, напряжения на шестом (6 вх.), третьем (3 вх.) и четвертом (4 вх.) входах первого канала 1(1К),

t9 - момент времени начала сбоя информации поступающей из

первого и второго каналов на входы второго элемента сравнения

18(2ЭС) в первом канале 1(1К) устройства,

t10 - момент отключения первого канала 1(1К) устройства,

t11 - момент включения третьего канала,

t12 - момент окончания задержки обусловленной сбоем информации.

До момента t9 включены первый 1 (1К) и второй 2(2К) каналы устройства, при этом контроль осуществляется по кодам, поступающим на седьмой (Вх.7) и восьмой (Вх.8) входы устройства, информация из которых поступает, соответственно, на седьмые входы (7 вх.), соответственно, первого 1 (1К) и второго 2 (2К) каналов. Далее информация с указанных входов поступает, соответственно, на первый и второй вход, второго элемента сравнения 18 (2ЭС) первого канала 1(1К), на инверсном выходе которого, в случае ее сравнения, формируется логический «0». На четвертый вход второго элемента «И» 15 (2И) первого канала 1 (1К), логическая «1» поступает со второго, прямого выхода второго запоминающего элемента 12 (23Э) поскольку первый канал 1 (1К) включен. На третий вход второго элемента «И» 15 (2И) первого канала 1 (1К) логическая «1» поступает с шестого входа (6 вх.) первого канала 1 (1К), так как на указанный вход поступает информация с третьего выхода (3 вых.) второго канала 2(2К), который является вторым прямым выходом второго запоминающего элемента 12 (2ЗЭ) второго канала 2 (2К), поскольку указанный канал включен. Начиная с момента t9 коды, поступающие на седьмой (Вх.7) и восьмой (Вх.8) информационные входы устройства отличаются, при этом на инверсном выходе второго элемента сравнения 18 (2ЭС) первого канала 1 (1К) формируется логическая «1», которая поступает на шестой вход второго элемента «И» 15 (2И) первого канала 1 (1К), а на его пятый вход поступает логическая «1» с выхода первого элемента сравнения 7 (1ЭС) первого канала 1 (К 1), так как перегрузка по току в первом канале 1(1 К) отсутствует.

На первый вход второго элемента «И» 15 (2И) первого канала 1 (1К) логическая «1» поступает с четвертого входа (4 вх.) первого канала 1 (1К), которая формируется на выходе (Вых. бк) блока контроля 19 (БК), поскольку содержимое счетчика 25 (СЧ) указанного блока не превышает порогового значения, подаваемого на его четвертый вход (4 вх.бк), соответственно на пятый вход устройства (Вх.5).

На третий вход второго элемента «И» 15 (2И) второго канала 2 (2К) логический «0» поступает с шестого входа (6 вх.) второго канала 2 (2К), так как на указанный вход поступает информация с третьего выхода (3 вых.) третьего канала 3(3К), который является вторым, прямым выходом второго запоминающего элемента 12 (2pЭ) третьего канала 3 (3К), так как указанный канал отключен.

Начиная с момента t9 коды, поступающие на седьмой (Вх.7) и восьмой (Вх.8) входы устройства, соответственно на первый и второй входы второго элемента сравнения 18 (2ЭС) первого канала 1(1К) различаются. При этом на инверсном выходе второго элемента сравнения 18 (2ЭС) первого канала 1(1К) формируется логическая «1», которая поступает на шестой вход второго элемента «И» 15 (2И) первого канала 1 (1К).

В момент t10, на шестой вход устройства (Вх.6), соответственно на пятый вход (5 вх.) первого канала 1(1К) и далее на второй вход второго элемента «И» 15 (2И) первого канала 1(1К) поступает импульс контроля ΔtКИ Ввиду того, что на остальных входах указанного элемента сформированы логические «1», импульс с выхода второго элемента «И» 15 (2И) первого канала 1(1К) поступает на вход второго элемента задержки 17 (2ЭЗ), длительность которой ΔtИС определена по формулам (4), а также поступает на первый вход установки третьего запоминающего элемента 16 (3ЗЭ) первого канала 1(1К), второй вход первого элемента «ИЛИ» 11 (1ИЛИ), а также на второй выход (2 вых.) первого канала 1(1К). При этом на инверсном выходе третьего запоминающего элемента 16 (3ЭЗ) первого канала 1(1К) формируется логический «0», который поступает на четвертый вход второго элемента «И» 15 (2И) первого канала 1 (1К) и, таким образом, блокирует формирование логической «1» на его выходе с момента t10 в течение времени задержки ΔtИС обусловленной сбоем информации то есть до момента t12

С выхода первого элемента «ИЛИ» 11 (1ИЛИ) первого канала 1(1К) в момент t10 импульс поступает на первый вход сброса второго запоминающего элемента 12 (2ЗЭ) первого канала 1(1К) и сбрасывает его по переднему фронту, при этом коммутатор тока 4 (КТ) размыкает ток, поступающий с первого входа (Вх.1) на первый выход (Вых.1) устройства.

Через время Δt3ЭЗ после момента t10, с выхода третьего элемента задержки 20 (3ЭЗ) импульс поступает на пятый вход (5 вх.) второго канала 2(2К) и, соответственно, на второй вход первого элемента «И» 13 (1И) второго канала 2(2К).

Формирование импульса на выходе второго элемента «И» 15 (2И) второго канала 2(2К) блокируется логическим «0» поступающим на его первый вход с первого, инверсного выхода второго запоминающего элемента 12 (23Э) второго канала 2(2К), так как указанный канал включен.

До момента t11 на первый вход второго элемента «И» 15 (2И) третьего канала 3 (3К) с инверсного выхода второго запоминающего элемента 12 (23Э) третьего канала 3(3К) поступает логическая «1», так как он находится в сброшенном состоянии, то есть канал отключен. На третий вход элемента «И-НЕ» 14 (И-НЕ) третьего канала 3 (3К), который является пятым входом (5 вх.) третьего канала 3(1 К), начиная с момента t10 поступает сигнал логического «0» с третьего выхода (3 вых.) первого канала 1(1К), который является прямым выходом второго запоминающего элемента (2ЗЭ) первого канала 1(1 К), поэтому на выходе элемента «И-НЕ» 14 (И-НЕ), соответственно, на третьем входе первого элемента «И» 13 (1И) третьего канала 3 (3К) формируется логическая «1». На втором и четвертом входах второго элемента «И» 15 (2И) третьего канала 3 (3К) логические «1» поступают с соответствующих инверсных выходов первого 10 (1ЗЭ) и третьего 20 (3ЗЭ) запоминающих элементов третьего канала 3 (3К) так как указанные элементы находятся в сброшенном состоянии.

В момент t11 импульс, с выхода четвертого элемента задержки 21 (4ЭЗ) поступает на пятый вход (5 вх.) третьего канала 3(3К), соответственно, на пятый вход первого элемента «И» 13 (1И) третьего канала 3(3К). Поскольку на входах с первого по четвертый первого элемента «И» 13 третьего канала 3(3К) формируются логические «1» импульс проходит на его выход и далее поступает на второй вход установки второго запоминающего элемента 12 (2ЗЭ) третьего канала 3(3К), который устанавливается в состояние логической «1». При коммутатора 4 (КТ) третьего канала 1 (1К) подает ток с третьего входа (Вх.3), на третий выход устройства (Вых. 3), то есть осуществляется включение третьего канала.

Начиная с момента t10 до момента t12 на инверсном выходе первого запоминающего элемента 10 (1ЗЭ) первого канала 1 (1К), в течение времени задержки обусловленной сбоем информации ΔtИС формируется логический «0», который поступает на четвертый вход первого элемента 13 «И» (1И) первого канала 1 (1К). При этом до момента t12 установка второго запоминающего элемента 12 (2ЗЭ) в состояние логической «1», то есть включение коммутатора 4 (КТ) первого канала, в случае отключения одного из ввух других каналов, блокируется. В момент t12 окончания задержки обусловленной сбоем информации ΔtИС на выходе второго элемента задержки 17 (2ЭЗ) первого канала 1(1К) формируется импульс, который поступает на второй вход сброса третьего запоминающего элемента 16 (3ЗЭ) первого канала 1 (1К), при этом на инверсном выходе указанного запоминающего элемента формируется логическая «1», которая разрешает формирование импульса на выходе первого элемента «И» 13 (1И) первого канала 1(1К), то есть разрешает включение первого канала 1(1К).

Циклограмма функционирования устройства при превышении счетчиком блока контроля порогового значения представлена на фиг. 6. Обозначения на фиг. 6:

t13 - момент времени появления отсутствия сравнения информации поступающей из первого и второго каналов на входы второго элемента сравнения 18(2ЭС) в первом канале 1 (1К) устройства,

t14 - момент отключения первого канала 1(1К) устройства,

t15, t17 - соответственно, моменты включения третьего 3(3К) и первого 1(1К) каналов,

t16 - момент окончания задержки обусловленной сбоем информации.

До момента t13 включены первый 1 (1К) и второй 2(2К) каналы устройства, при этом контроль осуществляется по кодам, поступающим на седьмой (Вх.7) и восьмой (Вх.8) информационные входы устройства, информация из которых, в свою очередь, поступает, соответственно, на седьмые входы (7 вх.) первого 1(1К) и второго 2(2К) каналов, а также на первый и на второй вход второго элемента сравнения 18 (2ЭС) первого канала 1(1К). При этом на инверсном выходе указанного элемента сравнения до момента цз формируется логический «0». На четвертый вход второго элемента «И» 15 (2И) первого канала 1 (1К), логическая «1» поступает со второго, прямого выхода второго запоминающего элемента 12 (2ЗЭ) поскольку данный канал включен. На третий вход второго элемента «И» 15 (2И) первого канала 1 (1К) поступает логическая «1» с шестого входа (6 вх.) первого канала 1 (1К), так как на указанный вход поступает информация с третьего выхода (3 вых.) второго канала 2 (2К), который является вторым, прямым выходом второго запоминающего элемента 12 (2ЗЭ) второго канала 2 (2К), который включен. На первый вход второго элемента «И» 15 (2И) первого канала 1 (1К) логическая «1» поступает с четвертого входа (4 вх.) первого канала 1 (1К), которая формируется на выходе (Вых. бк) блока контроля 19 (БК), поскольку содержимое счетчика 25 (СЧ) указанного блока не превышает порогового значения, подаваемого на его четвертый вход (4 вх.бк), соответственно на пятый вход устройства (Вх.5).

Начиная с момента t13 коды, поступающие на седьмой (Вх.7) и восьмой (Вх.8) информационные входы устройства начинают различаться, при этом на инверсном выходе второго элемента сравнения 18 (2ЭС) первого канала 1 (1К) формируется логическая «1», которая поступает на шестой вход второго элемента «И» 15 (2И) первого канала 1 (1К), на пятый вход которого поступает логическая «1» с выхода первого элемента сравнения 7 (1ЭС) первого канала 1(1К), так как перегрузка по току в первом канале 1(1К) не наблюдается.

На второй вход второго элемента «И» 15 (2И) второго канала 2 (2К) логический «0» поступает с шестого входа (6 вх.) данного канала, так как на указанный вход поступает информация с третьего выхода (3 вых.) третьего канала 3(3К), который является вторым, прямым выходом второго запоминающего элемента 12 (23Э) третьего канала 3 (3К), так как указанный канал отключен.

До момента t14 с выхода счетчика 25 (СЧ) блока контроля 19 (БК) на первый вход третьего элемента сравнения 26 (3ЭС) поступает код, менее порогового значения количества включений всех каналов на одном интервале времени сброса, поступающего на его второй вход. При этом на выходе (Вых. бк) блока контроля 19 (БК), который является инверсным выходом третьего элемента сравнения формируется логическая «1», поступающая на четвертые входы (4 вх) первого 1 (1К), второго 2 (2К) и третьего 3(3К) каналов устройства, соответственно, на вторые входы элементов «И-НЕ» 14 и на первые входы вторых элементов «И» 15 (2И) указанных каналов.

Начиная с момента t14 коды, поступающие на седьмой (Вх.7) и восьмой (Вх.8) входы устройства, соответственно на первый и второй входы второго элемента сравнения 18 (2ЭС) первого канала 1(1К) различаются. При этом на инверсном выходе указанного элемента формируется логическая «1», которая поступает на шестой вход второго элемента «И» 15 (2И) первого канала 1 (1К).

В момент t14, на шестой вход устройства (Вх.6), соответственно, на пятый вход (5 вх.) первого канала 1(1К) который является вторым входом второго элемента «И» 15 (2И) первого канала 1(1К) поступает импульс контроля ΔtКИ. Ввиду того, что на остальных входах указанного элемента сформированы логические «1», импульс с выхода второго элемента «И» 15 (2И) первого канала 1(1К) поступает на вход второго элемента задержки 17 (2ЭЗ), второй вход установки третьего запоминающего элемента 16 (3ЗЭ) первого канала 1(1К), второй вход первого элемента «ИЛИ» 11 (ШЛИ), а также второй выход (2 вых.) первого канала 1(1К). При этом на инверсном выходе третьего запоминающего элемента 16 (3ЭЗ) первого канала 1(1К) формируется логический «0», который поступает на четвертый вход первого элемента «И» 13 (1И) первого канала 1(1К) и, таким образом, блокирует формирование логической «1» на его выходе на время задержки обусловленной информационным сбоем ΔtИС до момента t16.

С выхода первого элемента «ИЛИ» 11 (1ИЛИ) первого канала 1(1К) импульс поступает на первый вход сброса второго запоминающего элемента 12 (2ЗЭ) первого канала 1(1К) и сбрасывает его, при этом коммутатор тока 4 (КТ) размыкает ток, поступающий с первого входа (Вх.1) на первый выход (Вых.1) устройства.

Кроме того, в момент t14 импульс, поступивший на второй выход первого канала (2 вых.) 1(1К), поступает на первый вход блока контроля 19 (БК) и, соответственно на первый вход второго элемента «ИЛИ» 22 (2ИЛИ) указанного блока, с выхода которого импульс поступает далее на первые входы третьего 23 (3И) и четвертого 24 (4И) элементов «И». До момента t14 на вторых входах указанных элементов формируется логическая «1», которая поступает с инверсного выхода третьего элемента сравнения 26 (3ЭС) блока контроля 19 (БК), поскольку код, соответствующий количеству переключений каналов поступающий на его первый вход менее кода допустимого количества повторных включений всех каналов после их отключения, поступающего на его второй вход который, является четвертым входом (4 вх.бк) блока контроля 19 (БК) и, соответственно, четвертым входом (Вх.4) устройства. На третьем входе третьего элемента «И» 23 (3И) логический «0», поступает с инверсного выхода четвертого запоминающего элемента 28 (4ЗЭ), при этом в момент t14 импульс с выхода четвертого элемента «И» 24 (4И) поступает на первый, счетный вход счетчика 25 (СЧ) и увеличивает его содержимое на «1». Далее, информация с выхода счетчика 25 (СЧ) поступает на первый вход третьего элемента сравнения 26 (3ЭС), в результате чего содержимое счетчика 25 (СЧ) достигает величины, равной количеству переключений каналов поступающему на его первый вход, при этом на инверсном выходе третьего элемента сравнения 26 (3ЭС) устанавливается логический «0», который поступает выход (Вых.бк) блока контроля 19 (БК) и затем на четвертые входы (4 вх.) первого 1(1К), второго 2(2К) и третьего 3 (3К) каналов устройства.

Через время Δt3ЭЗ после момента t14, с выхода третьего элемента задержки 20 (3ЭЗ) импульс поступает на шестой вход (6 вх.) второго канала 2(2К) и, соответственно, на пятый вход первого элемента «И» 13 (1И) указанного канала. Импульс на выходе второго элемента «И» 15 (2И) на установку в состояние логической «1» второго запоминающего элемента 12 (2ЗЭ) второго канала 2(2К) не формируется, так как блокируется логическим «0» поступающим на его первый вход с первого, инверсного выхода второго запоминающего элемента 12 (2ЗЭ) второго канала 2(2К), так как указанный канал включен.

До момента ti5 на первый вход второго элемента «И» 15 (2И) третьего канала 3 (К3) с инверсного выхода второго запоминающего элемента 12 (2ЗЭ) третьего канала 3 (3К) поступает логическая «1», так как указанный запоминающий элемент находится в сброшенном состоянии, то есть канал отключен. На третий вход элемента «И-НЕ» 14 (И-НЕ) третьего канала 3 (3К), который является пятым входом (5 вх.) третьего канала 3 (3К), начиная с момента t14 отключения первого канала 1 (1К) поступает сигнал логического «0» с третьего выхода (3 вых.) первого канала 1 (1К), который является вторым, прямым выходом второго запоминающего элемента 12 (2ЗЭ) первого канала 1(1К). Вследствие этого на выходе элемента «И-НЕ» 14 (И-НЕ) третьего канала 3 (3К), соответственно, на третьем входе второго элемента «И» 15 (2И) этого канала формируется логическая «1». На втором и четвертом входах второго элемента «И» 15 (2И) третьего канала 3 (3К) формируются логические «1», которые поступают с инверсных выходов первого 10 (1ЗЭ) и третьего 16 (3ЗЭ) запоминающих элементов третьего канала 3 (3К) так как указанные элементы находятся в сброшенном состоянии.