О

о

р

развивается процесс уменьшения расстрой ки и нарастания скорости этого процесса до следующего момента переключения. Подбором моментов срабатывания второго компаратора и глубины обратной связи по скорости обеспечивается переходный процесс, близкий к переходному процессу в устройстве, оптимальном по быстродействию. Непостоянство восстанавливающего воздействия устраняется введением операции нормировки выходного напряжения второго сумматора, чем достигается зависимость выходного напряжения блока нормировки от величины входного сигнала устройства, и последующим его сравнением с нулевым порогом в первом компараторе, в результате которого формируется статистическая DX. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1981 |

|

SU1840035A1 |

| УСТРОЙСТВО СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ СИГНАЛА | 1997 |

|

RU2128398C1 |

| Устройство синхронизации псевдослучайных сигналов | 1981 |

|

SU985961A1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШИРОКОПОЛОСНОГО СИГНАЛА | 1991 |

|

RU2040858C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Следящий фильтр фазоманипулированного псевдослучайного сигнала | 1982 |

|

SU1072252A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ | 1979 |

|

SU1840116A2 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ | 1979 |

|

SU1840071A1 |

| Цифровой дискриминатор псевдослучайной импульсной последовательности | 1974 |

|

SU496649A1 |

Изобретение относится к радиотехнике и может быть использовано в системах радиолокации, радионавигации, связи и управления, в которых применяются псевдослучайные сигналы. Цель изобретения - повышение точности синхронизации. Устройство содержит хронизатор 1, коррелятор 2, первый и второй блоки 3, 4 выбора максимума, фильтр 5 нижних частот, регистр 6 сдвига с обратными связями, регистр 7 сдвига, третий блок 8 выбора максимума, первый, второй и третий сумматоры 9, 10,11, первый и второй компараторы 12,13, усилитель 14с переменным коэффициентом усиления, блок 5 нормировки, формирователь 16 управляющих сигналов, первый и второй ключи 17,-18. Введение регулируемой обратной связи по скорости сдвигает в зависимости от знака и величины скорости компенсации начального рассогласования в переходном режиме дискриминационную характеристику по оси временных расстроек и увеличивает затухание в устройстве путем увеличения времени торможения, когда в устройстве нарастает инерционная расстройка (после переключения управляющего воздействия -1 на +1, или наоборот, после перехода DX через нуль), и сокращения времени расстройки, когда инерционная расстройка достигает максимума, и Ё

Изобретение относится к радиотехнике и может быть использовао в системах радиолокации, радионавигации, связи и управления, в которых применяются псевдослучайные сигналы.

Цель изобретения - повышение быстродействия устройства.

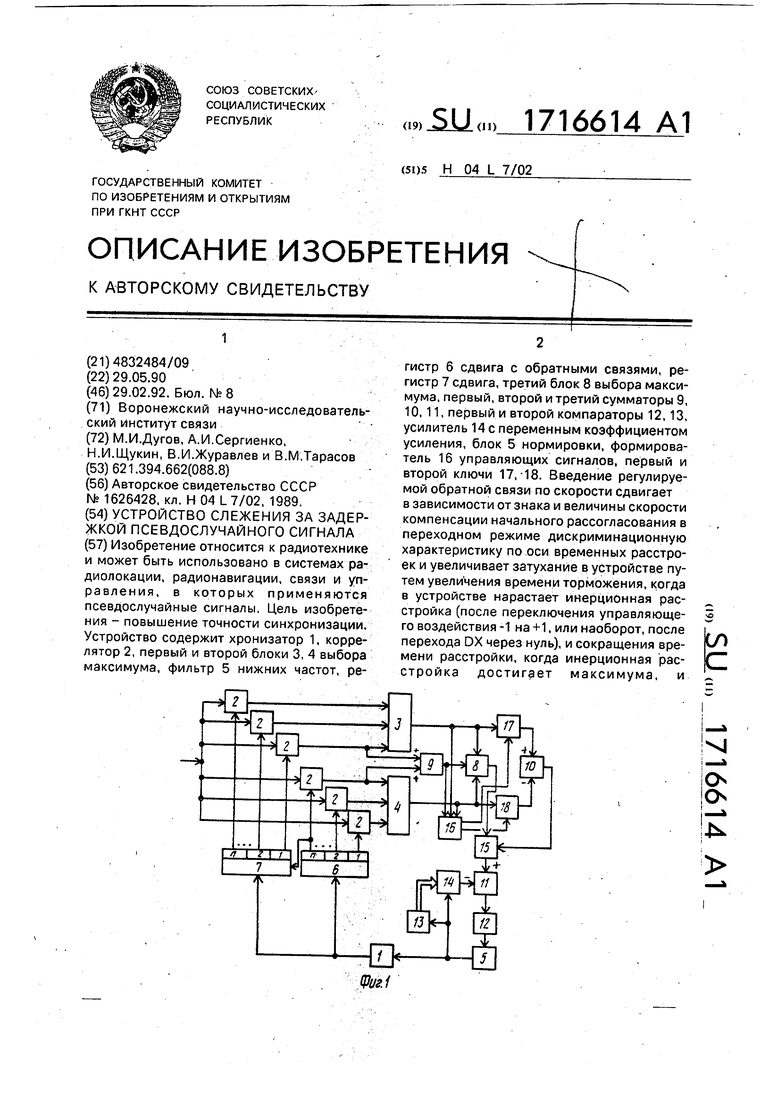

На фиг. 1 представлена структурная электрическая схема устройства слежения за задержкой псевдослучайного сигнала; на фиг. 2 - его дискриминационная характеристика; на фиг. 3 - пример реализации формирователя управляющих сигналов.

Устройство, слежения за задержкой псевдослучайного сигнала содержит хрони- затор 1, корреляторы 2, первый и второй блоки 3,4 выбора максимума, фильтр 5 нижних частот, регистр 6 сдвига с обратными связями, регистр 7 сдвига, третий блок 8 выбора максимума, первый, второй и третий сумматоры 9, 10, 11, первый и второй компараторы 12; 13, усилитель 14 с переменным коэффициентом усиления, блок 15 нормировки, формирователь 16 управляющих Сигналов, первый и второй ключи 17,18.

Формирователь 16 управляющих сигналов содержит первый, второй, третий и четвертый компараторы 19-22, первый и второй элементы ИЛИ 23, 24.

Устройство слежения за задержкой ра- ботает следующим образом.

При временных расстройках между приходящим сигналом и опорными псевдослучайными сигналами (ПСП) ближайших к нулю дискриминационной характеристики (ДХ) корреляторов, превышающих ±тъ максимальный отклик, полученный в одном из корреляторов 2 первой группы с опорными ПСП от регистра 7 сдвига выделяется первым блоком 3 выбора максимума и через первый вход третьего блока 8 выбора максимума поступает на первый вход блока 15 нормировки. Формирователь 16 управляющих сигналов в зависимости от соотношений сигналов на его входе включает первый ключ 17 в случае, когда максимально

возможный корреляционный отклик появляется на входе первого блока выбора максимума, закрывая при этом второй ключ 18. Если максимум напряжения на выходе второго блока 4 выбора максимума, формирователь 16 управляющих сигналов закрывает ключ 17 и открывает ключ 18. В случаях, когда расстройка , максимально возможное напряжение будет на выходе первого сумматора 9, и формировател.ь 16 управляющих сигналов даст команду на включение обоих ключей 17 и 18.

При расстройке, превышающей т0, формирователь 16 управляющих сигналов открывает ключ 17 и закрывает ключ 18, вычитающий вход второго сумматора 10 от схемы отключен, на его входе напряжение равно нулю, на выходе второго сумматора 10 появляется точно такое же напряжение, как и на выходе третьего блока 8 выбора максимума, и на выходе блока 15 нормировки появляется уровень единичного напряжения Um, соответствующего отношению входных напряжений блока 15 нормировки, равному единицу.

Аналогично при расстройках, меньших - Т0 , максимально возможный отклик появится на выходах корреляторов 2 второй группы, на выходе второго блока 4 выбора максимума, формирователь 16 управляющих сигналов закроет ключ 17, откроет ключ 18, и на .выходе блока 15 нормировки появится отрицательный уровень единичного напряжения -Dm.

При расстройках внутри интервала ( ±т0/2 ) выходное напряжение блока 15 нормировки линейно, проходя через т О, изменяется от Dm до -Um.

Нормировка напряжения дискриминатора дает возможность не регулировать параметры устройства (соответствующие коэффициенты) в зависимости от уровня входного широкополосного сигнала и существенно упростить само устройство. ФНЧ 5 представляет собой идеальный интегратор, а в качестве хронизатора 1 используется

генератор, управляемый напряжением (ГУН). Их передаточные функции соответственно,

Kn(p)-pV K(p)-f.

где Т и S - постоянная времени интегратора и крутизны управляющего входа ГУН.

В этом случае на выходе ФНЧ 5 будет формироваться напряжение, пропорциональное производной от расстройки г. Вы читая это напряжение с соответствующим весом из выходного напряжения блока 15 нормировки в третьем сумматоре 11, вво- дим таким образом обратную связь по скорости. Первый компаратор 12 с нулевым порогом сравнения формируют окончательную ДХ устройства, показанную нг фиг. 2.

Из фиг. 2 видно, что при любой рас- стройке восстанавливающая сила будет постоянной и максимальной, чем обеспечивается максимальное быстродействие при компенсации больших расстроек:

Формула изобретения Устройство слежения за задержкой псевдослучайного сигнала, содержащее первую и вторую группы корреляторов, ин- формационные входы которых объединены и являются входом устройства, а выходы подключены к входам соответственно первого и второго блоков выбора максимума, выходы которых подключены к первому и второму входам третьего блока выбора максимума, а также первый компаратор и фильт нижних частот (ФНЧ), выход которого через хронизатор подключен к тактовым входам регистра сдвига и регистра сдвига с обрат- ными связями, выход последнего разряда которого подключен к информационному входу регистра сдвига, выходы разрядов.ко-

U

-ffTo

-Zfo-to

торого подключены к опорным входам первой группы корреляторов, а выходы разрядов регистра сдвига с обратными связями - к опорным входам корреляторов второй группы, отличающееся тем, что, с целью повышения быстродействия устройства, введены первый - третий сумматоры, пер: вый и второй ключи, блок нормировки, формирователь управляющих сигналов, усилитель с переменным коэффициентом усиления и второй компаратор, к входу которого и входу усилителя с переменном коэффициентом усиления подключен выход ФНЧ, а выход второго компаратора подключен к управляющему входу усилителя с переменным коэффициентом усиления, выход которого и выход блока нормировки подключены соответственно к вычитающему и суммирующему входам третьего сумматора, выход которого через первый компаратор подключен к входу ФНЧ, при этом выходы первого и второго блокоб выбора максимума подключены соответственно к первому и второму входам формирователя управляющих сигналов и к информационным входам соответственно первого и второго ключей, к управляющим входам которых подключены соответственно первый и второй выходы формирователя, управляющих сигналов, к третьему входу которого и к третьему входу третьего блока выбора максимума подключен выход первого сумматора, к первому и второму суммирующим входам которого подключены выходы первых корреляторов первой и второй групп корреляторов, причем выход третьего блока выбора максимума подключен к первому входу блока нормировки, к второму входу которого подключен выход второго сумматора, а выходы первого.и второго ключей подсоединены соответственно к суммирующему и вычитающему входам втброго сумматора.

То

лТ0 &Г

Фиг.2

от Ьлоки 3

Фиг.З

| Дискриминатор для синхронизации по задержке псевдослучайного сигнала | 1989 |

|

SU1626428A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-02-28—Публикация

1990-05-29—Подача