Изобретение относится к области автоматики и вычислительной техники, в частности к устройствам для селекции признаков объектов, и может быть использовано при распознавании образов в процессе различных технологических операций.

Цель изобретения - расширение области применения за счет обеспечения процедуры ввода признаков недетерминированных распознаваемых объектов в реальном масштабе времени.

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок обновления признаков; на фиг. 3 - блок выдачи запросов; на фиг. 4 - селектор адреса; на фиг. 5 - третий блок памяти..

Устройство (фиг. 1) содержит первый 1, второй 2 и третий 3 блоки памяти, реверсивный счетчик 4, дешифратор 5, первый элемент И 6, инвертор 7, регистр 8, сумматор 9, первый элемент ИЛИ 10, первый 11, второй 12, третий 13 и четвертый 14 элементы задержки, селектор 15 адреса, блок 16 обновления признаков, блок 17 выдачи запросов, второй 18, третий 19 и четвертый 20 элементы И, второй 21, третий 22, четвертый 23, пятый 24 и шестой 25 элементы ИЛИ, триггер 26, первый управляющий вход 27, второй управляющий вход 28, третий управляющий вход 29, группу информационных входов 30, информационный вход 31, синхронизирующий вход 32, тактирующий вход 33, первый информационный выход 34, второй информационный выход 35.

Блок обновления признаков (фиг. 2) содержит первый 36 и второй 37 элементы И, первую группу элементов И 38, регистр 39 сдвига, счетчик 40, элемент И 41, дешифратор 42, триггер 43, первый 44, второй 45 и третий 46 элементы задержки, информационный вход 47, управляющий вход 48, тактирующий вход 49, синхронизирующий вход 49а, первую группу информационных выходов 50, вторую группу информационных выходов 51.

(Л

С

VJ

ю

СП

ю со VJ

Блок выдачи запросов (фиг. 3) содержит первый 52 и второй 53 элементы И, первый 54 и второй 55 триггеры, регистр 56 сдвига, счетчик 57, группу элементов И 58, элемент 59 задержки, информационный вход 60, синхронизирующий вход 61, управляющий вход 62, тактирующий вход 63, информационный выход 64, управляющий выход 65.

Селектор адреса (фиг. 4) содержит первый 66, второй 67, третий 68, четвертый 69, пятый 70 выходы блока 71, шестой 72 элемент И, первый триггер 73, второй триггер 74, третий триггер 75, первый 76, второй 77, третий 78, четвертый 79, пятый 80 и шестой 81 элементы ИЛИ, первый 82, второй 83 и третий 84 элементы задержки, управляющий вход 85, группу информационных входов 86, первый выход 87, второй выход 88, первую группу выходов 89, вторую группу выходов 90.

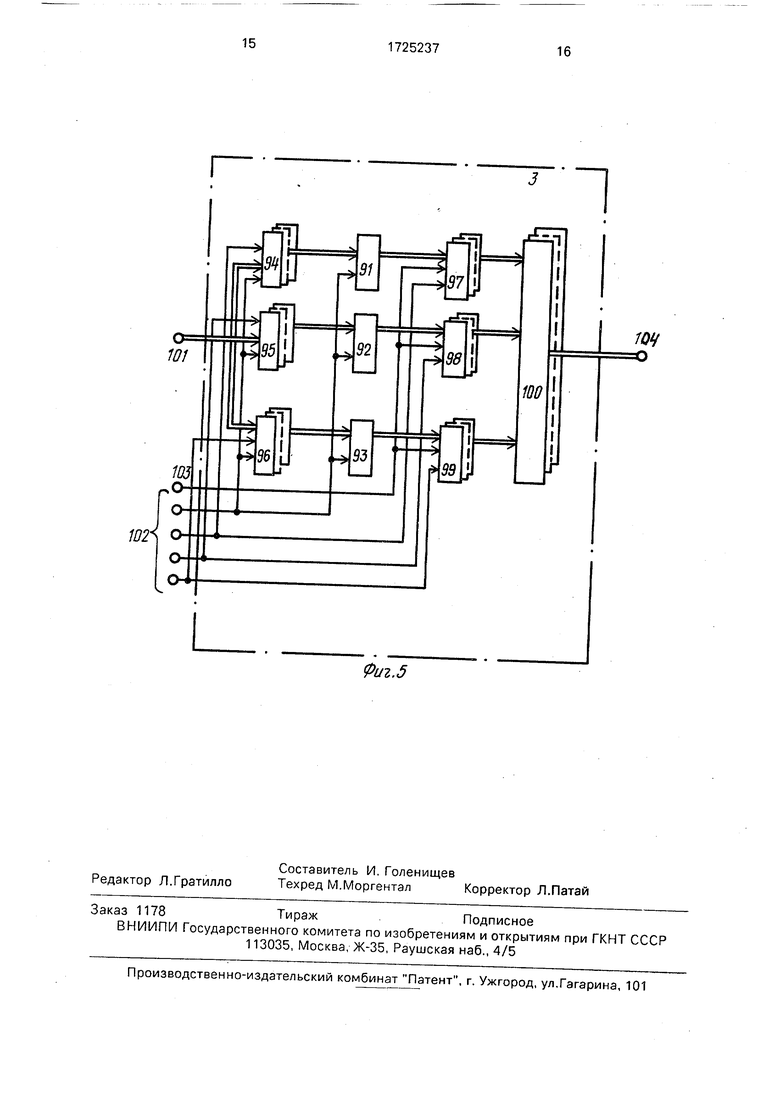

Третий блок памяти (фиг. 5) содержит первый 91, второй 92 и третий 93 регистры, первую 94, вторую 95, третью 96, четвертую 97, пятую 98 и шестую 99 группу элементов И, группу элементов ИЛИ 100, информационный вход 101, группу управляющих входов 102, синхронизирующий вход 103, выход 104.

Первый 1 блок памяти выполнен в виде постоянного запоминающего устройства, в фиксированных ячейках которого хранятся базовые адреса, с которых начинаются признаки по соответствующим объектам распознавания.

Второй блок памяти выполнен по адресной структуре.

Устройство работает следующим образом.

Последовательность признаков, характеризующих каждый из заданных объектов распознавания, заранее записывается в блок 2 памяти (фиг. 1).

Идентификация любого из объектов приводит к появлению на одном из разрядов группы входов 30 (фиг. 1) сигнала идентификации.

Допустим, что такой сигнал появился на первом разряде группы входов 30 (фиг. 1), откуда он поступает на входы элементов И 66 и 67 (фиг. 4). Однако открыт по второму входу будет только один элемент И 67, поскольку он соединен с прямым выходом триггера 73, находящегося в исходном (нулевом) состоянии, а элемент И 66 будет заперт низким потенциалом с инверсного выхода того же триггера.

Пройдя элемент И 67 (фиг. 4), импульс идентификации через элементы ИЛИ 77 и 78 поступает на R-входы триггеров 74 и 75, подтверждая их нулевое состояние, через

элемент ИЛИ 80 - на выход первого разряда первой группы выходов 89, а также через элемент 82 задержки - на S-вход триггера 73, устанавливая его в единичное состоя5 ние. Кроме того, этот же импульс поступает на выход первого разряда второй группы выходов 90 селектора непосредственно и через элемент ИЛИ 81 - на выход 88.

Импульс идентификации с первого раз10 ряда группы 89 (фиг. 4) поступает на входы группы элементов И 94-96 (фиг. 5) и синхронизирующие входы регистров 91-93. Однако, поскольку группы элементов 94-96 закрыты по потенциальному входу низким

15 потенциалом с инверсных выходов триггеров 73-75, то поступление синхроимпульса на первый разряд группы 102 не оказывает никакого влияния на состояние регистров 91-93.

0 После задержки импульса идентификации на элементе 82 (фиг. 4) на время, определяемое временем срабатывания регистров 91-93 (фиг. 5), он поступает на S- вход триггера 73, устанавливая его в

5 единичное состояние, при котором высоким потенциалом открывается элемент И 66 и низким потенциалом закрывается элемент И 67. Кроме того, высокий потенциал с прямого выхода триггера 73 выдается на второй

0 разряд группы 89, откуда он поступает на соответствующие входы элементов И 94 и 97 блока 3 и открывает их по одному из входов. Кроме того, этот же импульс с выхода 88 (фиг, 4) поступает на синхронизирующий

5 вход реверсивного счетчика 4 и на входы соответствующих элементов И 97-99 (фиг. 5), подключающих выходы регистра 91 через элемент ИЛИ 100 и выход 104 к информационным входам реверсивного счетчика 4. Од0 нако, поскольку в исходном состоянии все регистры 91-93 были обнулены, то и в реверсивный счетчик 4 по информационным шинам заносится нулевая информация. С первого разряда второй группы выходов 90

5 (фиг. 4) селектора адреса этот же импульс через элемент ИЛИ 21 (фиг. 1) поступает на вход фиксированной ячейки блока 1, где записан базовый адрес массива признаков, характеризующих объект идентификации.

0 Этот адрес с выхода блока 1 по информационным шинам парафазным кодом заносится в регистр 8 по синхросигналу с выхода элемента 11 задержки. Последний с выхода элемента 11 задержки,пройдя элемент ИЛ И

5 10, поступает на вход второго элемента 12 задержки, где задерживается на время установки кода в регистре 8.

С выхода регистра 8 и реверсивного

счетчика 4, в котором в данный момент времени одни нули, их содержимое поступает

на вход сумматора 9, где по синхросигналу с выхода элемента 12 задержки формируется окончательный результат, поступающий на адресный вход блока 2 памяти, на вход считывания которого поступает сигнал с выхода элемента 13 задержки, задерживающий синхроимпульс на время переходных процессов в сумматоре.

В результате на выход 34 (фиг. устройства выдается содержимое соответствующей ячейки памяти блока памяти в виде кода соответствующего признака, а сам импульс считывания поступает на суммирующий вход реверсивного счетчика 4 и увеличивает его содержимое на единицу. Кроме того, этот же импульс после задержки на элементе 14 на время считывания признака поступает на сбросовый вход сумматора 9 и устанавливает его в исходное состояние.

Если будет получен следующий признак этого же объекта, то на первый разряд группы входов 30 (фиг. 1) вновь подается импульс идентификации. Однако теперь этот импульс пройдет через открытый по второму входу элемент И 66 (фиг, 4) и через элемент ИЛИ 79 на выход 87 селектора, откуда через элемент ИЛИ 10 поступает на вход элемента 12 задержки и далее на синхронизирующий вход сумматора 9, в котором к содержимому базового адреса добавится содержимое реверсивного счетчика, увеличивая на единицу очередной адрес считывания и т.д.

Описанный процесс выдачи информации о признаках объекта будет продолжаться аналогичным образом до тех пор, пока на первый разряд группы входов 30 (фиг.. 1) поступают импульсы идентификации. При необходимости возврата к предыдущему признаку нажимается клавиша Возврат (не показана), в результате чего на входе 23 появляется импульс, поступающий на вход элемента И 6, на другой вход которого поступает высокий потенциал с выхода инвертора 7, подключенного к выходу дешифратора 5. Дешифратор 5 выдает на выход высокий потенциал только в том случае, если содержимое реверсивного счетчика 4 равно нулю. Так как рассматриваем случай возврата к ранее предыдущему признаку, то в реверсивном счетчике 4 уже зафиксировано число просмотренных признаков. В результате этого на выходе дешифратора будет низкий потенциал, а на выходе инвертора - высокий. При. этом импульс с входа 23, пройдя элемент И 6, поступает как на вычитающий вход реверсивного счетчика 4, уменьшая его содержимое на единицу, так и через элементы ИЛИ 10 и задержки 12 (фиг. 1) на синхронизирующий вход сумматора, обеспечивая формирование адреса на входе блока памяти.

Импульсом с выхода элемента 13 задержки (фиг. 1} по адресу, определяемому кодом в сумматоре 9, считывается содержимое соответствующей ячейки блока 2 памяти, а затем импульсом с выхода элемента 14 задержки сумматор сбрасывается в исход0 ное состояние. Повторное нажатие клавиши Возврат вызовет анализ признаков объектов в обратном листании до тех пор, пока содержимое реверсивного счетчика 4 не станет равным нулю. Этот момент будет за5 фиксирован дешифратором 5 выдачей высокого потенциала, который после инвертирования инвертором 7 заблокирует элемент И 6 по второму входу.

Необходимость классификации другого

0 объекта приведет к появлению сигнала на другом входе селектора 15 (фиг. 1), например на втором разряде группы входов 30. Этот импульс пройдет открытый в исходном состоянии элемент И 69 (фиг. 4) и через

5 элемент ИЛИ 80 потупит на первый разряд первой группы выходов 89 селектора, откуда поступит на синхронизирующие входы элементов 94-96. Поскольку открыты будут потенциалом триггера 73 (фиг. 4) только эле0 менты 94 и 97, то импульс с первого разряда группы 102 перепишет содержимое ревер- сивногосчетчика4 врегистр91, а импульсом с выхода элемента 83 задержки и элемента ИЛИ 81 (выход 88) содержимое регистра 92

5 через элементы ИЛИ 98 и 100 будет переписано в реверсивный счетчик 4. При фиксации факта отсутствия в памяти устройства признаков, характеризующих объект идентификации, на вход 29 устройства (фиг. 1)

0 подается сигнал. Этот сигнал поступает на вход элемента И 52 (фиг. 3), на другой вход которого поступает разрешающий потенциал с инверсного выхода триггера 26, находя- щегося в нулевом состоянии. Сигнал

5 запроса признака проходит через элемент И 52 на S-вход триггера 54, устанавливая его в единичное состояние. При этом открываются элементы И группы 58, и код адреса ячейки памяти с выхода сумматора 9 через

0 вход 60 блока 17 поступает на информационный вход регистра 56 сдвига. Тот же импульс запроса задерживается элементом 59 (фиг. 3) на время подключения выхода сумматора 9 к входу регистра 56 и поступает на

5 синхровход регистра 56, записывая в него код адреса.

Одновременно тот же импульс поступает на S-вход триггера 55, переводя его в единичное состояние. Высоким потенциалом триггер 55 переключает регистр 56 в

режим сдвига и открывает элемент И 53, на другой вход которого начинают поступать импульсы сдвига, которые осуществляют поразрядную последовательную выдачу кода адреса признака блока 2 на выход 64 (фиг. 3). Такая процедура выдачи кода адреса обусловлена тем, что канал связи с удаленной базой работает только в последовательном коде.

Число импульсов сдвига фиксируется счетчиком 57, и как только код из регистра 56 будет полностью выдан на выход 64, на выходе переполнения счетчика 57 появится импульс, который возвратит триггеры 54 и 56 в исходное состояние.

По готовности запрашиваемых данных на вход 24 поступает сигнал готовности, который устанавливает триггер 26 в единичное состояние, при котором он низким потенциалом с инверсного выхода закрывает элемент И 18, а также через вход 61 блокирует работу элемента И 52 блока 17. Высокий потенциал с прямого выхода триггера 26 через вход 48 (фиг. 2) поступает на входы элементов И 36 и 37. С задержкой на время срабатывания триггера 26 на вход блока 47 блока 16 поступает последовательный код из канала связи.

Структура сообщения имеет вид: код идентификационного признака и код информационного содержания.

Одновременно на синхровход регистра 39 с выхода элемента И 37 поступают синхроимпульсы, записывающие код в регистр 39. После записи очередного разряда в регистр 39 импульс с выхода элемента И 37 задерживается элементом 44 задержки на время записи в регистр 39 и поступает на S-вход триггера 43, устанавливая его в единичное состояние, при котором он высоким потенциалом переключает регистр 39 в режим сдвига и открывает элемент И 41, через который очередной импульс сдвига с входа 49а поступает на вход сдвига регистра 39.

После сдвига кода в регистре 39 тем же импульсом, задержанным на время сдвига элементом 45, триггер 43 возвращается в исходное состояние и вновь переводит регистр 39 в режим записи.

Счетчик 40 (фиг. 2) ведет подсчет числа импульсов сдвига, и как только все разряды будут приняты регистром 39, на выходе переполнения счетчика 40 появляется импульс, который через элемент 46, задерживающий импульс на время переходных процессов, и дешифратор 42 поступает на входы группы элементов И 38 и на последний разряд группы выходов 51 (фиг. 2).

Дешифратор 42 расшифровывает код признака и открывает один из элементов И

группы 38, через который импульс с выхода элемента 46 задержки поступает на один из выходов группы 51 (фиг. 2) соответственно. Откуда этот импульс проходит через соответствующий элемент ИЛИ 21-23 и далее на соответствующий вход считывания блока 1 памяти. Параллельно с этим, импульсом с второго выхода блока 16 сбрасывается в исходное состояние реверсивный счетчик 4,

0 одновременно импульс проходит через элемент ИЛИ 24 на вход элемента задержки, где задерживается на время считывания кода адреса с блока 1 и затем поступает на синхронизирующий вход регистра 8, занося

5 в него код с выхода блока 1.

Кроме того, этот же импульс через элементы ИЛИ 10 и задержки 12 поступает на синхронизирующий вход сумматора 9, блокируя в нем код только с выхода регистра 8,

0 так как реверсивный счетчик сброшен в исходное состояние. После задержки элементом 13 на время срабатывания сумматора импульс с его выхода проходит через элемент И 19 на вход управления записью бло5 ка 2, записывая содержательную часть признака в ячейку памяти с адресом, указанным в сумматоре 9.

Этот же импульс сбрасывает триггер 2.6 и через элемент ИЛИ 22, элемент 14 задер0 жки и элемент И 20 проходит на вход сброса сумматора 9, устанавливая его в исходное состояние.

Таким образом, введение новых блоков, и связей позволило осуществить возмож5 ность ввода признаков недетерминированных распознаваемых объектов и расширить область применения устройства. Формула изобретения Устройство для селекции признаков

0 объектов, содержащее селектор адреса, информационные входы которого являются группой информационных входов устройства, первый блок памяти, выход которого подключен к информационному входу пер5 вого регистра, выход которого подключен к первому информационному входу сумматора, второй информационный вход которого подключен к выходу реверсивного счетчика, а выход соединен с адресным входом второ0 го блока памяти, выход которого является первым информационным выходом устройства, первый элемент ИЛИ, первый вход которого соединен с синхронизирующим входом первого регистра и подключен к вы5 ходу первого элемента задержки, второй вход подключен к первому выходу селектора адреса, а выход соединен с входом второго элемента задержки, выход которого подключен к синхронизирующему входу сумматора и к входу третьего элемента задержки, инвертор, вход которого соединен с выходом дешифратора, а выход подключен к одному из входов первого элемента И, другой вход которого является первым управляющим входом устройства, выход первого элемента И соединен с вычитающим входом реверсивного счетчика, синхронизирующий вход которого подключен к второму выходу селектора адреса, а выход соединен с входом дешифратора и с информационным входом третьего блока памяти, группа управляющих входов которого соединена с группой выходов селектора адреса, тактирующий вход подключен к третьему выходу селектора адреса, синхронизирующий вход соединен с вторым выходом селектора адреса, а выход подключен к информационному входу реверсивного счетчика, и четвертый элемент задержки, отличающееся тем, что, с целью расширения области применения за счет обеспечения возможности ввода признаков недетерминированных распознаваемых объектов в реальном масштабе времени, введены второй, третий, четвертый, пятый и шестой элементы ИЛИ, блок обновления признаков, второй, третий и четвертый элементы И, триггер, блок выдачи запросов, первые входы второго, третьего и четвертого элементов ИЛИ подключены поразрядно к второй группе информационных выходов блока, обновления признаков, первая группа информационных выходов которого соединена с группой информационных входов второго блока памяти, информационный, синхронизирующий и тактирующий входы блока обновления признаков являются соответственно одноименными входами устройства, вторые входы второго, третьего и четвертого элементов ИЛИ подключены поразрядно к второй группе выходов селектора адреса, выходы второго, третьего и четвертого элементов ИЛИ соединены с соответствующими входами считывания первого блока памяти, первый вход пятого

элемента ИЛИ объединен с установочным входом реверсивного счетчика и подключен к управляющему выходу блока обновления признаков, второй вход пятого элемента ИЛИ подключен к второму выходу селектора адреса, а выход - к входу первого элемента задержки, первый и второй входы шестого элемента ИЛИ объединены соответственно с входами Запись, Считыва- ние второго блока памяти и подключены к

выходам соответственно второго и третьего элементов И, первые входы которых объединены и подключены к выходу третьего элемента задержки, а вторые объединены с входами управления соответственно

селектора адреса .и блока обновления признаков и подключены соответственно к инверсному и прямому выходам триггера, S-вход которого является вторым управляющим входом устройства, а R-вход соединен с выходом третьего элемента И, выход шестого элемента ИЛИ соединен с входом четвертого элемента задержки, выход которого соединен с вторым входом четвертого элемента И, первый вход которого

подключен к управляющему выходу блока выдачи запросов, а выход соединен с синхронизирующим входом сумматора, информационный вход блока выдачи запросов соединен с выходом сумматора, тактирующий вход является тактирующим входом устройства, управляющий вход является третьим управляющим входом устройства, синхронизирующий вход подключен к инверсному выходу триггера, информационный

выход является вторым информационным выходом устройства.

zi

LCZSZLl

и

Фиг А

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распознавания подвижных объектов | 1989 |

|

SU1649575A1 |

| Устройство для ввода информации | 1989 |

|

SU1661748A1 |

| Устройство для выборки информации из блока памяти | 1987 |

|

SU1509982A2 |

| Устройство для информационного поиска | 1986 |

|

SU1399769A1 |

| Устройство для обмена информацией | 1989 |

|

SU1644149A1 |

| Устройство для сбора данных о состоянии массы, перемещаемой технологическими линиями | 1989 |

|

SU1810897A1 |

| Устройство для селекции изображений объектов | 1988 |

|

SU1608711A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРЕДЪЯВЛЕНИЕМ ИНФОРМАЦИИ В СИСТЕМЕ ДИСТАНЦИОННОГО ОБУЧЕНИЯ | 2001 |

|

RU2248605C2 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ПОГРАНИЧНОГО КОНТРОЛЯ | 2006 |

|

RU2316811C1 |

| Устройство для ввода информации | 1990 |

|

SU1709294A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для селекции признаков объектов, и может быть использовано при распознавании образов в процессе различных технологических операций. Цель изобретения - расширение области применения за счет обеспечения процедуры ввода признаков недетерминированных распознаваемых объектов в реальном масштабе времени - достигается введением блока обновления признаков, блока выдачи запросов, трех элементов И, двух элементов ИЛИ, трех групп элементов ИЛИ и тригера. 5 ил.

Фиг.5

| Патент США № 4636846, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР М 1591051, 04.05.89. | |||

Авторы

Даты

1992-04-07—Публикация

1990-03-16—Подача