Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подсчета числа единиц | 1988 |

|

SU1730621A1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1797110A1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1797111A1 |

| Устройство для подсчета числа единиц | 1988 |

|

SU1658146A1 |

| Сумматор по модулю пять | 1991 |

|

SU1783514A1 |

| Устройство для вычисления фундаментальных симметрических булевых функций | 1990 |

|

SU1730616A1 |

| Устройство для вычисления симметрических булевых функций | 1989 |

|

SU1765818A1 |

| СУММАТОР ПО МОДУЛЮ ПЯТЬ | 1992 |

|

RU2018931C1 |

| СУММАТОР ПО МОДУЛЮ ПЯТЬ | 1992 |

|

RU2012038C1 |

| Сумматор по модулю пять | 1991 |

|

SU1807478A1 |

Изобретение относится к области вычислительной техники и микроэлектроники и предназначено для построения быстродействующих матричных арифметических устройств. Цель изобретения - расширение области применения за счет увеличения разрядности входной информации. Поставленная цель достигается тем, что устройство

00

ы ю

00

о

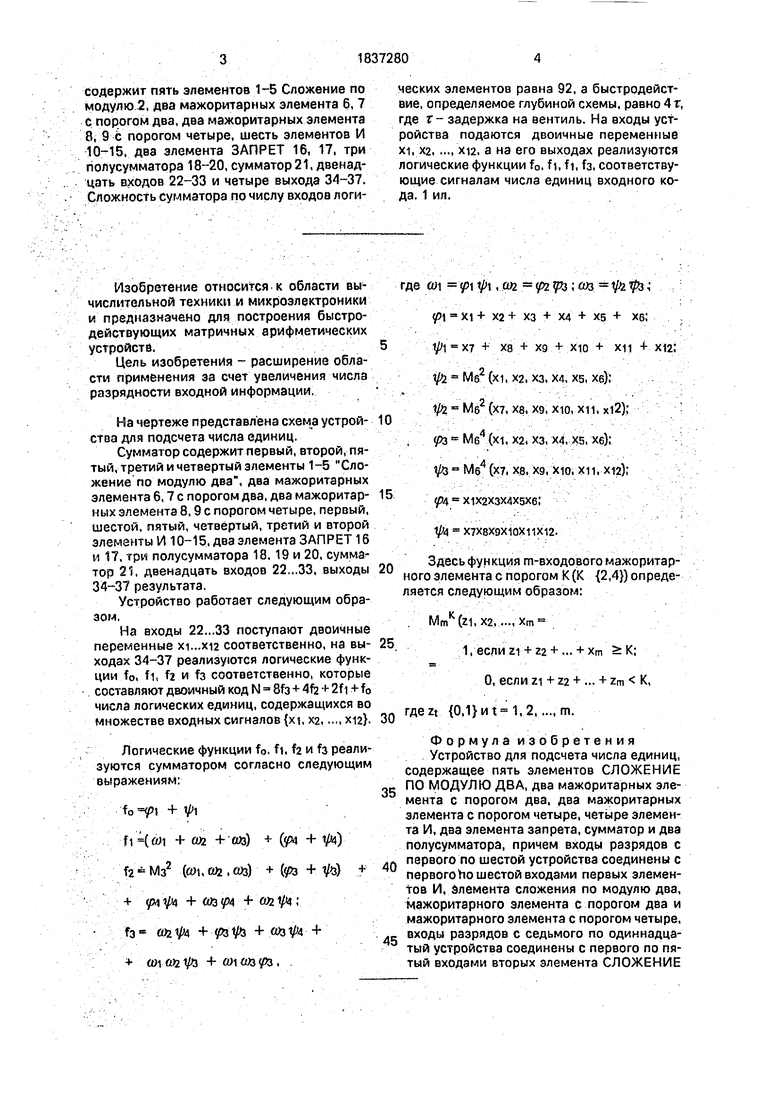

Содержит пять элементов 1-5 Сложение по модулю 2, два мажоритарных элемента 6, 7 с порогом два, два мажоритарных элемента 8, 9 с порогом четыре, шесть элементов И 10-15, два элемента ЗАПРЕТ 16, 17, три полусумматора 18-20, сумматор 21, двенадцать входов 22-33 и четыре выхода 34-37. Сложность сумматора по числу входов логиИзобретение относится к области вычислительной техники и микроэлектроники и предназначено для построения быстродействующих матричных арифметических устройств.

Цель изобретения - расширение области применения за счет увеличения числа разрядности входной информации,

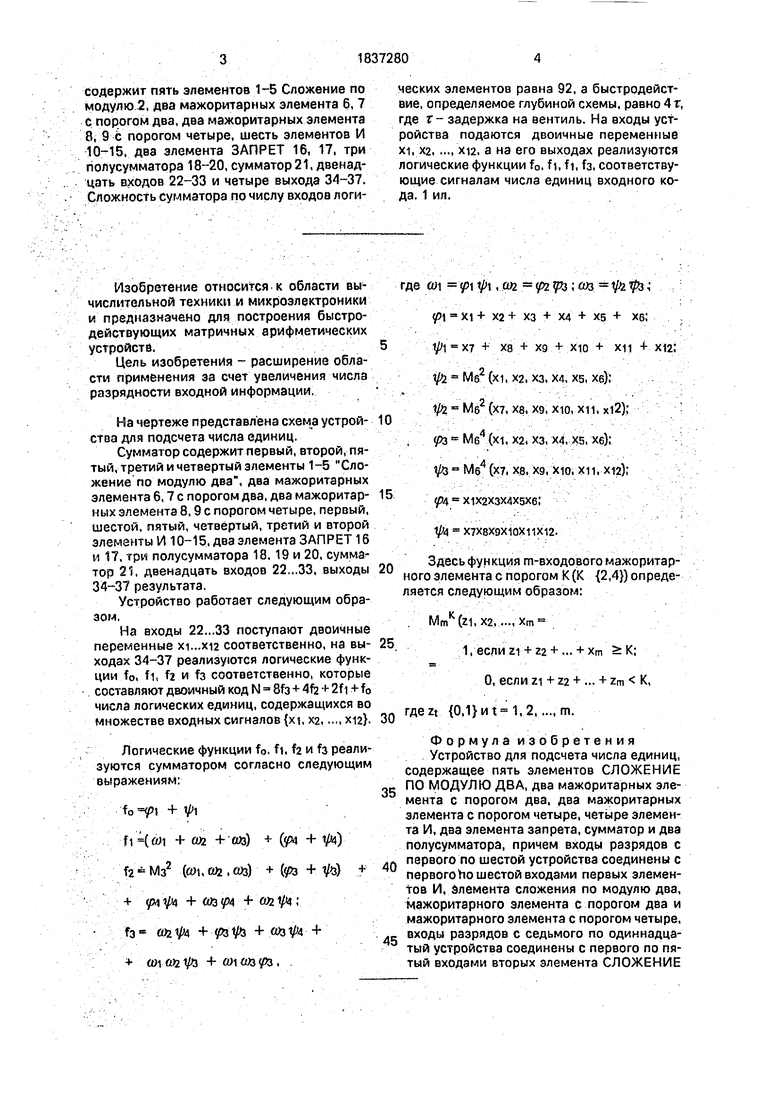

На чертеже представлена схема устройства для подсчета числа единиц.

Сумматор содержит первый, второй, пятый, третий и четвертый элементы 1-5 Сложение по модулю два, два мажоритарных элемента 6,7 с порогом два, два мажоритарных элемента 8,9с порогом четыре, первый, шестой, пятый, четвёртый, третий и второй элементы И 10-15. два элемента ЗАПРЕТ 16 и 17, три полусумматора 18, 19 и 20, сумма - тор 21, двенадцать входов 22...33, выходы 34-37 результата.

Устройство работает следующим образом,

На входы 22...33 поступают двоичные переменные xi...xi2 соответственно, на выходах 34-37 реализуются логические функции f0, fi, h и fs соответственно, которые составляют двоичный код N 8f3 + 4fe + 2f 1 + fo числа логических единиц, содержащихся во множестве входных сигналов {xi, Х2,.... х12}.

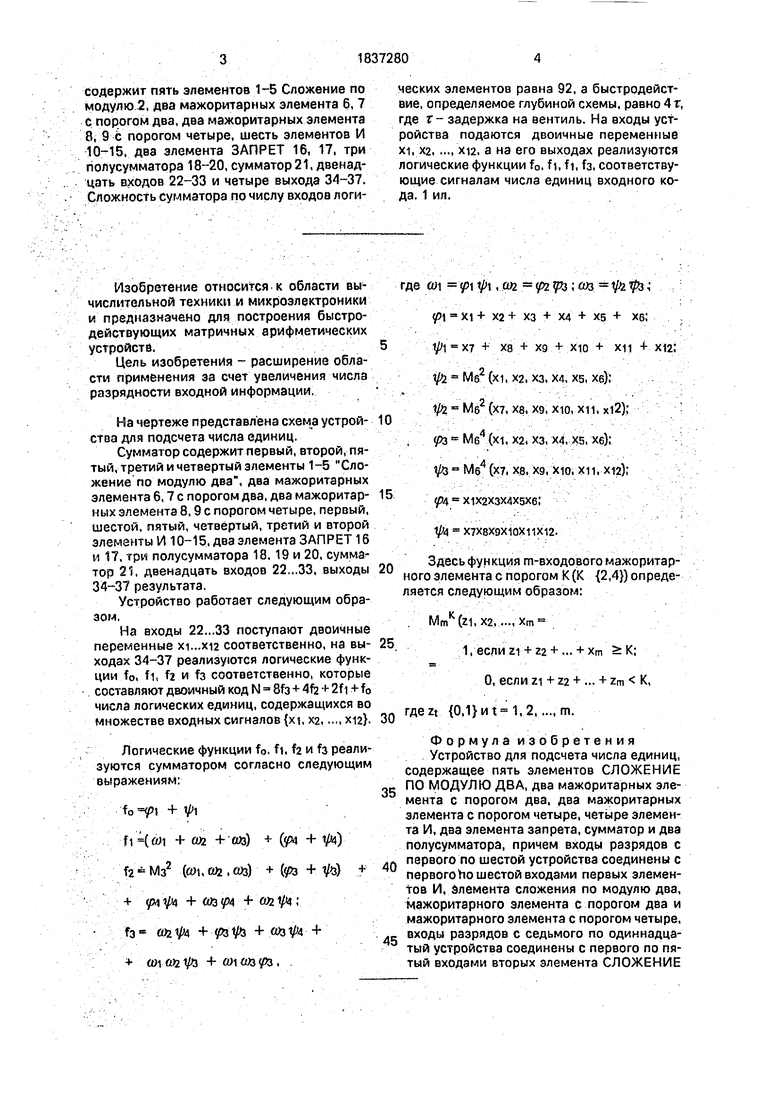

Логические функции fo, fi, f2 и f3 реализуются сумматором согласно следующим выражениям:

+

f i ( + од + юз) + (/ч + VO fa Мз2 -(ал,ufc ,Шз) + (0& + фд .

-V р 4} + (ОЗ ф4 + (02 V Г

.Тз ofeV + де$5 + GUV- +

: OHUJzt/Q + O 1UUp3, .

ческих элементов равна 92, а быстродействие, определяемое глубиной схемы, равно 4т, где т- задержка на вентиль. На входы устройства подаются двоичные переменные

xi, X2Х12, а на его выходах реализуются

логические функции f0, fi, fi, f3, соответствующие сигналам числа единиц входного кода. 1 ил.

где ал ,w $2Фзi P xi + X2 + хз + X4 + xs + xe;

Vl X7 + X 8 + X9.+ .X10 + X11 + X12:

(xil X2, хз, Х4, xg, xe); t# « Me2 (x, xs, X9, xio,xii,xi2); ;

. ... рз Me4 (xi,X2, хз, Х4, xs, xe);;

V ° Мб4 (X7, X.8, X9, X10, X11, X12); 4 te X1X2X3X4X5X6,1 X7X8X9X10X11X12.

Здесь функция m-входового мажоритарного элемента с порогом К(К {2,4}) определяется следующим образом:

Mm (zi,X2,...,Xm

1, еСЛИ Z1+ Z2 + ...+ Xm К;

О, если zi + Z2 + ... + zm К, гдегг {0,,2..... m.

Формула и зобретен ия Устройство для подсчета числа единиц, содержащее пять элементов СЛОЖЕНИЕ

ПО МОДУЛЮ ДВА, два мажоритарных элемента с порогом два, два мажоритарных элемента с порогом четыре, четыре элемента И, два элемента запрета, сумматор и два полусумматора, причем входы разрядов с

первого по шестой устройства соединены с первого ho шестой входами первых элементов И, элемента сложения по модулю два, мажоритарного элемента с порогом два и мажоритарного элемента с порогом четыре,

входы разрядов с седьмого по одиннадцатый устройства соединены с первого по пятый входами вторых элемента СЛОЖЕНИЕ

ПО МОДУЛЮ ДВА, мажоритарного элемента с порогом два и мажоритарного элемента с порогом четыре, выходы первого и второго элементов СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соединены с входами первого и второго ела- гаемых первого полусумматора, выход суммы которого соединен с выходом первого разряда результата устройства, выходы первого и второго мажоритарных элементов с порогом два соединены с прямыми входа- ми первого и второго элементов запрета соответственно, выход первого мажоритарного элемента с порогом четыре соединен с инверсным входом первого элемента запрета, входом первого слагаемого второго пол- усу,мматора и первым входом второго элемента И, второй вход которого соединен с выходом переноса первого полусумматора, с входом переноса сумматора и первым входом третьего элемента И, второй вход которого соединен с выходом второго мажоритарного элемента с порогом четыре, инверсным входом второго элемента запрета и входом второго слагаемого второго полусумматора, выход1 суммы и переноса кото- рого соединены с первыми входами третьего и четвертого элементов СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соответственно, выход первого элемента запрета соединен с входом первого слагаемого сумматора и третьим входом третьего элемента И, выход которого соединен с вторым входом четвертого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, третий вход которого соединен с выходом второго элемента И, третий вход ко- торого соединен с выходом второго элемента запрета, первым входом четвертого элемента И и входом второго слагаемого

сумматора, выход суммы и переноса которого соединены соответственно опервым входом пятого и вторым входом третьего элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, выход первого элемента И соединен с вторым входом четвертого элемента И, выход которого соединен с третьим входом третьего и четвертым входом четвертого элементов СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, выходы пятого, третьего и четвертого элементов СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соединены с выходами второго, третьего и четвертого разрядов результата устройства соответственно, отличающееся тем, что, с целью расширения области применения за счет увеличения разрядности входной информации, в устройство введены пятый и шестой элементы И и третий полусумматор, выходы суммы переноса которого соединены с вторым входом пятого и четвертым входом третьего элементов СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соответственно, выход первого элемента И соединен с первым входом пятого элемента И и входом первого слагаемого третьего полусумматора, вход второго слагаемого которого соединен с выходом шестого элемента И и вторым входом пятого элемента И, выход которого соединен с пятыми входами третьего и четвертого элементов СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, аходЫ с первого по пятый шестого элемента И соединены с первого по пятый входами второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, шестой вход которого соединен ,с шестыми входами вторых мажоритарных элементов с порогом два и с порогом четыре, шестым входом шестого элемента И и входом двенадцатого разряда устройства.

Авторы

Даты

1993-08-30—Публикация

1989-01-16—Подача