(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения S-ичных цифр в позиционно-остаточной системе счисления | 1989 |

|

SU1633401A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ S-ИЧНЫХ ЦИФР В ПОЗИЦИОННО-ОСТАТОЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ | 1991 |

|

RU2006919C1 |

| Устройство для умножения в системе остаточных классов | 1984 |

|

SU1236472A1 |

| Устройство для умножения S-ичных цифр в позиционно-остаточной системе счисления | 1991 |

|

SU1837284A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

| УСТРОЙСТВО ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2012051C1 |

| Устройство для определения позиционных характеристик непозиционного кода | 1985 |

|

SU1283948A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных устройств, работающих в позиционно-остаточ- ной системе счисления. Цель изобретения - сокращение аппаратурных затрат. В устройство, содержащее два коммутатора 14, 15, два блока 1,2 хранения констант, два блока 5, 6 умножения, первый элемент 7 задержки, шесть блоков 8-13 элементов И и два сумматора 3, 4, введены второй элемент 26 задержки, два регистра 24 и 25 и два мультиплексора 22 и 23, что позволило вывести из состава устройства два блока умножения, объем которых во много раз превышает объем введенных блоков. 3 ил.

vj со

о о ю ел

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих арифметических устройств, работающих в позицион- но-остаточной системе счисления.

Цель изобретения - сокращение аппаратурных затрат.

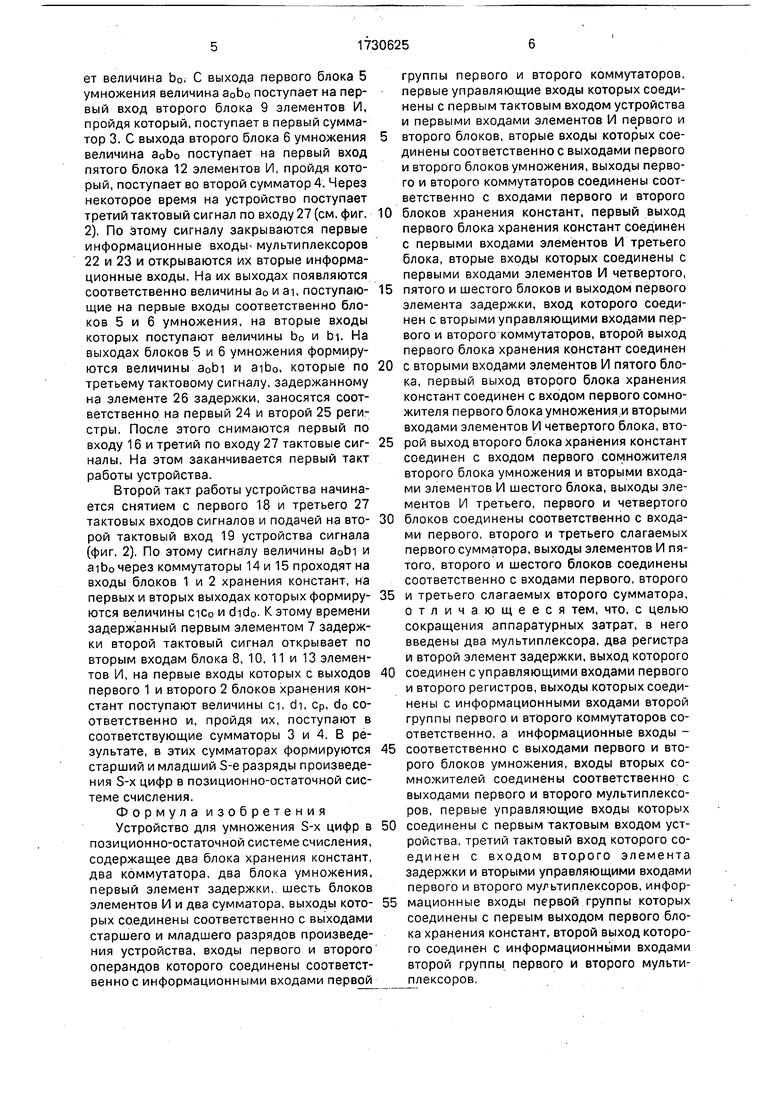

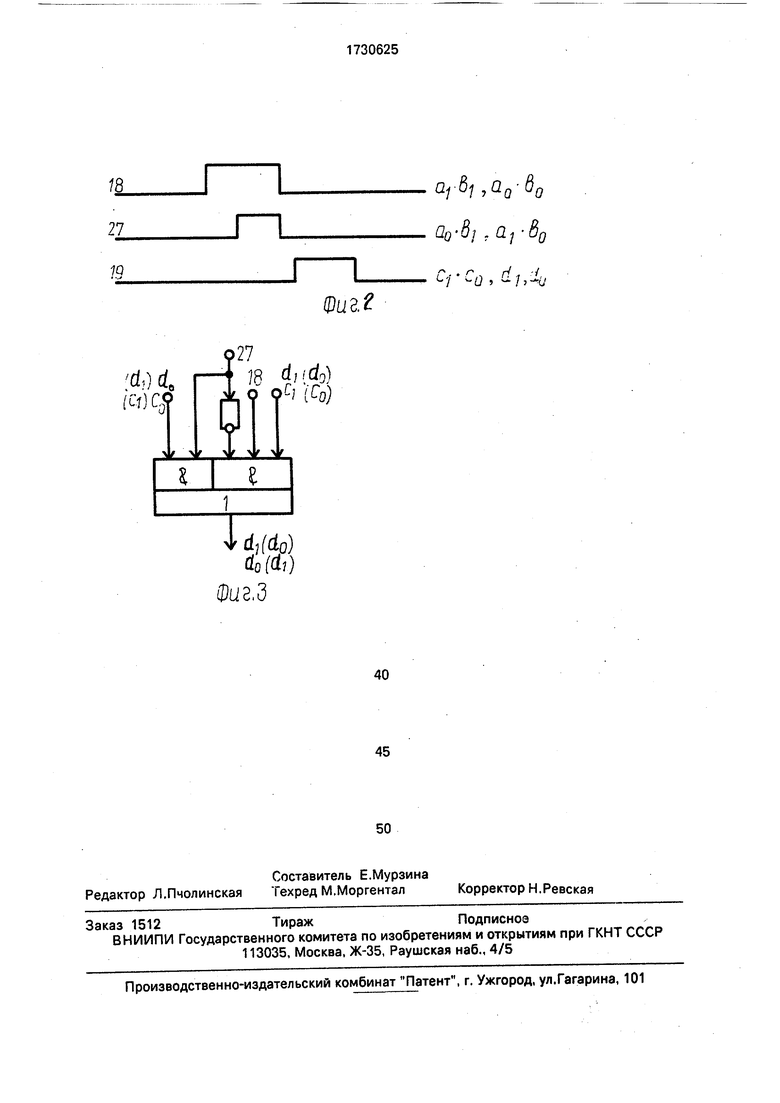

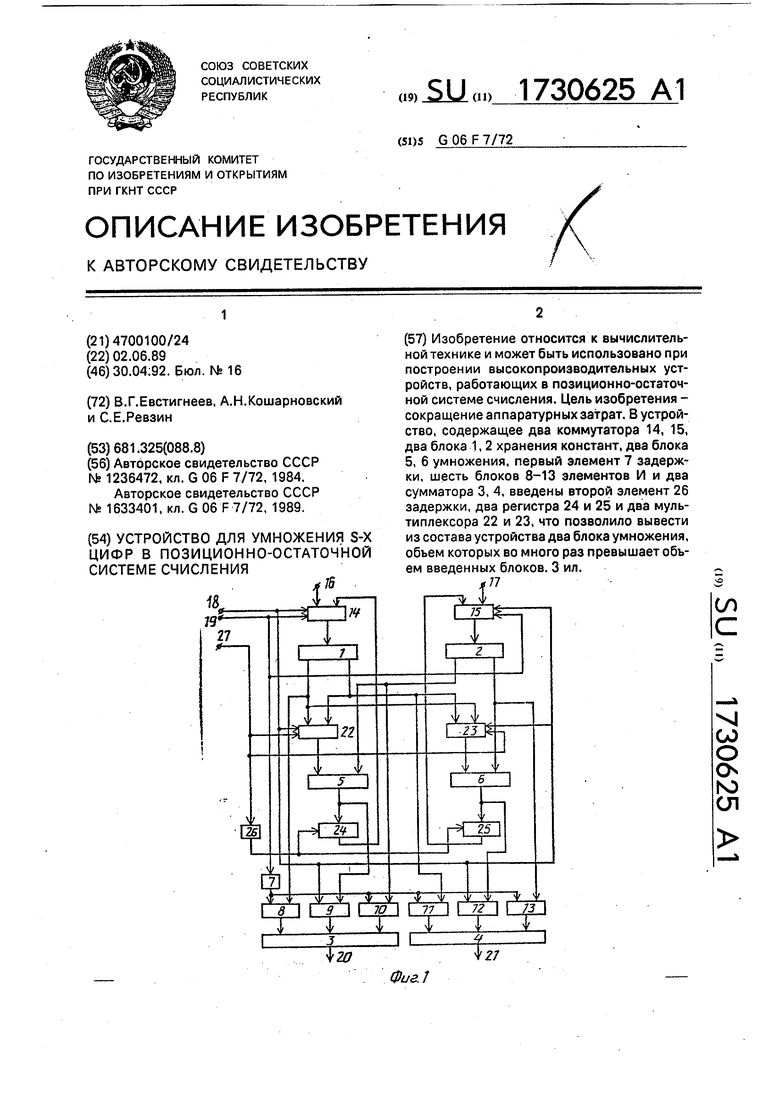

На фиг, 1 представлена функциональная схема устройства; на фиг. 2 - временная диаграмма токовых сигналов; на фиг. 3функциональная схема мультиплексоров.

Устройство содержит два блока 1 и 2 хранения констант, два сумматора 3 и 4, два блока 5 и 6 умножения, первый элемент 7 задержки, шесть блоков 8-13 элементов И, два коммутатора 14 и 15, входы первого 16 и второго 17 операндов устройства, первый 18 и второй 19 тактовые входы устройства, выходы старшего 20 и младшего 21 разрядов произведения устройства, два мульти- плексора 22 и 23, два регистра 24 и 25, второй элемент 26 задержки и третий 27 тактовый вход устройства.

В основу работы устройства для умножения 3-х цифр в позиционно-остаточной системе счисления положено следующее.

Запишем произведение двух 3-х цифр в виде

a-b (ai V1T+ a0)(bi VlT+bo)

aibr S + a0bi + aib0

+ a0bo flS1 + foS0,

Запишем второе и третье слагаемое в виде

aobiS . aiboS

+ c0 + diS1 + do,

где fi aibi + ci + di; to a0b0 + Co + do

a0 rest (a/ VS); ai ent(a/ ); b0 rest(b/VTj: bi ent(); c0 rest (a0bi/ ); ci ent(a0bi/ VS); d0 rest(aib0/ ); di ent(aib0/ VSl, где rest (X/Y) - остаток от деления X на Y;

5

0

5 0

5

0

5

0

5

0

5

ent (X/Y) - целое частное от деления X на Y.

Известно, что цифры в 3-й позиционно- остаточной системе счисления представляются по модулям системы (СОК) в виде

а ( «1 , aiак ) ;

Ь (,),

где«| rest(a/Pj);

(b/Pj);

j 1, К;

Pj - модули СОК, удовлетворяющие уск

ловию П Pj - 23 (простые числа), j 1

Для согласования с устройствами, работающими в двоичной системе счисления,в позиционно-остаточных устройствах обычно выбирают S 2m. Удобнее всего принять m 8 и соответственно 3 28 256, а среди модулей СОК иметь один, равный VS . в частном случае пусть Pi V256 16. Это позволяет при аппаратной реализации блоков 1 и 2 хранения констант получить экономичные решения.

Устройство для умножения 3-х цифр в позиционно-остаточной системе счисления работает следующим образом.

По первому тактовому сигналу, поступающему на устройство по входу 18, А

( «1 , «2«к ) И В ( , /fc/ к ) ,

представленные кодом СОК по модулям Pi,

2 Рк, по входам 16 и 17 поступают на.

коммутаторы 14 и 15, с выходов которых передаются на входы соответствующих блоков 1 и 2 хранения констант. Эти блоки конструктивно представляют собой блоки постоянной памяти на 21-разрядных слов

к

каждый, где I j j двоичная разрядJ 1

ность вычета а или Д-. В этих блоках в соответствии с выражением (3) формируются величины ai, ао и bi, bo соответственно. Величина а с первого выхода блока 1 хранения констант через первый информационный вход первого мультиплексора 22 поступает на его выход, с которого поступает на первый вход первого блока 5 умножения, на второй вход которого с первого выхода второго блока 2 хранения констант поступает величина bi. Одновременно с второго выхода первого блока 1 хранения констант величина ао поступает на первый информационный вход второго мультиплексора 23, открытый первый вход второго блока 6 умножения, на второй вход которого с второго выхода блока 2 хранения констант поступает величина Ь0. С выхода первого блока 5 умножения величина а0Ь0 поступает на первый вход второго блока 9 элементов И, пройдя который, поступает в первый сумматор 3. С выхода второго блока 6 умножения величина а0Ьо поступает на первый вход пятого блока 12 элементов И, пройдя который, поступает во второй сумматор 4. Через некоторое время на устройство поступает третий тактовый сигнал по входу 27 (см. фиг. 2). По этому сигналу закрываются первые информационные входьь мультиплексоров 22 и 23 и открываются их вторые информационные входы. На их выходах появляются соответственно величины ао и ач, поступающие на первые входы соответственно блоков 5 и 6 умножения, на вторые входы которых поступают величины Ь0 и bi. На выходах блоков 5 и 6 умножения формируются величины a0bi и aibo, которые по третьему тактовому сигналу, задержанному на элементе 26 задержки, заносятся соответственно на первый 24 и второй 25 регистры. После этого снимаются первый по входу 16 и третий по входу 27 тактовые сигналы. На этом заканчивается первый такт работы устройства.

Второй такт работы устройства начинается снятием с первого 18 и третьего 27 тактовых входов сигналов и подачей на второй тактовый вход 19 устройства сигнала (фиг. 2), По этому сигналу величины a0bi и aibo через коммутаторы 14 и 15 проходят на входы блоков 1 и 2 хранения констант, на первых и вторых выходах которых формируются величины cico и dido. К этому времени задержанный первым элементом 7 задержки второй тактовый сигнал открывает по вторым входам блока 8, 10, 11 и 13 элементов И, на первые входы которых с выходов первого 1 и второго 2 блоков хранения констант поступают величины ci, di, Cp, do соответственно и, пройдя их, поступают в соответствующие сумматоры 3 и 4. В результате, в этих сумматорах формируются старший и младший 3-е разряды произведения 3-х цифр в позиционно-остаточной системе счисления.

Формула изобретения Устройство для умножения S-x цифр в позиционно-остаточной системе счисления, содержащее два блока хранения констант, два коммутатора, два блока умножения, первый элемент задержки, шесть блоков элементов И и два сумматора, выходы которых соединены соответственно с выходами старшего и младшего разрядов произведения устройства, входы первого и второго операндов которого соединены соответственно с информационными входами первой

группы первого и второго коммутаторов, первые управляющие входы которых соединены с первым тактовым входом устройства и первыми входами элементов И первого и

второго блоков, вторые входы которых соединены соответственно с выходами первого и второго блоков умножения, выходы первого и второго коммутаторов соединены соответственно с входами первого и второго

0 блоков хранения констант, первый выход первого блока хранения констант соединен с первыми входами элементов И третьего блока, вторые входы которых соединены с первыми входами элементов И четвертого,

5 пятого и шестого блоков и выходом первого элемента задержки, вход которого соединен с вторыми управляющими входами первого и второго коммутаторов, второй выход первого блока хранения констант соединен

0 с вторыми входами элементов И пятого блока, первый выход второго блока хранения констант соединен с входом первого сомножителя первого блока умножения и вторыми входами элементов И четвертого блока, вто5 рой выход второго блока хранения констант соединен с входом первого сомножителя второго блока умножения и вторыми входами элементов И шестого блока, выходы элементов И третьего, первого и четвертого

0 блоков соединены соответственно с входами первого, второго и третьего слагаемых первого сумматора, выходы элементов И пятого, второго и шестого блоков соединены соответственно с входами первого, второго

5 и третьего слагаемых второго сумматора, отличающееся тем, что, с целью сокращения аппаратурных затрат, в него введены два мультиплексора, два регистра и второй элемент задержки, выход которого

0 соединен с управляющими входами первого и второго регистров, выходы которых соединены с информационными входами второй группы первого и второго коммутаторов соответственно, а информационные входы 5 соответственно с выходами первого и второго блоков умножения, входы вторых сомножителей соединены соответственно с выходами первого и второго мультиплексоров, первые управляющие входы которых

0 соединены с первым тактовым входом устройства, третий тактовый вход которого со- единен с входом второго элемента задержки и вторыми управляющими входами первого и второго мультиплексоров, инфор5 мационные входы первой группы которых соединены с первым выходом первого блока хранения констант, второй выход которого соединен с информационными входами второй группы первого и второго мультиплексоров.

/8

27

1Q

1 L

Фиг

27

:) do

(Cr)C09

18 d,(d0)

О ОС; (C0)

г r r r r

i

I

Шп}

do№)

Фиг,3

a161 ,aQ-60 Qo-Bj. a1 -B0 CrCo.dj

| Устройство для умножения в системе остаточных классов | 1984 |

|

SU1236472A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения S-ичных цифр в позиционно-остаточной системе счисления | 1989 |

|

SU1633401A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-30—Публикация

1989-06-02—Подача