Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих арифметических устройств, работающих как в системе остаточных классов (СОК), так и в позиционных S-ичных системах,

Целью изобретения является повышение точности.

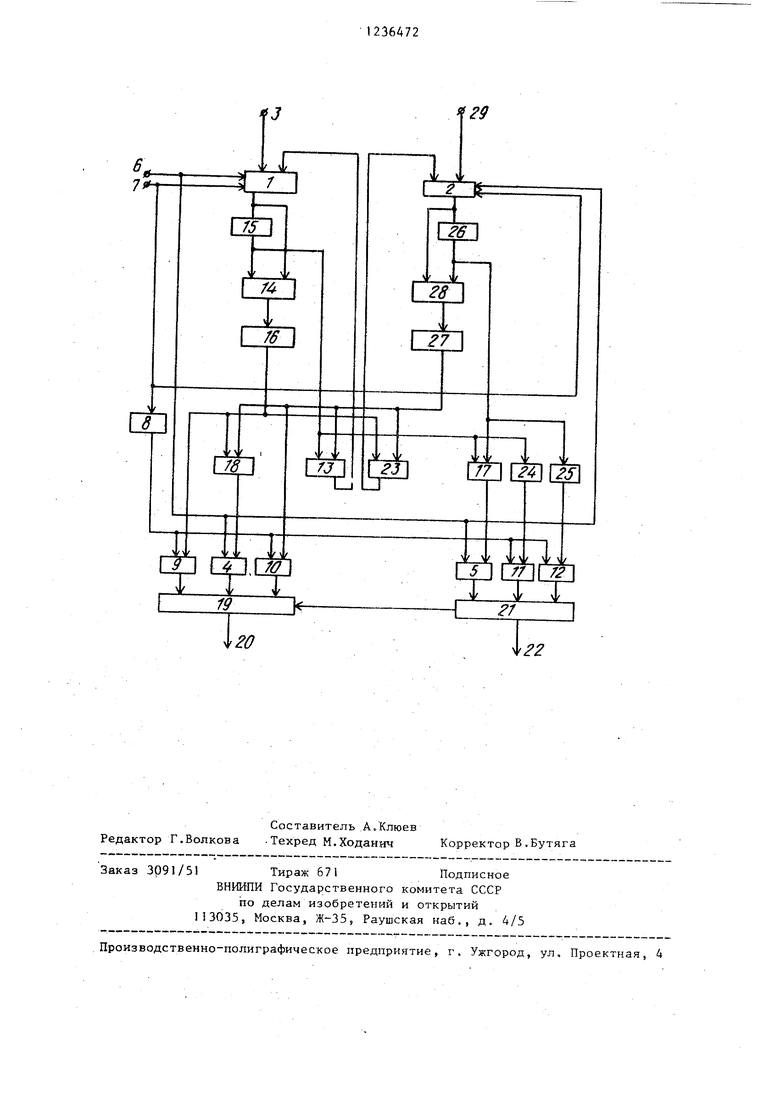

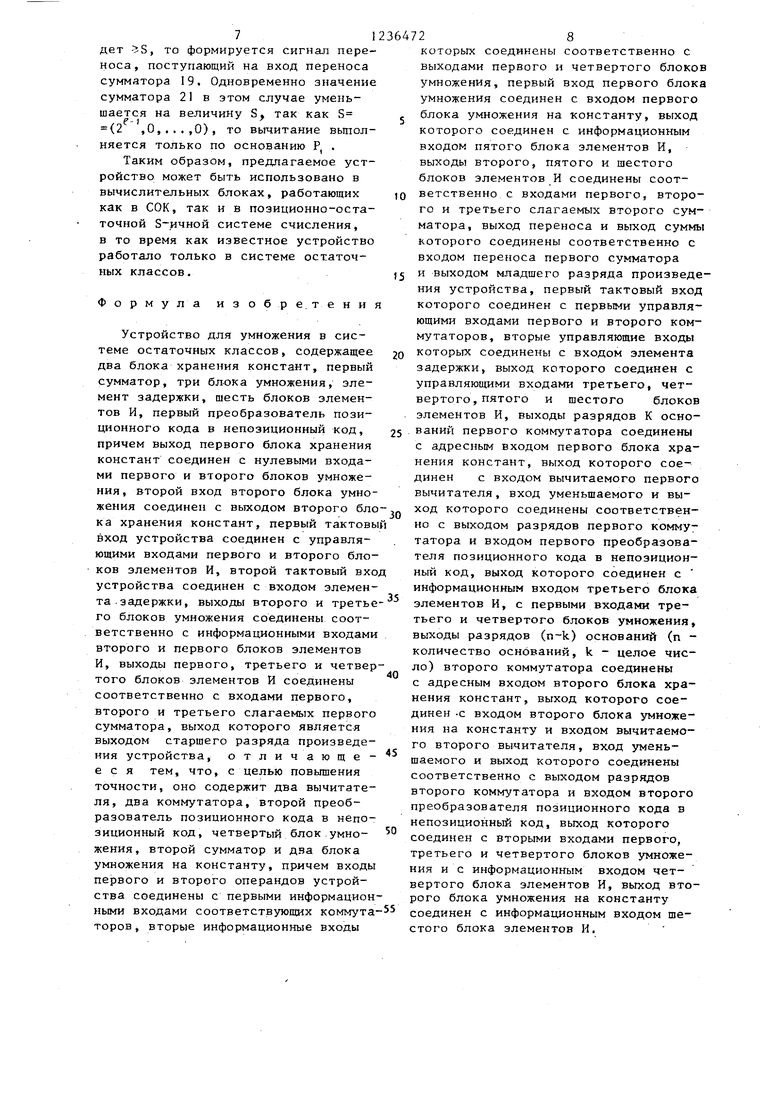

На чертеже представлена схема устройства для умножения в системе остаточных классов.

Устройство для умножения в системе остаточных классов содержит коммутаторы и 2, вход 3 первого операнда, блоки 4 и 5 элементов И, тактовые входы 6 и 7 устройства, элемент 8 задержки, блоки 9-12 элементов И, блок 13 умножения, вычита- тель 14, блок 15 хранения констант, преобразователь 16 позиционного кода в непозиционный код, блоки 17 и 18 умножения, сумматор 19, выход 20 старшего разряда произведения устройства, сумматор 21, выход 22 младшего разряда произведения устройства, блок 23 умножения, блоки 24 и 25 умножения на константу, блок 26 хранения констант, преобразователь 27 позиционного кода в непозиционный код, вычитатель 28, вход 29 второго операнда устройства.

В основу работы устройства для умножения в системе остаточных -классов положено следующее.

h

Обозначим Р П р. R

R, и запише

первый А и второй В операнды в виде , R,+B , (1)

де А

f--l

b.J,

1,-|(

A,A-A,R, ;

B,B-B,R,; txy - ближайшее к х целое.

Тогда

,P+A,,, А,В,

(2)

Всегда можно так сгруппировать основания СОК, что .получится система из двух составных оснований R

J 1

И R. n Р;.

Тогда А и li можно записать в виде вычетов по составным основаниям

А(П,. П); в(Р, ,Р,);

А, (.П,), (П,,п;); в (Р,,)р(р ,Р );

А-А (0,Y );

в-в.

(,о

(3)

(4)

Дальнейшее состоит в том, чтобы поделить (О, у ) и (7 ,0) соответственно на R, и R , в результате чего получаем А,, и В, . Обозначим в С2) B,j, , , представим их в виде (I), т.е, , , , и подставим в (2). Получаем

А В(А, B,+F, +D,)S , + )S°,

(5)

т.е. старший и младший разряды произведения.

В выражении (5) вместо Р применено обозначение S, которое будем называть основанием позиционной S-ич- ной системы, счисления. При этом

возможны следующие случаи.

При в сумматоре 21 результат может достигать величины 2Р. Следовательно, этот сумматор должен быть рассчитан на такой расширенный диапазон, для чего потребуется расширение операндов, поступающих на его входы на основание дополнительного диапазона Р + 1 ; 2. переполнения в сумматоре 21 не будет.

Здесь необходимо, чтобы одно из оснований СОК было четным, т.е. пусть , Тогда можно записать

Р 7

1

К.

R,l/2np. , R п Р

S(

J--1 о,0.

(6)

,0) .

(ПЛР

((T.,-R.,,

если n,R

Р если П , R

(7)

А-А

, (, ,t;); А, ()р; . В2(. )р; в-Е,, (7,,о); ;

Р

(8) (9) (10) (П)

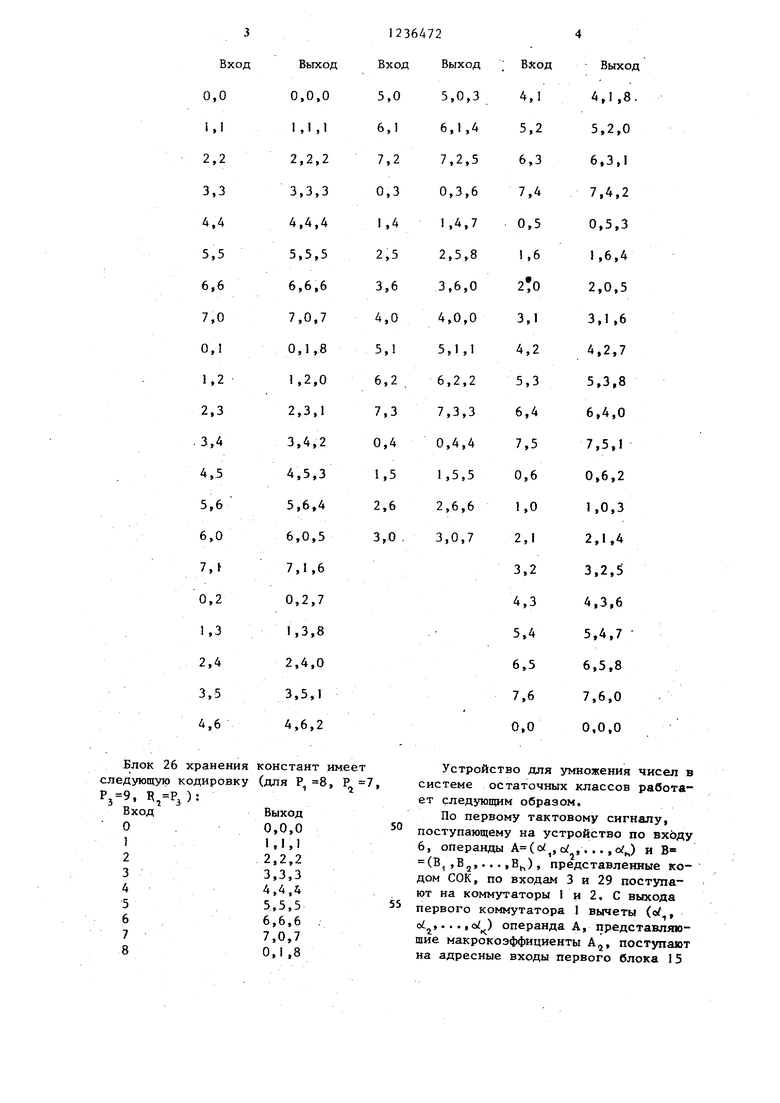

Блок 15 хранения констант имеет следующую, кодировку (рля Р, 8,

7

Р 7 Р Q R : Р 1 г J 3 : л, К, / .

хранения констант, с выхода которого перекодированные в соответствии с (7) на основании Р ,..,,Р поступают на вход вычитаемого вьгчитате- ля 14. На вход уменьшаемого вьтита- теля 14 с выхода первого коммутатора I поступают вычеты (o/,, . . . ..,) операнда А. В вычитателе 14 происходит вычисление величины, пропорциональной AS т.е. вьшолнйется выражение (8). По значению У А, преобразователь 16 кода СОК в соответствии с (9) формирует А, представленное по основаниям Р jPg ,, ..,Fj. С выхода первого блока 15 хранения коне- ,тант снимается макрокоэффициент А, поступающий на соответствующие входы блоков 13, 17 и 24. С выхода преобразователя 16 снимается макрокоэффициент А,, поступающий на входы блоков 23, 18 умножения и блока 9 элементов И,

Одновременно с вьпюда второго коммутатора 2 вычеты (В, , . .. ,В|) операнда В поступают на вход уменьшаемого вычитателя 28. С выхода .второго коммутатора 2 вычета (В, В , ...,В) операнда В, представляющие макрокоэффициент Е , поступают на ад ресные входы второго блока 26 хранения констант, с выхода которого пе рекодированные в соответствии с (10) на основания Р, jP ,..,,Р, поступают на вход вычитаемого вычитателя 28, в котором происходит вычисление величины s пропорциональной В , т.е. вы полняется выражение (4). По значению 2 -Sf соответствии с (11) преобразователь 27 кода СОК формирует В, , представленное по основаниям Р ,Р ,...,Р. Одновременно с выхода второго блока 26 хранения констант снимается макрокоэффициент В , поступающий на соответствующие входы блоков 17 и 25, С выхода второго пре образователя 27 кода СОК снимается макрокоэффициент В , поступающий на вторые входы блоков 13, 23 и 18 умно жения и на вход блока 10, элементов И. С выхода блока 18 умножения величина ,, пройдя открытые элементы И блока 4, поступает на вход 19 сумматора, С выхода блока 17 умножения величина , , пройдя открытые элет-- менты блока И 5, поступает на сумматор 21 .

С выхода блоков 13 и 23 умножения величины , и поступа

ют на вторые информационные входы соответственно первого 1 и второго 2 коммутаторов. На этом первый такт работы устройства заканчивается. Второй такт работы устройства начинается снятием с тактового входа

6сигнала и подачей на. тактовый вход

7устройства сигнала. По этому сиг- калу величины Вир, представленные кодом СОК, через вторые информационные входы поступают-соответственно в первый 1 и второй 2 коммутаторы. Разложение D и F на макрокоэффициенты D, ,, D, F, и F происходит аналогично разложению величин А и В на

20

25

30

3.5

40

45

50

55

макрокоэффициенты А

А, В,

И В„

В результате такого разложения с выхода первого блока 15 хранения констант соответственно снимается макрокоэффициент D , поступающий на соответствующие входы блоков 13, 17 и 24. С выходов преобразователя 16 кода СОК снимается макрокоэффициент D,, поступающий на первые входы блоков 23 и 8 умножения и элементов И блока 9 . С выхода второго блока 26 хранения констант снимается макрокоэффициент F , поступающий на соответствующие входы блоков 17 и 26. ,С выхода преобразователя 27 i-: кода СОК снимается макрокоэффмциент F , поступающий на вторые входьг блоков 13, 23. и 18 умножения ; на вторые входы элементов И блока 10.

Величины D, и F., через открытые элементы И блока 9 и блока 10 поступают на входы сумматора 19.

Величины D и F, , блоками 24 и 25 умножения на константу превращенные в Dj R,, и F, R, , через открытые элементы И блока И и блока 12 поступают на входы сумматора 21,

Перед появлением на выходах блоков 13 и 23 умножения произведений D,, F, и Ц, F,., сигнал с тактового входа 7 снимается. В результате комк-ута- торы I и 2 закрьгваются.

Время задержки элемента 8 выбирается таким, чтобы после снятия сигнала с входа 7 элементы Н блоков 9-S2 оставались открытыми до окончания процесса суммирования в сумматорах 19 и 21. в результате работы которых образз ются старший (с весом s ) и младший (с весом S°) разряды про- .изведения.

Если при,образовании очередной суммы в сумматоре 21 результат будет 5S, то формируется сигнал переноса, поступающий на вход переноса сумматора 19. Одновременно значение сумматора 21 в этом случае уменьшается на величину S, так как S (2 ,0,...,0), то вычитание выполняется только по основанию Р .

Таким образом, предлагаемое устройство может быть использовано в вычислительных блоках, работающих как в СОК, так и в позиционно-оста- точной S-ичной системе счисления, в то время как известное устройство работало только в системе остаточных классов.

Формула из об ре. тения

Устройство для умножения в системе остаточных классов, содержащее два блока хранения констант, первый сумматор, три блока умножения, элемент задержки, шесть блоков элементов И, первый преобразователь позиционного кода в непозиционный код, причем выход первого блока хранения констант соединен с нулевыми входами первого и второго блоков умножения, второй вход второго блока умножения соединен с выходом второго бло ка хранения констант, первый тактовы вход устройства соединен с управляющими входами первого и второго блоков элементов И, второй тактовый вхо устройства соединен с входом элемента.задержки, выходы второго и третьего блоков умножения соединены соответственно с информационными входами второго и первого блоков элементов И, выходы первого, третьего и четвертого блоков элементов И соединены соответственно с входами первого, второго и третьего слагаемых первого сумматора, выход котарого является выходом старшего разряда произведения устройства, отличающее с я тем, что, с целью повьшения точности, оно содержит два вычитате- ля, два коммутатора, второй преобразователь позиционного кода в непозиционный код, четвертый блок умно- жения, второй сумматор и два блока умножения на константу, причем входы nejpBoro и второго операндов устройства соединены с первыми информационными входами соответствующих коммута торов, вторые информационные входы

,

)о }5

20 25 5

5

0

которых соединены соответственно с выходами первого и четвертого блоков умножения, первый вход первого блока умножения соединен с входом первого блока умножения на константу, выход которого соединен с информационным входом пятого блока элементов И, выходы второго, пятого и шестого блоков элементов И соединены соответственно с входами первого, второго и третьего слагаемых второго сумматора, выход переноса и выход суммы которого соединены соответственно с входом переноса первого сумматора и выходом младшего разряда произведения устройства, первый тактовый вход которого соединен с первыми управляющими входами первого и второго коммутаторов, вторые управляющие входы которых соединены с входом элемента задержки, выход которого соединен с управляющими входами третьего, четвертого, пятого и шестого блоков элементов И, выходы разрядов К оснований первого коммутатора соединены с адресным входом первого блока хранения констант, выход которого соединен с входом вычитаемого первого вычитателя, вход уменьщаемого и выход которого соединены соответственно с выходом разрядов первого коммутатора и входом первого преобразователя позиционного кода в непозиционный код, выход которого соединен с информационным входом третьего блока элементов И, с первыми входами третьего и четвертого блоков умножения, выходы разрядов (n-k) оснований (п - количество оснований, k - целое число) второго коммутатора соединены с адресным входом второго блока хранения констант, выход которого соединен -с входом второго блока умножения на константу и входом вычитаемого второго вычитателя, вход уменьшаемого и выход которого соединены соответственно с выходом разрядов второго коммутатора и входом второго преобразователя позиционного кода в непозиционный код, выход которого соединен с вторыми входами первого, третьего и четвертого блоков умножения и с информационным входом четвертого блока элементов И, выход второго блока умножения на константу соединен с информационным входом шестого блока элементов И,

I

20

Составитель .АоКлюев Редактор Г.Волкова -Техред М.Ходанич Корректор В .Бутяга

заказ 3091/5 Тираж 671Подписное

BH№fflH Государственного комитета СССР

по делам изобретений и открытий II3035, Москва, Ж-35, Раушская иаб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

I

22

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Устройство для умножения в системе остаточных классов | 1984 |

|

SU1335998A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ S-ИЧНЫХ ЦИФР В ПОЗИЦИОННО-ОСТАТОЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ | 1991 |

|

RU2006919C1 |

| Устройство для умножения | 1985 |

|

SU1275440A1 |

| Устройство для суммирования | 1984 |

|

SU1233153A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| @ -Ичный сумматор | 1983 |

|

SU1166097A1 |

| Арифметическое устройство по модулю | 1986 |

|

SU1425666A1 |

| Устройство для умножения S-ичных цифр в позиционно-остаточной системе счисления | 1989 |

|

SU1633401A1 |

| Арифметическое устройство в системе остаточных классов | 1984 |

|

SU1176326A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих арифметических устройств, работающих как в системе остаточных классов (сок), так и в позиционных S-ичньгх системах. Цель изобретения повышение точности работы устройства. Устройство для y ffloжeния в СОК содержит два блока хранения констант, первый сумматор, три блока умножения, элемент задержки и шесть групп элементов И. Новым в устройстве для умножения в СОК является то, что в него дополнительно введены три сумматора, четвертый блок умножения, два блока умножения на константу, два преобразователя кода СОК и два мультиплексора. I ил. С to оо а 4 IND

| Устройство для умножения одноразрядных @ -ичных чисел в системе остаточных классов | 1982 |

|

SU1100619A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения в системе остаточных классов | 1980 |

|

SU962942A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-07—Публикация

1984-09-20—Подача