оэ

ОЭ

оо

Јъ

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих арифметических устройств, работающих в позиционно-остаточной системе счисления.

Цель изобретения - уменьшение объема оборудования и увеличение быстродействия.

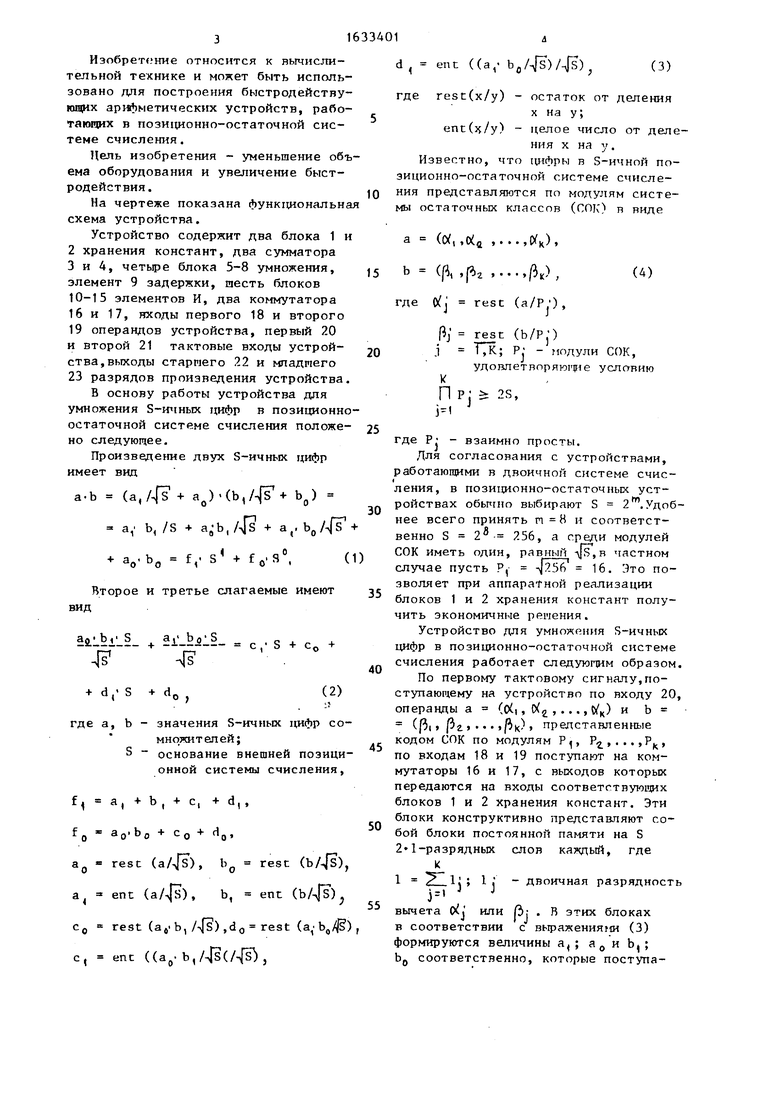

На чертеже показана функциональна схема устройства.

Устройство содержит два блока 1 и

2хранения констант, два сумматора

3и 4, четыре блока 5-8 умножения, элемент 9 задержки, шесть блоков 10-15 элементов И, два коммутатора 16 и 17, нходы первого 18 и второго 19 операндов устройства, первый 20 и второй 21 тактовые входы устройства, выходы старшего 22 и младшего 23 разрядов произведения устройства.

В основу работы устройства для умножения S-ичных цифр в позиционно остаточной системе счисления положено следующее.

Произведение двух S-ичных цифр имеет вид

а-b (а, 4 + ао)(Ь, bfl)

+ f

а-Ь./лГз

+ а.

boAfs1

s + fe.s,

(1)

Второе и третье слагаемые имеют

вид

§.aLblLS + а,. s + с

4

Я

+ d,1 S + d

0 )

(2)

а,

b - значения S-ичных цифр сомножителей;

S - основание внешней позиционной системы счисления,

4 b , + с,

+ d

i

а0 Ь0 + с0 + dc rest (а/лПз), I ent (aA|S),

rest

b. ent

,

(bAjs), (bAfs);

rest (ae- b, Afs) ,d0 rest (a- b0/|§) , ent ((a0-b,/4s(/4s),

d

ent ((a,- )/-jS);

(3)

где rest(x/y) - остаток от деления

x на у;

ent(x/y) - целое число от деления х на у.

Известно, что цифры в S-ичной по- эиционно-остаточной системе счисления представляются по модулям системы остаточных классов (СОК) в виде

а (tf, ,0(fl b ф, ,рг

,0fk)t Л,

(4)

где

0(j rest (a/P ) ,

0

Pj rest

j Пк;

(b/Pj)

подули СОК,

К

П Н

Pi удовлетворяюг1ие условию

2S,

где Р: - взаимно просты.

Для согласования с устройствами, работающими в двоичной системе счисления, в позиционно-остаточных устройствах обычно выбирают S 2m.Удобнее всего принять и соответственно S 1 256, а среди модулей СОК иметь один, равный л|8.в частном

случае пусть Р, V-56 16. Это позволяет при аппаратной реализации блоков 1 и 2 хранения констант получить экономичные решения.

Устройство для умножения S-ичных цифр в позиционно-остаточной системе счисления работает следуюпим образом.

По первому тактовому сигналу,поступающему на устройство по входу 20, операнды а (о((, (Х , ..., к) и b ф| fit - ) представленные кодом СОК по модулям Р, РЈ,...,РК, по входам 18 и 19 поступают на коммутаторы 16 и 17, с выходов которых передаются на входы соответствующих блоков 1 и 2 хранения констант. Эти блоки конструктивно представляют собой блоки постоянной памяти на S 2 1-разрядных слов каждый, где k

5

1

J:

ij; ij

- двоичная разрядность

вычета (Xj или ft: . В этих блоках с внра енляю (з)

в соответствии

формируются величины а

bn соответственно, которые поступао и Ьи

ют на первые и вторые входы блоков 5-8 умножения. 5 н 8 умножения формируют соответственно величины

«

ки

b -S, которые через блоа0- Ь,- л и

aV ho

b,- S и

11 и 14 элементов И поступают в соответствующее первый 3 и второй 4 сумматоры. Одновременно блоками 6 и 7 умножения формируются величины

-JS, которые поступают на вторые информационные входы соответственно первого 16 и второго 17 коммутаторов. На этом первый такт работы устройства заканчивается.

Второй такт работы устройства начинается снятием с первого тактового входа 20 сигнала и подачей сигнала на второй тактовый вход 21. По этому сигналу величины а Ь . -Js7 и

а bQ. через вторые информационные входы коммутаторов 16 и 17 проходят на выходы последних, а с их выходов в виде величины с,1 о, с0, d,- S и d0 поступают на входы блоков 5-8 умножения, вторые входы блоков 12 и 10 элементов И и входы блоков 13 и 15 элементов И. Величины S и d S через блоки 10 и 12 элементов И поступают на сумматор 3, величины с и d0 через блоки 13 и 15 элементов И поступают на сумматор 4. Перед появлением на выходах блоков 6 и 7 умножения величин с.

1

и г.,

о

21

сигнал с

второго тактового входа 21 снимается. В результате коммутаторы 16 и 17

закрываются. i

Время задержки элемента 9 выбираеся таким, чтобы после снятия сигнала с входа 21 элемента и блоков 10, 13 15 оставались открытыми до окончания процесса суммирования в сумматорах 3 и 4, в результате работы которых

и разряды произвеобразуются ставший (с весом S ) младший (с весом S°) дения.

Формула изобретения

Устройство для умножения S-ичных цифр в позиционно-остаточной системе счисления, содержащее два блока хранения констант, два сумматора, четыре блока умножения, элемент задержки, шесть блоков элементов И и два коммутатора, пер вые информационные входы которых соединены соответствено с входами первого и второго операндов устройства, первый тактовый вход ко

10

15

20

25

33401б

торого соединен с первыми управляющими входами первого и второго коммутаторов и первыми входами первого и второго блоков элементов И, второй тактовый вход устройства соединен с вторыми управляющими входами первого и второго коммутаторов и входом элемента задержки, выход которого соединен с первыми входами третьего, четвертого, пятого н шестого блоков элементов Н, выходы первого и второго коммутаторов соединены соответственно с входами первого и второго блоков хранения констант, входы первых сомножителей первого и второго блоков умножения и второй вход третьего блока элементов И объединены между собой, второй вход ч-етвертого блока элементов II объединен с входом второго сомножителя первого блока умножения и входом первого сомножителя третьего блока умножения, выход которого соединен с вторым информационным входом первого коммутатора, вход второго сомножителя третьего блока умножения соединен с первым выходом первого блока хранения констант и входом первого сомножителя четвертого блока умножения, вход второго сомножителя которого соединен с первым выходом второго блока хранения констант, пыход второго блока умножения соединен с вторым информационным входом второго коммутатора,выходы первого и четвертого блоков умножения соединены соответственно с вторыми входами первого и второго блоков элементов И, выходы третьего, первого и четвертого блоков элементов И соединены соответственно с входами первого,второго и третьего слагаемых первого сумматора,выход которого соединен с выходом старшего разряда произведу дения устройства , выход мпадшего разряда произведения которого соединен с выходом второго сумматора, входы первого, второго и третьего слагаемых которого соединены соответственно с выходами пятого, второго и шестого блоков элементов II, о т л и чающееся тем, что,с целью уменьшения объема оборудования и увеличения быстродействия, вторые ВЕКОДЫ первого и второго блоков хранения констант соединены соответственно с входами первого и второго сомножителей первого блока умножения, первый выход первого блока хранения констант со30

35

40

50

55

716334018

единен с вторым входом пятого блокавходом второго сомножителя второго

элементов И, первый выход второгоблока умножения и вторым входом шесблока хранения констант соединен стого блока элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения S-х цифр в позиционно-остаточной системе счисления | 1989 |

|

SU1730625A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ S-ИЧНЫХ ЦИФР В ПОЗИЦИОННО-ОСТАТОЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ | 1991 |

|

RU2006919C1 |

| Устройство для умножения S-ичных цифр в позиционно-остаточной системе счисления | 1991 |

|

SU1837284A1 |

| Устройство для умножения в системе остаточных классов | 1984 |

|

SU1236472A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Устройство для умножения в системе остаточных классов | 1984 |

|

SU1335998A1 |

| Устройство для умножения | 1985 |

|

SU1275440A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

Изобретение относится к вычислительной технике и может быть исполь- човано для построения быстродействующих арифметических устройств, работающих в позиционно-остаточной системе счисления. Цель изобретения - повышение быстродействия и уменьшение объема оборудования. Устройство содержит два блока 1 и 2 хранения констант , два сумматора 3 и 4, четыре блока 5-8 умножения, элемент 9 задержки, шесть блоков 10-15 элементов И, два коммутатора 16 и 17 и соответствующие связи, которые обеспечивают за счет выбора коэффициента 4s избежать возникновения сигнала переноса из сумматора 4 в сумматор 3, а также получить более регулярную структуру устройства за счет применения более современного алгоритма. 1 ил. (Л

| Устройство для умножения в системе остаточных классов | 1980 |

|

SU962942A1 |

| Г, 06 F 7/72, 1980 | |||

| Устройство для умножения в системе остаточных классов | 1984 |

|

SU1236472A1 |

| Г, 06 F 7/72, 1484. | |||

Авторы

Даты

1991-03-07—Публикация

1989-05-22—Подача