формационными входами блока элементов ИЛИ, выход которого соединен с вторым информационным входом первого регистра, разрядный выход и третий информа- ционный вход которого соединен соответственно с информационным входом и выходом четвертого регистра, разрядный выход и информационный вход второго регистра соединены соответствен- но с информационным входом и выходом преобразователя кодов, разрядный выход третьего регистра соединен с четвертым информационным входом первого регистра, информационный выход счет- чика соединен с входом младшего разряда третьего регистра, управляющий вход блока информационной разгрузки, вход разрешения выдачи четвертого регистра, вход разрешения приема, первый и второй выходы разрешения выдачи первого регистра, первый и второй вправляющие входы коммутатора, входы разрешения приема и разрешения выдачи преобразователя кодов, входы разрешения сдвига, разрешения выдачи обратного кода, разрешения выдачи прямого кода второго регистра, входы обнуления и разрешения выдачи счетчика, вход разрешения выдачи третьего регистра соединены соответственно с выходом второго элемента задержки, первым выходом второго распределителя импульсов, выходами пятого,-шестого и седьмого элементов ИЛИ, выходами первого и второго триггеров, выходами восьмого, девятого, второго, десятого, одиннадцатого и четвертого элементов ИЛИ, выходом пятого элемента И, входом третьего элемента задержки блока управления, второй вход первого элемента И, второй вход второго элемента И, первые входы шестого и пятого элементов И, входы третьего, четвертого и пятого распределителей им- пульсов которого соединены соответственно с выходами неравенства и равенства схемы сравнения, прямым и инверсным выходами знака второго сумматора, входами операций вычитания, сложения и деления устройства, причем в блоке управления выход первого элемента задержки соединен с вторым входом первого элемента ИЛИ, выход которого через четвертый элемент задержки соединен с первым входом первого элемента И, выход которого соединен с первыми входами седьмого и одиннадцатого элементов ИЛИ, второй выход пер5 О 5

0

5

вого распределителя импульсов соединен с первыми входами третьего и пятого элементов ИЛИ, выход второго элемента И соединен через пятый элемент задержки с вторыми входами третьего и четвертого элементов И, выходы которых соединены соответственно с первым входом шестого элемента ИЛИ и с третьим входом первого элемента ИЛИ, выход второго элемента И соеди- нен с первыми входами второго элемента ИЛИ и двенадцатого элемента ИЛИ, выход которого соединен со счетным входом счетчика, выходы равенства и неравенства нулю которого соединены соответственно с первыми входами седьмого и восьмого элементов И, вторые входы которых соединены с вторым выходом второго распределителя импульсов, вход которого соединен с вторыми входами двенадцатого элемента ИЛИ, второго и четвертого элементов ИЛИ, выход седьмого элемента И через третий элемент задержки соединен с вторым входом шестого элемента ИЛИ, выход восьмого элемента И соединен с первым входом тринадцатого элемента ИЛИ, выход которого через шестой элемент задержки соединен с вторыми входами пятого и шестого элементов И, выходы которых соединены соответственно с входами второго распределителя импульсов и седьмого элемента задержки, выход и вход которого соединены соответственно с вторыми входами тринадцатого и третьего элементов ИЛИ, выход первого элемента задержки соединен с третьим входом четвертого элемента ИЛИ и с первым входом четырнадцатого элемента ИЛИ, выход которого соединен с единичным входом первого триггера, нулевой вход которого соединен с нулевым входом второго триггера, с входом второго элемента задержки и с выходом шестого элемента ИЛИ, вход третьего распределителя импульсов соединен с вторым входом одиннадцатого и первым входом восьмого элементов ИЛИ, первым входом пятнадцатого элемента ИЛИ, выход которого соединен с единичным входом второго триггера, первый, второй, третий и четвертьй выходы третьего распределителя импульсов соединены соответственно с первыми входами девятого, десятого, вторым входом пятого и третьим входом шестого элементов ИЛИ, первый вход десятого элемента ИЛИ соединен с вторым входом седьмого элемента ИЛИ, третий вход которого соединен с третьим входом одиннадцатого элемента ИЛИ, с вторым входом четырнадцатого элемента ИЛИ, с входом четвертого распределителя импульсов, первый и второй выходы которого соединены соответственно с третьим входом пятого и четвертым входом шестого элементов ИЛИ, четвертый вход четвертого элемента ИЛИ соединен с вторым входом пятнадцатого элемента ИЛИ, вторым установочным входом счетчика и входом пятого распределителя импульсов, первый, второй и третий выходы которого соединены соответственно с вторыми входами восьмого и девятого элементов ИЛИ, третьим входом тринадцатого элемента ИЛИ, выход которого соединен с четвертым входом седьмого и вторым входом десятого элементов ИЛИ, второй вход восьмого элемента ИЛИ соединен с четвернен с четвертым входом пятого элемента ИЛИ.

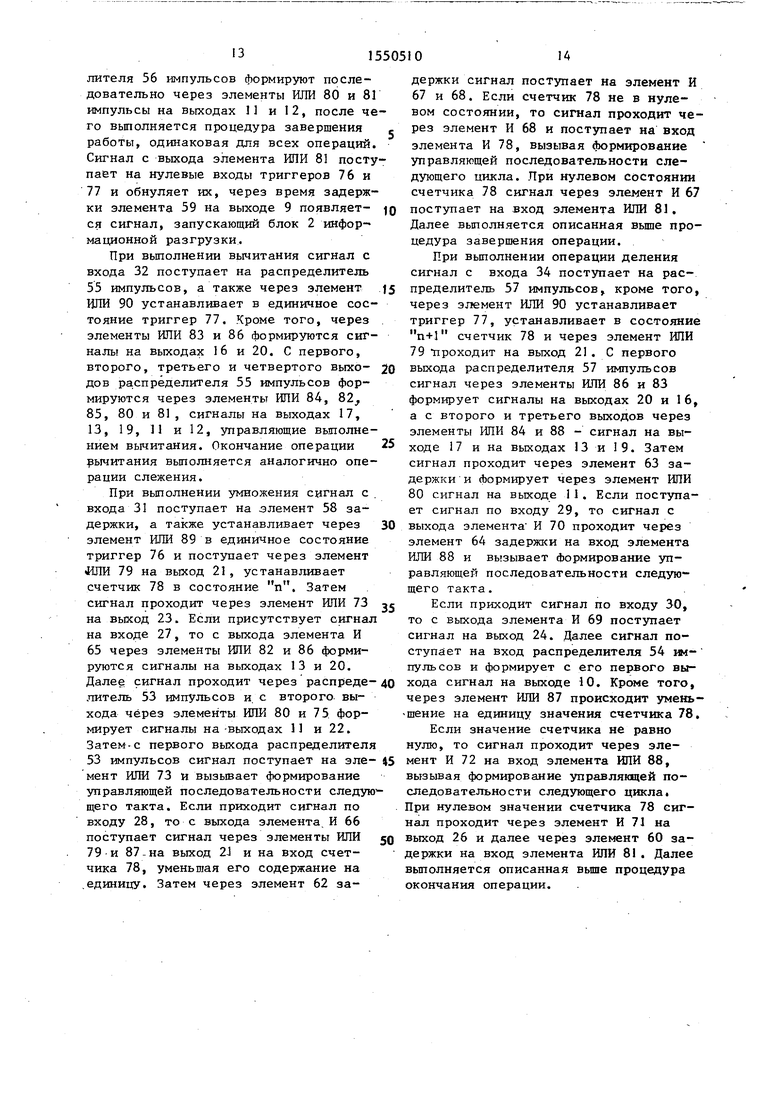

2. Устройство по п. 1, отличающееся тем, что преобразователь кодов содержит два регистра, группу узлов деления на константу, сумматор, причем выходы разрядов первого регистра соединены с входами соЮ ответствующих узлов деления на константу группы, выходы остатков которых соединены с первыми входами соответствующих разрядов сумматора, выходы частных узлов деления на констанJ5 ту группы соединены со сдвигом на один разряд влево с вторыми входами разрядов сумматора, выход которого соединен с информационным входом второго регистра, выход которого, инфор-

20 мационный вход первого регистра, вход разрешения приема первого регистра и вход разрешения выдачи второго регистра соединены соответственно с выходом, информационным входом, входами

тым входом одиннадцатого элемента ИЛИ, 25 разрешения приема и разрешения выда- второй вход пятого элемента И соеди-чи преобразователя кодов.

нен с четвертым входом пятого элемента ИЛИ.

2. Устройство по п. 1, отличающееся тем, что преобразователь кодов содержит два регистра, группу узлов деления на константу, сумматор, причем выходы разрядов первого регистра соединены с входами соответствующих узлов деления на константу группы, выходы остатков которых соединены с первыми входами соответствующих разрядов сумматора, выходы частных узлов деления на констан5 ту группы соединены со сдвигом на один разряд влево с вторыми входами разрядов сумматора, выход которого соединен с информационным входом второго регистра, выход которого, инфор-

0 мационный вход первого регистра, вход разрешения приема первого регистра и вход разрешения выдачи второго регистра соединены соответственно с выходом, информационным входом, входами

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода одной позиционной системы счисления в другую | 1980 |

|

SU960793A1 |

| Устройство для деления | 1980 |

|

SU928344A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Устройство для умножения в позиционной избыточной ( @ , @ )-системе счисления | 1982 |

|

SU1067498A1 |

| Устройство для умножения | 1979 |

|

SU920705A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1103225A1 |

Изобретение относится к вычислительной технике и может быть использовано для суммирования чисел в минимальной форме представления и получения суммы в этой же форме без приведения. С целью расширения области применения за счет суммирования с получением результата в минимальной форме представления, сумматор в каждом разряде содержит триггер 1, десять элементов ИЛИ 12 - 21, десять элементов И 2 - 11, пять элементов ИЛИ-НЕ 22 - 26 с соответствующими связями. 2 ил.

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых вычислительных машин с фиксированной запятой, работающих в позиционных избыточных (г,k)-системах счисления.

Целью изобретения является расширение функциональных возможностей за счет выполнения операций деления, ело жения, .вычитания и умножения.

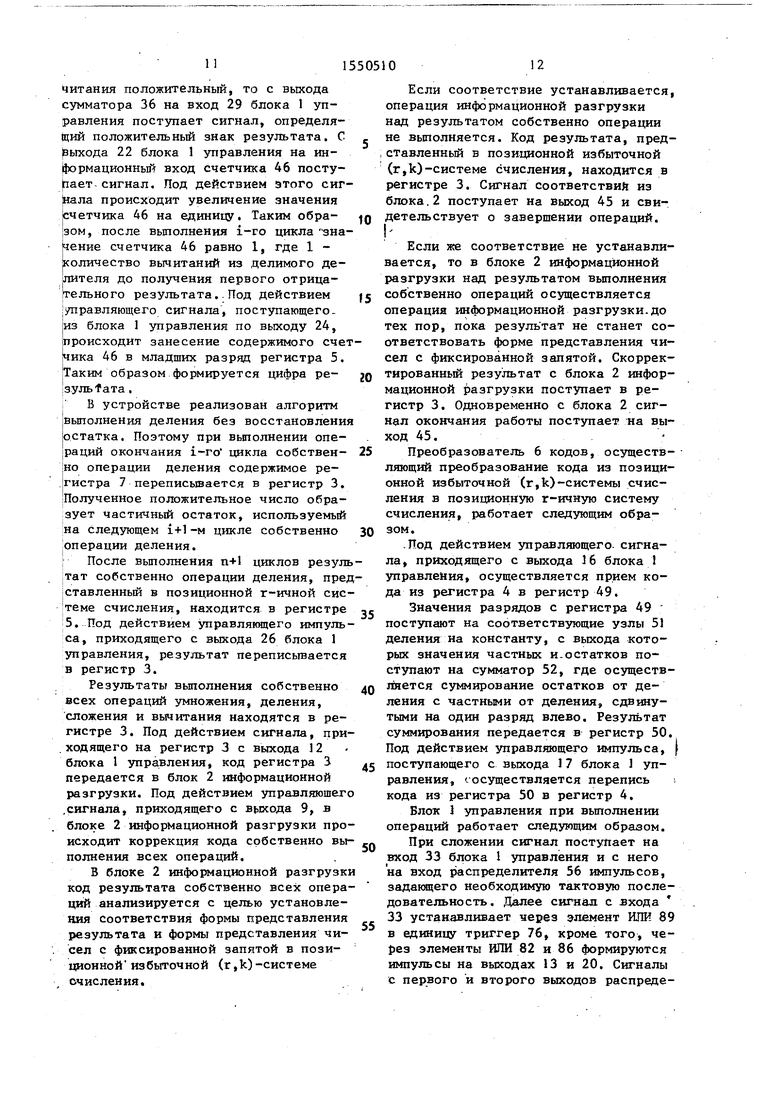

На Лиг. 1 приведена структурная схема арифметического устройства; на фиг. 2 - структурная схема преобразователя кодов; на фиг. 3 - структурная схема блока управления. ч

Арифметическое устройство содержит блок Г управления, блок 2 информационной разгрузки, регистры 3-5, преобразователь 6 кодов, регистр 7, коммутатор 8, выходы 9-26 и входы 27-34 блока 1 управления, сумматоры 35 и 36, блок 37 элементов ИЛИ, выход 38 регистра 3, выходы 39 и 40 обратного и прямого кодов регистра 7, выходы 41- 44 коммутатора 8, выход 45 конца работы устройства, счетчик 46, схему 47 сравнения и блок 48 элементов И.

35

40

45

50

55

Преобразователь 6 кодов (фиг. 2) включает регистры 49 и 50, группу узлов 51 деления на константу и сумматор 52.

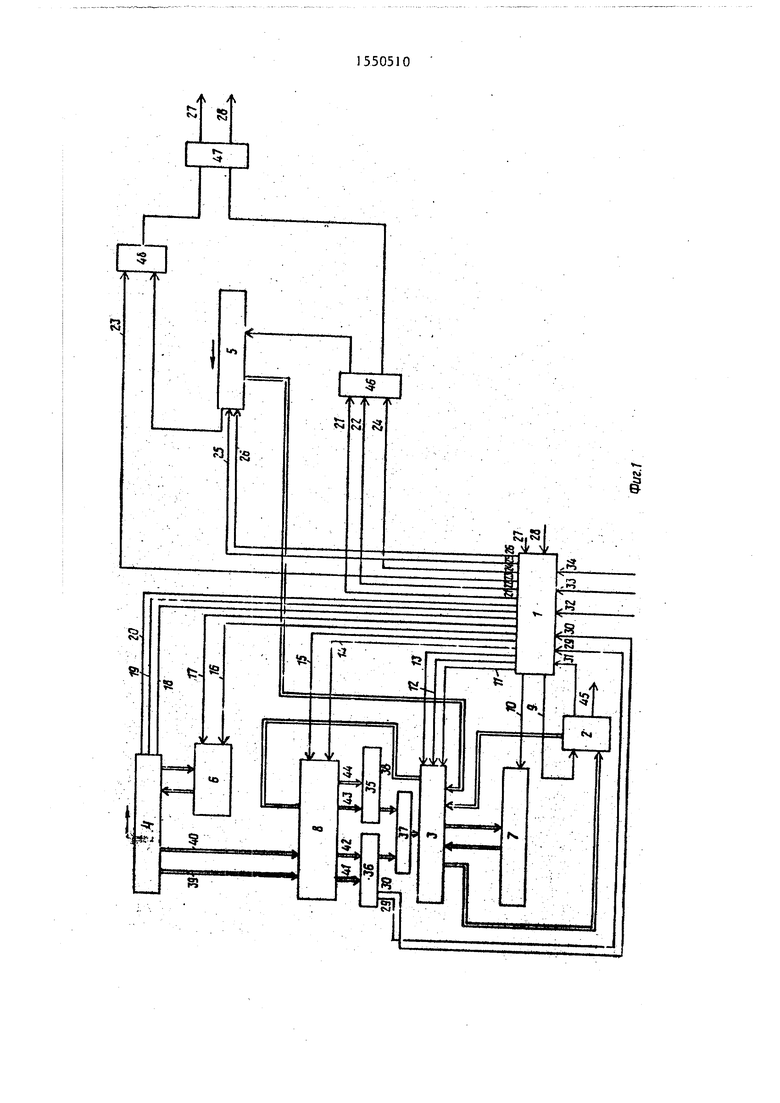

Блок 1 управления (фиг. 3) содержит распределители 53-57 импульсов, элементы 58-64 задержки, элементы И 65-72, элементы ИЛИ 73-75, триггеры 76 и 77, счетчик 78 и элементы ИЛИ 79-90. Регистры 3, 4 и 7 имеют 2п k-ичных информационных разрядов и , один r-ичный знаковый разряд.

Регистр 5 содержит п информационных k-ичных разрядов и один г-ичный знаковый разряд.

Счетчик 46 включает 31о§4К двоичных разрядов.

Сумматор 36 работает в позиционной r-ичной системе счисления, а сумматор 35 - в позиционной избыточной (г,k)-системе счисления.

Сумматор 36 содержит один знаковый и 2п информационных r-ичных разрядов, а сумматор 35 - 2п информационных k-ичных разрядов.

Регистр 49, группа узлов 51 деления на константу и сумматор 52 в позиционной r-ичной системе сложения, регистр 50 преобразователя 6 кодов

имеют соответственно 2п и 2п+1 разрядов .

Блок 2 информационной разгрузки идентичен прототипу.

Коммутатор 8 выполняет следующие передачи.

При выполнении операций сложения и умножения операнды в прямом коде поступают с выходов 38 и 40 на комму- татор 8„ Разрешающий сигнал Iна коммутатор 8 поступает с выхода 14 блока 1 управления. Коды операндов проходят через коммутатор 8 и по выходам 43 и 44 соответственно поступают на входы сумматора 35.

При выполнении операций вычитания и деления уменьшаемое (делимое в прямом коде поступает с выхода 38 на коммутатор 8. Вычитываемое (дели- тель) в обратном коде поступает с выхода 39 на коммутатор 8. Разрешающий сигнал на коммутатор 8 поступает с вы- хода 15 блока 1 управления. Коды операндов проходят через коммутатор 8 и с выходов 41 и 42 подаются на сумматор 36.

Арифметическое устройство выполняет операции сложения, вычитания, умножения и деления. Процесс выполнения всех операций над числами, представленными в позиционной избыточной (ч.к.) системе счисления, в общем случае состоит из собственно названных операций и коррекции результата, связанной с выполнением операции информационной разгрузки,ч

Перед началом выполнения операции сложения операнды находятся в регистрах 3 и 4.

Блок 1 управления выдает сигналы, поступающие по выходам 13 и 20 на управляющие входы выдачи кодов регистров 3 и 4 соответственно. Прямые коды этих регистров по выходам 38 и 40 поступают на коммутатор 8, на вход управления которого поступает сигнал с выхода 14. Операнды поступают на сумматор 35, далее результат проходит через блок 37 элементов ИЛИ и под действием управляющего импульса, приходящего из блока 1 управления по выходу 11, осуществляется прием кода результата в регистр 3. На этом выполнение собственно операции сложения заканчивается.

Перед началом выполнения операции вычитания уменьшаемое находится в регистре 3, а вычитаемое - в регистре

,

0

е

0

Преобразование выполняется следующим образом.

-Под действием управляющего импульса, приходящего из блока 1 управления по выходу 20 на регистр 4, код вычитаемого передается в преобразователь 6 кодов, Прием кода в преобразователь 6 происходит под действием управляющего импульса, поступающего по выходу 1 6 из блока 1 управления. После преобразования кода код вычитаемого, представленный в позиционной г-йчной системе счисления, передается обратно в регистр 4. Вычитание выполняется следующим образом. Из блока 1 управления по выходам 13 и 1 9 на регистры 3 и 4 соответственно приходят управляющие сигналы. Под действием этих сигналов содержимое регистра 3 подается з прямом коде на .коммутатор 8 по выходу 38, а содержимое регистра 4 - в обратном коде по выходу 39.Поступает управляющий сигнал с выхода 15, и операнды поступают с коммутатора 8 на сумматор 36, далее результат через блок 37 элементов ИЛИ поступает под действием сигнала с выхода 11 в регистр 3.

Результат операции вычитания представлен в позиционной г-ичной системе счисления.

Перед началом выполнения операции умножения множитель находится в регистре 5, а множимое - в регистре 4.

Собственно операция умножения выполняется за п циклов, Б каждом очередном цикле множимое умножается на соответствующий i-й (i 1, 2, ..., п) разряд множителя. Пикл реализуется за 1+1 тактов, где 1 - цифра разряда множителя с номером i.

Перед началом выполнения счетчик 46 обнулен.

В первом такте цикла из блока 1 управления по выходу 23 на блок 48 элементов И поступает управляющий сигнал. Под действием этого сигнала происходит сравнение цифры старшего разряда регистра 5 со значением счетчика 46. Значение цифры старшего разряда регистра 5 через блок 48 поступает на первый вход схемы 47 сравнения. На второй вход схемы 47 сравнения посту пает значение счетчика 46. Если значение цифры стартего разряда не равно нулю, то с первого выхода схемы 47 сравнения по выходу 27 поступает сигнал в блок 1 управления. Под действием этого сигнала блок 1 управления выдает сигнал, поступающий на управ-, ляющие входы выдачи кодов регистров 3 и 4. Прямые коды поступают на коммутатор 8, далее суммируются и через блок 37 элементов ИЛИ заносятся в регистр 3. Одновременно по выходу 22 блока 1 управления поступает сигнал на информационный вход счетчика 46 тактов. Значение счетчика тактов увеличивается на единицу. Второй такт цикла снов а начинает.ся с поступления управляющего сигнала на блок 48 по выходу 23. Происходит сравнение цифры старшего разряда регистра 5 с значением счетчика 46, равным единице.

Если значение цифры старшего разряда регистра 5 не равно единице, то выполняется третий такт цикла выполнения собственно операции умножения и так далее.

Перед началом выполнения 1+1-го такте в счетчике, тактов находится число 1. Происходит сравнение цифры старшего разряда регистра 5 со значением счетчика 46. В этом случае с второго выхода схемы 47 сравнения по выходу 28 в блок J управления поступает сигнал. Под действием этого сигнала в блоке-1 управления вырабатываются сигналы, поступающие по выходам 21 и 25 соответственно на управляющий вход счетчика 46 и вход управления сдвигом регист.ра 5. Содержимое, счетчика 46 становится равным нулю, а содержимое регистра 5 сдвигается на один разряд влево. Сигналом на выходе 18 производится также сдвиг вправо на один разряд содержимого регистра 4т

После выполнения п циклов результат собственно операции умножения двух чисел, представленный в позици-- онной-избыточной (г,Ю-системе счисления, находится в регистре 3.

Перед началом выполнения операции деления делимое находится в регистре 3, а делитель - в регистре 4.

Операции деления предшествует операция преобразования кода делителя

0

5

0

5

0

5

0

5

0

5

из позиционной (г,k)-системы счисления в позиционную г-ичную систему счисления, выполняемая описанным выше , способом.

Собственно операция деления выпол-4 няется за п+1 циклов. В каждом цикле вычисляется одна цифра частного (результат). Количество тактов в каждом цикле - переменное и зависит от значения определяемой цифры результата. Первый такт каждого цикла начинается с вычитания из содержимого регистра 3 содержимого регистра 4. Вычитание происходит описанным выше способом. Одновременно содержимое регистра 3 поступает в регистр 7. После выполнения вычитания его результат поступает в регистр 3.

При делении чисел во избежание переполнения берут делимое меньше, чем делитель. В соответствии с этим результат выполнения операции вычитания в первом цикле - отрицательный и с выхода сумматора 36 на вход 30 поступает на блок 1 управления управляющий сигнал,- определяющий отрицательный знак результата. Под действием этого сигнала блок J управления выдает управляющий сигнал, поступающий по выходу 24 на счетчик 46, происходит пе- репись содержимого счетчика 46 в младший разряд регистра 5. Далее под действием управляющего импульса, приходящего с выхода 25 блока I управления, происходит сдвиг содержимого регистра 5 на один разряд влево, а под действием управляющего импульса, приходящего с выхода 2J блока 1, счетчик 46 устанавливается в нулевое состояние. В первом цикле происходит формирование целой части результата, равной нулю. Далее управляющий сигнал из блока 1 управления с выхода 10 поступает на регистр 7, ас выхода 18 на регистр 4.

Содержимое регистра 7 переписывается в регистр 3, а содержимое регистра 4 сдвигается на один разряд вправо.

На этом выполнение первого цикла собственно операции деления заканчивается. При выполнении тактов циклов : с номерами 2,...,п+1 результат выполнения операции вычитания из делимого (частичного остатка) делителя может оказаться как положительным, так и отрицательным.

Если при очередном такте i-ro цик- ла результат выполнения операции вычитания положительный, то с выхода сумматора 36 на вход 29 блока 1 управления поступает сигнал, определи- щий положительный знак результата. С Выхода 22 блока 1 управления на информационный вход счетчика 46 посту- |пает сигнал. Под действием этого сиг- |нала происходит увеличение значения счетчика 46 на единицу, Таким образом, после выполнения 1-го цикла зна- чение счетчика 46 равно 1, где 1 - количество вычитаний из делимого делителя до получения первого отрицательного результата. Под действием управляющего сигнала, поступающего. из блока 1 управления по выходу 24, происходит занесение содержимого счетчика 46 в младших разряд регистра 5. Таким образом формируется цифра ре- syrtbfaTa .

В устройстве реализован алгоритм выполнения деления без восстановления остатка. Поэтому при выполнении операций окончания 1-го цикла собственно операции деления содержимое ре- гистра 7 переписывается в регистр 3. Полученное положительное число образует частичный остаток, используемый на следующем i+1-м цикле собственно операции деления.

После выполнения п+1 циклов результат собственно операции деления, представленный в позиционной г-ичной системе счисления, находится в регистре 5. Под действием управляющего импульса, приходящего с выхода 26 блока 1 управления, результат переписывается в регистр 3.

Результаты выполнения собственно всех операций умножения, деления, сложения и вычитания находятся в регистре 3. Под действием сигнала, приходящего на регистр 3 с выхода 12 блока 1 управления, код регистра 3 передается в блок 2 информационной разгрузки. Под действием управляющего .сигнала, приходящего с выхода 9, в блоке 2 информационной разгрузки происходит коррекция кода собственно выполнения всех операций.

В блоке 2 информационной разгрузки код результата собственно всех операций анализируется с целью установления соответствия формы представления результата и формы представления чисел с фиксированной запятой в позиционной избыточной (г,k)-системе счисления.

0

5

0

5

0

5

0

5

Если соответствие устанавливается, операция информационной разгрузки над результатом собственно операции не выполняется. Код результата, пред- ,ставленный в позиционной избыточной (г,k)-системе счисления, находится в регистре 3. Сигнал соответствия из блока,2 поступает на выход 45 и свидетельствует о завершении операций.

I

Если же соответствие не устанавливается, то в блоке 2 информационной разгрузки над результатом выполнения собственно операций осуществляется операция информационной разгрузки.до тех пор, пока результат не станет соответствовать форме представления чисел с фиксированной запятой. Скорректированный результат с блока 2 информационной разгрузки поступает в регистр 3. Одновременно с блока 2 сигнал окончания работы поступает на выход 45.

Преобразователь 6 кодов, осуществляющий преобразование кода из позиционной избыточной (г,Ю-системы счисления в позиционную r-ичную систему счисления, работает следующим образом.

.Под действием управляющего сигнала, приходящего с выхода 16 блока 1 управления, осуществляется прием кода из регистра 4 в регистр 49,

Значения разрядов с регистра 49 поступают на соответствующие узлы 51 деления на константу, с выхода которых значения частных и.остатков поступают на сумматор 52, где осуществляется суммирование остатков от деления с частными от деления, сдвинутыми на один разряд влево. Результат суммирования передается в регистр 50. Под действием управляющего импульса, поступающего с выхода 17 блока 1 управления, . осуществляется перепись кода из регистра 50 в регистр 4.

Блок 1 управления при выполнении операций работает следующим образом.

При сложении сигнал поступает на вход 33 блока 1 управления и с него на вход распределителя 56 импульсов, задающего необходимую тактовую последовательность . Далее сигнал с входа 33 устанавливает через элемент ИЛИ 89 в единицу триггер 76, кроме того, через элементы ИЛИ 82 и 86 формируются импульсы на выходах 13 и 20. Сигналы с первого и второго выходов распределителя 56 импульсов Лорнируют последовательно через элементы ИЛИ 80 и 81 импульсы на выходах 11 и 12, после чего выполняется процедура завершения работы, одинаковая для всех операций. Сигнал с выхода элемента ИЛИ 81 поступает на нулевые входы триггеров 76 и 77 и обнуляет их, через время задержки элемента 59 на выходе 9 появляет- J ся сигнал, запускающий блок 2 инфор-- мационной разгрузки.

При выполнении вычитания сигнал с входа 32 поступает на распределитель 55 импульсов, а также через элемент J ИЛИ 90 устанавливает в единичное состояние триггер 77. Кроме того, через элементы ИЛИ 83 и 86 Формируются сигналы на выходах 16 и 20. С первого, второго, третьего и четвертого вьгхо- 2 дов распределителя 55 импульсов формируются через элементы ИЛИ 84, 82 85, 80 и 81 , сигналы на выходах 17, 13, 19, 11 и 12, управляющие выполнением вычитания. Окончание операции 2 вычитания выполняется аналогично операции слежения.

При выполнении умножения сигнал с входа 31 поступает на элемент 58 задержки, а также устанавливает через 3 элемент ИЛИ 89 в единичное состояние триггер 76 и поступает через элемент |ИЛИ 79 на выход 21, устанавливает счетчик 78 в состояние п. Затем сигнал проходит через элемент ИЛИ 73 на выход 23. Если присутствует сигнал на входе 27, то с выхода элемента И 65 через элементы ИЛИ 82 и 86 формируются сигналы на выходах 13 и 20.

3

Далее сигнал проходит через распреде-40 хода сигнал на выходе 10. Кроме того,

литель 53 импульсов и с второго выхода через элементы ИЛИ 80 и 75 формирует сигналы на выходах 11 и 22. Затем-с первого выхода распределителя 53 импульсов сигнал поступает на эле- 45 мент ИЛИ 73 и вызывает формирование управляющей последовательности следую щего такта. Если приходит сигнал по входу 28, то с выхода элемента И 66 поступает сигнал через элементы ИЛИ jO 79 и 87 на выход 2J и на вход счетчика 78, уменьшая его содержание на единицу. Затем через элемент 62 зачерез элемент ИЛИ 87 происходит умень- шение на единицу значения счетчика 78.

Если значение счетчика не равно нулю, то сигнал проходит через элемент И 72 на вход элемента ИЛИ 88, вызывая формирование управляющей последовательности следующего цикла. При нулевом значении счетчика 78 сигнал проходит через элемент И 71 на выход 26 и далее через элемент 60 задержки на вход элемента ИЛИ 81 . Далее выполняется описанная выше процедура окончания операции.

Q

5 0 5

0

5

держки сигнал поступает на элемент И 67 и 68. Если счетчик 78 не в нулевом состоянии, то сигнал проходит через элемент И 68 и поступает на вход элемента И 78, вызывая Нормирование управляющей последовательности следующего цикла. При нулевом состоянии счетчика 78 сигнал через элемент И 67 поступает на вход элемента ИЛИ 81. Далее выполняется описанная выше процедура завершения операции.

При выполнении операции деления сигнал с входа 34 поступает на распределитель 57 импульсов, кроме того, через элемент ИЛИ 90 устанавливает триггер 77, устанавливает в состояние п+1 счетчик 78 и через элемент ИЛИ

79 проходит на выход 21 . С первого выхода распределителя 57 импульсов сигнал через элементы ИЛИ 86 и 83 формирует сигналы на выходах 20 и 16, а с второго и третьего выходов через элементы ИЛИ 84 и 88 - сигнал на выходе 17 и на выходах 13 и 19. Затем сигнал проходит через элемент 63 задержки и Аормирует через элемент ИЛИ

80сигнал на выходе 11. Если поступает сигнал по входу 29, то сигнал с выхода элемента И 70 проходит через элемент 64 задержки на вход элемента ИЛИ 88 и вызывает формирование управляющей последовательности следующего такта.

Если приходит сигнал по входу 30, то с выхода элемента И 69 поступает сигнал на выход 24. Далее сигнал поступает на вход распределителя 54 импульсов и формирует с его первого вычерез элемент ИЛИ 87 происходит умень- шение на единицу значения счетчика 78.

Если значение счетчика не равно нулю, то сигнал проходит через элемент И 72 на вход элемента ИЛИ 88, вызывая формирование управляющей последовательности следующего цикла. При нулевом значении счетчика 78 сигнал проходит через элемент И 71 на выход 26 и далее через элемент 60 задержки на вход элемента ИЛИ 81 . Далее выполняется описанная выше процедура окончания операции.

1

ч ai

| Устройство для деления | 1980 |

|

SU928344A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения в позиционной избыточной ( @ , @ )-системе счисления | 1982 |

|

SU1067498A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-03-15—Публикация

1985-01-14—Подача