Изобретение относится к радиотехнике и может быть использовано для демодуляции частотно-модулированных сигналов в телевизионных приемниках системы СЕ- КАМ.

Цель изобретения - повышение точности детектирования.

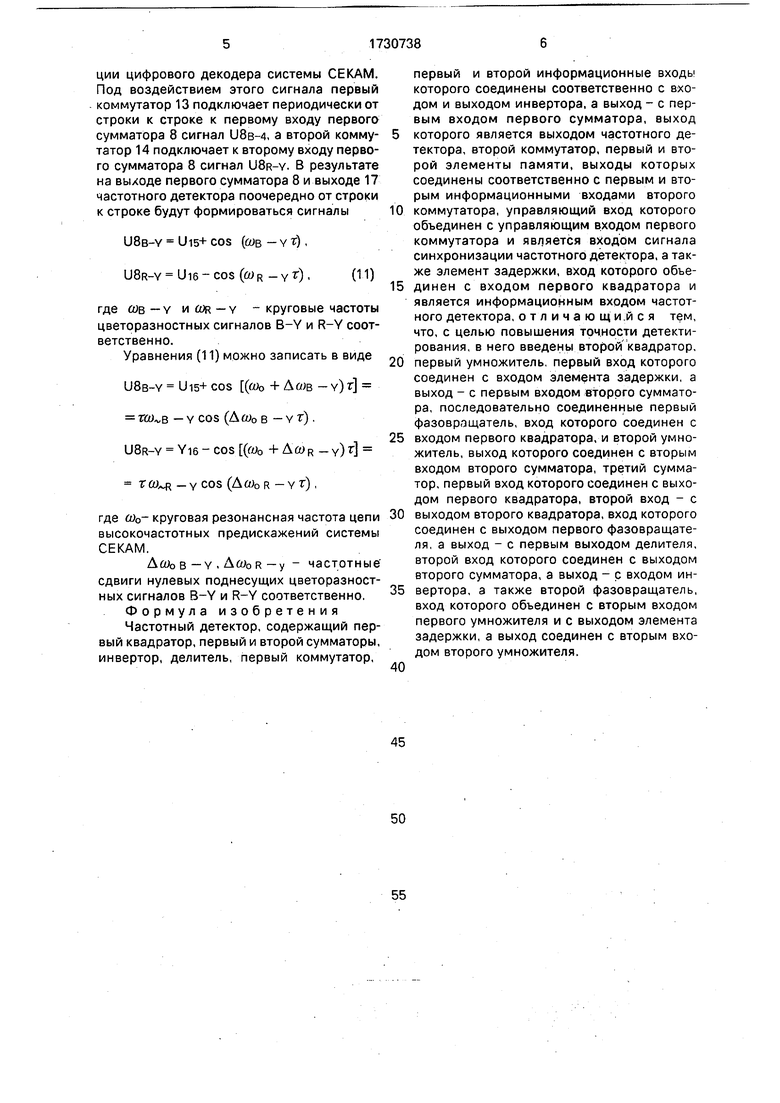

На чертеже представлена электрическая структурная схема частотного детектора.

Частотный детектор содержит информационный вход 1 и вход 2 сигнала синхронизации частотного детектора, первый 3 и второй 4 квадраторы, элемент задержки 5 третий сумматор 6, второй сумматор 7. первый сумматор 8. первый 9 и второй 10 умножители, делитель 11 инвертор 12, первый 13 и второй 14 коммутаторы первый 15 и второй 16 элементы памяти выход 17 частотного детектора, первый 18 и второй 19 фазовращатели.

Частотный детектор работает следующим образом,

Входной частотно-модулированный сигнал UBx(t) вида

UBx(t) R cos cot,

0)

где t -- текущее время;

R и (D - амплитуда и круговая частота входного сигнала,

через информационный вход частотного детектора поступает на входы фазовращателя 18, первого квадратора 3, элемента 5 задержки и первого умножителя 9.

Первый фазовращатель 18 осуществляет поворот фазы сигнала на л /2. На его выходе формируется сигнал Ui(t), который может быть записан в виде

Ui(t) R cos ( a) t+ л /2) - R sin ш t (2)

Этот сигнал с выхода первого фазовращателя 18 поступает на вход второго квадратора 4 и на второй вход второго умножителя 10

Элемент 5 задержки осуществляет задержку входного сигнала на период т тактовой частоты. На его выходе формируется сигнал Us(t) вида

сл

с

vj СО О VI CJ |00

U5(t) (t-T),(3)

который поступает на вход второго фазовращателя 19 и на вход первого умножителя 9.

Первый умножитель 9 осуществляет перемножение поступающих на его вход сигналов Uux(t) и U8(t) и на его выходе формируется сигнал Us(t), который может быть записан в виде

Ug(t) K9UBx(t)U5(t) Kg у cos 0) t+

+ cos(2 uJt-оиг)

(4)

где Kg - коэффициент передачи первого умножителя 9. Этот сигнал поступает на вход второго сумматора 7,

Второй фазовращатель 19 осуществляет поворот фазы сигнала Us(t) на л/2. На его выходе формируется сигнал (t), который может быть записан в виде

U2(t) (t-T)+ -Rsin w(t-r).

(5)

Этот сигнал с выхода второго фазовращателя 19 поступает на первый вход второго умножителя 10.

Второй умножитель 10 осуществляет перемножение поступивших на его входы сигналов Ui(t) и U2(t). На его выходе формируется сигнал lho(t), который может быть записан в виде

(

Uio(t) RioUi(t)U2(t) Кю -у

х COS Ш t - Ш Ш Т).

(6)

Этот сигнал поступает на вход второго сумматора 7.

Первый 3 и второй 4 квадраторы осуществляют возведение в квадрат поступающих на их входы сигналов и на их входах формируются сигналы соответственно UaW и U4(t), которые могут быть записаны в виде

Ua(t) K3lJBx2(t) KaR2 cos2 o t,

U4(t) K4Ui(t)

K4R2 sin2

wt,

где Кз и К4 коэффициенты передачи перво- го 3 и второго 4 квадраторов соответственно.

Сигналы Us(t)H U4(t) поступают на входы третьего сумматора 6. На его выходе формируется сигнал Ue(t), определяемый равенством

U6(t) U3(t) + U4(t) cos2 a) t+ + K4Sin2 (7)

При выборе коэффициентов Кз и К4 получим

U6(t) K3R2

(8)

Таким образом, на выходе третьего сумматора б формируется постоянный сигнал, уровень которого пропорционален квадрату амплитуды входного сигнала. Этот сигнал поступает на вход делителя 11.

На выходе второго сумматора 7 формируется сигнал U(t), равный сумме поступающих на его входы сигналов Ug(t) и Uio(t)

U7(t) Ug(t)+Uio(t)

При выборе коэффициентов получим

R2 U(t) Kg у cos on(9)

Этот сигнал поступает на вход делителя 11,

На его выходе формируется сигнал Un(t), пропорциональный отношению поступающих на его входы сигналов

Uii(t)Kn MQ J№cosun. (Ю)

где Кп - коэффициент передачи делителя. Выбирая коэффициенты Кз, Kg и Кп из

KnKg 0

условия --- 2, получим Кз

Un(t).cos

Сигнал Un(t) поступает на информационный вход первого коммутатора 13 и на вход инвертора 12. На выходе инвертора 12 формируется инверсный сигнал

U 12(t) -U1 l(t) -COS Ш Г ,

который поступает на другой информационный вход первого коммутатора 13.

На первый и второй информационные входы второго коммутатора 14 поступают сигналы Uis и Die.

Первый 13 и второй 14 коммутаторы управляются сигналом цветовой синхронизации полустрочной частоты, поступающим на их управляющие входы с входа 2 частотного детектора, на который он в свою очередь поступает со схемы цветовой синхронизации цифрового декодера системы СЕКАМ. Под воздействием этого сигнала первый коммутатор 13 подключает периодически от строки к строке к первому входу первого сумматора 8 сигнал 1)8в-4, а второй коммутатор 14 подключает к второму входу первого сумматора 8 сигнал U8R-Y. В результате на выходе первого сумматора 8 и выходе 17 частотного детектора поочередно от строки к строке будут формироваться сигналы

U8B-Y U15+ COS (toB - Y Т) , U8R-Y U16 - COS (to R - Y Т) ,

где сов - У и UR - Y - круговые частоты цветоразностных сигналов B-Y и R-Y соответственно.

Уравнения (11) можно записать в виде

U8B-Y U15+ COS (too + A MB - Y) T - Y COS ( В - Y T) .

U8R-Y Yie - cos (too + A to R - Y)

Г Y COS (Д too R - Y T) ,

где to0- круговая резонансная частота цепи высокочастотных предискажений системы СЕКАМ.

Atoo в - Y . Л&Ъ R - у - частотные сдвиги нулевых поднесущих цветоразностных сигналов B-Y и R-Y соответственно. Формула изобретения Частотный детектор, содержащий первый квадратор, первый и второй сумматоры, инвертор, делитель, первый коммутатор,

первый и второй информационные входы которого соединены соответственно с входом и выходом инвертора, а выход - с первым входом первого сумматора, выход

5 которого является выходом частотного детектора, второй коммутатор, первый и второй элементы памяти, выходы которых соединены соответственно с первым и вторым информационными входами второго

10 коммутатора, управляющий вход которого объединен с управляющим входом первого коммутатора и является входом сигнала синхронизации частотного детектора, а также элемент задержки, вход которого объе15 динен с входом первого квадратора и является информационным входом частотного детектора, отличающийся тем, что, с целью повышения точности детектирования, в него введены второй квадратор,

20 первый умножитель, первый вход которого соединен с входом элемента задержки, а выход - с первым входом второго сумматора, последовательно соединенные первый фазовращатель, вход которого соединен с

25 входом первого квадратора, и второй умножитель, выход которого соединен с вторым входом второго сумматора, третий сумматор, первый вход которого соединен с выходом первого квадратора, второй вход - с

30 выходом второго квадратора, вход которого соединен с выходом первого фазовращателя, а выход - с первым выходом делителя, второй вход которого соединен с выходом второго сумматора, а выход - с входом ин35 вертора, а также второй фазовращатель, вход которого объединен с вторым входом первого умножителя и с выходом элемента задержки, а выход соединен с вторым входом второго умножителя.

40

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕТЕКТОР | 2008 |

|

RU2345476C1 |

| Управляемый фазовращатель | 1990 |

|

SU1721536A1 |

| Преобразователь угла поворота вала в код | 1989 |

|

SU1649665A1 |

| ИНДИКАТОРНОЕ УСТРОЙСТВО | 1991 |

|

RU2005994C1 |

| Система передачи и приема информации с многоосновным кодированием | 1989 |

|

SU1642590A1 |

| ФАЗОВЫЙ СПОСОБ ПЕЛЕНГАЦИИ И ФАЗОВЫЙ ПЕЛЕНГАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2012 |

|

RU2518428C2 |

| АКУСТИЧЕСКИЙ ЭХОЛОКАТОР | 2002 |

|

RU2205421C1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ФАЗОВЫХ ФЛЮКТУАЦИЙ | 1991 |

|

RU2023272C1 |

| ИНДИКАТОРНОЕ УСТРОЙСТВО | 1991 |

|

RU2005993C1 |

| Адаптивная оптическая система с многоканальной фазовой модуляцией | 1988 |

|

SU1569785A1 |

Изобретение относится к радиотехнике и может быть использовано для демодуляции, частотно-модулированных сигналов в телевизионных приемниках системы СЕ- КАМ Цель изобретения - повышение точности детектирования. Частотный детектор содержит информационный вход и вход сигнала синхронизации, квадраторы, элемент задержки сумматоры, умножители, делитель, инвертор, коммутаторы, элементы памяти, выход, фазовращатели. 1 ил.

| Цифровой частотный детектор | 1987 |

|

SU1483591A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-30—Публикация

1990-05-03—Подача