мирователи 11 и 12, вход 13 устройст-20 состоит из нескольких посылок после

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1987 |

|

SU1442996A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

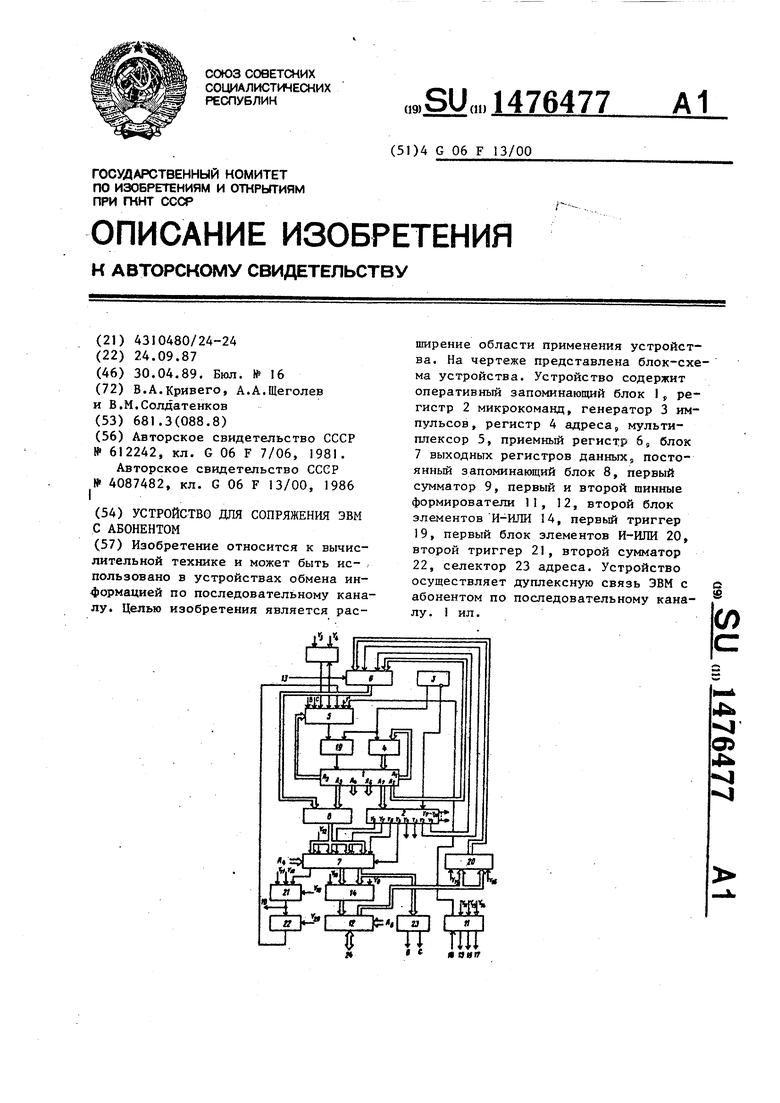

Изобретение относится к вычислительной технике и может быть использовано в устройствах обмена информацией по последовательному каналу. Целью изобретения является расширение области применения устройства. На чертеже представлена блок-схема устройства. Устройство содержит оперативный запоминающий блок 1, регистр 2 микрокоманд, генератор 3 импульсов, регистр 4 адреса, мультиплексор 5, приемный регистр 6, блок 7 выходных регистров данных, постоянный запоминающий блок 8, первый сумматор 9, первый и второй шинные формирователи 11, 12, второй блок элементов И-ИЛИ 14, первый триггер 19, первый блок элементов И-ИЛИ 20, второй триггер 21, второй сумматор 22, селектор 23 адреса. Устройство осуществляет дуплексную связь ЭВМ с абонентом по последовательному каналу. 1 ил.

ва для подключения к последовательному информационному выходу абонента, второй блок элементов И-ИЛИ 14, выходы 15-17 устройства для подключения соответственно к входам прерывания, чтения и записи данных ЭВМ, вход 18 устройства для подключения выхода ответа ЭВМ, первый триггер 19, первый блок элементов И-ИЛИ 20, второй триггер 21, второй сумматор 22, селектор 23 адреса, вход-выход 24 устройства для подключения к входу-выходу данных ЭВМ.

Устройство работает следующим образом.

В режиме последовательного асинхронного приема данных от абонента, передаваемые по последовательному каналу, поступают на вход 13 устройства на приемный регистр 6, на вход мультиплексора 5 и сумматора 9.

Управление функционированием уст- ройства в этом решении осуществляется последовательностью микрокоманд.

Исходя из структуры последователь- . единичном состоянии. Анализ этого

50

ной информационной посылки (согласно, например, интерфейсу НМ МПК по ВТ- 10-78) прием последней начинается со стартового бита, который всегда подается в линию связи нулевым потенциалом. В конце каждой посылки высоким потенциалом в линии передается два бита сигнала . При этом каждый бит в линию связи передается сигналом строго определенной длительности, чем обеспечивается синхронизация приема информационной посылки.

При поступлении стартового бита на вход 13 устройства производится

триггера через мультиплексор 5 под тверждает правильность приема. Нас ройка на контроль по четности или нечетности производится микропрогр мным путем.

В случае правильного приема информационная посылка поступает на ресный вход блока 8, где декодируе ся табличным способом и поступает новременно на информационные входы п секции блока 7 выходных регистро данных, а с регистра 2 микрокоманд поступает один из разрядов микроко манды, фиксирующий преобразованную

5 0

Q

5

довательного кода, то их размещение в блоке 7 выходных регистров данных производится в зависимости от позиции принятой посылки и реализуется различными программами, зафиксированными в оперативном запоминающем блоке 1 .

После формирования полного формата выходного сообщения устройство настраивается на режим передачи этого сообщения на магистраль межмодульного параллельного интерфейса (МПИ). Для этого управление передается следующей подпрограмме, которая также отрабатывается микрокомандным путем.

В процессе приема информационной посылки ведется контроль приема, для чего служит последовательный сумматор 9. В простейшем варианте это счетный триггер, установленный в нулевое состояние. При поступлении на его вход четного количества положительных фронтов, он остается в нулевом состоянии, а нечетного - он остается J3

0

триггера через мультиплексор 5 подтверждает правильность приема. Настройка на контроль по четности или нечетности производится микропрограммным путем.

В случае правильного приема информационная посылка поступает на адресный вход блока 8, где декодируется табличным способом и поступает одновременно на информационные входы п секции блока 7 выходных регистров данных, а с регистра 2 микрокоманд поступает один из разрядов микрокоманды, фиксирующий преобразованную

посылку на соответствующей секции блока 7.

После подготовки информации в блоке 7 выходных регистров данных управление передается подпрограмме выдачи данных на шину МПИ.

Для вывода информации на шину МПИ шинный формирователь 12 настраивается на выдачу информации, блок элемен-JQ нает его. Затем шинный формирователь

15

20

тов И-ИЛИ 14 настраивается на выдачу адресного кода, который через шинный формирователь 12 поступает на вход- выход 24 данных устройства.

Одновременно (с разницей в один шаг микропрограммы) формируется микрокоманда обмена. В этом состоянии магистраль и шины удерживаются на несколько тактов. Количество тактов обусловлено быстродействием устрой- ,ства, задействованного на шину МПИ.

После выполнения таким образом адресной части сообщения формируется микрокоманда, отпирающая блок элементов И-ИЛИ 14, коммутирующий данные с 25 блока 7 выходных регистров данных на вход шинного формирователя 12. Шинный формирователь 12 коммутирует данные на вход-выход 24 данных через шинный формирователь 11 формируется сигнал записи данных ДЗП. Длительность этого сигнала зависит от за- j держки сигнала ответа, который через шинный формирователь 11 подается на соответствующий вход мультиплексора 5 и после фиксации его в триггере 19 снимаются данные с входа-выхода 24 МПИ и сигнал записи данных ДЗП. Сигнал ответа Отв снимается ЭВМ по заднему фронту сигнала ДЗП. Обмен по шине МПИ завершается сбросом сигнала обмена Обм по заднему фронту сигнала ответа Отв, после чего устрой12 настраивается на передачу информации с входа-выхода 24 МПИ на блок элементов И-ИЛИ 20. Следующая микрокоманда формирует сигнал, переводящий сигнал 17 чтения данных ДЧТ через шинный формирователь 11 сигналов управления в активный уровень. По фронту сигнала чтения данных ДЧТ ЭВМ формирует на входе-выходе 24 МПИ данные, о чем сообщает активным уровнем сигнала 18 ответа Отв. Далее анализируется уровень этого сигнала прохождения его через мультиплексор 5 на триггер 19.

Блок элементов И-ИЛИ 20 настраивается на пропуск младшего байта информации, который фиксируется в приемном регистре 6. С выхода регистра 6 младший байт информации поступает на блок Зо 8, выполняющий функцию перекодировщика в код КОИ-7. Перекодированный байт информации фиксируется в младших 8 разрядах блока 7 выходных регистров данных.

Аналогично обрабатывается старший байт данных, пропускаемый на приемный регистр 6 блоком элементов И-ИЛИ 20. Перекодированный старший байт информации фиксируется в старших 8 разрядах блока 7 выходных регистров данных.

По завершению обработки данных снимается сигнал чтения данных ДЧТ, по его спаду ЭВМ снимает сигнал от35

40

По завершению обработки данных снимается сигнал чтения данных ДЧТ, по его спаду ЭВМ снимает сигнал отство переходит на начало программы.

Параллельный ввод информации опи- дг вета Отв и данные с входа-выхода сан для случая выбора ведущим устрой- 24 МПИ. Далее анализируется состоя- ства ввода-вывода и ведомым - внешние сигнала ответа Отв и после его снятия заканчивает процесс обмена, переводя сигнал 15 обмена Обм в неактивное состояние.

него устройства по отношению к магистрали межмодульного параллельного интерфейса (МПИ).

Для реализации алгоритма устройство переходит на соответствующую подпрограмму, расположенную в адресном пространстве оперативного запоминающего блока I. Процесс чтения с шины МПИ начинается записью адреса устройства, к которому будет происходить обращение, в блок 7 выходных регистров.

После этого блок элементов И-ИЛИ 14 настраивается на пропуск записанного адреса через шинный формирователь 12 на вход-выход 24 МПИ. Затем через шинный формирователь 11 формирует активный уровень сигнала 15 обмена Обм. По фронту этого сигнала ЭВМ считывает с шины адрес и запомиQ нает его. Затем шинный формирователь

5

0

5

12 настраивается на передачу информации с входа-выхода 24 МПИ на блок элементов И-ИЛИ 20. Следующая микрокоманда формирует сигнал, переводящий сигнал 17 чтения данных ДЧТ через шинный формирователь 11 сигналов управления в активный уровень. По фронту сигнала чтения данных ДЧТ ЭВМ формирует на входе-выходе 24 МПИ данные, о чем сообщает активным уровнем сигнала 18 ответа Отв. Далее анализируется уровень этого сигнала прохождения его через мультиплексор 5 на триггер 19.

Блок элементов И-ИЛИ 20 настраивается на пропуск младшего байта информации, который фиксируется в приемном регистре 6. С выхода регистра 6 младший байт информации поступает на блок о 8, выполняющий функцию перекодировщика в код КОИ-7. Перекодированный байт информации фиксируется в младших 8 разрядах блока 7 выходных регистров данных.

Аналогично обрабатывается старший байт данных, пропускаемый на приемный регистр 6 блоком элементов И-ИЛИ 20. Перекодированный старший байт информации фиксируется в старших 8 разрядах блока 7 выходных регистров данных.

По завершению обработки данных снимается сигнал чтения данных ДЧТ, по его спаду ЭВМ снимает сигнал от5

0

вета Отв и данные с входа-выхода 24 МПИ. Далее анализируется состоя-

ние сигнала ответа Отв и после его снятия заканчивает процесс обмена, переводя сигнал 15 обмена Обм в неактивное состояние.

Организация последовательного вывода осуществляется переходом на со- соответствующую программу в блоке I. Согласно интерфейсу НМ МПИ по ВТ 10-78 состоянию активного ожидания соответствует единица в последовательном канале связи на входе 13. Началу информационной посылки предшествует старт бит нулевого уровня,

а после окончания информационной, по сылки - два стоп-бита высокого уровня . Для обеспечения выдачи в линию уровня активного ожидания и формирования старт- и стоп-бита информации используется D-триггер 21 с входами установки и сброса.

При отсутствии передаваемой информации D-триггер 21 установлен в единичное состояние. Программа последовательного вывода информации начинается сбросом D-триггера 21, что соответствует выдаче в линию старт-бита. Как было указано выше, длительность сигнала Т в последовательном канале соответствует 16 шагам программы

Т - 16t

ОГТ

Следовательно, по истечении 16 шагов программы начинается выборка информации из блока 7 выходных регистров данных для передачи. При этом подразумевается, что блок 7 уже загружен данными для передачи. Для последовательной выдачи информации блок 7 настраивается на выполнение операции сдвига вправо. Младший разряд блока 7 соединен с D-входом D-триггера 21. Во время передачи происходит загрузка D-триггера 21 битом информации, сдвиг информации в выходном регистре 7 - воздействием на тактирующие входы выходного регистра, формирование вре- 1менного интервала Т. Выдав байт ин- формации, устройство формирует в линии бит контроля по четности, формируемый сумматором 22 и заводимый на мультиплексор 5. Состояние сумматора 22 анализируется и производится либо сброс, либо установка в единицу D- триггера 21, в последовательном канале формируется при этом девятый информационный быт - бит контроля четности. Передача информации заканчивается формированием двух стоп-битов установкой D-триггера 21 на время 2Т. После чего в линии устанавливается режим активного ожидания, соответствующий единице на выходе D-триггера 21.

Старший байт данных из блока 7 выводится аналогично описанному. После выдачи принятой информации устройство переходит в начало программы, ожидая дальнейших запросов на ввод-вывод.

После включения питания устройство переходит в режим ввода последова

5

5

0

5

0

5

0

5

тельной информации: четыре байта информации загружаются в блок 7. После этого происходит анализ разрядов В и С селектора адреса 23. В зависимости от их состояния выбирается один из режимов работы: повтор последовательного ввода; вывод в шину МПИ; ввод из шины МПИ; последовательный вывод.

После отработки каждой программы управление передается на программу ввода последовательной информации.

Формула изобретения

Устройство для сопряжения ЭВМ с абонентом, содержащее мультиплексор, оперативный запоминающий блок, ре- ч регистр адреса, первый триггер, регистр микрокоманд и генератор импульсов, причем выход мультиплексора соединен с информационным входом первого триггера, вход синхронизации которого и вход синхронизации регистра адреса соединены с первым выходом генератора импульсов, выход регистра адреса соединен с входом младших разрядов оперативного запоминающего блока, вход старшего разряда адреса которого соединен с выходом первого триггера, с первого по третий выходы оперативного запоминающего блока соединены соответственно с информационным входом регистра адреса, с управляющим входом мультиплексора и .а информационным входом регистра микрокоманд, вход синхронизации которого соединен с вторым выходом генератора импульсов, отличающееся тем, что, с целью расширения области применения устройства, в него введены приемный регистр, блок выходных регистров данных, постоянный запоминающий блок, селектор адреса, первый, второй блоки элементов И-ИЛИ, первый второй шинные формирователи, первый, второй сумматоры и второй триггер, причем вход устройства для подключения последовательного информационного выхода абонента соединен с первыми информационными входами мультиплексора, первого сумматора и приемного регистра, второй, третий информационные входы, вход синхронизации и сброса приемного регистра соединены соответственно с третьим выходом оперативного запоминающего блока, с выходом первого блока элементов

И-ИЛИ и с первым, вторым выходами регистра микрокоманд, третий, четвертый выходы которого соединены с входами сброса и синхронизации первого сумматора, выход которого соединен с вторым информационным входом мультиплексора, третий, четвертый, пятый и шестой информационные входы которого соединены соответственно с первым, вторым выходами селектора адреса, с первым выходом первого шинного формирователя и с выходом второго сумматора, выход приемного регистра соединен с первым адресным входом пос- тоянного запоминающего блока, второй адресный вход и выход которого соединены соответственно с пятым выходом оперативного запоминающего блока и с первым информационным входом бло- ка выходных регистров данных, вход синхронизации которого соединен с пятым выходом регистра микрокоманд, шестой, седьмой выходы оперативного запоминающего блока соединены соот- ветственно с вторым информационным входом блока выходных регистров данных и с первым информационным входом второго шинного формирователя, второй информационный вход которого сое- динен с выходом второго блока элемен- тов И-ИЛИ, первый вход которого соединен с входом селектора адреса и с первым выходом блока выходных регистров данных, второй, третий выходы которого соединены соответственно с вторым входом второго блока элементо И-ИЛИ и с информационным входом второго триггера, единичный, нулевой входы и вход синхронизации которого соединены с выходами с шестого по восьмой регистров микрокоманд, выход второго триггеров соединен с информационным входом второго сумматора и с выходом устройства для подключения к последовательному информационному входу абонента, с девятого по шестнадцатый выходы регистра микрокоманд соединены соответственно с третьим, четвертым входами второго блока элементов И-ИЛИ, с первым, вторым, тоеть им информационными входами первого шинного формирователя, с синхровходом второго сумматора, с первым, вторым входами первого блока элементов И-ИЛИ, третий вход которого соединен с выходом второго шинного формирователя, вход-выход данных которого соединен с входом-выходом устройства для подключения к информационному входу-выходу ЭВМ, второй, третий, четвертый выходы первого шинного формирователя соединены с выходами устройства для подключения соотетствен- но к входам прерывания чтения и записи данных ЭВМ, четвертый информационный вход первого шинного формирователя соединен с входом устройства для подключения выхода ответа ЭВМ.

| Устройство для поиска информации на перфоленте | 1976 |

|

SU612242A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 4087482, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-30—Публикация

1987-09-24—Подача