Изобретение относится к электро технике и может быть использовано в качестве источников электропитания электротехнической и радиоэлек ронной аппаратуры. Известен многофазный импульсный стабилизатор напряжения, содержащий силовую цепь, выполненную в виде М параллельно включенных силовых преобразовательных ячеек, каждая из которых может быть выполнена по любой из известных схем импульсного преобразования электри ,ческой энергии,и блок управления, состоящий из генератора синхроимпульсов, формирователя импульсов синхронизации широтно-импульсного модулятора, М-разрядного регистра сдвига, источника опорного напряжения, аналоговой схемы сравнения Гц . Недостатком данного стабилизато ра является низкая надежность и ма лые удельно-массовые показатели вследствие того, что равномерность распределения тока Нагрузки между параллельно работающими силовыми преобразовательными ячейками при увеличении числа М параллельно включенных силовых ячеек. Кроме того, блок управления обеспечивает лишь управление фиксированным количеством преобразовательных ячеек Это исключает использование одного и того же блока управления при изменении количества преобразователь ных ячеек и требует разработки нового блока управления. Наиболее близким к предлагаемом по технической сущности является многофазный импульсный стабилизатор напряжения, содержащий силовую цепь, выполненную в виде М паралле но включенных силовых преобразовательных ячеек, каждая из которых соединена с входными и выходными выводами питания, и блок управления, состоящий из генератора синхр импульсов, формирователя импульсов синхрони-зации широтно-импульсного модулятора М-ра-зрядного регистра сдвига, универсального регистра сдвига, М триггеров управления, М логических элементов И-НЕ, двух фо ,мирователей тактовых импульсов, дв формирователей строб-импульсов, источника опорного напряжения, ана логового узла сравнения, причем узел сравнения одним из входов под ключен к источнику опорного напряжения, другим - к выходным выводам стабилизатора, а выходом - к од- , ному из входов широтно-импуль.сного модулятора, другой выход которого подключен к формирователю импульсов синхронизации широтно-импульсного модулятора, выход широтно-импульсного модулятора подключен к информационному входу М-разрядного регистра сдвига и через второй формирователь строб-импульсов к входам универсального М разрядного регистра и к входу установки в второго формирователя тактовых импульсов, выход формирователя импульсов синхронизации широтно-импульсного модулятора подключен к входу синхронизации режима последовательного приема информации универсального М-разрядного регистра, а вход к генератору импульсов и входу первого формирователя тактовых импульсов , выход которого подключен к входу синхронизации М-разрядного регист1 а сдвига и через первый формирователь строб-импульсов к входам М логических элементов И-НЕ, каждый выход универсального М-разрядного регистра подключен к входу синхронизации соответствующего триггера управления, к выходам которых подключены управляющие входы силовых преобразовательных ячеек С2, Недостатком известного стабилизатора является ограничение функциональных возможностей и низкая экономичность вследствие того, что не обеспечивается работоспособность стабилизатора при изменении числа преобразовательных ячеек без дополнительных затрат на разработку и изготовление вновь спроектированного многофазного устройства. Цель изобретения - расширение функциональных возможностей. Поставленная цель достигается тем, что в МНОГОФАЗНЫЙ импульсный стабилизатор напряжения/ содержащий силовую цепь, выполненную в виде М параллельно включенных силовых преобразовательных ячеек, каж-, дая из которых соединена с входными и выходными выводами питания, и блок управления, сострящий из генератора синхроимпульсов, формирователя импульсов синхронизации широтно-импульсного модулятора, М-разрядного регистра сдвига, универсального регистра сдвига, М триггеров управления, М логических элементов И-НЕ, двух формирователей тактовых импульсов, двухформирователей строб-импульсов, источника опорного напряжения, аналогового узла сравнения, причем узел сравнения одним из входов подключен к источнику опорного напряжения, другим - к выходным выводам стабилизатора, а выходом - к одному из входов широтно-импульсного модулятора, другой вход которого подключен к выходу формирователя импульсов синхронизации широтно-импульсного модулятора, выход широтно-импульсного модулятора подключен к информационному входу М-разрядного регистра сдвига и через второй формирователь строб-импульсов - к входам универсального М-разрядного регистра и к входу установки в О второго формирователя тактовых импульсов, выход которого подключен к входу синхронизации режима последовательного приема информации универсального М-разрядного регистра, а вход - к генератору синхроимпульсов и : входу первого формирователя тактовых импульсов, вход формирователя импульсов синхронизации широтно-импульсного модулятора подключен к входу Синхронизации М-разрядного регистра сдвига и через первый формирователь строб-импульсов - к входам М логических элементов И-НЕ, каждый выход универсального М-разрядного регистра подключе к входу синхронизации соответствующего триггера управления, к выходам которых подключены управляющие входы силовых преобразовательных ячеек, введены К-разрядный двоичный счетчик, К-разрядный цифровой узел сравнения и кодирующий блок, причем вход К-разрядного счетчика подключен к выходу первого формирователя тактовых импульсов, каждый из К выходов - к соответствующим информационным входам цифрового узла сравнения, кодирующие входы которого подключены к соответствующим выходам кодирующего блока, а выход к входу установки в О К-разрядного двоичного счетчика и входу формирователя импульсов синхронизации широтно-импульсного модулятора.

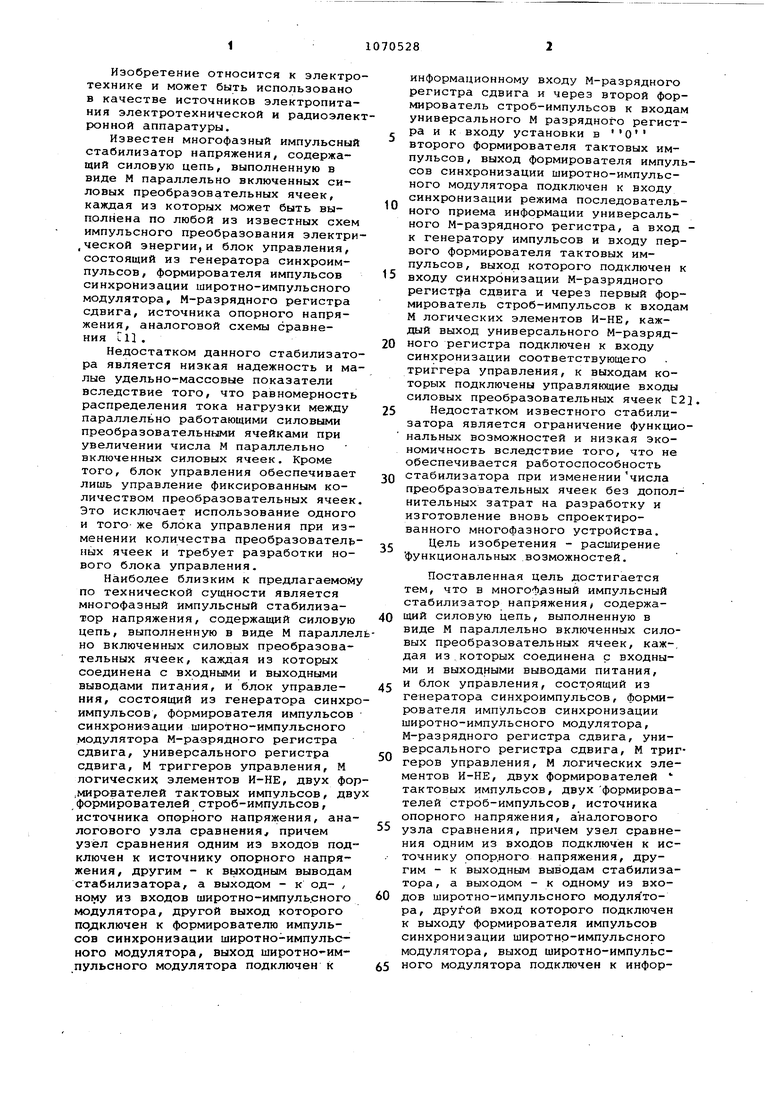

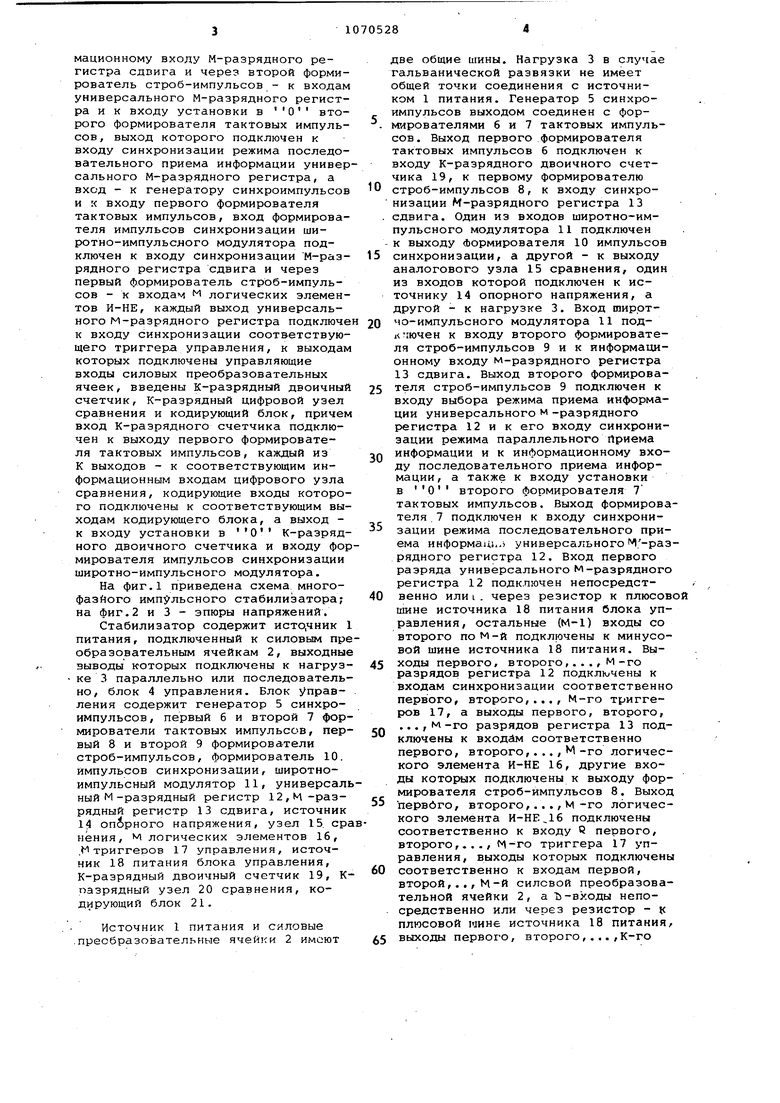

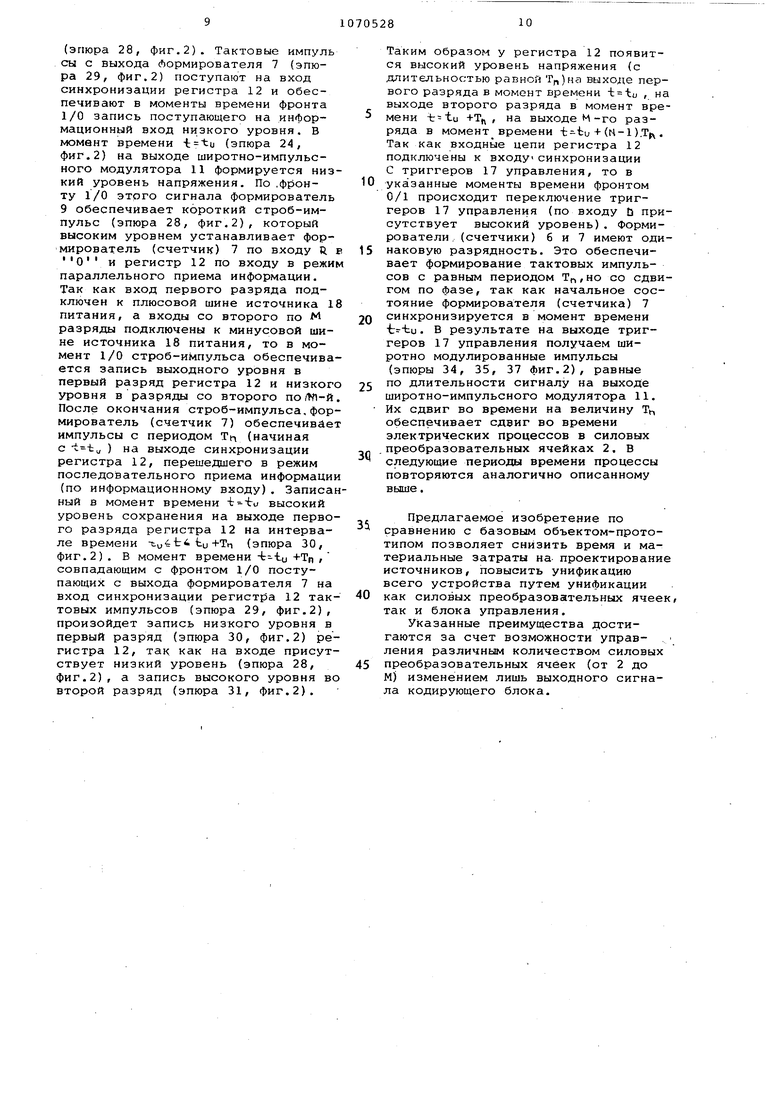

На фиг.1 приведена схема многофазйого имп /льсного стабилизатора; на фиг.2 и 3 - эпюры напряжений.

Стабилизатор содержит источник 1 питания, подключенный к силовым преобразовательным ячейкам 2, выходные выводы которых подключены к нагрузке 3 параллельно или последовательно, блок 4 управления. Блок Управления содержит генератор 5 синхроимпульсов, первый б и второй 7 формирователи тактовых импульсов, первый 8 и второй 9 формирователи строб-импульсов, формирователь 10. Импульсов синхронизации, широтноимпульсный модулятор 11, универсальный М -разрядный регистр 12,И -разрядный регистр 13 сдвига, источник 1;3 опорного напряжения, узел 15 сранения, и логических элементов 16, .И триггеров 17 управления, источник 18 питания блока управления, К-разрядный двоичный счетчик 19, Кпазрядный узел 20 сравнения, кодирующий блок 21.

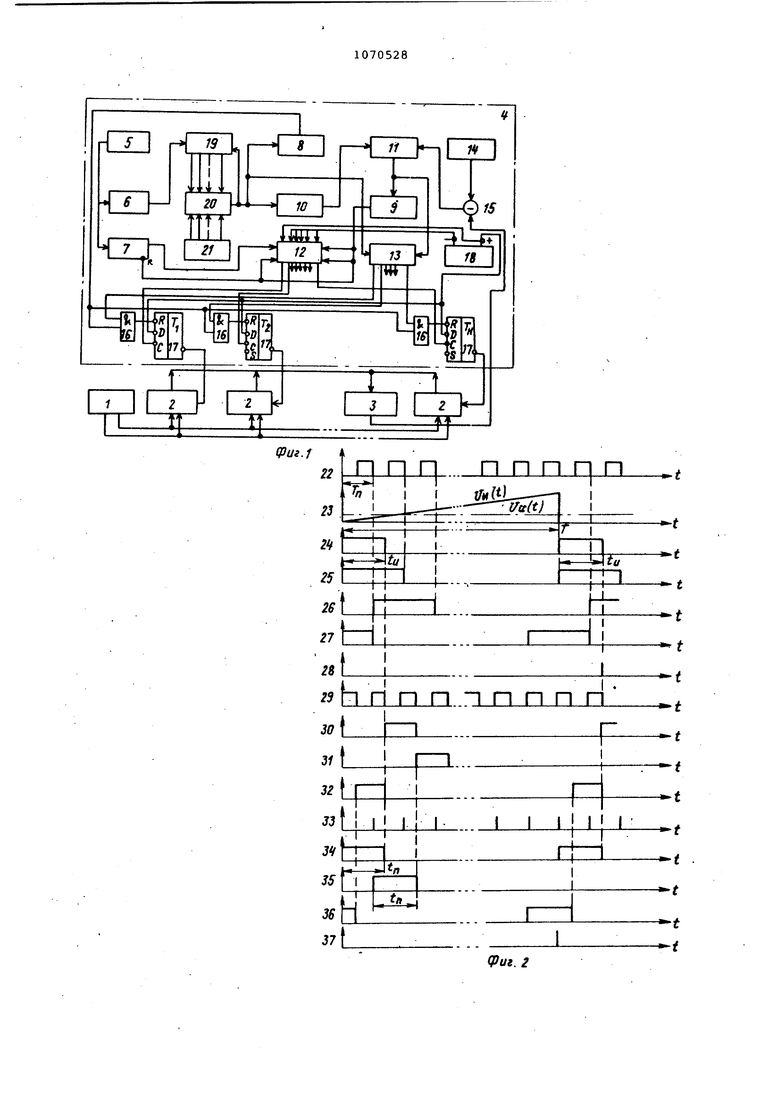

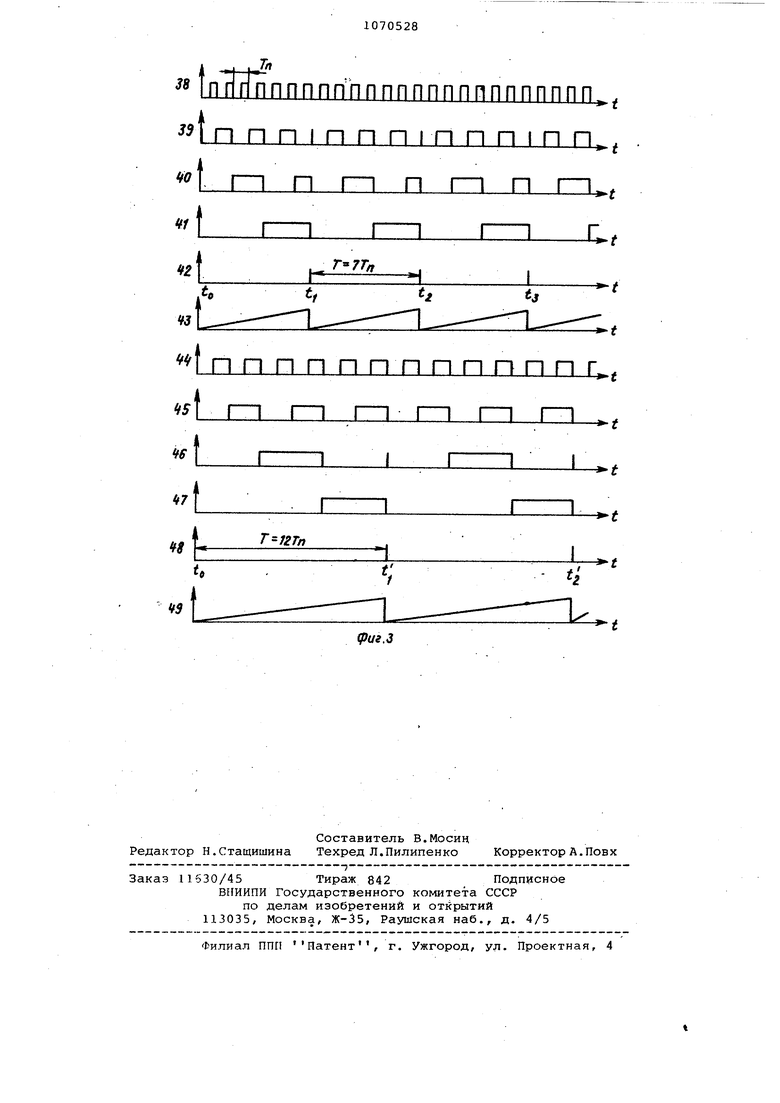

Источник 1 питания и силовые .преобразовательные ячейки 2 имеют

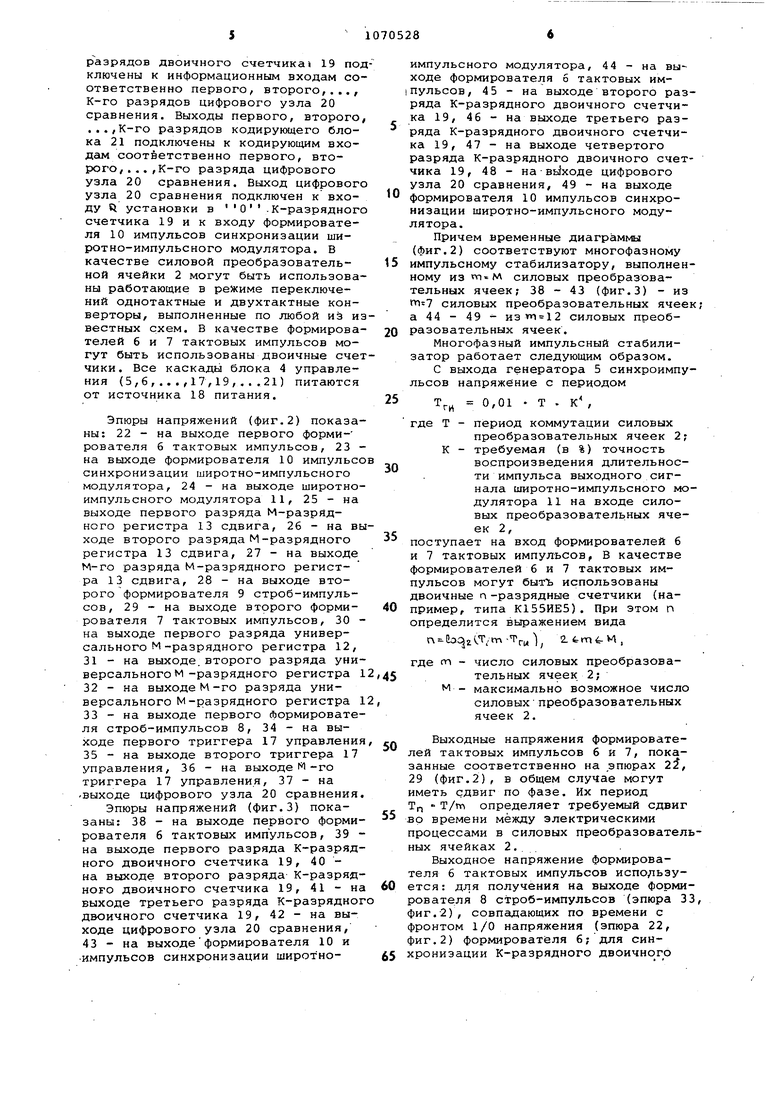

две общие шины. Нагрузка 3 в случае гальванической развязки не имеет общей точки соединения с источником 1 питания. Генератор 5 синхроимпульсов выходом соединен с формирователями б и 7 тактовых импульсов. Выход первого формирователя тактовых импульсов б подключен к входу К-разрядного двоичного счетчика 19, к первому формирователю строб-импульсов 8, к входу синхронизации М-разрядного регистра 13 сдвига. Один из входов широтно-импульсного модулятора 11 подключен к выходу Формирователя 10 импульсов синхронизации, а другой - к выходу аналогового узла 15 сравнения, один из входов которой подключен к источнику 14 опорного напряжения, а другой - к нагрузке 3. Вход ширртчо-импульсного модулятора 11 подключен к входу второго формирователя строб-импульсов 9 и к информационному входу М-разрядного регистра 13 сдвига. Выход второго формирователя строб-импульсов 9 подключен к входу выбора режима приема информации универсального м-разрядного регистра 12 и к его входу синхронизации режима параллельного Приема информации и к информационному входу последовательного приема информации, а также к входу установки в О второго формирователя 7 тактовых импульсов. Выход формирователя .7 подключен к входу синхронизации режима последовательного приема информац,) универсального .-разрядного регистра 12. Вход первого разряда универсального М-разрядного регистра 12 подключен непосредственно или I . через резистор к плюсов шине источника 18 питания блока управления, остальные (М-1) входы со второго поМ-й подключены к минусовой шине источника liB питания. Выходы первого, второго,...,М-го разрядов регистра 12 подключены к входам синхронизации соответственно первого, второго,..., М-го триггеров 17, а выходы первого, второго, ...,М-го разрядов регистра 13 подключены к входам соответственно первого, второго,...,М-го логического элемента И-НЕ 16, другие входы которялх подключены к выходу формирователя строб-импульсов 8, Выход первбго, второго,...,М -го логического элемента И-НЕ .,16 подключены соответственно к входу С первого, второго,..., триггера 17 управления, выходы которых подключены соответственно к входам первой, второй,..,М-и силовой преобразовательной ячейки 2, а Ь-в ходы непосредственно или через резистор - jf. плюсовой мине источника 18 питания выходы первого, второго,...,К-го разрядов двоичного счетчика 19 по ключены к информационным входам со ответственно первого, второго,..,, К-го разрядов цифрового узла 20 сравнения. Выходы первого, второго ...,К-го разрядов кодирующего блока 21 подключены к кодирующим входам соответственно первого, второго, ... ,К-го разряда цифрового узла 20 сравнения. Выход цифровог узла 20 сравнения подключен к вхоДУ Q установки в О-К-разрядног счетчика 19 и к входу формирователя 10 импульсов синхронизации широтно-импульсного модулятора. В качестве силовой преобразовательной ячейки 2 могут быть использова ны работающие в режиме переключений однотактные и двухтактные конверторы, выполненные по любой из и вестных схем. В качестве формирова талей 6 и 7 тактовых импульсов могут быть использованы двоичные сче чики. Все каскады блока 4 управления {5,6,...,17,19,...21) питаются от источника 18 питания. Эпюры напряжений (фиг.2) показаны: 22 - на выходе первого формирователя б тактовых импульсов, 23 на выходе формирователя 10 импульсо синхронизации широтно-импульсного модулятора, 24 - на выходе широтноимпульсного модулятора 11, 25 - на выходе первого разряда М-разрйдного регистра 13 сдвига, 26 - на вы ходе второго разряда М-разрядного регистра 13 сдвига, 27 - на выходе М-го разряда М-разрядного регистра 1 3 сдвига, 28 - на выходе второго формирователя 9 строб-импульсов, 29 - на выходе второго формирователя 7 тактовых импульсов, 30 на выходе первого разряда универсального М -разрядного регистра 12, 31- на выходе.второго разряда универсального М -разрядного регистра 32- на выходе М-го разряда универсального М-разрядного регистра 33- на выходе первого формирователя строб-импульсов 8, 34 - на выходе первого триггера 17 управления 35 - на выходе второго триггера 17 управления, 36 - на выходе триггера 17 управления, 37 - на выходе цифрового узла 20 сравнения Эпюры напряжений (фиг.З) показаны: 38 - на выходе первого форми рователя 6 тактовых импульсов, 39 на выходе первого разряда К-разрядного двоичного счетчика 19, 40 на выходе второго разряда К-разрядного двоичного счетчика 19, 41 - на выходе третьего разряда К-разрядног двоичного счетчика 19, 42 - на выходе цифрового узла 20 сравнения, 43 - на выходеформирователя 10 и импульсов синхронизации широтноимпульсного модулятора, 44 - на вы ходе формирователя 6 тактовых импульсов, 45 - на выходе второго разряда К-разрядного двоичного счетчика 19, 46 - на выходе третьего разряда К-разрядного двоичного счетчика 19, 47 - на выходе четвертого разряда К-разрядного двоичного счетчика 19, 48 - на цифрового узла 20 сравнения, 49 - на выходе формирователя 10 импульсов синхронизации широтно-импульсного модулятора. Причем временные диаграммы (фиг.2) соответствуют многофазному импульсному стабилизатору, выполненному из силовых преобразовательных ячеек; 38 - 43 (фиг.З) - из силовых преобразовательных ячеек; а 44 - 49 - из1л 12 силовых преобразовательных ячеек. Многофазный импульсный стабилизатор работает следующим образом. С выхода генератора 5 синхроимпульсов напряжение с периодом 0,01 Т . К где Т - период коммутации силовых преобразовательных ячеек 2; К - требуемая (в %) точность воспроизведения длительности импульса выходного сигнала широтно-импульсного модулятора 11 на входе силовых преобразовательных ячеек 2, поступает на вход формирователей 6 и 7 тактовых импульсов, В качестве формирователей 6 и 7 тактовых импульсов могут бытЪ использованы двоичные п-разрядные счетчики (например, типа К155ИЕ5). При этом п определится выражением вида ги X 2., где гп - число силовых преобразовательных ячеек 2; М - максимально возможное число силовых преобразовательных ячеек 2. Выходные напряжения формирователей тактовых импульсов 6 и 7, показанные соответственно на эпюрах 2, 29 (фиг.2), в общем случае могут иметь сдвиг по фазе. Их период TD T/m определяет требуемый сдвиг вр времени между электрическими процессами в силовых преобразовательных ячейках 2. Выходное напряжение формирователя 6 тактовых импульсов используется: для получения на выходе формирователя 8 строб-импульсов (эпюра 33, фиг.-2) , совпадающих по времени с фронтом 1/0 напряжения (эпюра 22, фиг.2) формирователя 6; для синхронизации К-разрядного двоично гр счетчика 19; для синхронизации Р/-р рядного регистра 13 сдвига. .Количество разрядов двоичного счетчика 19 и цифрового узла 20 ср внения определяется максимально во можным числом И преобразовательных фаз 2 и определяется выражением вида {M+l),(M + l) ,2,3 Выходные сигналы на каждом из К выходов кодирующего блока 21 могут принимать два значения: О низкий уровень напряжения, высокий уровень напряжения. Предположим, что на выходе первых трех младших разрядов кодирующего блока 21 установлены высокие уровни н пряжений,, а с четвертого по К-й (при ) - низкие уровни. Это означает, что на выходе кодирующего блока 21 (соответственно на выходе узла сравнения 20) установлено число 111 в двоичной системе сч ления, соответствующее числу 7 в десятичной системе счисления. При этом на выходе цифрового узла 20 сравнения появится сигнал (высокий уровень напряжения) лишь в случае, когда на выходе всех трех младших разрядов К-разрядного счетчика 19 будут присутствовать одновременно высокие уровни,напряжений. Происходит это в моменты времени toftA 2./ fcb (эпюры 39-42, фиг.З) через равные интервалы времени Т - 7 Тц Высокий уровень напряжения с выход цифрового узла 20 сравнения поступает в указанные моменты времени О К-разря на выход установки в ного счетчика 19 (фиг.1) и на выход, формирователя 10 пилообразного напряжения. Указанный сигнал обеспечивает на выходе всех К разрядов двоичного счетчика 19 появлени низких уровней напряжений (эпюры 39-41.,- фиг.З) и на выходе Формиров теля 10 спад пилообразного напряжения (эпюра 43, фиг.З). На фиг.З (эпюры 44-49) показан случай, когд на выходе кодирующего блока устано лено в двойной системе счисления число 1100, соответствующее числу в десятичной системе счисления. Пр этом сброс в О К-разрядного счетчика 19(эпюра 28-32, фиг.2) и синхронизация формирователя 10 пилообразного напряжения производится в моменты ti , i, , i (эпюры 48 и 49, фиг.З) через равные интервалы времени Т 12 - Т. Таким образом, установка.на выходе кодир щего блока цифры позволяет формировать период пилообразного напряжения Т в гя раз превышающий период следования Т„ тактовых импуль сов. Как будет показано ниже это позволяет сформировать равномерно сдвинутые идентичные сигналы для правления т-м количеством силовых преобразовательных фаз. Очевидно число фаз м ограничено сверху максимально возможным числом М, определяемым количеством разрядов регистров 12 и 13 и соответственно количеством триггеров 17 управления, которые в свою очередь выбираются из условия обеспечения функциони рования максимально возможного числа м работающих на общую нагрузку силовых преобразовательных ячеек 2. Далее рассматривается работа многофазного стабилизатора при m N. Пилообразное напряжение Un(t) с периодом следования Т (эпюра 23, фиг.2) на выходе формирователя 10 и постоянное напряжение U(..t(t) Ha выходе схемы 15 сравнения используются для формирования на выходе модулятора 11 широтно-модулированного сигнала с длительностью импульсов tu и периодом Т (эпюра 24, фиг.2). Указанные сигнал поступает на информационный вход регистра 13 сдвига. Запись информации регистром 13 сдвига осуществляется фронтом 1/0 тактовых импульсов (эпюра 22, фиг.2), поступающих с выхода формирователя 6 на вход синхронизации регистра 13. Это обеспечивает появление у регистра 13 высокого уровня напряжения на выходе первого разряда в -момент (эпюра 25, фиг.2) на выходе второго разряда в момент (эпюра 26, Лиг.2), на выходе М-го разряда в момент ±(н-1)Т. В общем случае длительность импульсов на выходе регистра 13 (эпюры 25-27, фиг.2) отличается от длительности импульсов на выходе широтноимпульсного модулятора 11 (эпюра 24, фиг. 2) на величину O AttlVi. Такая же погрешность имеется в прототипе. Одновременное присутствие высоких уровней на входах логических элементов И-НЕ 16 обеспечивает на входе С. триггеров 17 управления низкий уровень -и их установку в О . Согласно временным диаграммам напряжений на входе логических элементов (эпюры 25-27, 30, 33, фиг.2), на выходе а первого триггера. 17 появится высокий уровень в момент , на выходе второго триггера 17 - в момент ,..., на выходе Ы-го триггера 17 - в -момент t-(M-l)T. До момента . универсальный М-разрядный регистр 12 находится в режиме последовательного приема информации со .сдвигом вправо, так как на входе выбора режима информаЦии присутствует низкий уровень

(эпюра 28, фиг.2). Тактовые импуль сы с выхода Лормирователя 7 (эпюра 29, фиг.2) поступают на вход синхронизации регистра 12 и обеспечивают в моменты времени фронта 1/0 запись поступающего на информационный вход низкого уровня. В момент времени (эпюра 24, фиг.2) на выходе широтно-импульсного модулятора 11 формируется низкий уровень напряжения. По .фронту 1/0 этого сигнала формирователь 9 обеспечивает короткий строб-импульс (эпюра 28, фиг.2), который высоким уровнем устанавливает формирователь (счетчик) 7 по входу R. в О и регистр 12 по входу в режим параллельного приема информации. Так как вход первого разряда подключен к плюсовой шине источника 18 питания, а входы со второго по М разряды подключены к минусовой шине источника 18 питания, то в момент 1/0 строб-импульса обеспечивается запись выходного уровня в первый разряд регистра 12 и низкого уровня в разряды со второго по/К1-й. После окончания строб-импульса.формирователь (счетчик 7) обеспечивает импульсы с периодом Tt (начиная с ) на выходе синхронизации регистра 12, перешедшего в режим последовательного приема информации (по информационному входу). Записанный в момент времени высокий уровень сохранения на выходе первого разряда регистра 12 на интервале времени -tu :t4tu+Tn (эпюра 30, фиг. 2) . В момент времени -t-tu +Тп , совпадающим с фронтом 1/0 поступающих с выхода формирователя 7 на вход синхронизации регистЕ)а 12 тактовых импульсов (эпюра 29, фиг.2), произойдет запись низкого уровня в первый разряд (эпюра 30, фиг.2) регистра 12, так как на входе присутствует низкий уровень (эпюра 28, фиг.2), а запись высокого уровня во второй разряд (эпюра 31, фиг.2).

Таким образом у регистра 12 появится высокий уровень напряжения (с длительностью равной Т,)г1а выходе первого разряда в момент времени -t tu , на выходе второго разряда в момент времени +Т , на выходе М-го разряда в момент времени -fc-tu + (1Ч-1).Т(у. Так как входные цепи регистра 12 подключены к входу синхронизации С триггеров 17 управления, то в

указанные моменты времени фронтом 0/1 происходит переключение триггеров 17 управления (по входу D присутствует высокий уровень). Формирователи, (счетчики) 6 и 7 имеют одинаковую разрядность. Это обеспечивает формирование тактовых импульсов с равным периодом Т,, но со сдвигом по фазе, так как начальное состояние формирователя (счетчика) 7

синхронизируется в момент времени t-tu. В результате на выходе триггеров 17 управления получаем широтно модулированные импульсы (эпюры 34, 35, 37 фиг.2), равные

по длительности сигналу на выходе широтно-импульсного модулятора 11. Их сдвиг во времени на величину Тц обеспечивает сдвиг во времени электрических процессов в силовых преобразовательных ячейках 2. В

следующие периоды времени процессы повторяются аналогично описанному выше.

Предлагаемое изобретение по сравнению с базовым объектом-прототипом позволяет снизить время и материальные затраты на проектирование источников, повысить унификацию всего устройства путем унификации

как силовых преобразовательных ячеек, так и блока управления.

Указанные преимущества достигаются за счет возможности управления различным количеством силовых

преобразовательных ячеек (от 2 до М) изменением лишь выходного сигнала кодирующего блока.

(риг. 2

Tn

i

38

ППППППППППППППППППППППППП,

39

ППП1ППП1ППП1ПП

40

n

n

n

t

ПП n n ПППППППП r

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизатор напряжения | 1983 |

|

SU1156032A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| Многофазный импульсный стабилизатор напряжения | 1987 |

|

SU1483438A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1019413A1 |

| Блок управления многофазным импульсным стабилизатором | 1983 |

|

SU1123085A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265741A1 |

| Многофазный импульсный стабилизатор | 1984 |

|

SU1196830A1 |

| Многофазный импульсный стабилизатор напряжения | 1990 |

|

SU1700545A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1317415A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1302255A1 |

МНОГОФАЗНЫЙ.ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР напряжения, содержащий силовую цепь, выполненную в виде параллельно включенных силовых преобразовательных ячеек, каждая из которых соединена с входными и выходными выводами, и блок управления, состоящий из генератора синхроим- , пульсов, формирователя импульсов синхронизации широтно-импульсного модулятора, М -разрядного регистра сдвига, универсального регистра сдвига, м триггеров управления, логических элементов И-НЕ, двух формирователей тактовых импульсов, двух формирователей строб-импульсов, источника опорного напряжения, аналогового узла сравнения, причем аналоговый узел сравнения одним из входов подключен к источнику опорного напряжения, другим - к выходным выводам, а выходом - к одному из входов широтно-импульсного модулятора, другой вход которого подключен к выходу формирователя импульсов синхронизации широтно-импульсного модулятора, выход широтно-импульсного модулятора подключен к информационному входу М-разрядного регистра сдвига и через второй формирователь стробимпульсов - к входам универсального М -разрядного регистра и к входу установки в О второго формирователя тактовых импульсов, выход которого подключен к входу синхронизации режима последовательного приема информации универсального И-разрядного регистра, а вход - к выходу генератора синхроимпульсов и к входу первого формирователя тактовых импульсов, вход формирователя импульсов синхронизации широтно-импульсного модулятора подключен к входу синхронизации М-разрядного регистра сдвига и (g через первый формирователь строб(Л импульсов - к входам М логических элементов И-НЕ, каждый выход универсального М -разрядного регистра под ключен к входу синхронизации соответствующего триггера управления, к выходам которых подключены управляющие входы силовых преобразовательных ячеек, отличающийся тем, что, с целью увеличения функцио-. нальных возможностей, введены -разрядный двоичный счетчик, к-разрядный цифровой узел сравнения и ел ю модулирующий блок, причем вход («.-разрядного счетчика подключен к вы ходу первого формироватедя тактовых оо импульсов, а каждый из . выходов к соответствующим информационным .входам цифрового узла сравнейия, кодирукнцие входы которого подключены к соответствующим выходам кодирующего блока, а выход - к входу установки в О к-разрядного двоичного счетчика и входу формирователя импульсов синхронизации широтно-импульсного модулятора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Юрченко А.И,, гауваев Ю,Н, Основные структурные схемы управления многофазных импульсных преобразователей, - Вопросы радиотехники | |||

| Серия общетехническая | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке I 3394059/07, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1984-01-30—Публикация

1982-11-11—Подача