Изобретение относится к аналого- цифровой вычислительной технике и может быть применено для решения краевых задач, описываемых дифференциальными уравнениями в частных производных с функциональными и нелинейными зависимостями коэффициентов, методом дискретного моделирования.

Целью изобретения является повышение точности функционирования устройства .

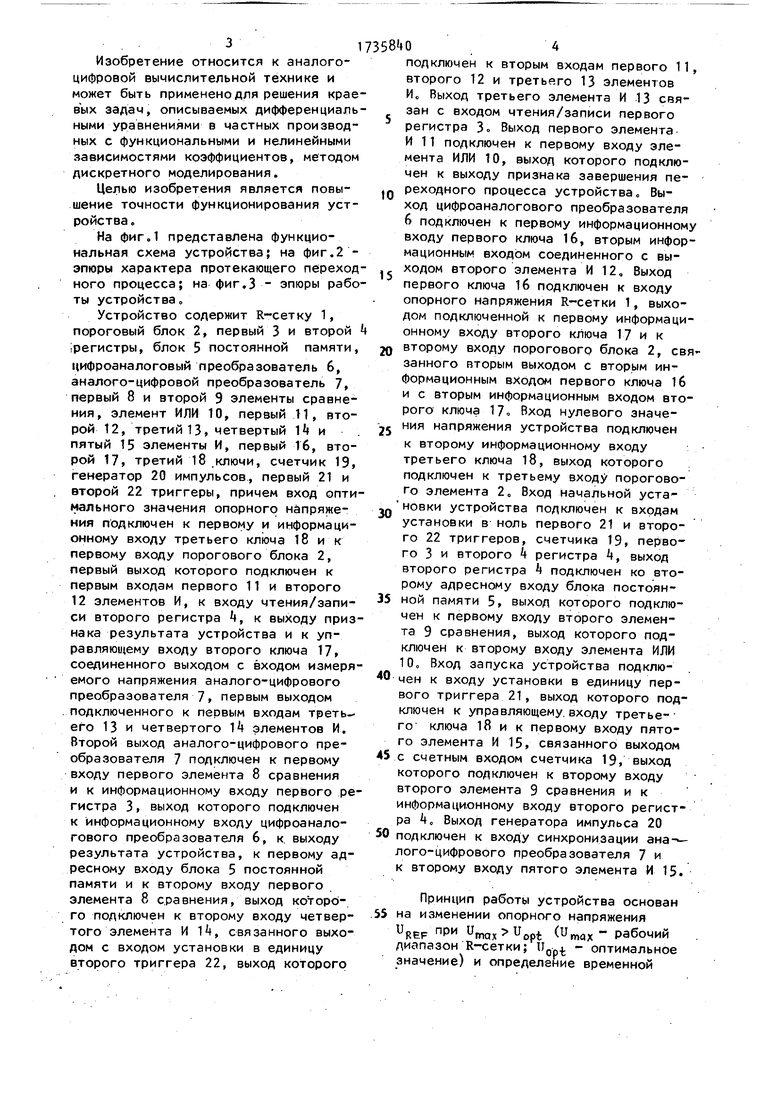

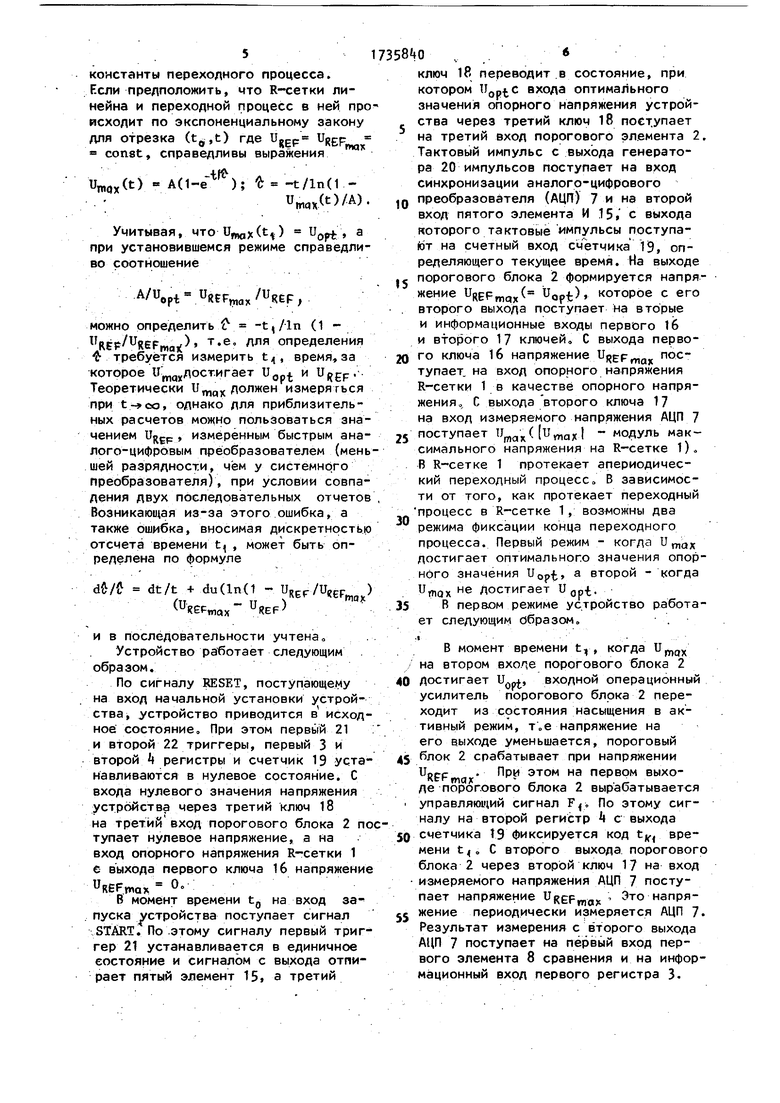

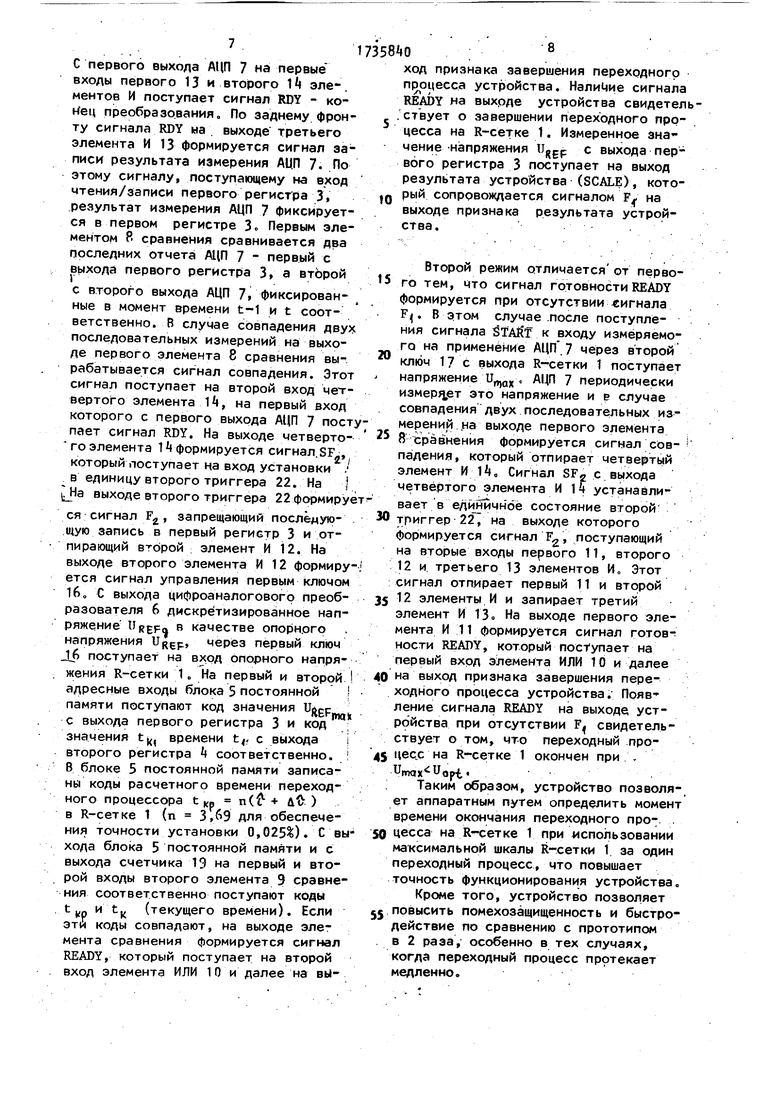

На фиг.1 представлена функциональная схема устройства; на фиг.2 - эпюры характера протекающего переходного процесса; на фиг.З - эпюры работы устройства.

Устройство содержит R-сетку 1, пороговый блок 2, первый 3 и второй регистры, блок 5 постоянной памяти, цифроаналоговый преобразователь 6, аналого-цифровой преобразователь 7, первый 8 и второй 9 элементы сравнения, элемент ИЛИ 10, первый 11, второй 12, третий 13, четвертый 1 и пятый 15 элементы И, первый 16, второй 17, третий 18 ключи, счетчик 19, генератор 20 импульсов, первый 21 и второй 22 триггеры, причем вход оптимального значения опорного напряжения подключен к первому и информационному входу третьего ключа 18 и к первому входу порогового блока 2, первый выход которого подключен к первым входам первого 11 и второго 12 элементов И, к входу чтения/записи второго регистра , к выходу признака результата устройства и к управляющему входу второго ключа 17, соединенного выходом с входом измеряемого напряжения аналого-цифрового преобразователя 7, первым выходом подключенного к пеовым входам третьего 13 и четвертого 1 элементов И. Второй выход аналого-цифрового преобразователя 7 подключен к первому входу первого элемента 8 сравнения и к информационному входу первого регистра 3. выход которого подключен к информационному входу цифроанало- гового преобразователя 6, к выходу результата устройства, к первому адресному входу блока 5 постоянной памяти и к второму входу первого элемента 8 сравнения, выход которого подключен к второму входу четвертого элемента И 1, связанного выходом с входом установки в единицу второго триггера 22, выход которого

5

5

подключен к вторым входам первого 11, второго 12 и третьего 13 элементов И0 Выход третьего элемента И 13 связан с входом чтения/записи первого регистра 3° Выход первого элемента И 11 подключен к первому входу элемента ИЛИ 10, выход которого подключен к выходу признака завершения переходного процесса устройства. Выход цифроаналогового преобразователя 6 подключен к первому информационному входу первого ключа 16, вторым информационным входом соединенного с выходом второго элемента И 12. Выход первого ключа 16 подключен к входу опорного напряжения R-сетки 1, выходом подключенной к первому информационному входу второго ключа 17 и к

второму входу порогового блока 2, связанного вторым выходом с вторым информационным входом первого ключа 16 и с вторым информационным входом второго ключа 17° Вход нулевого значения напряжения устройства подключен к второму информационному входу третьего ключа 18, выход которого подключен к третьему входу порогового элемента 2. Вход начальной установки устройства подключен к входам установки в ноль первого 21 и второго 22 триггеров, счетчика 19, первого 3 и второго k регистра , выход второго регистра h подключен ко второму адресному входу блока постоянной памяти 5, выход которого подключен к первому входу второго элемента 9 сравнения, выход которого подключен к второму входу элемента ИЛИ 10, Вход запуска устройства подключен к входу установки в единицу первого триггера 21, выход которого подключен к управляющему входу третьего ключа 18 и к первому входу пятого элемента И 15, связанного выходом с счетным входом счетчика 19, выход которого подключен к второму входу второго элемента 9 сравнения и к информационному входу второго регистра 4. Выход генератора импульса 20

0 подключен к входу синхронизации лого-цифрового преобразователя 7 и к второму входу пятого элемента И 15.

Принцип работы устройства основан 5 на изменении опорного напряжения UREF при VmQ1(Vofi (Umax- рабочий диапазон R-сетки; Пор - оптимальное значение) и определение временной

0

5

0

S

константы переходного процесса. Если предположить, что R-сетки линейна и переходной процесс в ней происходит по экспоненциальному закону

для отрезка (t0,t) где UREF UREp

U,

const, справедливы выражения -tfЈ,

ma

ТП0Х

(t) - А(1-е ); fc - -t/ln(1 UWMW(t)/A)

max

Учитывая, что ) uopt а при установившемся режиме справедливо соотношение

U

REF,

мах

/и

REF

А

можно определить с TW%Fwa)(. т.е

-t,/ln (1 - для определения

Ј требуется измерить t, время,за которое итахдостигает Uopt и URЈF Теоретически Umqx должен измеряться при , однако для приблизительных расчетов можно пользоваться значением UREF , измеренным быстрым аналого-цифровым преобразователем (меньшей разрядности, чем у системного Преобразователя), при условии совпадения двух последовательных отчетов Возникающая из-за этого ошибка, а также ошибка, вносимая дискретностью отсчета времени ц , может быть определена по формуле

dfc/Ј dt/t + du(ln(1 - UREF/U EF «Wcu- EF)

НЮХ

и в последовательности учтена

Устройство работает следующим образом.

По сигналу RESET, поступающему на вход начальной установки устройства, устройство приводится в исходное состояние При этом первый 21 и второй 22 триггеры, первый 3 и второй А регистры и счетчик 19 устанавливаются в нулевое состояние. С входа нулевого значения напряжения устройства через третий ключ 18

на третий вход порогового блока 2 потупает нулевое напряжение, а на вход опорного напряжения R-сетки 1 с выхода первого ключа 16 напряжение

REFmax °°

В момент времени tQ на вход запуска устройства поступает сигнал START. По этому сигналу первый триггер 21 устанавливается в единичное состояние и сигналом с выхода отпирает пятый элемент 15, а третий

,

10

„

ключ 18 переводит в состояние, при котором И0рЈС входа оптимального значения опорного напряжения устройства через третий ключ 18 поступает на третий вход порогового элемента 2. Тактовый импульс с выхода генератора 20 импульсов поступает на вход синхронизации аналого-цифрового преобразователя (АЦП) 7 и на второй вход пятого элемента И 15 с выхода которого тактовые импульсы поступают на счетный вход сч етчика 19, определяющего текущее время. На выходе порогового блока 2 формируется напряжение UREFrnqx( UQp), которое с его второго выхода поступает на вторые и информационные входы первого 16 и второго 17 ключей, С выхода перво- 20 го ключа 16 напряжение . пос тупает. на вход опорного напряжения R-сетки 1 в качестве опорного напряжения С выхода второго ключа 17 на вход измеряемого напряжения АЦП 7

15

25

споступает Umax( (Uynax I модуль макma х

30

KIM n .

симального напряжения на R-сетке ) В R-сетке 1 протекает апериодический переходный процесс В зависимости от того, как протекает переходный процесс в R-сетке 1, возможны два режима фиксации конца переходного процесса. Первый режим - когда U max достигает оптимального значения опорного значения U0pЈ, а второй - когда umax He Достигает U0p. 35 В первом режиме устройство работает следующим образом.

i

В момент времени ц , когда Umax

на втором вхопе порогового блока 2

40 Достигает U0(., входной операционный усилитель порогового блока 2 переходит из состояния насыщения в активный режим, т.е напряжение на его выходе уменьшается, пороговый

45 блок 2 срабатывает при напряжении URPF р этом на первом выходе порогового блока 2 вырабатывается управляющий сигнал По этому CHI- налу на второй регистр k с выхода

50 счетчика 19 фиксируется код tKl времени 14„ С второго выхода порогового блока 2 через второй ключ 17 на вход измеряемого напряжения АЦП 7 поступает напряжение , Это напрясе жение периодически измеряется АЦП 7. Результат измерения с второго выхода АЦП 7 поступает на первый вход первого элемента 8 сравнения и на информационный вход первого регистра 3.

С первого выхода АЦП 7 на первые входы первого 13 и второго 1 эле-, ментов И поступает сигнал RDY - ко- преобразования,, По заднему фронту сигнала RDY на выходе третьего элемента И 13 формируется сигнал записи результата измерения АЦП 7. По этому сигналу, поступающему на вход чтения/записи первого регистра 3, результат измерения АЦП 7 фиксируется в первом регистре 3. Первым элементом 8 сравнения сравнивается два последних отчета АЦП 7 - первый с выхода первого регистра 3, а второй

1

с второго выхода АЦП 7, фиксирован- ные в момент времени t-1 и t соответственно. В случае совпадения двух последовательных измерений на выходе первого элемента 8 сравнения вы рабатывается сигнал совпадения. Этот сигнал поступает на второй вход четвертого элемента , на первый вход которого с первого выхода АЦП 7 постпает сигнал RDY. На выходе четверто- го элемента 1 формируется сигнал. SF, который поступает на вход установки J ; в единицу второго триггера 22. На } ijte выходе второго триггера 22формируся сигнал F2, запрещающий последующую запись в первый регистр 3 и отпирающий второй ; элемент И 12. На выходе второго элемента И 12 формиру ется сигнал управления первым ключом 16 С выхода цифроаналоговогр преобразователя 6 дискрётизированное напряжение MREFQ в качестве опорного напряжения UR6F, через первый ключ 1б поступает на вход опорного напряжения R-сетки 1. На первый и второй адресные входы блока 5 постоянной памяти поступают код значения U6pp

лсг|ГИ

с выхода первого регистра 3 и код значения t, времени t с выхода второго регистра соответственно. В блоке 5 постоянной памяти записаны коды расчетного времени переход

ного процессора t к. п(Ј + Л ) в R-сетке 1 (п 3,69 для обеспечения точности установки .0,025%) С вы хода блока 5 постоянной памяти и с выхода счетчика 19 на первый и второй входы второго элемента 9 сравнения соответственно поступают коды tkp и tK (текущего времени). Если эти коды совпадают, на выходе эле мента сравнения формируется сигнал READY, который поступает на второй вход элемента ИЛИ 10 и далее на вЫ

; 8

ход признака завершения переходного процесса устройства. Наличие сигнала READY на выходе устройства свидетель- .ствует о завершении переходного процесса на R-сетке 1. Измеренное значение -напряжения с выхода первого регистра 3 поступает на выход результата устройства (SCALE), кото- JQ рый сопровождается сигналом F на

выходе признака ства.

результата устрои

Второй режим отличается от первого тем, что сигнал готовности READY формируется при отсутствии «игнала F. В этом случае .после поступления сигнала START к входу измеряемого на применение АЦП.7 через второй ключ 17 с выхода R-сетки 1 поступает напряжение Umax с АЦП 7 периодически измеряет это напряжение и в случае совпадения двух последовательных измерений на выходе первого элемента

8 сравнения формируется сигнал сов- падения, который отпирает четвертый элемент И И, Сигнал SF«.с. выхода четвёртого элемента И 1ч устанавливает в единичное состояние второй

триггер 22, на выходе которого формируется сигнал F2, поступающий на вторые входы первого 11, второго 12 и третьего 13 элементов И0 Этот сигнал отпирает первый 11 и второй

12 элементы И и запирает третий

элемент И 13 На выходе первого элемента И 11 формируется сигнал готов ности READY, который поступает на первый вход элемента ИЛИ 10 и далее

на выход признака завершения переходного процесса устройства. Появление сигнала READY на выходе устройства при отсутствии FJ свидетельствует о том, что переходный проиес,с на R-сетке 1 окончен при ,

Umax UoptТаким образом, устройство позволяет аппаратным путем определить момент времени окончания переходного про- . цесса на R-сетке 1 при использовании максимальной шкалы R-сетки 1. за один переходный процесс, что повышает точность функционирования устройства.

Кроме того, устройство позволяет повысить помехозащищенность и быстродействие по сравнению с прототипом в 2 раза, особенно в тех случаях, когда переходный процесс протекает медленно.

Формула изобретения

Устройство для решения дифференциальных уравнений в частных производных, содержащее R-сетку, пороговый блок, первый регистр, блок постоянной памяти, цифроаналоговый преобразователь, аналого-цифровой преобразователь, элемент сравнения, элемент ИЛИ и с первого по пятый элементы И, причем вход оптимального значения опорного напряжения подключен к первому входу порогового блока, первый выход которого подключен к первым входам первого и второго элементов И и к выходу признака результата устройства, первый выход аналого-цифрового преобразователя подключен к первым входам третьего и четвертого элементов И, второй выход аналого-цифрового преобразователя подключен к первому входу первого элемента сравнения и к информационному входу первого регистра, выход которого подключен к информационному входу цифроаналогового преобразователя, к выходу результата устройства, к первому адресному вход блока постоянной памяти и к второму входу первого элемента сравнения, выход которого подключен к второму входу четвертого элемента И, выход R-сетки, выход третьего элемента И и выход первого элемента И подключены соответственно к второму входу порогового блока, к входу чтения записи первого регистра и к первому входу элемента ИЛИ, выход которого подключен к выходу признака завершения .переходного процесса устройства, обличающееся тем, что, с целью повышения точности функционирования устройства, оно содержит с первого по третий ключи, счетчик, генератор импульсов, первый и второй триггеры, второй регистр и второй элемент сравнения, причем выход цифро аналогового преобразователя и выход второго элемента И подключены соот5

ветственно к первому информационному и к управляющему входу первого ключа, выход которого подключен к входу опорного напряжения R-сетки, первый выход порогового блока подключен к входу чтения записи второго регистра и к управляющему входу второго ключа, выход которого подключен к 0 входу измеряемого напряжения аналого- цифрового преобразователя, выход R-сетки подключен к первому информационному входу второго ключа, второй выход порогового блока подключен к вторым информационным входам первого и второго ключей, вход оптимального значения опорного напряжения и вход нулевого значения напряжения устройства подключены соответствен- 0 но к первому и к второму информационным входам третьего ключа, выход которого подключен к третьему входу порогового блока, вход начальной установки устройства подключен к с входам установки в О первого и второго триггеров, счетчика и второго регистра, выход которого подключен к второму адресному входу блока постоянной памяти, выход которого подключен к первому входу второго элемента сравнения, выход которого подключен к второму входу элемента ИЛИ, вход запуска устройства подключен к входу установки в 1 первого триггера, выход которого подключен к управляю- щему входу третьего ключа и к первому входу пятого элемента И, выход которого подключен к счетному входу счетчика, выход которого подключен к второму входу второго элемента сравнения и к информационному входу второго регистра, выход генератора импульсов подключен к входу синхронизации аналого-цифрового преобразователя и к второму входу пятого 5 элемента И, выход четвертого элемента И подключен к входу установки в 1 второго триггера, выход которого подключен к вторым входам первого, второго и третьего элементов И. 0

0

5

0

4ГЈЛ

mix

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1675911A1 |

| Дифференцирующее устройство | 1988 |

|

SU1508246A1 |

| Устройство передачи информации по волоконно-оптической линии связи | 1988 |

|

SU1675919A1 |

| Радиометр | 1990 |

|

SU1723460A1 |

| Статистический анализатор выбросов и провалов напряжения | 1990 |

|

SU1837325A1 |

| Устройство для измерения гистерезиса @ характеристик | 1985 |

|

SU1247797A1 |

| УСТРОЙСТВО ДЛЯ СИГНАЛИЗАЦИИ ОДНОФАЗНОГО ЗАМЫКАНИЯ НА ЗЕМЛЮ В ЭЛЕКТРИЧЕСКОЙ СЕТИ ПЕРЕМЕННОГО ТОКА | 1995 |

|

RU2101826C1 |

| Преобразователь угла поворота вала в код | 1981 |

|

SU1246371A1 |

| Устройство для измерения сварочного тока | 1983 |

|

SU1098715A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2012 |

|

RU2504830C2 |

Изобретение относится к аналого-цифровой вычислительной технике и может быть применено для решения краевых задач, описываемых дифференциальными уравнениями в частных производных с функциональными и нелинейными зависимостями коэффициентов, методом дискретного моделирования. Цель изобретения - повышение точности функционирования устройства. Поставленная цель достигается тем, что устройство содержит R-сетку 1, пороговый блок.2, первый 3 и второй 4 регистры, блок постоянной памяти 5, цифроаналоговый преобразователь 6, аналого-цифровой преобразователь 7, первый 8 и второй 9 элементы сравнения, элемент ИЛИ 10, первый 11, второй 12, третий 13, четвертый 14 и пятый 15 элементы И, первый 16, второй 17, третий 18 ключи, счетчик 19, генератор импульсов 20, первый 21 и второй 22 триггеры, 3 ил. (Я v| со СЛ оо ФиеЛ

VteFmax

to i7

Фиг. 2

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1986 |

|

SU1324043A2 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1992-05-23—Публикация

1989-12-22—Подача