i

(/

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения фазового сдвига | 1988 |

|

SU1661668A1 |

| Устройство для числового программного управления | 1985 |

|

SU1352459A1 |

| Устройство для контроля сдвига фаз двух сигналов | 1989 |

|

SU1716522A1 |

| Устройство для считывания графической информации | 1989 |

|

SU1683046A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЫСТРОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1989 |

|

SU1841074A1 |

| Устройство для обмена информацией между объектом контроля и электронной вычислительной машиной | 1983 |

|

SU1156078A1 |

| Устройство для электроразведки | 1986 |

|

SU1350642A1 |

| Приемник сигналов с двойной фазовой манипуляцией | 1985 |

|

SU1264370A2 |

| Способ определения цикловой подачи топлива и устройство для его осуществления | 2015 |

|

RU2665566C2 |

Изобретение относится к вычислительной технике и может быть использовано для измерения фазового сдвига между двумя сигналами и периода входного сигнала. Целью изобретения является повышение полноты контроля . Устройство содержит блоки 1,2 приема сигнала, блоки 3, измерения,

vl

со ел

00

К1

блок 5 формирования опорных частот, блок 6 управления, блок 7 контроля. Устройство может работать в режимах Фаза 1, аэа 2 и Период. Пос- тавленная цель достигается за счет контроля отношения значения опорной частоты к ее допустимому значению. При работе в режиме аза 1 устройство переходит на программу измерения

Изобретение относится к вычислительной технике и может быть использовано в контрольно-измерительной технике для измерения фазового сдвига между двумя сигналами и периода входного сигнала.

Известно устройство, содержащее формирователь, входы которого подклю чены к входным шинам устройства, а выход - к входу блока управления и первому входу первого элемента И, выход которого подключен к счетному входу первого счетчика импульсов и первому входу второго элемента И, второй вход которого подключен к выходу первой схемы сравнения кодов, а выход - к счетному входу второго счетчика импульсов, первый выход которого подключен к регистрируемому устройству, а вторые входы - к первым входам первой схемы сравнения кодов, вторые входы которой подключены к выходам первого счетчика импульсов, вход С.брос которого объединен с первым входом третьего элемента И и подключен к первому выходу блока управления, второй выход которого подключен к первому входу триггера, второй вход которого подключен к вы- ходу второй схемы сравнения кодов, первые входы которой подключены к выходам первого счетчика импульсов и входам Перезапись регистра, а вторые входы - к первым выходам регистра, второй вход Перенос которого подключен к выходу третьего элемента И, второй вход которого соединен с выходом триггера, последовательно соединенные инвертор и четвертый элемент И, последовательно соединенные фазовый детектор, фильтр нижних частот и перестраиваемый генератор, а также третий счетчик импульсов, выхо которого подключен к первому входу фзового детектора, и вход инвертора,

сдвига, обеспечивающего минимум времени на определение величины фазового сдвига При задании режима Фаза 2 или Период устройство переходит на программу измерения периода входного сигнала tT, а при реализации режима Фаза 2 также производится измерение фазового сдвига t™.

3 З.П, ф-ЛЫ, 15 ИЛ,

5

второй вход фазового детектора соединен с входом, шиной устройства и с вторым входом четвертого элемента И, третий вход которого соединен с вхо дом третьего счетчика импульсов, второй вход первого элемента И - с выходом перестраиваемого генератора, при этом выход четвертого элемента И подключен к входу Сброс второго счетчика импульсов и регистра.

Недостатком устройства является низкая полнота его контроля

Известно также устройство для измерения временных интервалов с само- контролем, содержащее генератор им0 пульсов эталонной частоты, первый и второй блоки сравнения, счетчик импульсов, первый и второй элементы И, коммутатор, три коммутационных блока, дешифратор, реверсивный счетчик им5 пульсов, четыре триггера, три элемента НЕ, тринадцать элементов И и блок задержки, причем коммутатор подключен первым информационным входом к первому информационному входу устройства

0 и к первому входу первого блока сравнения, вторым информационным входом - к второму информационному входу устройства, а выходом - к первому входу второго блока сравнения, соединенно5 го вторым входом с выходом источника опорного напряжения и с вторым входом1 первого блока сравнения, подключенного выходом к первому входу элемента И, связанного выходом с первым входом

0 второго элемента И, подключенного выходом к счетному входу счетчика импульсов, первый вход блока задержки подключен к выходу второго блока сравнения, первым выходом через пер5 вый элемент НЕ - к второму входу первого элемента И, а группами вторых входов и выходов - соответственно к первым группам информационных выходов и входов первого коммутационного

блока, соединенного группой вторых информационных входов-выходов с шиной данных устройства, а первым и вторым управляющими входами - с выходами соответственно третьего и четвертого элементов И, подключенных первыми входами к шине управления устройства, а вторыми входами - к первому выходу дешифратора, связанного с шиной адреса устройства, вторым входом - с первыми входами пятого и шестого элементов И, а третьим выходом - с первыми входами седьмого и восьмого элементов И, подключенных вторыми входами к вторым входам соответственно пятого и шестого элементов И и к шине управления устройства, а выходами соответственно - к первому и к второму управляющим входам второго коммутационного блока, соединенного группами первых информационных входов и выходов соответственно с разрядными выходами и с установочными входами реверсивного счетчика импульсов, а группой вторых информа- ционных входов «-выход о в - с шиной данных устройства, подключенной к группе первых информационных входов- выходов третьего коммутационного блока, соединенного первым и вторым управляющими входами с выходами соответственно шестого и пятого элементов И, а группами вторых информационных входов-выходов - соответственно с разрядными выходами и установочными входами счетчика импульсов, подключенного выходом переполнения к первым входам девятого элемента И и десятого элемента И, соединенного выходом со счетным входом первого , триггера, а вторым входом - с входом прямого счета реверсивного счетчика импульсов, с прямым выходом второго I триггера и с первым входом одиннадцатого элемента И, подключенного вторым входом к инверсному выходу третьего триггера, третьим входом - к выходу первого элемента И, к первому вхо- ду двенадцатого элемента И и к первому входу тринадцатого элемента И, а выходом через второй элемент НЕ - второму входу двенадцатого элэмента И и непосредственно к счетному входу третьего триггера, связанного нулевым входом с нулевыми входами первого, второго и четвертого триггеров и с входом Сброс устройства, а гГря- мым выходом - с управляющим входом коммутатора, с первым входом четырнадцатого элемента И и с вторым входом тринадцатого элемента И, подключенного выходом к единичному входу четвертого триггера, а третьим входом - к инверсному выходу четвертого триггера и к второму входу четырнадцатого элемента И, соединенного выходом через третий элемент НЕ с первым вхо- JQ дом пятнадцатого элемента И, подключенного вторым входом к выходу генератора импульсов эталонной частоты, третьим входом - к второму входу второго элемента И и к инверсному выходу 15 первого триггера, четвертым входом - к третьему входу второго элемента И и к входу Пуск устройства, пятым входом - к выходу двенадцатого элемента И, ,а выходом - к счетному входу ре- Q версивного счетчика импульсов, связанного входом обратного счета с инверсным выходом второго и с вторым входом девятого элемента И, подклю-- ченного выходом.к счетному входу вто- 5 РОГО триггера.

Недостатком известного устройства является низкая полнота контроля, обусловленная тем, что из-за отклонений значений опорной частоты не обеспечивается требуемая точность измерения, причем неисправности, возникающие в устройстве, в реальном масштабе времени не обнаруживаются.

Цель изобретения - повышение полноты контроля. 5 Поставленная цель достигается

тем,что устройство для контроля пара метров, содерж51нее первый блок приема сигнала, первый блок измерения, блок формирования частоты, блок уп- 0 равления, адресный выход которого соединен с адресными входами первого блока приема сигнала, первого блока измерения и блока формирования опорных частот, выход управления 5 записью/чтением - с входом управления записью/чтением первого блока приема сигнала, первого блока измерения, блока формирования опорных частот, информационный выход - с команд- 0 ными входами первого блока приема

сигнала, первого блока измерения, блока формирования опорных частот, информационный вход - с информационными выходами первого блока приема сиг- 5 нала, первого блока измеренияt блока формирования опорных частот, первый и второй информационные входы первого блока приема сигнала являются соответственно первым и вторым инфор0

717

мационными входами устройства, предназначенными для подключения к выхо- дам объекта контроля, содержит блок приема сигнала, второй блок измерения и блок контроля, первый вход момента перехода контролируемого сигнала через ноль которого подключен к второму выходу момента перехода контролируемого сигнала через ноль первого бло- ка приема, второй вход момента перехода контролируемого сигнала через ноль - к первому выходу момента времени перехода контролируемого сигнала через ноль первого блока приема сигнала, третий вход момента перехода контролируемого сигнала через ноль - к второму выходу момента перехода контролируемого сигнала через ноль второго блока приема сигнала, четвертый вход момента перехода контролируемого сигнала через ноль - к первому выходу момента перехода контролируемого сигнала через ноль второго блока приема сигнала, пер- вый вход запуска - к выходу начала измерения второго блока измерения, первый вход длительности интервала измерения - к выходу длительности интервала измерения второго блока измерения, второй вход запуска - к выходу начала измерения первого блока измерения, второй вход длительности интервала измерения - к выходу длительности интервала измерения первого блока измерения, выход наличия неисправности - к входу блокировки первого и второго блоков измерения, первый выход момента перехода контролируемого сигнала через ноль и выход сигнала окончания измерения пер- вого блока приема сигналов соединены соответственно с выходом запуска и с входом сброса первого блока измерения, вход стробирования - с вторым выходом момента времени перехода контролируемого сигнала через ноль второго блока приема сигнала, первы и второй информационные входы которого являются соответственно третьим и четвертым информационными входа ми устройства, первый выход момента времени перехода контролируемого сигнала через ноль и выход сигнала окончания преобразования - входом за-i пуска и входом сброса второго блока измерения, входы опорной частоты первого и второго блоков измерения соответственно соединены с первым и вторым выходами блока формирования 4ac

S

1

5 5 0 S 0 5

В

тот, адресный выход блока управления подключен к адресным входам второго блока приема сигнала, второго блока измерения, блока контроля, выход управления записью/чтением - к входам управления записью/чтением второго блока приема сигнала, блока контроля, информационный выход - к командным входам второго блока приема сигнала, второго блока измерения, блока контроля, информационный вход - к информационным выходам второго блока приема сигнала, второго блока измерения, блока контроля.

С этой целью блок контроля содержит первый, второй, третий триггеры, элемент ИЛИ, с первого по девятый элементы И, сумматор по модулю два, первый и второй элементы сравнения, элемент НЕ, причем первый и второй входы момента перехода контролируемого сигнала через ноль блока соединены с первым и вторым входами элемента сравнения, третий и четвертый входы момента перехода контролируемого сигнала через ноль блока соединены с первым и вторым входами второго элемента сравнения, выход второго элемента сравнения подключен к второму входу пятого элемента И, первый вход которого соединен с выходом первого элемента сравнения, выход которого соединен с вторым входом восьмого элемента И и через элемент НЕ с входом третьего триггера, выход которого подключен к первому входу девятого элемента И, второй вход которого соединен с адресным входом блока, третий вход - с управляющим входом блока, адресныйвход блока соединен с первыми входами первого, второго, третьего и четвертого элементов И, командный вход блока - с вторым входом первого элемента И, управляющий вход блока - с третьим входом первого элемента И, с вторым входом второго, третьего и четвертого элементов И, выход которого подключен к входу сброса второго и третьего триггеров, выход первого элемента И соединен с входом установки первого триггера, вход сброса которого подключен к выходу второго элемента И, прямой выход - к третьему входу шестого элемента И и к управляющему входу третьего элемента сравнения, инверсный выход - к третьему входу седьмого элемента И и к управляющему входу второго элемента сравнения, первый и

второй входы длительности интервала измерения блока соединены соответственно с первым и вторым входами сумматора по модулю два, выход которого подключен к второму входу шестого и седьмого элементов И, первый вход которого соединен с вторым входом запуска блока, а выход - с вторым входом первого элемента ИЛИ, первый вход которого подключен к выходу шестого элемента И, первый вход которого соединен с первым входом запуска блока, четвертый вход - с вторым входом запуска блока, выход первого элемента ИЛИ подключен к входу установки второго триггера, инверсный выход которого соединен с первым входом восьмого элемента И и с третьим входом четвертого элемента И, выход восьмого элемента И соединен с выходом наличия неисправности блока.

Каждый из блоков приема сигналов содержит узел преобразования синусоидального сигнала в прямоугольный, узел выделения переднего фронта, .регистр, с первого по восьмой элементы 1ч, первый и второй элементы ИЛИ, первый и второй триггеры, масштабный преобразователь, блок элемента И, причем первый и второй информационные блоки соединены с первым и вторым входами узла преобразования синусоидального сигнала в прямоугольный выход которого соединен с входом узла выделения переднего фронта, выход которого соединен с вторым выхо-- дом третьего момента перехода контролируемого сигнала через ноль блока, с первыми входами третьего и пятого элементов И, вход стробирования блока через масштабный элемент соединен с первым входом второго и четвертого элементов И, выходы второго и третьего элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с первым выходом момента времени перехода контролируемого си|- нала через ноль блока И и с входом установки первого триггера, прямой выход которого соединен с третьим входом седьмого элемента И, выходы четвертого и пятого элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с выходом сигнала окончания измерения блока .и с входом установки второго триггера, прямой выход которого подключен к

0

5

5

третьему входу шестого элемента И, первый вход первого элемента И соединен с адресным входом блока, второй в-ход - с управляющим входом блока , а выход - с входом сброса первого и второго триггеров, адресный вход блока соединен с первым входом шестого, седьмого и восьмого элементов И, с вторыми входами блока элементов И, управляющий вход блока - с вторым входом шестого, седьмого и восьмого элементов И и с первыми входами блока элементов И, выходы которого и выходы шестого и седьмого элементов И образуют информационный выход блока, выход восьмого элемента V соединен с синхровходом регистра, информационные входы которого являются командQ ным-входом блока, а выходы соединены- с вторыми входами второго, третьего, четвертого, пятого элементов И, и с третьими входами блока элементов И.

Блок измерения содержит первый и второй триггер, элемент ИЛИ, с первого по шестой элементы И, первый и второй счетчики импульсов, первую и вторую группы элементов И, причем адресный вход блока соединен с первыми входами пятого элемента И, первой группы элементов И, шестого элемента И, второй группы элементов И и с вторыми входами третьего и четвертого элементов И, вход управления записью/чтением блока - с вторыми вхо5 дами пятого, шестого, элементов И, первой, второй группы элементов И и с третьим входом третьего и четвертого элементов И, командный вход блока- с информационными входами первого и второго счетчика импульсов и с четвертым входом третьего элемента И, информационный выход блока образуют выходы первой и второй групп элементов И и выход третьего элемента И, вход блокировки блока соединен с четвертым входом третьего элемента И и с первым входом четвертого элемента И, выход которого подключен к первому входу первого элемента И и с

0 входом сброса второго триггера, прямой выход которого соединен с вторым входом первого элемента ИЛИ и с первым входом третьего элемента И, а инверсный выход - с первым входом первого элемента И, выход которого подключен к счетному входу первого счетчика импульсов, вход разрешения которого соединен с выходом пятого элемента И, информационные выходы 0

0

S

5

11

с третьей группой входов первой группы элементов И, а выход переполнения - с входом установки второго ; триггера, вход запуска блока соединен с входом установки первого гера, с вторым входом первого элемента И, вход сброса блока - с входом сброса первого триггера, вход установки которого подключен к выходу первого элемента ИЛИ, а выход соединен с вторым входом второго элемента И и с выходом начала измерения блока, , вход опорной частоты блока - с первым входом второго элемента И, выход которого соединен со счетным входом второго счетчика импульсов и с выходом длительности интервала измерения блока, выходы второго счетчика импульсов соединены с третьей группой входов второй группы элементов И, вход разрешения счета второго сче чика - с выходом шестого элемента И.

I

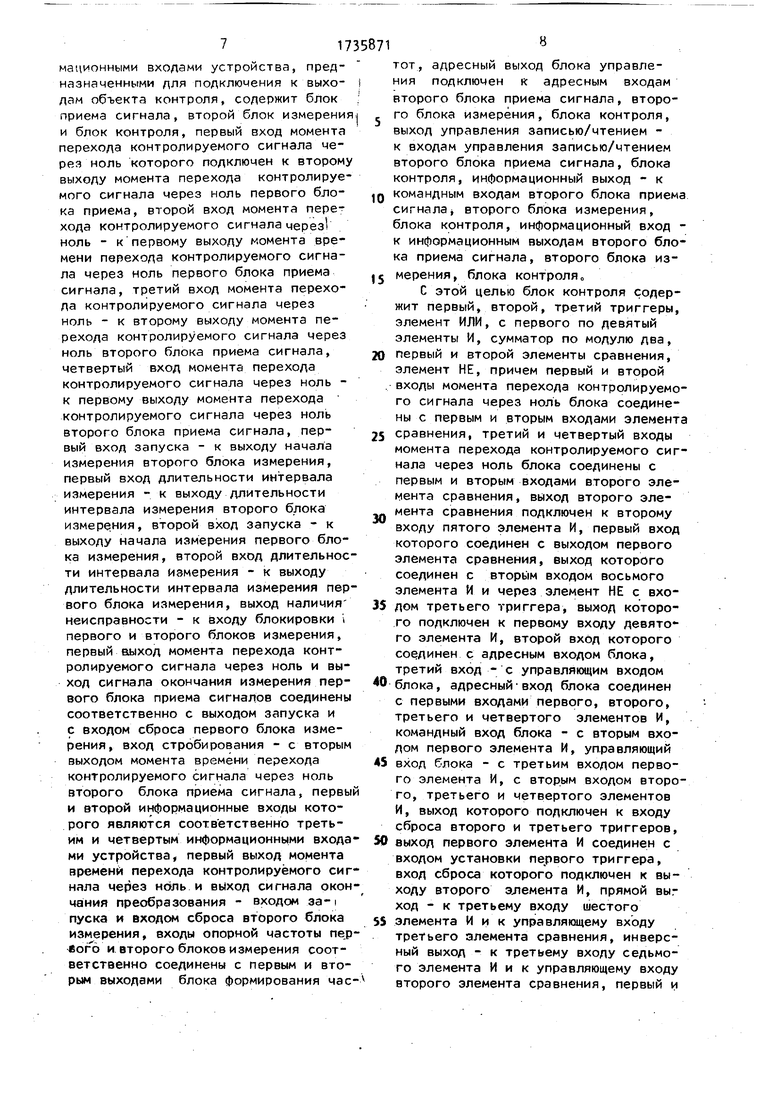

На фиг.1 приведена структурная

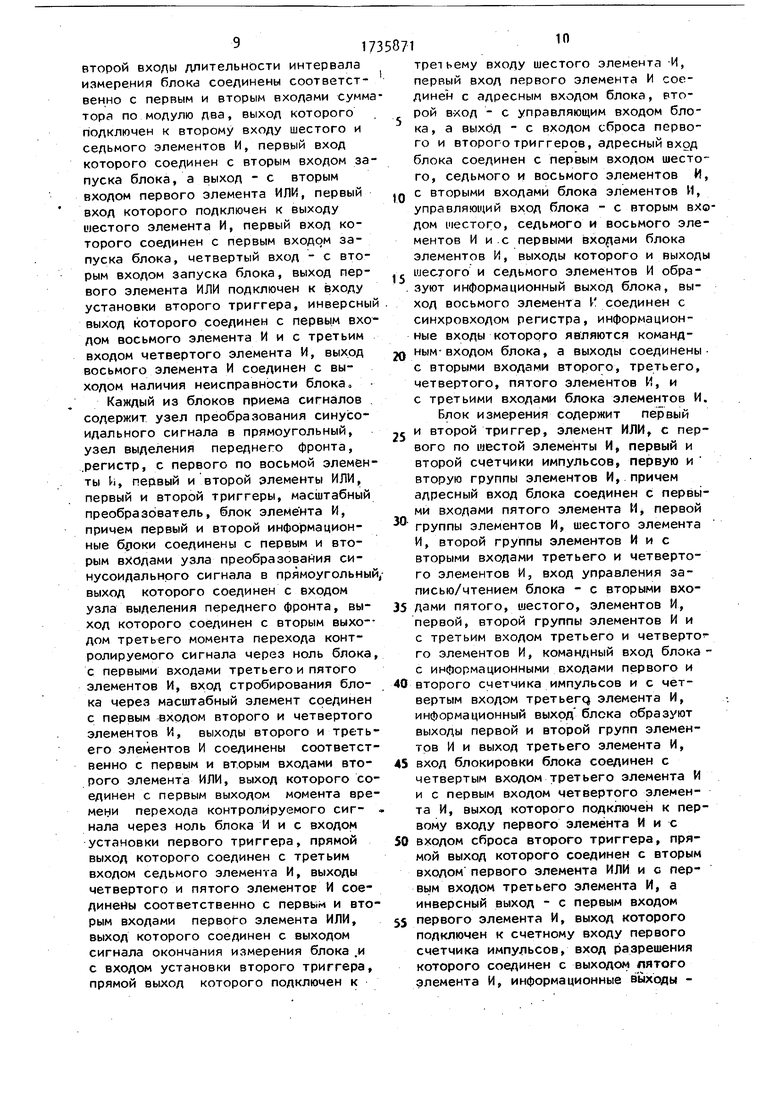

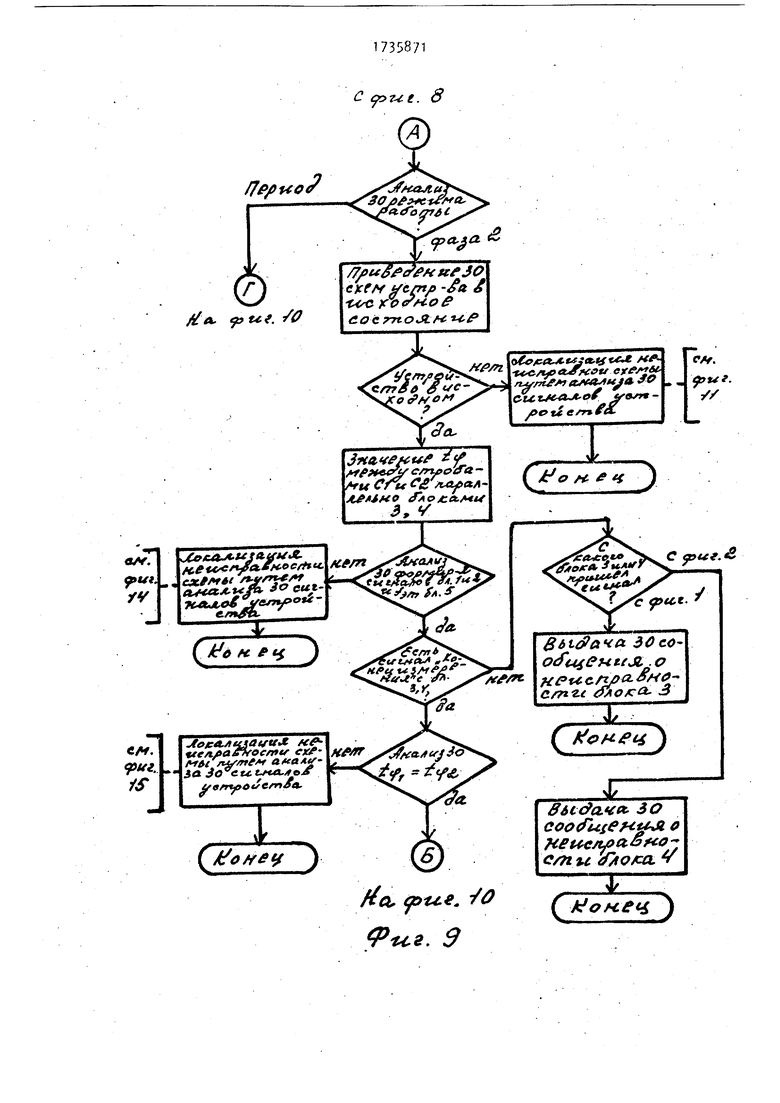

схема устройства; на фиг«2 - схема блока измерения,: на фиг.З - схема блока управления; на фиг„А - схема блока приема сигнала; на фиг.5 временные диаграммы работы устройстве в режиме Фаза на фиг.6 - схема блока контроля; на фиг.7 - временные диаграммы работы устройства в режиме Фаза 2 и Период в части измерения tT; на фиг«8-15 алгоритмы | работы устройства

Устройство (фиГо1) содержит первый блок 1 приема сигнала, второй блок 2 приема сигнала, первый блок 3 измерения, второй блок 4 измерения блок 5 формирования опорных частот, блок 6 управления, блок 7 контроля, входы 8-11 устройства, выход Г2 управления записью/чтением, информационный выход 13, информационный вход 14, адресный выход 15.

Блок 3 измерения (фиг.2) содержит первый триггер 16, элемент ИЛИ 17, первый элемент И 18, второй элемент И 19, первый счетчик 20-импульсов, второй триггер 21, второй счетчик 22 импульсов, третий элемент И 23, четвертый элемент И 2k, пятый элемент И 25, шестой элемент И 26, первую группу элементов И 27, вторую группу элементов И 28.

Блок 6 управления (фиг.З) содержит блок 29 постоянной памяти, процессор 30, блок 31 оперативной памяти, первый дешифратор 32, первый ре25

35871П

гистр 33, панель 34 индикации, панель 35 управления, седьмой элемент И 36, восьмой элемент И 37, девятый элемент И 38, первый переключатель 39, второй переключатель 40, третий переключатель 41.

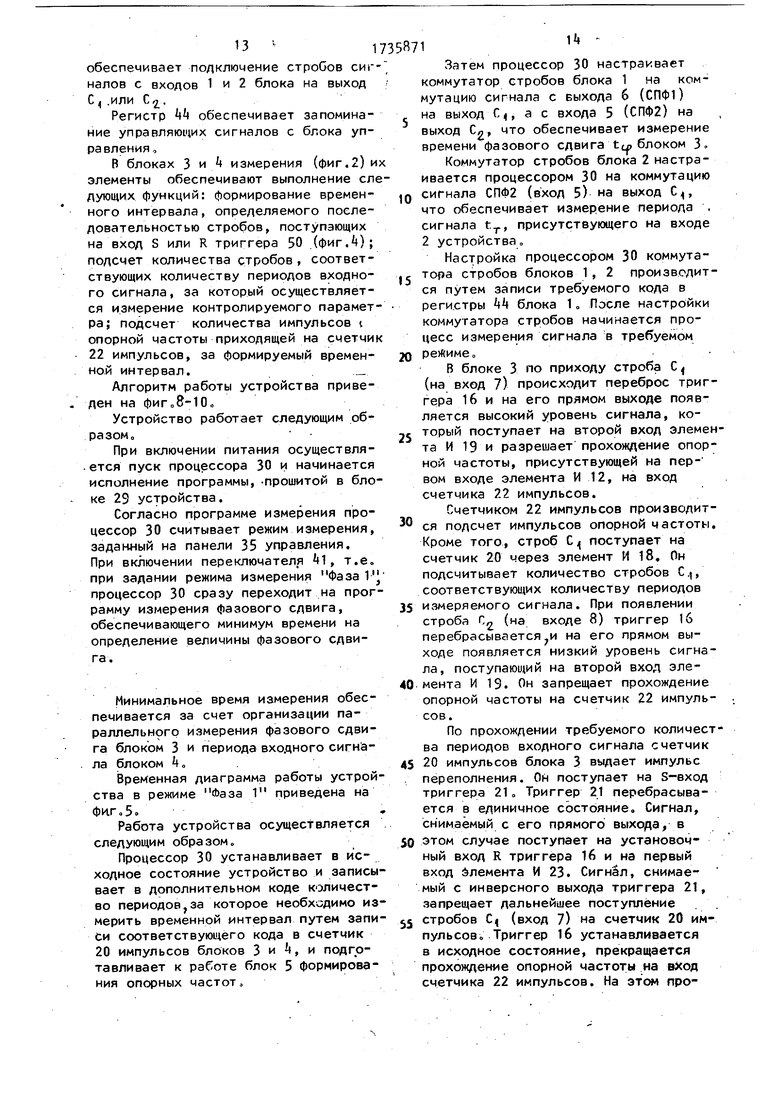

Блок 1 приема сигнала (фиг.4) содержит узел 42 преобразования синуJQ соидального сигнала в прямоугольный, узел 43 выделения переднего фронта, регистр 44, первый элемент И 45, второй элемент И 46, третий элемент И 47, четвертый элемент И 48, пятый

j, элемент И 49, первый триггер 50, первый элемент ИЛИ 51, второй элемент ИЛИ 52, второй триггер 53, шестой элемент И 54, седьмой элемент И 55, масштабный элемент 56, восьмой эле2Q мент И 57, блок элементов И 58.

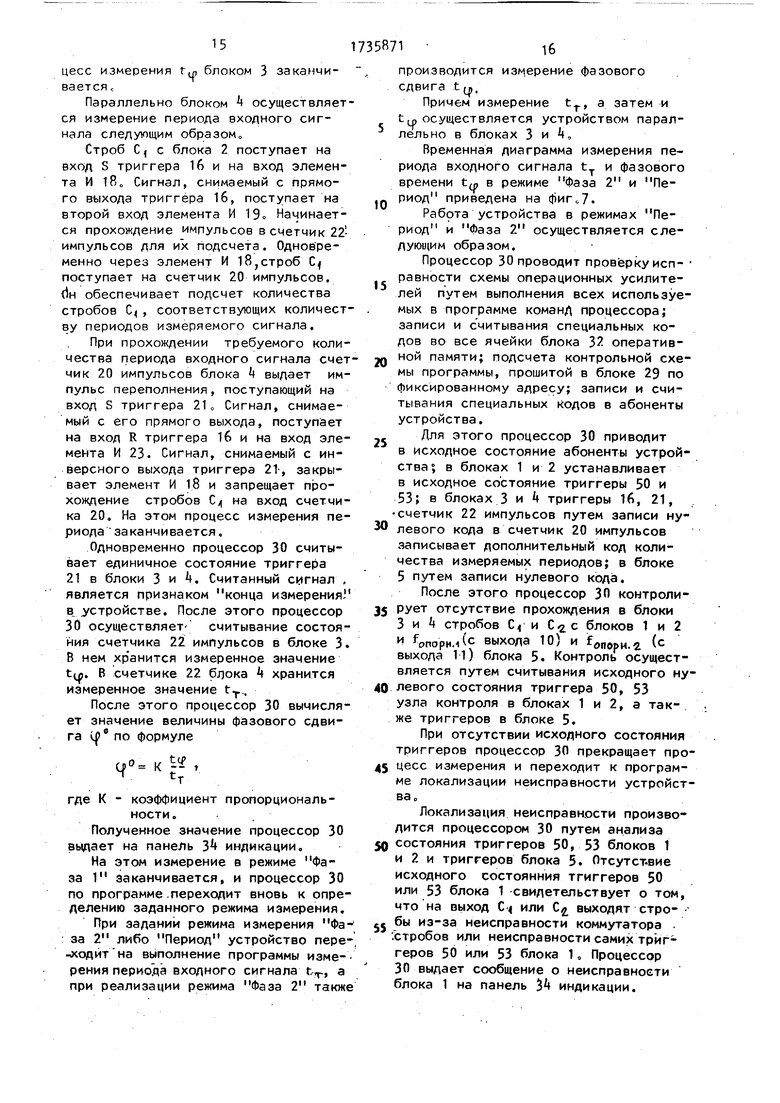

На фиг с 5 представлена временная диаграмма формирования сигналов в контрольных точках устройства во время его функционирования в режиме Фаза 1.

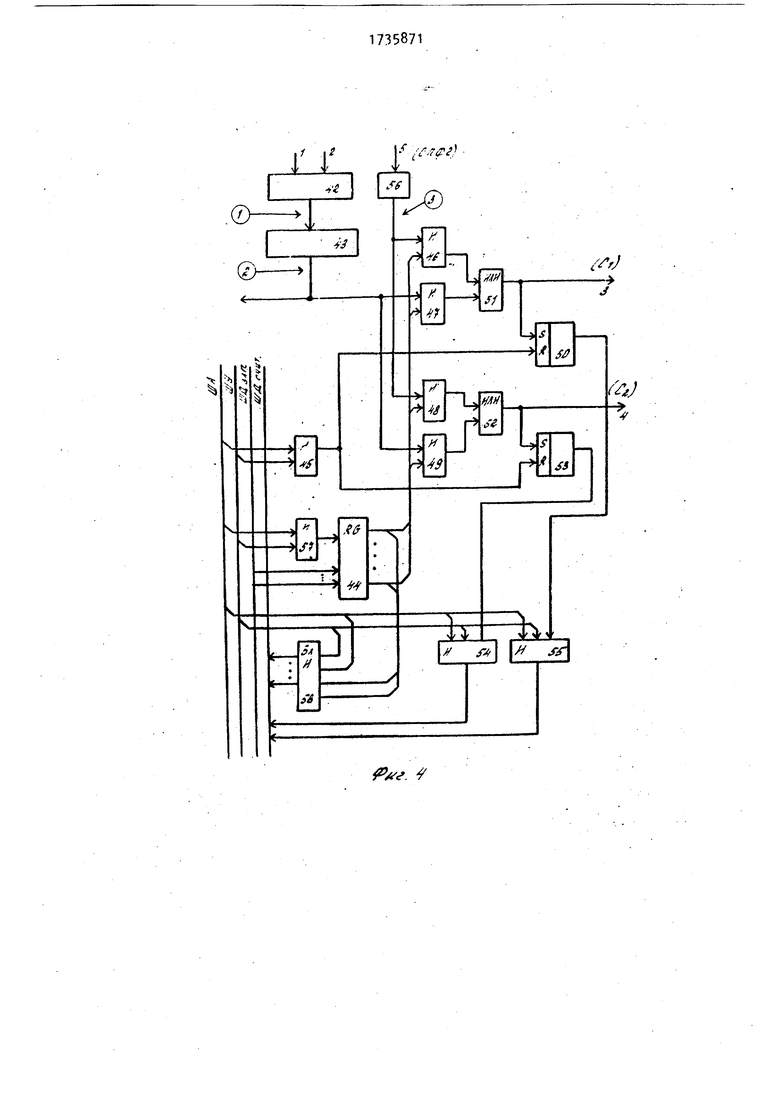

Блок 7 контроля (фиг.6) содержит первый элемент И 59, второй элемент И 60, сумматор 61 по модулю два, первый триггер 62, первый элемент бЗсрав-1 нения, второй элемент 64 сравнения,

™ третий элемент И 65, четвертый элемент И 66, пятый элемент И 67, шестой элемент И 68, седьмой элемент И 69, первый элемент ИЛИ 70, элемент НЕ 71, . второй триггер 72 третий триггер 73,35 восьмой элемент И 74, девятый элемент И 75 о

В блоке 1(2) приема сигнала (фиго4) элементы обеспечивают выполнение следующих функций.

40 Узел 42 обеспечивает прием входного сигнала, сравнение входного сигнала с общим питанием устройства и формирование прямоугольных импульсов с периодом повторения, длитель-.

45 ностью импульса и длительностью паузы соответствующих входному сигналу на нулевом уровне измерения

Узел 43 обеспечивает, согласова- 50 ние по напряжению уровней сигнала

аналоговой и цифровой частей устройства, формирование стробы по переднему фронту сигнала.(СПФ)..

Узел контроля,состоящий из триг- 55 геров 50,53, а также элементов И 54, 55 и 45, обеспечивает контроль выдачи стробов С и Са„

Коммутатор стробов, состоящий из элементов 46-49, ИЛИ 51, 52,

13 v обеспечивает подключение стробов сиг входов 1 и 2 блока на выход

налов с входов 1 и 2 блока на С4 .или С.

Регистр й обеспечивает запоминание управляющих сигналов с блока управления,

В блоках 3 и k измерения (фиг.2) и элементы обеспечивают выполнение слдующих функций: формирование временного интервала, определяемого последовательностью стробов, поступающих на вход S или R триггера 50 (фиг.); подсчет количества стробов , соответствующих количеству периодов входного сигнала, за который осуществляется измерение контролируемого параметра; подсчет количества импульсов i опорной частоты приходящей на счетчи 22 импульсов, за формируемый временной интервал..

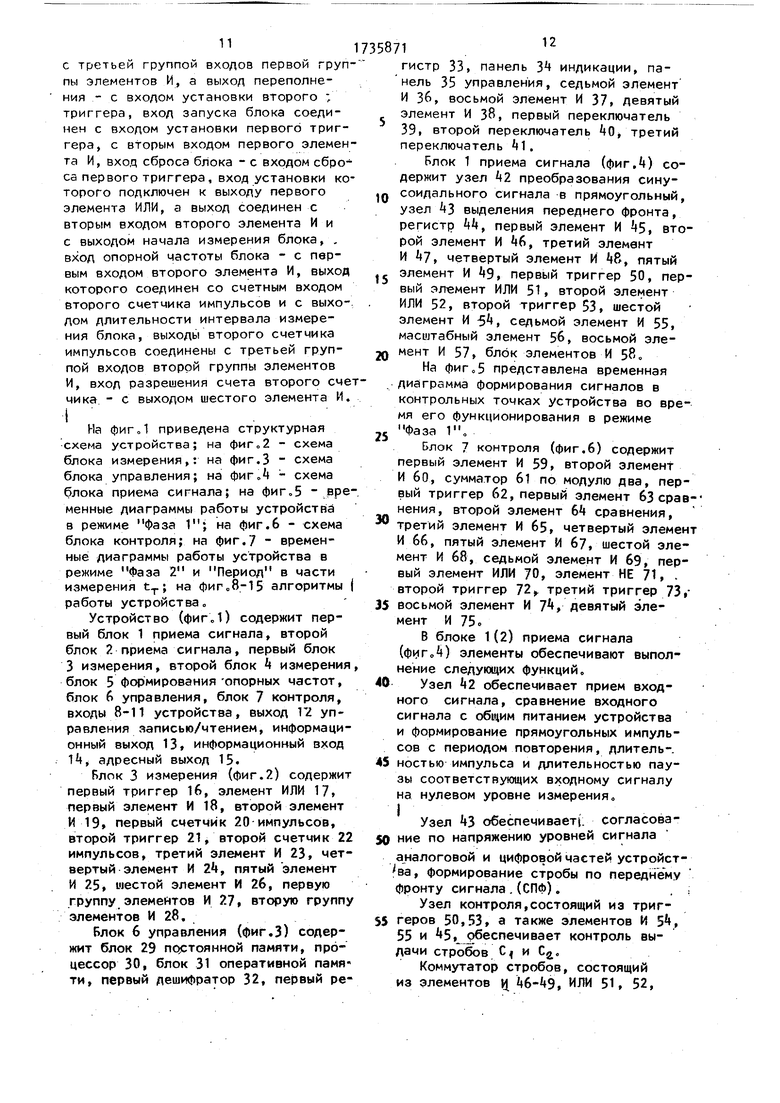

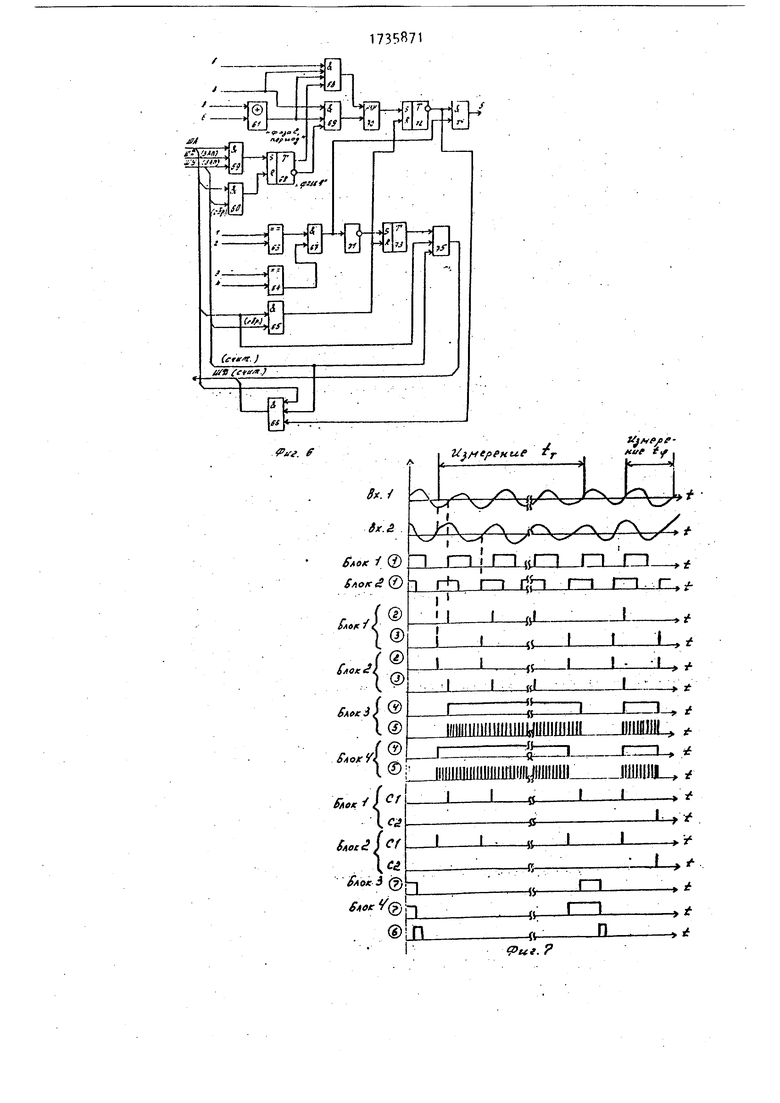

Алгоритм работы устройства приведен на фиг08-10о

Устройство работает следующим образом.

При включении питания осуществля- .ется пуск процессора 30 и начинается исполнение программы, -прошитой в блоке 2S устройства.

Согласно программе измерения процессор 30 считывает режим измерения, заданный на панели 35 управления. При включении переключателя П, т.е. при задании режима измерения Фаза 1 процессор 30 сразу переходит на программу измерения фазового сдвига, обеспечивающего минимум времени на определение величины фазового сдвига.

Минимальное время измерения обеспечивается за счет организации па- раллельн9го измерения фазового сдвига блоком 3 и периода входного сигнала блоком 1+,,

Временная диаграмма работы устройства в режиме Фаза 1 приведена на

фиг о 5.

Работа устройства осуществляется

следующим образом.

Процессор 30 устанавливает в исходное состояние устройство и записывает в дополнительном коде количество периодов,за которое необходимо измерить временной интервал путем записи соответствующего кода в счетчик 20 импульсов блоков 3 и , и подготавливает к работе блок 5 формирования опорных частот,

И

0

5

0

5

Затем процессор 30 настраивает коммутатор стробов блока 1 на коммутацию сигнала с выхода 6 (СПФ1) на выход С«, а с входа 5 (СПФ2) на выход С, что обеспечивает измерение времени фазового сдвига t блоком 3. Коммутатор стробов блока 2 настраивается процессором 30 на коммутацию сигнала СПФ2 (вход 5) на выход С, что обеспечивает измерение периода . сигнала tT, присутствующего на входе 2 устройства.

Настройка процессором 30 коммутатора стробов блоков 1, 2 производится путем записи требуемого кода в регистры й блока 1. После настройки коммутатора стробов начинается процесс измерения сигнала в требуемом режиме.

В блоке 3 по приходу строба С (на вход 7) происходит переброс триггера 16 и на его прямом выходе появляется высокий уровень сигнала, который поступает на второй вход элемента И 19 и разрешает прохождение опорной частоты, присутствующей на первом входе элемента И 12, на вход счетчика 22 импульсов.

Счетчиком 22 импульсов производится подсчет импульсов опорной частоты. Кроме того, строб С,j поступает на счетчик 20 через элемент И 18. Он подсчитывает количество стробов С., соответствующих количеству периодов

5 измеряемого сигнала. При появлении строба С Ј (на входе 8) триггер 16 перебрасывается;и на его прямом выходе появляется низкий уровень сигнала, поступающий на второй вход эле0 мента И 19. Он запрещает прохождение опорной частоты на счетчик 22 импульсов.

По прохождении требуемого количества периодов входного сигнала счетчик

5 20 импульсов блока 3 выдает импульс переполнения. Он поступает на S-вход триггера 21. Триггер 21 перебрасывается в единичное состояние. Сигнал, снимаемый с его прямого выхода, в

0 этом случае поступает на установочный вход R триггера 16 и на первый вход элемента И 23. Сигнал, снимае- мый с инверсного выхода триггера 21, запрещает дальнейшее поступление

5 стробов C (вход 7) на счетчик 20 импульсов. Триггер 16 устанавливается в исходное состояние, прекращается прохождение опорной частоты на вход счетчика 22 импульсов. На этом про0

цесс измерения Гц, блоком 3 заканчивается с

Параллельно блоком Ь осуществляется измерение периода входного сигнала следующим образом

Строб С j с блока 2 поступает на вход S триггера 16 и на вход элемента И 18„ Сигнал, снимаемый с прямого выхода триггера 16, поступает на второй вход элемента И 19° Начинается прохождение импульсов в счетчик 22- импульсов для их подсчета. Одновременно через элемент И 18,строб С поступает на счетчик 20 импульсов. (1н обеспечивает подсчет количества стробов С, соответствующих количеству периодов измеряемого сигнала.

При прохождении требуемого количества периода входного сигнала счетчик 20 импульсов блока выдает импульс переполнения, поступающий на вход S триггера 21„ Сигнал, снимаемый с его прямого выхода, поступает на вход R триггера 16 и на вход элемента И 23. Сигнал, снимаемый с инверсного выхода триггера 21, закрывает элемент И 18 и запрещает прохождение стробов С4 на вход счетчика 20. На этом процесс измерения периода заканчивается.

Одновременно процессор 30 считывает единичное состояние триггера 21 в блоки 3 и 4. Считанный сигнал , является признаком конца измерения, в устройстве. После этого процессор 30 осуществляет считывание состояния счетчика 22 импульсов в блоке 3. В нем хр анится измеренное значение t,. В счетчике 22 блока Ц хранится измеренное значение tT.

После этого процессор 30 вычисляет значение величины фазового сдвига по формуле

Ч

- к ,

где К - коэффициент пропорциональности .

Полученное значение процессор 30 выдает на панель 3k индикации.

На этом измерение в режиме Фаза 1 заканчивается, и процессор 30 по программе переходит вновь к определению заданного режима измерения.

При задании режима измерения Фаза 2 либо Период устройство пере-, -лодит на выполнение программы изме-- рения периода входного сигнала r.., a при реализации режима Фаза 2 также

производится измерение фазового сдвига tq,.

Причем измерение tr, а затем и tц, осуществляется устройством параллельно в блоках 3 и 4,

Временная диаграмма измерения периода входного сигнала tT и фазового времени tg, в режиме Фаза 2 и Пе

риод приведена на фиг0.

5

Работа устройства в режимах Период и Фаза 2 осуществляется следующим образом.

Процессор 30 проводит проверку исп- равности схемы операционных усилителей путем выполнения всех используемых в программе команд процессора; записи и считывания специальных кодов во все ячейки блока 32 оператив- ) ной памяти; подсчета контрольной схемы программы, прошитой в блоке 29 по фиксированному адресу; записи и считывания специальных кодов в абоненты устройства.

Для этого процессор 30 приводит в исходное состояние абоненты устройства; в блоках 1 и 2 устанавливает в исходное состояние триггеры 50 и 53; в блоках 3 и k триггеры 16, 21, счетчик 22 импульсов путем записи ну- 0 левого кода в счетчик 20 импульсов записывает дополнительный код количества измеряемых периодов; в блоке 5 путем записи нулевого кода.

После этого процессор 30 контроли- 5 Рует отсутствие прохождения в блоки 3 и Ц стробов С 4 и С Ј с блоков 1 и 2 и Апории (с выхода 10) и Јоп.г (с выхода 11) блока 5. Контроль осуществляется путем считывания исходного ну- 0 левого состояния триггера 50, 53 узла контроля в блоках 1 и 2, а также триггеров в блоке 5.

При отсутствии исходного состояния триггеров процессор 30 прекращает про- 5 цесс измерения и переходит к программе локализации неисправности устройства

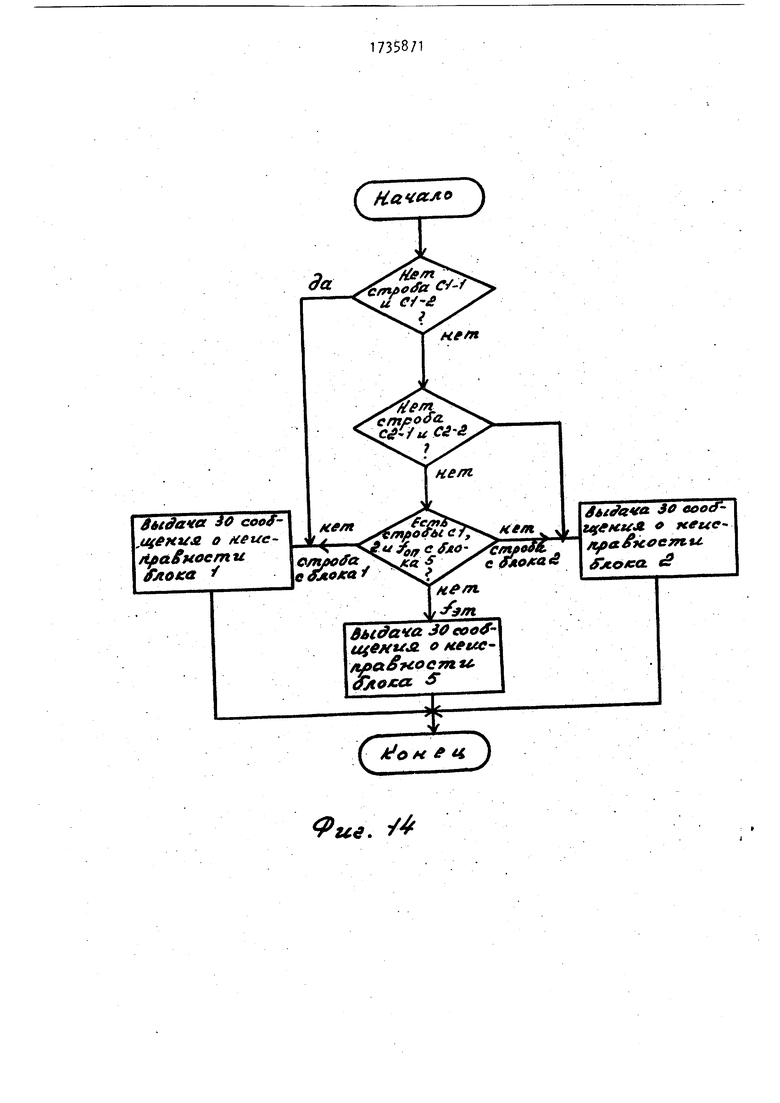

Локализация неисправности производится процессором 30 путем анализа 0 состояния триггеров 50, 53 блоков 1 и 2 и триггеров блока 5. Отсутствие исходного состоянния тгиггеров 50 или 53 блока 1 свидетельствует о том, что на выход С. или С выходят стро- , бы из-за неисправности коммутатора . .стробов или неисправности самих триггеров 50 или 53 блока 1, Процессор 30 выдает сообщение о неисправности блока 1 на панель 3 индикации.

17

Отсутствие исходного состояния триггеров 50, 53 блока 2 свидетельствует о том, что на выход Сц или С2

выходят стробы из-за неисправности коммутатора стробов или неисправности триггеров 50 или 53 блока 2„ Процессор 30 выдает сообщение о неисправности блока 2 на панель индикации.

Об отсутствии исходного состояния триггеров в блоке 5 свидетельствует наличие опорной частоты на его выходах

Алгоритм поиска неисправностей приведен на фиг 011.

При наличии исходного (нулевого) состояния триггеров процессор 30 продолжает реализацию программы измерения, подключая опорную частоту с блока 5 к блоку 3 и А.

После этого процессор 30 осуществляет выдачу строба СПФ1 с блока 1 на выход С и строба СПФ2 с блока 2 на выход СiЗатем процессор 30 проверяет прохождение стробов с блоков 1 и 2, а также опорной частоты с выходов 10 и 11 блока 5 в блоки 3 и 4. Проверка осуществляется путем смачивания единичного состояния с триггеров 50 блоков 1 , 2 и триггеров блока 5 и нулевого состояния с триггеров 53 блоков 1,2. При отсутствии указанного состояния процессор 30 прекращает процесс измерения и переходит на программу локализации неисправности, Локализация неисправности осуществляется процессором 30 путем анализа состояния триггеров 50, 53 блоков 1, 2 и триггеров блока 5. Отсутствие требуемого состояния триггеров 50 {единичное состояние), 53 (нулевое состояние) блока 1 свидетельствует о том, что на выходе Г4 и С выдаются (не выдаются) требуемые в режиме измерения периода стробы передних фронтов (СП) сигналов из-за неисправности блока 1 или неисправности самих триггеров 50 или 53 блока 1. Процессор 30 выдает сообщение о неисправности блока 1 на панель 3 индикации. Отсутствие требуемого состояния триггеров 50 (единичное состояние), 53 (нулевое состояние) блока 2 свидетельствует о таких же неисправностях, как описано в блоке 2. О наличии неисправности в блоке 5 будет свидетельствовать1 отсутствие наличия опорной частоты на одном из его выходов.

1

5

73587118

Алгоритм поиска неисправностей в устройстве представлен на фиг.12. При наличии указанного состояния процессор 30 продолжает выполнение программы измерения времени периода входных сигналов0 Процесс измерения времени периода блоками 3 h аналогичен измерению времени периода сигнала JQ блоком в режиме Фаза 1м.

Затем процессор 30 осуществляет повторное измерение времени периода в блоках 3 и k аналогично описанному

5

0

0

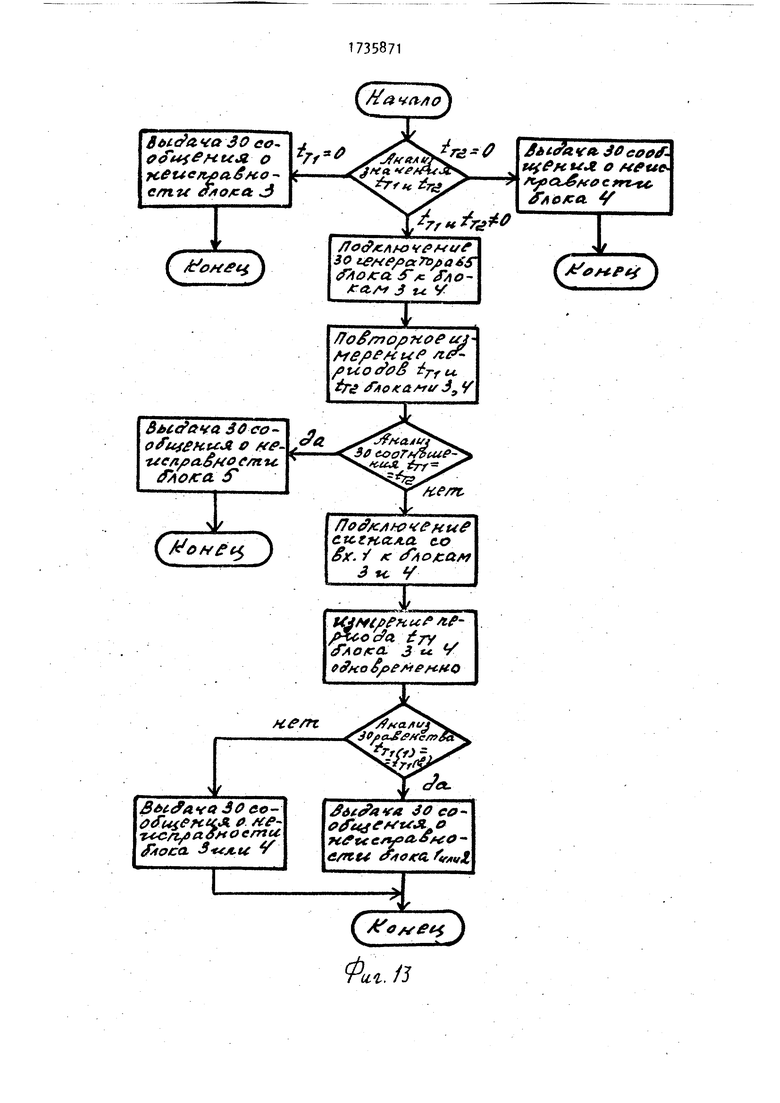

и производит сравнение значений полученных результатов и -ту . Равенство значений t{ и t r свидетельствует о том, что относительная нестабильность опорной частоты одного блока 5 ушла за допускаемые пределы из-за его неисправности.

В случае повторного неравенства значений t-r и tT процессор 30 организует измерение времени периода tT одновременно двумя блоками 3 и k с

5 целью нахождения неисправностей в блоках 3 и или 1 и 2„

Отключение СПФ2 от выхода С5 блока 2 осуществляется путем подачи сигнала низкого уровня на второй вход элемента 7 и подачей сигнала высокого уровня на второй вход элемента И kf путем записи процессором 30 соответствующего кода в регистр № блока 1.

Затем процессор 30 осуществляет

5 в третий раз измерение временного периода tTl одновременно в блоках 3 и аналогично описанному и проводят сравнение значений полученных результатов.,

Одновременно процессор 30 осуществляет считывание состояния сигнала Конец измерения с блоков 3 и 4 через элемент И 23 При отсутствии от одной из схем сигнала Конец измере5 ния процессор 30 прекращает процесс измерения и локализует неисправный блок 3 и Ц в зависимости от того, от какого блока не поступил сигнал. При наличии сигналов Конец изме0 рений с блоков 3 и k процессор 30 производит считывание результатов измерения со счетчиков 22 блока 3 t-j- и блока tTn и записывает их в блок

0

31

тг

55 Затем процессор 30 сравнивает их значения по формуле

ч, + «VGT /ст -tTЈ/,

(о

19

1735Я71

t (

-г(т2

где о - максимально допустимое значение величины отно сительной погрешности опорной частоты генера торов в блоке 5; - величина кванта опорной частоты;

время периода, измеренное устройством. При невыполнении соотношения (1)

процессор 30 прекращает процесс измерения и переходит на программу локализации неисправности.

Локализация неисправности производится процессором 30 путем анализа результатов измерения на равенство их нулю Нулебое значение времени периода tT свидетельствует о неисправности блока 3° Процессор 30 выдает сообщение на индикацию о неисправности блока 3

Нулевое значение времени периода

г

свидетельствует о неисправности

блока 4„ Процессор 30 выдает соотношение о неисправности блока 4.

Если же значение tT Ј стл/ ° то одной из возможных причин возникновения данного соотношения является уход за допускаемые пределы значения относительной неисправности опорной частоты одного из генераторов блока 5 из-за их неисправности.

Для выявления неисправности в блоке 5 процессор 26 организует повтор - ное измерение времени периода блоками 3 и k с подачей одной и той же опорной.частоты на оба блока 3 и Ц,

Равенство полученных значений tTl свидетельствует о правильной работе блоков 3 и 4, одинаково измеряющих один и тот же период и наличие неисправности в одной из схем 1 или 2. Процессор 30 выдает сообщение о неисправности блока 1 либо 2.

Неравенство значений tTl( свидетельствует о неисправности в блоке 3 либо 4.

Алгоритм поиска неисправности в устройстве приведен на фиг.13.

В противном случае процессор 30 продолжает измерение контрольного параметра, вычисляя устраненное значение времени периода по формуле

t... 2)

-т,

т

После этого процессор 30 анализирует режим измерения, заданный переЯ71

20

ключателями , и в случае задания режима Период выдает значения tr на панель 3 индикации, используя запись значения tT в регистр 33 (предполагается, что в режиме Пери- измеряемый сигнал подключен к обо0

од1

им входам),

При задании режима измерения Фаза . процессор Зп переходит к измерению времени фазового сдвига tfn между сигналами, присутствующими

5

0

5

0

р между сигналами, на его входах.

Процессор 30 приводит в исходное состояние блоки устройства и осуществляет анализ его исходного состояния аналогично тому, как Зто производится перёд измерением периода. При отсутствии исходного состояния триггера процессор 30 прекращает процесс измерения и переходит к программе локализации неисправности с точностью до блока„

Локализация неисправности производится процессором 30 путем анализа состояния триггеров 50, 53 блоков 1, 2 и триггеров блока 5. Отсутствие исходного состояния триггеров 50 либо 53 блока 1 свидетельствует о том, что на выход С, либо С поступают стробы СПФ из-за неисправности коммутатора стробов либо неисправны сами триггеры 50 или 53 блока 1.

Отсутствие исходного состояния триггеров 50, 53 блока 2 свидетельствует о том, что на выход С либо Сг. поступают стробы СПФ из-за неисправности коммутатора стробов либо неисправности триггеров 50 или -53 блока 2. Процессор 30 выдает сообщение о неисправности блока 2 на панель 3 индикации.

Об отсутствии исходного состояния блока 5 будет свидетельствовать то, что на его выходе имеется опорная частота.

Алгоритм поиска неисправности в устройстве приведен на фиг.14.

При наличии исходного состояния процессор 30 продолжает программу 50 измерения,подключая опорную частоту с выхода 10 блока 5 к блоку 3, опорную частоту с выхода 11 блока 5 к блоку 4 аналогично описанному.

После этого процессор 30 осущест- 55 вляет выдачу строба с блока 1 и в блоке 2 на выход С и строба СПФ2 в блоках 1 и 2 на выход С. Затем процессор 30 проверяет прохожде- ние стробов С и GЈ с блоков 1 и 2

5

0

4S

и опорной частоты с выходов 10 и 11 блока 5 в блоки 3 и k путем считывания единичного состояния с триггеров этих блоков,

При отсутствии указанного состояния процессор 30 прекращает процесс измерения и переходит на программу локализации неисправности.

Локализация неисправности производится процессором 30 путем анализа состояния триггеров в блоках 1, 2 и 5 о Одновременное отсутствие требуемого единичного состояния триггеров 50 в блоке 1 и 2 свидетельствует о неисправности приемных элементов либо формирователя стробов в блоке 1, так как строб , формируемый блоком 1, программируется при измерении t (n одновременно на выходы С блоков 1 и 2.

Одновременное отсутствие требуемого единичного состояния триггеров. 53 в блоках 1 и 2 свидетельствует о неисправности приемных элементов либо формирователя стробов в блоке 2, так как строб СПФ2, формируемый блоком 2, программируется при измерении ty одновременно на выходы С2 блоков 1 и 2.

Одновременное отсутствие требуемого единичного состояния триггеров 5 в блоках 1 и 2 свидетельствует о неисправности приемных элементов либо формирователя стробов в блоке 2, так как строб СПФ2,формируемый блоком 2, программируется при измерении tq, одновременно на выходы С2 блоков 1 и 2 о

Отсутствие единичного состояния одного из триггеров 50, 53 блока 1 при единичном состоянии этих триггеров в блоке 2 свидетельствует о наличии неисправности в блоке 1.

Отсутствие единичного состояния в одном из триггеров 50 либо 53 блока 2 при единичном состоянии аналогичных триггеров в блоке 1 свиде- тельствует о неисправности блока 2.

Отсутствие единичного состояния триггеров в блоке 5 свидетельствует об отсутствии опорной частоты на одном из выходов блока 5.

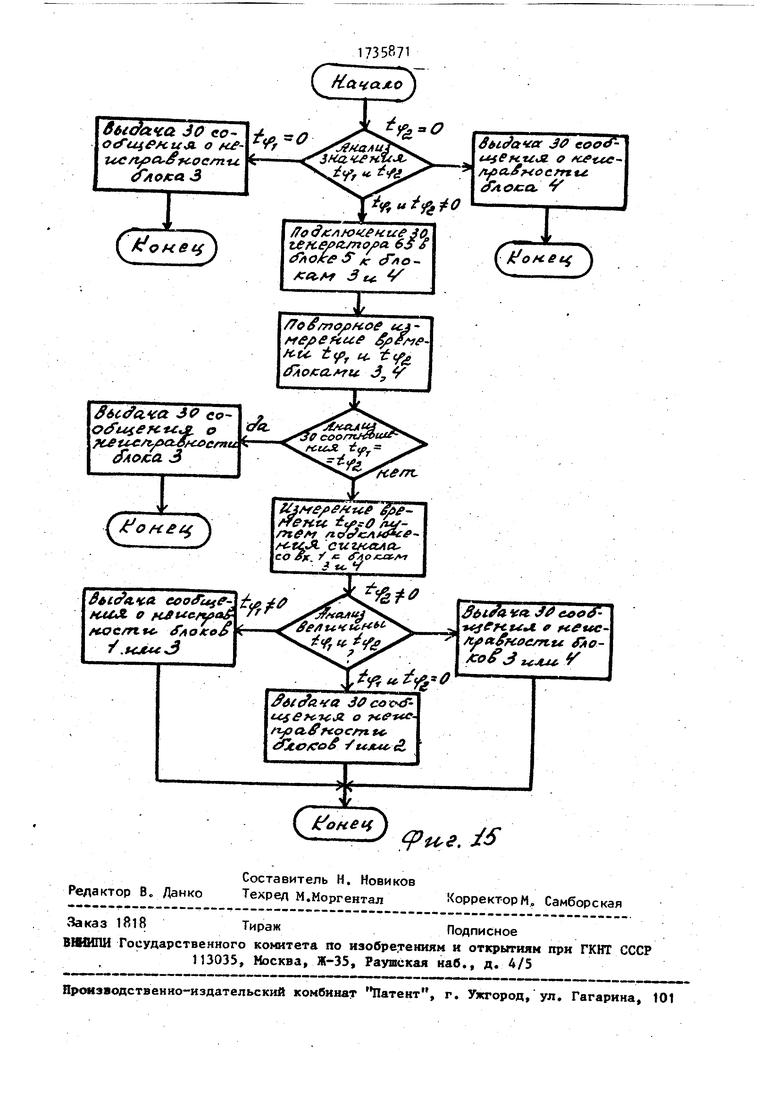

Алгоритм поиска неисправности в устройстве приведен на .

При наличии указанного состояния процессор 30 продолжает выполнение программы измерения фазового времени входных сигналов.

5

Процесс измерения фазового поеме-. ни блоками 3 и 4 аналогичен измерению фазового времени блоком 3 в режиме Лаза 1.

Одновременно процессор 30 осуществляет считывание состояния сигнала Конец измерения с блоков 3, через элемент И 23. При отсутствии

п у одной из схем сигнала Конец измерения процессор 30 прекращает про- цесс измерения и локализует неисправный блок 3 или k в зависимости от того, откуда не поступил сигнал, и вы/Тает сообщение на панель Jk индикации о неисправном блоке.

При наличии сигнала Конец измерения процессор 30 производит считывание состояния счетчиков 22 блоков

0 3, Ь и запоминает измеренные значения и ty, в блоке 31 оперативной памяти.

Затем процессор 30 производит сравнение полученных результатов по

5 Формуле

(tq,, +tyz)tf + 4 /tg,, ,

где С - максимально допустимое значение величины 0относительной погрешности опорной частоты, формируемой в блоке 5; ci - величина кванта опорной частоты, формируе- 5мой блоком 5;

tyj и - величины фазового времени, измеряемого устройством,

При невыполнении соотношения (3) 0 процессор 30 прекращает процесс измерения и переходит на программу локализации неисправности,

Локализация неисправности проводится процессором 30 путем анализа ре- 5 зультатов измерения на равенство их нулевому значению. Нулевое значение фазового времени tq( свидетельствует о неисправности блока 3.

Нулевое значение фазового време- 0 ни свидетельствует о неисправности блока k,

Если же значение tq О, то одной из наиболее вероятных причин наличия данного соотношения яв- ляется уход за допустимые пределы значения относительной нестабильности опорной частоты одного из генераторов блока 5 из-за возникновения неисправности. Для определения технического состояния блока 5 процессо 26 организует повторное измерение фазового времени ( ) блоками 3 и ч с подачей одной и той же опорной частоты на оба блока 3 и ч, Для подключения опорной частоты с выхода 10 блока 5 к блоку k процессор 30 осуществляет вначале отключение опорной частоты с выхода 11 блока 5 от блока ч.

После этого процессор 30 осуществляет повторное измерение фазового времени блоками 3 и k аналогично описанному и производит сравнение значений полученных результатов и t.

Равенство значений свидетельствует о том, что относительная нестабильность опорной частоты одного из генераторов блока 5 вышла за допустимые пределы

Затем процессор 30 осуществляет повторное измерение фазового времени блоками 3 и k аналогично описанному и производит сравнение значений полученных результатов tu и . Равенство значений свидетельствует о том, что относительная нестабильность опорной частоты одного из генераторов блока 5 вышла за допустимые пределы.

В случае повторного неравенства значений t(j, и процессор 30 организует измерение блоками 3 и ч фазо,- вого времени t - 0 путем одновременной подачи строба СПФ1 блока 3 на выходе С и С2 блока 1 и строба блока 2 на выходы С и С блока 2.

Затем процессор 26 осуществляет измерение фазового времени tq О в блоках 3 и k аналогично описанному и производит анализ результатов полученных значений t y и измеренных блоками 3 и ч.

Значение tq И 0 (при 0) свидетельствует о том, что либо в результате неисправности в блоке 1 не формируется фазовое время t(( 0 либо в результате неисправности в блоке 3 фазовое время t{« 0, поступающее на вход блока 3 с блока 1, измеряется неправильно. Процессор 30 выдает сообщение о неисправности блока 1 или 3.„

Значение t Ј 0 (при- t, О свидетельствует о том, что или в результате неисправности в блоке k не формируется фазовое время О

или в результате неисправности в блоке k фазовое время t 0, поступающее на вход блока k с блока 2, измеряется неправильное Процессор 30 выдает сообщение о неисправности блока

5

или ч„ В случае, если t О и ty 0, то это свидетельствует о том, что элемент И ч8 блока 1 или элемент И чб блока 2 искажает временные соотношения между стробами СПФ1 и во время измерения фазового времени t и ,

Алгоритм поиска неисправности представлен на фиг.15При выполнении неравенства (3) процессор 30 продолжает выполнение программы измерения и вычисляет i величину фазового сдвига по формуле

0

Ч

к

tq, + t

2t.

5

где t

- величины фазового сдвига измеренные со5

0

ответственно блоками 3 и ч;

tT - величина времени периода, измеренная ранее 0и хранящаяся в блоке 31;

К - коэффициент пропорциональности.

Затем процессор 30 выдает результат измерения на панель Зч индикации. Блок 7 контроля обеспечивает функциональное диагностирование блоков 1 и 2„ В данном случае в соответствии с временной диаграммой, представленной на фиг.5 и 7 в каждый момент времени сигналы на выходе 2 блока 1 и выходе 3 блока 2 (и наоборот) должны совпадать. Контроль осуществляется с помощью элементов 63 и 6ч совпадения. Если возникает несовпадение сигналов на этих элементах, то осуществляется переброс в единичное состояние триггера 73 и одновременно на выходе 5 блока 7 формируется сигнал, эквивалентный логическому нулю. Этот сигнал закрывает элементы И 23, 2ч в блоках 3 и ч. При функционировании устройства в режиме Фаза 1 триггер 62 должен находиться в исходном (нулевом)состоянии. Это 5 обеспечивает контроль наличия инфорч мации в 5-й контрольной точке блоков 3 и ч. Контроль осуществляется в моменты времени, когда триггер 16

S

0

25

в блоке 3 накопится в единичном состоянии. При функционировании в режиме Лаза 2, Период триггер 62 переводится в единичное состояние и контроль информации в контроль- ной точке блоков 3 и k осуществляется в тот момент времени, когда триггер 16 в блоке находится в единичном состоянии Если сигналы,поступающие на вход 9 и 7 блока 7 контроля не будут совпадать, то триггер 72 перебросится в единичное состояние и сформирует на выходе блока 7 сигнал, эквивалентный логическому нулю. Перед проведением контроля каждого параметра процессор 30 опрашивает состояние триггеров 72 и 73 с помощью элементов И 66 и 7. В случа нахождения их в единичном состоянии процессор 30 выдает сообщение на панель 30 индикации.

Предлагаемое устройство обеспечивает:

повышение достоверности вычисления результатов измерений на величину, пропорциональную вероятности отклонения от допустимых значений опорной частоты блока 5, обеспечивающих требуемую точность контроля параметров в режимах измерения Фаза 21Г и Период ;

повышение достоверности- функционирования устройства на величину, пропорциональную вероятности возникновения неисправности в элементах, функционирующих в режиме измерения Фаза 2 и Период ;

повышение контролепригодности устройства за счет автоматического перехода на программу локализации неисправности (при ее появлении) с использованием измеряемых сигналов на выходе устройства в качестве тестовых при измерении в режимах Фаза 2 и Период ;

сокращение времени измерения величины фазового сдвига в режиме Фаза 1 за счет одновременного измерения устройством периода и фазового времени в блоках 3 и соответственно;

повышение достоверности функционирования устройства за счет контроля в реальном масштабе времени функционирования блоков приема сигналов и элементов блоков формирования и измерения о

е

to

15

25

26

Формула изобретения)

1, Устройство для контроля параметров , содержащее первый блок приема сигнала, первый блок измерения, блок формирования опорных частот и блок управления, адресный выход которого соединен с адресными входами первого блока приема сигнала, первого блока изме- рения и блока формирования опорных частот, выход управления записью/чтением - с входом управления записью/ /чт ёнием первого блока приема сигнала, первого блока измерения, блока Формирования опорных частот, информационный выход - с командными входами первого блока приема сигнала, перво- 2Q го блока измерения, блока формирова- ния опорных частот, информационный вход - с информационными выходами первого блока приема сигнала, первого блока измерения, блока формирования опорных частот, первый и второй информационные входы первого блока . приема сигнала являются соответственно первым и вторым информационными . входами устройства, предназначенными для подключения к выходам объекта контроля, отличающееся тем, что, с целью повышения полноты контроля, в него введены второй блок приема сигнала, второй блок измерения и блок контроля, первый вход момента перехода контролируемого сигнала через ноль которого подключен к второму выходу момента перехода контролируемого сигнала через ноль первого блока приема, второй вход момента перехода контролируемого сигнала через ноль - к первому выходу момента времени перехода контролируемого сигнала через ноль первого блока приема сигнала, третий вход момента перехода контролируемого сигнала через ноль - к второму выходу момента перехода контролируемого сигнала через ноль второго блока приёма сигнала, четвертый вход момента перехода контролируемого сигнала через ноль - к первому выходу момента перехода контролируемого сигнала через ноль второго блока приема сигнала, первый вход запуска - к выходу начала измерения второго блока измерения, первый вход длительности интервала измерения - к выходу длительности интервала измерения второго блока измерения, второй вход за30

35

40

45

50

SS

пуска - к выходу начала измерения первого блока измерения, второй вход длительности интервала измерения - к выходу длительности интервала измерения первого блока измерения, выход наличия неисправности - к входу блокировки; первого и второго блоков измерения, первый выход момента перехода контролируемого сигнала через ноль и выход сигнала окончания измерения первого блока приема сигналов соединены соответственно с выходом запуска и с входом сброса первого блока измерения, вход стробиро- вания - с вторым выходом момента времени перехода контролируемого сигнала через ноль второго блока приема сигнала, первый и второй информационные входы которого являются соответственно третьим и четвертым информационными входами устройства, первый выход момента времени перехода контролируемого сигнала через ноль и выход сигнала окончания преобразования - с входом запуска и. входом сброса второго блока измерения, входы опорной частоты первого и второго блоков измерения соответственно соединены с первым и вторым выходами блока формирования частот, адресный выход блока управления подключен к адресным входам второго блока приема сигнала, второго блока измерения, блока контроля, выход управления записью/чтением - к входам управления записью/чтением второго блока сигналов, блока контроля, информационный выход - к командным входам второго блока приема сигнала, второго блока измерения, блока контроля, информационный вход - к информационным выходам второго блока приема сигнала, второго блока измерения и блока контроля.

. о Устройство поп.1,отлича- ю ui e e с я тем, что блок контроля содержит первый, второй, третий триггеры, элемент ИЛИ, с первого по девятый элементы И, сумматор по модулю два, первый, второй элементы сравнения, элемент НЕ, причем первый и второй входы момента перехода контролируемого сигнала через ноль блока соединены с первым и вторым входами элемента сравнения, третий и четвертый входы момента перехода контролируемого сигнала через ноль блока соединены с первым и вторым входами второго элемента сравнения, выход

второго элемента сравнения подключен к второму входу пятого элемента И, первый вход которого соединен с вы, холом первого элемента сравнения, выход которого соединен с вторым входом восьмого элемента И и через элемент НЕ соединен с входом третьего триггера, выход которого подклюЮ чен к первому входу девятого элемента И, второй вход которого соединен с адресным входом блока, третий вход - с управляющим входом блока, адресный вход блока соединен с пер15 выми входами первого, второго и третьего и четвертого элементов И, командный вход блока соединен с вто- рым входом-первого элемента И, управляющий вход блока соединен с

20 третьим выходом первого элемента И, с вторым входом второго,третьего и четвертого элементов И, выход которого подключен к входу сброса второго и третьего триггера, выход первого

25 элемента И соединен с входом установки первого триггера, вход сброса которого подключен к выходу второго элемента И, прямой выход - к третьему входу шестого элемента И и к упJQ равляющему входу третьего элемента сравнения, инверсный выход - к третьему входу седьмого элемента И и к управляющему входу второго элемента сравнения, первый и второй входы длительности интервала измере-

35 ния блока соединены соответственно с первым и вторым входами сумматора по модулю два, выход которого подключен к второму входу шестого и седьмого элементов И, первый вход которого соединен с вторым входом запуска блока, а выход - с вторым входом первого элемента ИЛИ, первый вход которого подключен к выходу шестого элемента И, первый вход

которого соединен с первым входом запуска блока, четвертый вход - с вторым входом запуска блока, выход первого элемента ИЛИ подключен к входу установки второго триггера, инверсный выход которого соединен с первым входом восьмого элемента И и с третьим входом четвертого элемента И, выход, восьмого элемента И соединен с выходом наличия неисп55 равности блока.

40

50

29

блоков приема сигнала содержит узел преобразования синусоидального сигна- ла в прямоугольный, узел выделения переднего фронта, регистр, с первого

по восьмой элементы И, первый и вто- рой элементы ИЛИ, первый и второй триггеры, масштабный элемент, блок элементов И, причем первый и второй информационные входы блока соединены с первым и вторым входами узла преобразования синусоидального сигнала в прямоугольный, выход которого соединен с входом узла выделения переднего фронта, выход которого соединен-с вторым выходом третьего момента перехода контролируемого сигнала через ноль блока,с первыми входами третьего и пятого элементов И, вход стробирования блока через масштабные элементы соединен с первым входом второго и четвертого элементов И, выходы второго и третьего элементов И соединены соответственно с первым входом второго

элемента ИЛИ, выход которого соединен с первым выходом момента времени перехода контролируемого сигнала через ноль блока элементов И, с вхо- дом установки первого триггера, прямой вЪ|ход которого соединен с третьим входом седьмого элемента И, выходы четвертого и пятого элементов И соединены соответственно с первым вторым входами первого элемента ИЛИ выход которого соединен с выходом

сигнала окончания измерения блока i

и с входом установки второго триггера, прямой выход которого подключен к третьему входу шестого элемента И, первый вход первого элемента И соединен с адресным входом блока, а второй вход - с управляющим входом блока, а выход - с входами сброса первого и второго триггеров, адресный вход блока соединен с первыми входами шестого, седьмого и восьмого элементов И, с вторыми входами блока элементов И, управляющий вход блока соединен с вторыми входами шестого, седьмого и восьмого элементов И и с первыми входами блока элементов И, выходы которого и выходы шестого и седьмого элементов И обра зуют информационный выход блока, выход восьмого элемента И соединен с синхровходом регистра, информационные входы которого являются команд735 71

зо

ным входом блока, а выходы соединены с вторыми входами второго, третьего, четвертого, пятого элементов И и с третьими входами блока элементов И.

А„ Устройство поп.1,отлича ю щ е е с я тем, что блок измерения содержит первый и второй триггеры,

JQ элемент ИЛИ, с первого по шестой элементы И, первый и второй счетчики импульсов и первую и вторую группы элементов И, причем адресный вход блока соединен с первыми входами пя.с того элемента И, первой группы элементов И, шестого элемента И, второй группы элементов И и с вторыми входами третьего и четвертого элементов И, вход управления записью/чте20 нием блока соединен с вторыми входами пятого, шестого элементов И, второй группы элементов И и с третьим входом третьего и четвертого элементов И, командный вход блока соединен

25 с информационными входами первого и второго счетчика импульсов и с четвертым входом третьего элемента И, информационный выход блока обра-1- зуют выходы первой, второй группы элементов И и выход третьего элемента И, вход блокировки блока соединен с четвертым входом третьего элемента И и с первым входом четвертого элемента И, выход которого подключен к первому входу первого элемента И и с входом сброса второго триггера , прямой выход которого соединен с вторым входом элемента ИЛИ и с первым входом третьего элемента И, а инверсный выход соединен с первым входом первого элемента И, выход которого подключен к счетному входу первого счетчика импульсов, вход разрешения счета которого соединен с выходом пятого элемента И, информационные выходы - с третьей группой входов первой группы элементов И, а выход переполнения - с входом установки второго триггера, вход за-- пуска блока соединен с входом установки первого триггера и с вторым входом первого элемента И, вход сброса блока соединен с входом сброса первого триггера, вход установки которого подключен к выходу первого

$5 элемента ИЛИ, а выход - с вторым входом второго элемента И и с выходом начала измерения блока, вход опорной частоты блока соединен с

30

35

40

4S

50

/1а.к.елй I

. 3

% %.

V.

© ®

Jkww Л

Ј

7 :#Ј0я 1/7Ј 0р jsrj W jwy

W&S#flfoS;ffjrj J0

ff -/V Sfffrf ff&syji Sl

-sw уяРягуя р

( fr #r#/y

jy&VfffdKV f

0р#елгяя& AvttfPv

2%Wrf 0 &A p& /& yjrJr#Fjrs-J /i ff/

(

nr

C rf t,Y re V4 Ј Cfc4

f&t /rr jrj S& JSKySt/fry

Jp&SJVff &V/ffirrJbt & S

Opj fx swj #wtfa

jpfff

лыг ,

JJHryiTZt J &S Jf&S/ ffiJWjf

SfVr SSS

- faoSbbt Јtjir c f

en.

9

л

Q

(ОУУЬЪ}/ }

LV&L

jr. ягег/

#ZfSfS# 2S

0 -/SPStff

( )

E

f #f0rf

S Jg/rp

S/V/f

JTJ SMjA Si/f -J,

-t WffSf f#W Wf W / 7-ir fb .

9

л

Q /

I

00 1.Л гчл

г4

ч

b

Ч

и

С

§

4

Q

5|5а « Й

i

$

5t

S

Ъ tv

5«

$ V C5 J h.4

i§

§

4i

i:

&

« Л в $

в

14 L v

i4

vS

N u

s

21 П

Pi

5ч

5чу F

l ййа4

i

я

.54 5

&Ч

1

©

r- oc

IA РЛ

r-

« 0 Оч

J

л

и

/-

Г

-d

V

Л 00 -J

L

/7оЈ/7гО/Ж0& &J

ме/}Јми/ ЯР- pu. fa 4 лол:лм&39 У

Bbterava 30 со- ofusЈH.tЈA о fff- tec/i/ A.&/40 f/n u. 0лол:& f

j

flofa/iH «екме с.гсгка.А.а с.о Ј. / xr f о хам Зъ У

кумрекиглр/Д ос а try . з « У е#но

хе/п

Ј&tЈa A J0 с0- к#ъс cfyeu - л/rtu 0 o :titir vi,

Фш. Я

//a va-/t0j

L

stem.

1

J

со

LA СЛ

Г««

«и 3

Q

06tcfeva 30 О НЈ

i4 Crtj e Ј H-ocrn -и. Гло/:а 3

.нЛ.й.|

ffo дх/иочекие J0 гек.е/ А/по/ л Ј tfAOKf /с сГлоХЈЬМ 3 к. /

/7Об/71 у КОе 4C.Jмфение фе/чрKU- 14. tffy

0лока.ги Зу /

J0 со- o fuiefc JL & &е t&Ј/tfft&c0cfn Ј$ло/са 3

)

Kjfife/ e u.e яеки /us/П0ЛГ ncftfcAMf

.ttJL сигкллаCO 6JC. / -с ГЛОХХХ./Ь1 «. V

.(t сооЈи$еНЛ А О nЈUCfyaЈ /wc/rtw- 6 локоЈ 1 .

0At era а 30 cowT- 14$ек.ъЈЛ о nf)a.ffr oc/7t t. tfjt0/caЈ Jttjui-cL

W « °

(#океч

Ttfrt

#6t.fa ҐЛ J0 eeof- KjfKttJl f /tfagfcocrtttf &o- ъсли. У

,

| Цифровой фазометр мгновенных значений | 1987 |

|

SU1415198A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения временных интервалов с самоконтролем | 1985 |

|

SU1325487A1 |

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| ( УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ | |||

Авторы

Даты

1992-05-23—Публикация

1989-09-05—Подача