чтения и блокировки записи буферной памяти, выход шестого элемента НЕ соединен со стробирующим входом пятого элемента НЕ и четвертым входом одиннадцатого элемента И-НЕ, выход которого соединен со счетным входом счетчика, при этом блок установки режима контроля содержит четыре триггера, элементы И, И-НЕ, И-ИЛИ-НЕ, S-вход первого триггера и первый вхо первого элемента И подключены к йшне общего сброса устройства, С-вход первого триггера подключен к выходу элемента И-НЕ, а его R-вход и D-вход третьего триггера соединены с выходами разрядов режимов блокировки регистра режима, D-вход первого триггера и первый вход элемента И-ИЛИ-НЕ соединены с единичным выходом второго триггера, нулевой выход которого соединен с вторьм входом шестого элемента И-НЕ блока управления памятью, первьй вход элемента ИНЕ и второй вход элемента И-ИЛИ-НЕ соединены с щной синхронизации электронной вычислительной машины, второй вход элемента и R-вход второго триггера соединены с выходом подтверждения захвата щин электронной вычислительной машины, С-вход второго триггера соединен с выходом второго элемента И, первый вход которого соединен с вькодом переполнения счетчика, а второй вход через первый элемент НЕ соединен с выходом коммутатора, С-вход третьего триггера соединен с вькодом третьего элемента И, первый и второй входы которого и второй вход первого элемента

И соединены с выходами управления захватом шин группы управляющих шин электрон::ой вычислительной машины, R-вход третьего триггера соединен с выходом элемента И-ИЛИ-НЕ, третий вход которого через второй элемент НЕ соединен с шиной общего сброса устройства, выход первого элемента И соединен с S-входом четвертого триггера, С-вход которого соединен с нулевым выходом первого триггера, который соединен с входом блокировки коммутатора, выход третьего триггера соединен с входом запроса захвата шин электронной вычислительной машины, выход четвертого триггера соединен с первым управляющим входом коммутатора., второй, третий и четвертый управляющие входы которого соединены соответственно с выходом счетчика, выходом управления записью и управляющим выходом адаптера памяти, информационные входы и выходы буферной памяти соединены с информационными входами и выходами электронной вычислительной машины, входы сброса счетчика, регистра режима, адаптера памяти соединены с шиной общего сброса устройства, информационньй и управляющий входы регистра режима подключены к информационной и управляющей шинам электронной вычислительной машины, входы блокировки записи, пуска и синхронизации адаптера памяти соединены соответственно с вькодом переполнения счетчика, шинами подтверждения захвата щин и синхронизации электронной вычислительной машины.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Устройство для отсчета времени | 1990 |

|

SU1784959A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1987 |

|

SU1520530A1 |

| Устройство для определения частот обращения к программам | 1985 |

|

SU1357963A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Устройство для контроля ЭВМ | 1987 |

|

SU1608666A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1401470A1 |

УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ МЕЩУ ОБЪЕКТОМ КОНТРОЛЯ И . ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНОЙ, содержащее буферную память, адресные входы которой подключены к выходу счетчика, двунаправленный коммутатор, первая группа информационных входов-вькодов которого соединена с группой информационных входов-выходов объекта контроля, а вторая группа информационных входов-выходов с группой информационных, адресных и управляющих шин электронной вычислительной машины, адаптер памяти, отличающееся тем, что, с целью сокращения оборудования, устройство содержит блок установки режима контроля, блок управления памятью, регистр режима, причем блок управления памятью содержит дешифратор, элементы НЕ, И-НЕ, первый и второй выходы дешифратора соединены с первыми входами первого и второго элементов И, вторые входы которых соединены с третьим выходом дешифратора, а выходы - с первыми входами соответственно третьего и четвертого элементов И-НЕ, выходы которых соединены с первым и вторым входами пятого элемента И-НЕ, вькод которого соединен с первым входом шестого элемента И-НЕ, выходы первого и второго элементов НЕ соединены с первым и вторым входами седьмого элемента И-НЕ, выход второго элемента НЕ соединен с вторыми входами третьего и четвертого элементов И-НЕ, выход третьего элемента НЕ соединен с Третьим входом четвертого элемента И-НЕ, выход второго элемента И-НЕ и выход четвертого элемента НЕ соединены с первым и вторым входами восьмого элемента И-НЕ, выход которого соеди(Л нен с третьим входом пятого элемента И-НЕ, четвертый вход которого соединен с выходом девятого элемента И-НЕ, входами соединенного с выходами пятого и шестого элементов НЕ, выходы шестого и седьмого элементов И-НЕ соединены с первым и вторым входами десятого элемента И-НЕ, выход котоел рого соединен с первьм входом одинOi надцатого элемента И-НЕ, второй и о третий входы которого соединены соответственно с выходом шестого эле00 мента НЕ и четвертыкг выходом дешифратора, входы которого соединены с выходами разрядов выбора типа контрольной информации регистра режима, входы первого, второго, третьего и четвертого элементов НЕ соединены соответственно с выходами чтения и записи группы выходных управляющих шин электронной вычислительной машины, выходы шестого, седьмого и де ятого элементов И-НЕ соединены соответственно с входами записи.

1

Изобретение относится к вычислительной технике и может быть использовано для проверки работоспособноети и диагностики неисправностей цифровьгх модулей микро-ЭВМ.

Цель изобретения - сокращение оборудования устройства контроля. ;

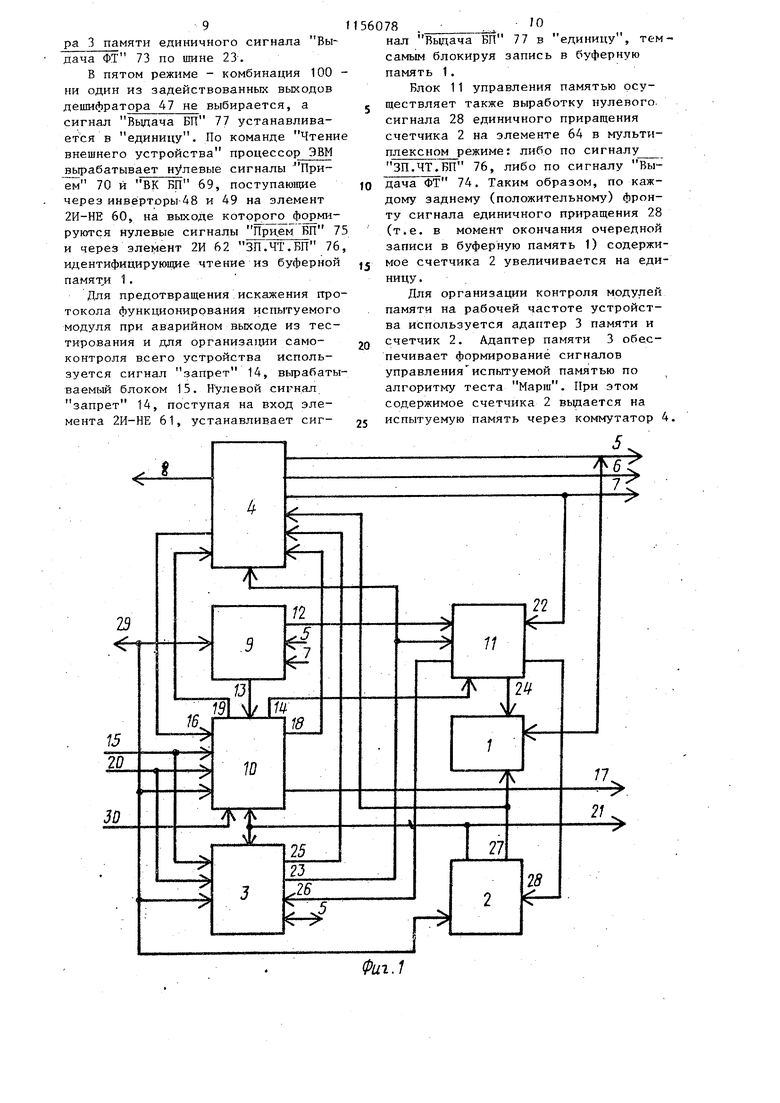

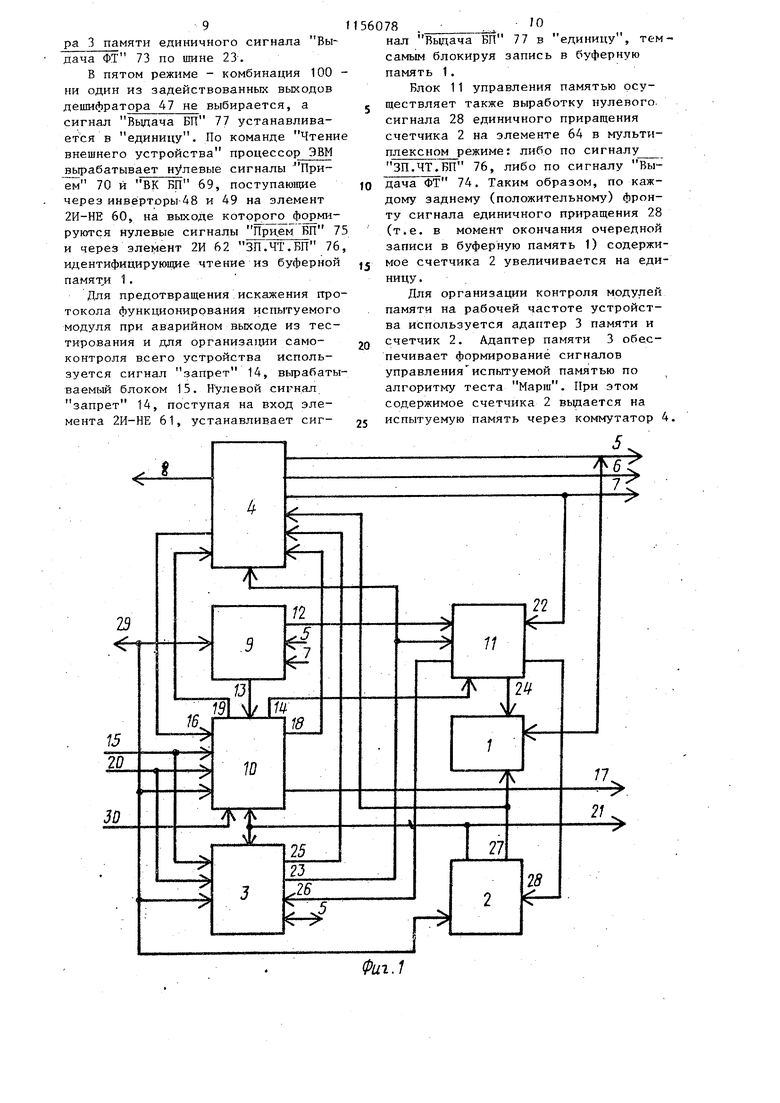

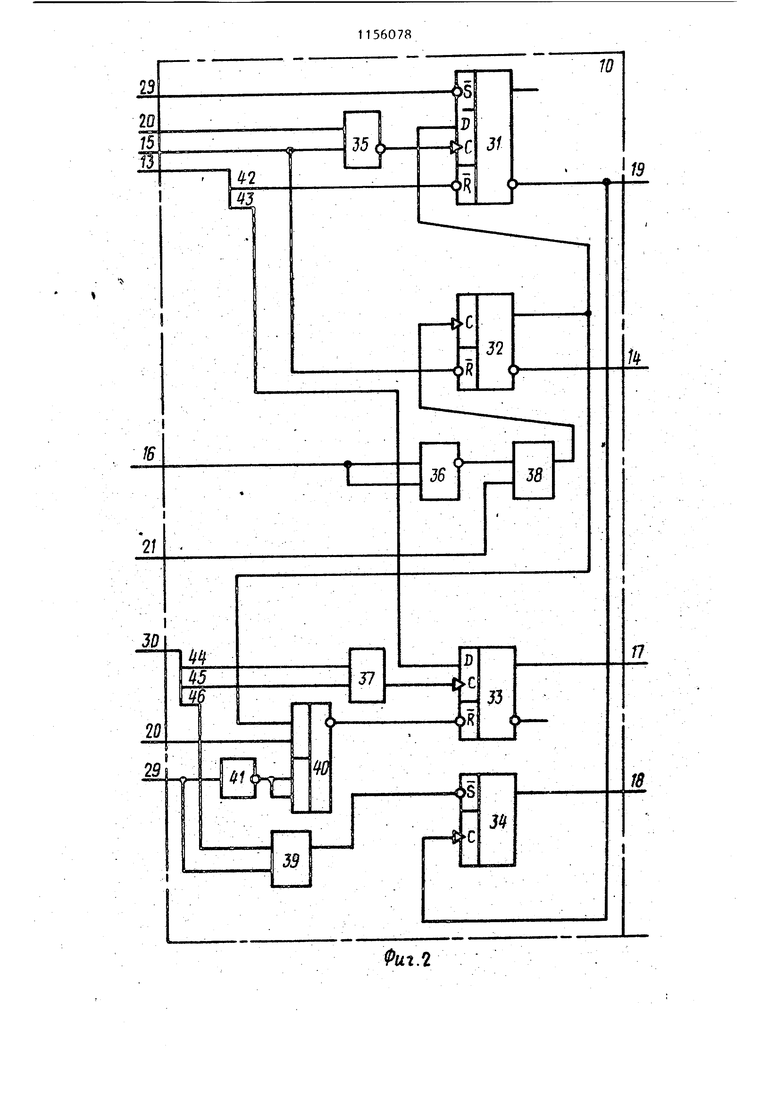

На фиг. 1 изображена схема устройства для обмена информацией между объектомконтроля и электронной вычислительной ма 1шной (ЭВМ); на фиг.2 схема блока установки режима контроля; на фиг. 3 - схема блока управления памятью.

Устройство содержит буферную память 1, счетчик 2, адаптер 3 памяти,

двунаправленньм коммутатор 4, вторая группа входов-выходов которого соединена с соответствующими информационнь ми 5, адресными 6 и управляющими 7 шинами электронной вычислительной

машины, а первая группа 8 входоввыходов - с соответствующими входамивыходами объекта контроля, регистр 9 режима, блок 10 установки режима блок 11 контроля, олок п управления памятью шину 12 выборки, пмну 13 установки, шину 14 запрета, шины 15 и 16 поддержания захвата шин процессора устройства и испытуемого процессора, шины 17 и 18 запроса захвата шин процессора устройства и испытуемого процессора, шину 19 блокировки, шину 20 синхронизации, шину 21 переполнения, шину 22 сопряжения, служебную шину 23, шину 24 управления буферной памятью, шину 25 управления испытуемой памятью, шину 26 строба памяти, шину 27 адресации буферной памяти, шину 28 единичного приращенная счетчика, шину 29 сброса, шину 30 управления захватом. Схема блока установки режима контроля (фиг. 2) включает триггер 31 блокировки, вспомогательный триггер 32, триггеры 33 и 34 запроса отключения процессора ЭВМ и испытуемого процессора, логические элементы 2И-НЕ 35 и 36, 2И 37-39, 2-2И-ИЛИ-НЕ 40, инвертор 41. По шине 13 установки в блок.15 поступает содержимое разрядов 42.и 43 регистра режима 9, определяющих программную установку режимов блоки ровки и отключения процессора соответственно, а по шине 30 управления - сигналы Ком.ЗП.ВУ 44, ВК РР (выбор регистра 9 режима)45 формируемые процессором ЭВМ на шине 7 управления, и сигнал ВК(х) 46. (выбор триггера 34 запроса отключения испытуемого процессора), формируемый испытуемым процессором и поступающий из коммутатора 4 на пшну управления; Схема блока управления памятью (фиг. 3) включает дешифратор 47, ин верторы 48-53, элементы ЗИ-НЕ 54 и 55, элементы 2И-НЕ 56-62, элемент 4И-НЕ 63, элемент 2-2И-2ИЛИ-НЕ 64, шину Земли 65. По шине 13 выборки поступает содержимое разрядов 66, 6 и 68 регистра 9 режима, определяющи выбор типа контрольной информации. По шине 22 сопряжения поступают сиг налы Прием (затрат вьдачи данных) 69, БК БП (выбор буферной памяти 70,Выборка 71 (идентификатор цикл выборки команды), Вьщача 72 (запи в память). По служебной шине 23 поступают сигналы Выдача ФТ 73 (запись в бу84 . ерную память 1 во время контроля модулей памяти) и СЧ+1 74 (единичное приращение счетчика 2). Блок вырабатывает сигналы управления буферной памятью 1: Прием БП 75, ЗП.ЧТ.БП 76 (строб выбора памяти) и Выдача БП 77, - поступаю1гще на шину 24. Работу устройства рассмотрим на примере его вьшолнения на базе микропроцессорного комплекта К580. В устройстве реализуется: самотестирование модулей, содержащих микропроцессор путем подключения испытуемого модуля к системным шинам данных адреса и управления (т.е. испытуемый микропроцессор получает возможность доступа к памяти устройства для выполнения программ самопроверки); протоколирование функционирования испытуемых модулей путем автоматической последовательной записи информации, циркулирующей во время тестирования по шине данных, в буферную память в одном из режимов записи только команд, только данных, команд и данных, данных из испытуемой памяти; тестирование и обработка результатов тестирования разделены во времени, что позволяет проводить проверку на рабочей частоте (при одинаковой рабочей частоте всего устройства и испытуемых модулей) и разрабатывать гибкие алгоритмы диагностирования на основе обработки протоколов функционирования. Испытуемый модуль микро-ЭВМ подключается к входным контактам кo Iмyтатора 4. После включения питания устройства процессор ЭВМ автоматически осуществляет сброс всего устройства по шине 29, и блок 15 вырабатывает сигнал блокировки шины 19 коммутатора 4 (фиг. 2), обеспечивающий отключение испытуемого модуля от системных шин данных 5, адреса 6 и управления 7. Процессор ЭВМ опрашивает пульт управления (не показан), на котором оператор набирает код проверяемого модуля. В зависимости от полученной информации возможны следующие режимы работы процессора ЭВМ. При контроле модулей, содержащих микропроцессор, происходит переход в состояние захвата шин (т.е. в третье состояние, эквивалентное отключению от системных шин 5, 6 и 7) сброс блокировки 19 коммутатора 4 и инициирование запуска тест-программ испытуемого микропроцессора. При контроле модулей памяти осуществляется переход в состояние захвата шин сброс блокировки шины 19 и инициирование запуска адаптера 3 памяти, фор мирующего контролирующий тест памяти а при контроле интерфейсных модулей сброс блокировки шины 19 и генерирование контролирунщих тестов. Общее управление режимами устройства обеспечивает регистр 9 режима, загружаемый программно по шине данны 5. Первая группа 12 разрядов регистра 9 режима кодирует режимы Ч-естирования и обработки протоколов (диагностика) и тип информации, записывае мой в буферную память 1 (т.е. содержимое протокола), вторая группа 13 разрядов предназначена Для программной самоустановки процессора ЭВМ в режим захвата шин и сброса блокировк шины 19 коммутатора 4. Процесс контроля и диагностики требует многократного автоматическог переключения процессора ЭВМ из актив ного состояния в пассивное (захват ишн) . И наоборот, с целью фор№ рования и обработки протоколов в соответтзо ствии с алгоритмами контроля и диагноза в состав устройства входит блок 15 задания режима контроля (фиг. 2), основньми режимами работы послед него являются: установка начальнсй блокировки шины 19 при включении питания устройства или системном сбросе; уход на режим самоконтроля испытуемого модуля с микропроцессором; выход из режима самоконтроля по сигналу ВК(х) 46 (запрос испытуемого микропроцессора на самоотключение путем перехода в состояние захвата шин); выход из режима самоконтроля по сигналу 21 переполнения счетчика 2 (переполнение буферной памяти 1); программный сброс блокировки шины 19.: В первбм режиме сигнал Сброс 29 устанавливает ннверсйьй выход тригге ра 31 блокировки в единичное состояние, т.е. формируется сигнал Блокировка 19 и режим захвата шин испытуемогоцикропроцессора (единичный сиг нал. Захват (х) 18 формируется на элементе 2И 39 и триггере 34) , одновременночерез элементы 41 и 40 устанав ливая логический О на выходе триг18 гера 33, фиксирующего отсутствие захвата шин процессора ЭВМ. Таким образом, по сигналу Сброс осуществляется блокировка коммутатора 4, захват шин испытуемого микропроцессора и разрешение работы процессора ЭВМ. Во втором режиме процессор ЭВМ по сигналу Ком.ЗП.ВУ 44 (запись во внешнее устройство) загружает в регистр 14 режима управляющее слово, содержащее единицу в разряде, соответствующем запросу на захват шин процессора ЭВМ, и по заднему фронту синхроимпульса, вырабатываемого элементами 2И 37, по сигналам Ком.ЗП.ВУ 44 и ВК РР 45 эта единица, поступающая в блок 15 по шине 13 (сигнал запроса 43), загружается в триггер 33 и на его выходе вырабатывается единичный сигнал Захват 17, поступающий в процессор ЭВМ. При переходе к выполнению следующей команды процессор ЭВМ анализирует сигнал Зарсват 17 и вырабатывает сигнал Под 15, дентифицирутверждение захвата ющий его переход в отключенное состояние. Сигнал Подтверждение захвата 15 стробируется на элементе 2И-НЕ 35 тактсвьм синхроимпульсом 20, перебрасывающим триггер 31 блокировки в инверсное состояние, т.е. осуществляется сброс блокировки (установка сигнала Блокировка 19 в единичное состояние) и одновременно сброс захвата шин испытуемого микропроцессора путем записи в триггер 33 нуля по фронту сигнала Блокировка 19. Таким.образом, во втором режиме последовательно вырабатываются сигналы: Захват 17 (единица), Подтверждение захвата 15 (единица), Блокировка 19 (единица), Захват (х) 18 (ноль) обеспечивакнцие переход к самоконтролю. Третий и четвертый режим используются для нормального и аварийного выхода из режима самоконтроля. В случае исправной работы испытуемого процессора (третий режим) им вьтолняется программа самопроверки, причем последней командой программы является команда загрузки триггера запроса захвата вти 33. По этой команде формируется нулевой сигнал ВК(х) 46, поступающий по шине 30, который и устанавливает триггер 33 в единичное состояние, т.е. вырабатывается единичньй сигнал Захват (х) 18. Сигнал Захват (х) 18 через коммутато 4 поступает на испытуемый процессор который вьфабатывает единичньй поте циал Подтверждение захвата (х) 16 идентифицирукшщй отключение испытуе мого процессора, по положительному фронту которого перебрасывается в единицу триггер 32, а в следующем такте по заднему фронту сигнала 20 триггер 3t блокировки (установка си нала Блокировка 19 в ноль) и триггер 33 (установка сигнала Захв 17 в ноль). В случае наличия неисправностей испытуемом процессоре (четвёртый ре жим) он будет выполнять вместо программы самопроверки случайньй набор функций, представляющих собой искаженную интерпретацию программы само проверки. В состоянии счета неиспра ный процессор может находиться неограниченное время до момента случай ного выполнения команды останова. Одновременно в буферной памяти 1 фрр мируется протокол вьшолняемых испытуемым процессором операций. Полное заполнение буферной памяти 1 идентиф цируется импульсом Переполнение 2 вырабатываемым счетчиком 2. Этот импульс отрицательной полярности через злемент 2И 38 поступает на синхровход триггера 32 и перебрасывает его в единицу. Дальнейшая установка Сигналов Впокировка 19 и Захват 17 осуществляется аналогично третьему режиму. В пятом режиме процессор ЭВМ по сигналу Ком.ЗП.ВУ 44 загружает в регистр 9 режима управляющее слово, содержащее ноль в разряде, соответствующем сбросу блокировки, и по заднему фронту указанного сигнала этот ноль, поступающий в блок 15 по шине 13 (сигнал 42 сброса блокировки), устанавливает инверсный вько триггера 31 блокировки в единицу, т.е. осуществляет выработку единичного сигнала Блокировка 19. Основньм назначением блока 11 управления памятью (фиг. 3) является выработка, сигналов управления буферной памятью Т в зависимости от режима контроля, задаваемого первой груп пой разрядов 66, 67 и 68 регистра 9 режима по шине 12. Для организации гибкого процесса контроля и диагности рования блок 11 управления памятью реализует: запись только команд (используется для контроля правильности выполнения программ самоконтроля используемого процессора); запись только данных (используется для контроля правильности выполнения команд испытуемым процессором) , последовательную запись команд и данных (используется при пошаговом контроле выполнения программы, а также в специальных режимах диагностики); запись данных при тестировании памяти (используется при проверке плат памяти); чтение содержимого буферной памяти (используется при обработке протоколов проверки испытуемых модулей). В первых четырех режимах единичный потенциал ВК БП 68, поступающий по шине 22 на вход инвертора 58 удерживает в единице сигнал Прием БП 75, настраивающий входные драйверы буферной памяти 1 на прием информации, а сигнал ЗП.ЧТ.БП 76 повторяет сигнал Вьщача БП 77. В первом режиме - комбинадая 111 (66,67,68) - нулевой потенциал на выходе A3-дешифратора 47 устанавливает выход элемента 56 в единицу, одновременно единичные потенциалы остальных выводов дешифратора 47 устанавливают выходы элементов 55, 58 и 59 в единицу. В первом цикле вьптолНения любой команды процессор ЭВМ вырабатывает сигнал Прием на шине 22. Во втором режиме - комбинация 001 - вырабатывается нулевой потен ал на выходе В1 депптфратора 47. Запись в буферную память 1 осуществляется либо в момент поступления из процессора ЭВМ сигнала Прием 70, если сигнал Выборка 71 равен нулю, пибо сигнала Вьщача 72. В третьем режиме - комбинация 010- вырабатывается кулевой потенциал на выходе В2 дешифратора 47. Запись в буферную память 1 осуществляется в момент поступления из про- цессора ЭВМ сигналов Прием 70 и Выдача 72 аналогично первому и второму режимам. В четвертом режиме - комбинация 011- вьфабатьшается нулевой потенциал на выходе ВЗ дешифратора 47. Заись в буферную память 1 осуществлятся в момент поступления из адаптеpa 3 памяти единичного сигнала Выдача ФТ 73 по шине 23. В пятом режиме - комбинация 100 ни один из задействованных выходов дешифратора 47 не выбирается, а сигнал Выдача БП 77 устанавливается в единицу. По команде Чтени внешнего устройства процессор ЭВМ вырабатыва ет нулевые сигналы Прием 70 и ВК БП 69, поступающие через инверторы 48 и 49 на элемент 2И-НЕ 60, на выходе которого формируются нулевые сигналы При,ем ВП 7 и через элемент 2И 62 ЗП.ЧТ.БП 76 идентифицирующие чтение из буферной памятей 1 . Для предотвращения искажения гтро токола функционирования испытуемого модуля при аварийном выходе из тестирования и для организации самоконтроля всего устройства используется сигнал запрет 14, вырабаты ваемый блоком 15. Нулевой сигнал запрет 14, поступая на вход элемента 2И-НЕ 61, устанавливает сигФиг.1 нал Выдача БП 77 в единицу, темсамым блокируя запись в буферную память 1. Блок 11 управления памятью осуществляет также выработку нулевого, сигнала 28 единичного приращения счетчика 2 на элементе 64 в мультиплексном режиме; либо по сигналу ЗП.ЧТ.БП 76, либо по сигналу дача ФТ 74. Таким образом, по каждому заднему (положительному) фронту сигнала единичного приращения 28 (т.е. в момент окончания очередной записи в буферную память 1) содержимое счетчика 2 увеличивается на единицу. Для организации контроля модулей памяти на рабочей частоте устройства используется адаптер 3 памяти и счетчик 2. Адаптер памяти 3 обеспечивает формирование сигналов управленияиспытуемой памятью по алгоритму теста Марш. При этом содержимое счетчика 2 вьцхается на испытуемую память через коммутатор 4.

Put.l

//

2«

| Устройство для контроля микропроцессора | 1977 |

|

SU660053A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Klectronics, v.53, 1980, 26, р | |||

| Способ приготовления строительного изолирующего материала | 1923 |

|

SU137A1 |

Авторы

Даты

1985-05-15—Публикация

1983-01-03—Подача