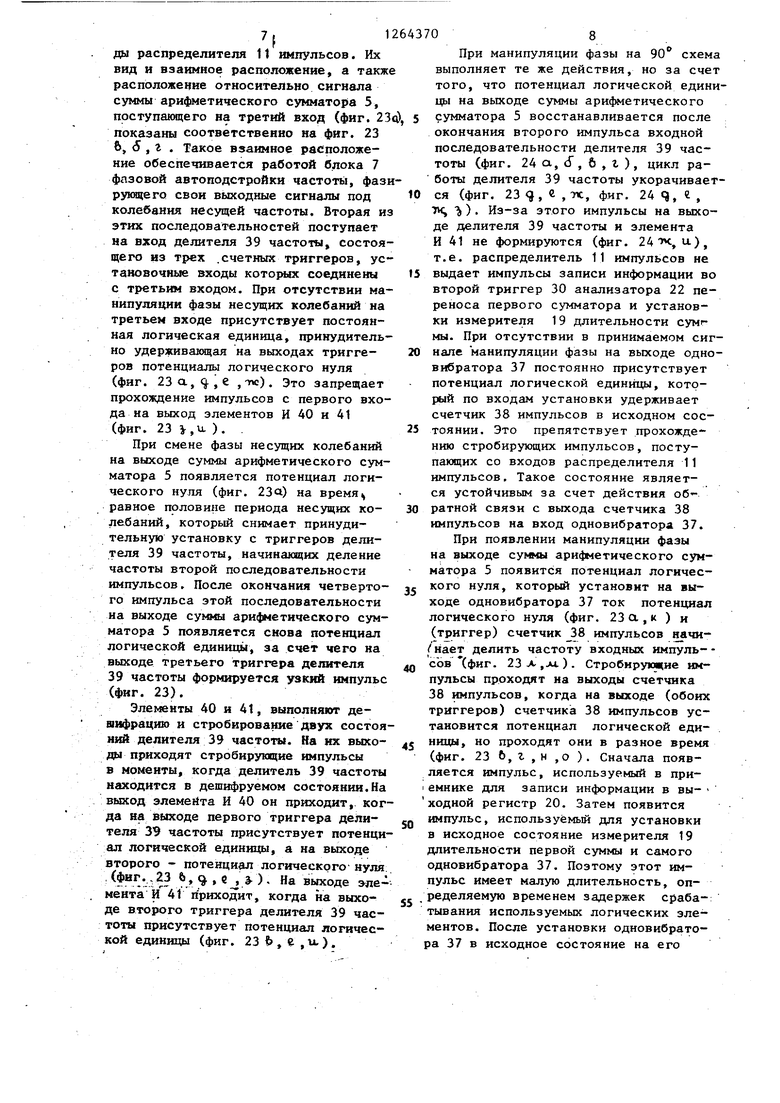

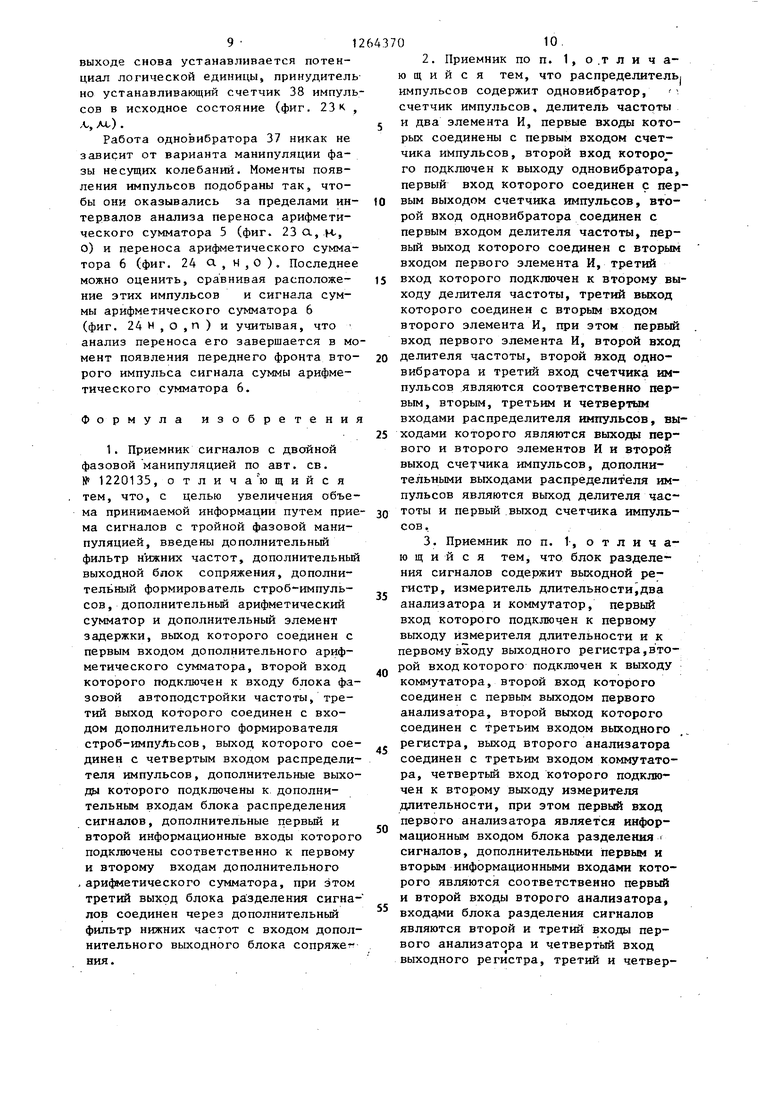

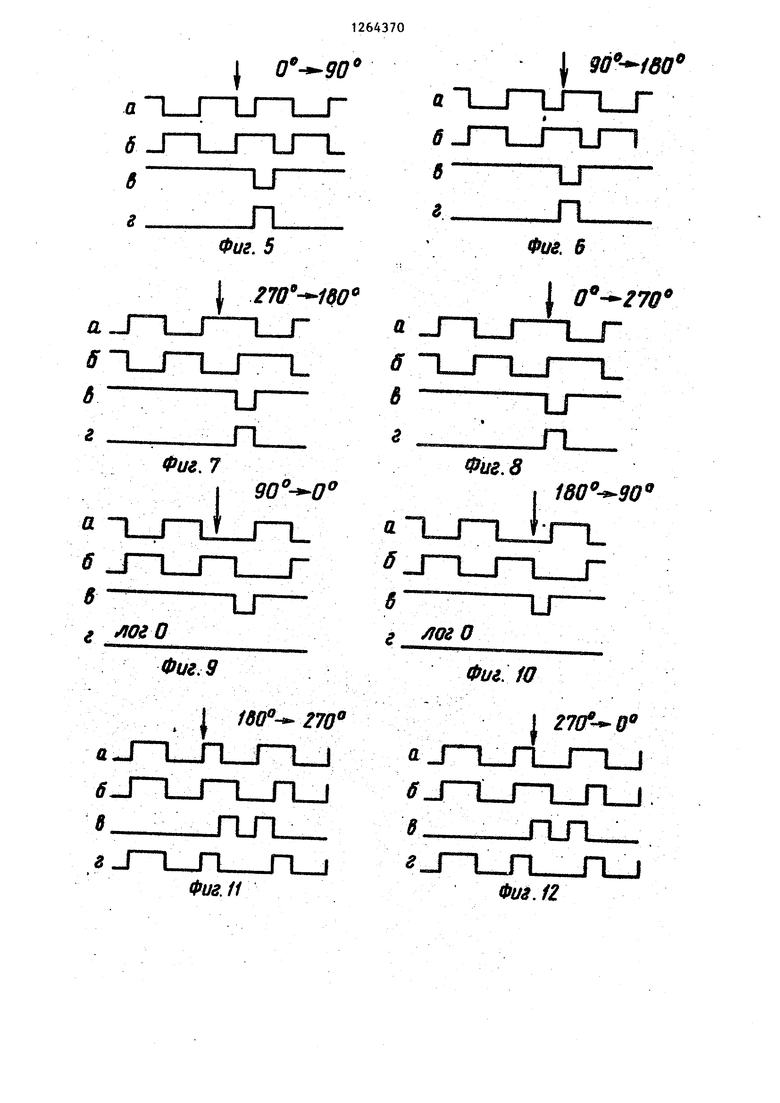

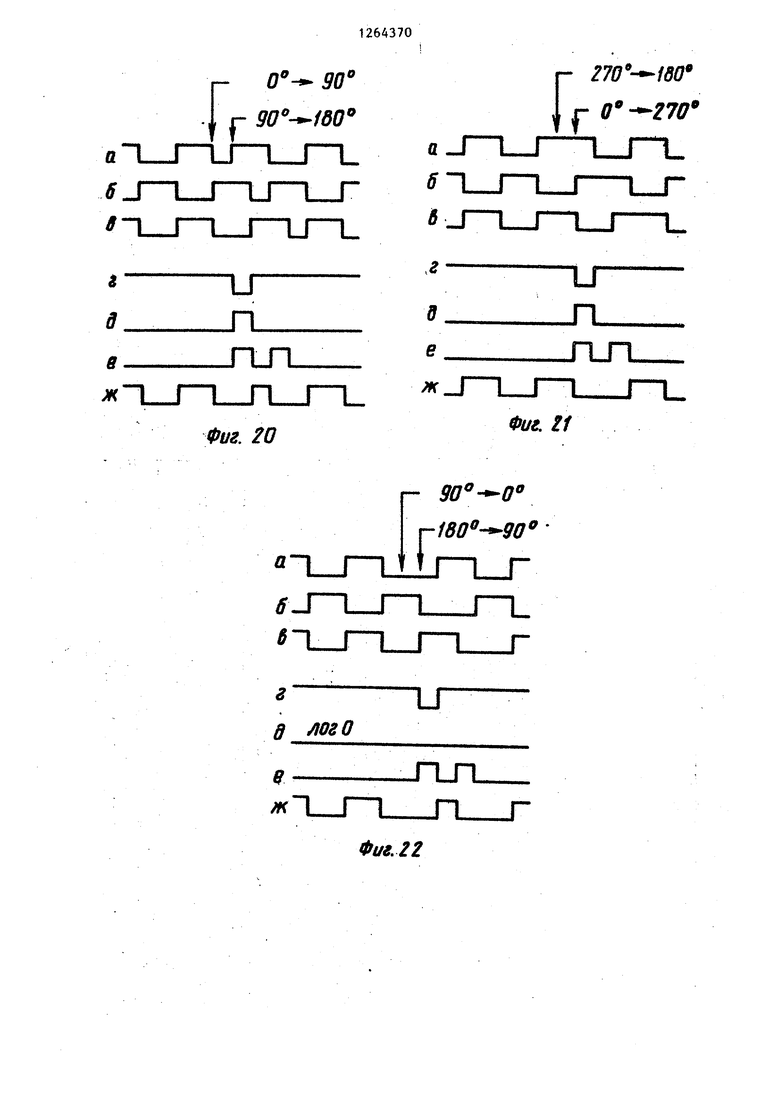

Изобретение относятся к телеграфии, может быть использовано в моделях среднескоростньк систем передачи дискретной информации и является дополнительным.к авт.св. № 1220135. Целью изобретения является увеличение объема принимаемой информации путем приема сигналов с тройной фазовой манипуляцией. На фиг. 1 изображена структурная электрическая схема предложенного приемника; на фиг. 2 - структурная электрическая схема распределения импульсов; на фиг. 3 - 22 - временные диаграммы работы устройства; на фиг. 23 и 24 - временные диаграм мы работь распределителя импульсов. Прием««к сигналов с двойной фазовой манипуляцией содержит полосовой фильтр 1, формирователь 2 импул сов, элемент 3 задержки, дополнитель ный элемент 4 задержки, арифметический сумматор 5, дополнительный арифметический сумматор 6, блок 7 фазовой автоподстройки частоты, первьй и второй формирователи 8 и 9 стробимпульсов , дополнительный формирователь 10 строб-импульсов, распределитель 11 импульсов, блок 12 разделения сигналов, первый и второй фильтры 13 и 14 нижних частот, первый и второй, вьпсодные блоки 15 и 16 соп ; ряжения, дополнительный фильтр 17 нижних частот, дополнительньм вьпсод ной блок 18 сопряжения. Блок 12 разделения сигналов соде жит измеритель 19 длительности, выходной регистр 20, коммутатор 21, первый и второй анализаторы 22 и 23 Измеритель длительности солепжит первый и второй элементы И-НЕ24 |и 25. Коммутатор содержит первый и вто рой элементы И 26 и 27, элемент И 2 Первый анализатор содержит первы и второй -триггеры 29 и 30. Выходной регистр содержит первый второй и третий D-триггеры 31, 32 и 33, Второй анализатор содержит инвер тор 34, первый и второй счетчики 35 и 36 импульсов. Распределитель {шпульсов содержи одновибратор 37, счетчик 38 импульсов, делитель 39 частоты, первый и второй элементы И 40 и 41 . Приемник работает следующим образом. Колебания несущей частоты, выделенные полосовым фильтром 1 из входного сигнала, преобразуются формирователем 2 импульсов в прямоугольные импульсы и поступают на первые входы арифметических сумматоров 5 и 6 непосредственно. На второй вход ари4 1етического сумматора 5 они поступают через элемент 3 задержки сдвигающий их по фазе на половину периода колебаний несущей частоты. На второй вход арифметического сумматора 6 они поступают через два одинаковых элемента 3 и 4 задержки, создающих задержку в период колебаний несущей частоты (фиг. 11 О-, «З 18 a,f ). Если в колебаниях несущей частоты появляется манипуляция фазы, на выходе суммы арифметического сумматора 5 устанавливается потенциал логического нуля на время, однозначно зависящее от величины сдвига фазы при манипуляции. При сдвиге фазы на 180 это время равно половине периода следования импульсов несущей частотьь Сигнал на выходе переноса в течение этого времени может быть различен, но полностью и однозначно определяется вариантом манипуляции колебаний несущей частоты. Его можно рассматривать как последовательный двухраэрядный код, который для различных вариантов манипуляции имеет значения: О - 180° - код 11; 180 - О - код 00; 90 - 270° - код 10; 270 - 90 код 01. Приемник разделяет разряды этого кода в два отдельных канала. При этом один разряд кода выражает зна- чение принятой элементарной посылки первого канала, а другой - второго канала. Эта работа выполняется анализатором 22 первого переноса-с помощью распределителя 11 импульсов. Анализ выполняется в течение интервала времени, пока на выходе суммы арифметического сумматора 5 присутствует потенциал логического нуля, и заключается в следукхцем. Интервал анализа разбивается на две части. Значение переноса на каждый из них заносится в отдельный D -триггер 29 и 30. Сначала значение переноса заносится в D -триггер 30, а затем в D -триггер 29, после чего последовательный к(5д с выхода переноса арифметического сумматора 5 оказывается преобразованным в первый, но разряды этого кода формируются в разное время. Когда в 1 -триггер 30 заносится первый разряд кода с выхода переноса, в 1 -триггере 29 еще хранится значение второго разряда такого же рода, но от прежнего момента манипуляции фазы, и заменится новым значением только пос ле записи в 1 -триггер 29 второго разряда нового кода. Эти моменты раз несены на постоянную величину, равную четверти периода колебаний несущей частоты. Для устранения этого сдвига содер жимое анализатора 22 первого переноса переписывается параллельным кодом в .Р -триггеры 31 и 32 выходного, регистра 20. При этом в его D -триггер 33 информация переписывается не посредственно, а в D -триггер 32 через коммутатор 21, управляемьй измерителем 19 длительности первой суммы, представляющим собой статический триггер. Если в анализируемом вариан те манипуляции фаза сдвигалась на 180, на вход установки этого тригге ра с третьего выхода распределителя 11 импульсов в конце интервала анализа поступает отрицательный импульс обеспечивающий на выходе элемента И 24 потенциал логической единицы, а на выходе элемента И 25 - логичес-кого нуля. За счет этого к моменту записи в выходной регистр 20, поступающему после окончания интервала анализа, коммутатор 21 подключает к информационному входу D -триггера 32 выход D -триггера 29. Когда с четвертого выхода распределителя 11 импульсов появится импульс записи, в два D -триггера 31 и 32 вы ходного регистра запишется код с выхода переноса арифметического сумматора 5,а в первый D-триггер 31 запи шется логическая единица с выхода из мерителя 19 длительности (первой сумТел)., т.е. в выходном регистре 20 будет записан один из четырех пер- вых кодов приведенной таблицы кодировки Какой именно код будет записан определяется значением переноса арифметического сумматора 5. После этого импульсом с пятого выхода распределителя 11 импульсов измеритель 19 длительности (первой суммы) будет установлен в исходное состояние. Результаты дополнительной обработки, выполняемой элементом 4 задержки, арифметическим сумматором 6 и анализатором 23 (второго переноса) , в этой ситуации не используются. При сдвиге фазы на 90° время существования потенциала логического нуля на выходе суммы арифметического сумматора 5 всегда равно четверти периода следования импульсов несущей частоты (фиг, 3,а ,(5 , Ь, г - 10 о., сГ , Ь , г. ) . Поэтому на выходе установки триггера, выполняющего роль измерителя 19 длительности (первой суммы), не поступает импульс с третьего выхода распределителя 11 импульсов и он остается в исходном состоянии, в которое он был установлен после анализа предыдущего варианта манипуляции фазы импульсом с пятого выхода распределителя 11 импульсов. В результате этого при записи кода в выходной регистр 20 к информационному входу D-триггера 32 через коммутатор 21 будет подключен выход анализатора 23 (второго переноса). Анализ второго переноса выполняется следующим образом. При арифметическом суммировании принятого сигнала и сигнала, задержанного на величину, равную периоду колебаний импульсов несущей частоты, сигнал с выхода суммы арифметического сумматора 6 при сдвиге фазы на 90 всегда имеет.вид двух импульсов, имеющих длительность, равную четверти перио-да колебаний несущей частоты. Они разделены интервалом такой же длительности. Сигнал на выходе переноса арифметического сумматора 6 при отсутствии манипуляции повторяет импульсы несущей частоты. Появление манипуляции нарушает регулярность сигнала. Нарушение может быть двух типов. При одном из них между импульсами суммы оказывается импульс переноса (фиг. 13 в, L- 185,г), при другом этот импульс отсутствует (фиг. 11 6,г. -166,г). Чтобы различить эти два типа нарушения регулярности сигнал с выхода суммы арифметического сумматора 6 поступает на счетный вход счетчиков 35 и 36 импульсов, на вход установки КОТОРЫХ поступает сигнал с выхода переноса арифметического сумматора 6. Выходом анализатора является выход второго счетчика 36. Так как с выхода переноса арифметического сумматора 6 при отсутствии манипуляции постоянно поступают импульсы, то счетчики 35 и 36 постоянно находятся в исходном состоянии. При появлении манипуляции начинается счет импульсов с выхода суммы арифметического сумматора.6. Если между этими импульсами отсутствует импульс переноса, то к моменту записи информации в выходной регистр 20 счетчики 35 и 36 досчитывают до двойки и на выходе анализатора 23 появится потенциал логической единицы. Если между импульсами суммы окажется импульс переноса, то после того, как счетчики 35 и 36 зафиксируют первый импульс, они будут снова установлены в исходное состояние и затем зафиксируют второй импульс суммы, т.е. к моменту записи информации в выходной регистр 20 счетчики 35 и 36 досчитают только до единихц; и на выходе анализатора 23 к этому моменту будет находиться потенциал логического нуля. Инвертор 34 введен в состав анализатора 23, чтобы обеспечить работу счетчикбв 35 и 36 на положительных фронтах импульсов суммы. Это позволя ет полностью.завершить анализ второ- го переноса уже в начале второго импульса суммы. К моменту записи инфор мации в выходной регистр 20 измеритель 19 длительности (первой суммы) будет находиться в исходном состоянии. Поэтому в первьй D -триггер 31 выходного регистра 20 запишется ноль. В следующую t) -триггеры 32 и 33 запишутся коды, которые для различных вариантов манипуляции будут иметь следукяцие значения:фиг. 1 CL, d, Ь , г , , е , тк - код 10; фиг. 20 а, cf , i) , г , 9 , , -код O.ljJbHr. 21 CL, d, ft , г , 3 ,е ,w.1- код 11; фиг. 22 а, сГ, U , 2, , 9 , - код 00. При этом надо учитывать, что в D-триггер 33 заносится значение по. тенциала на выходе переноса арифметического сумматора 5 в то время, 55

пока на втором выходе его суммы присутствует потенциал логического нуля. Во второй D -триггер 32 заносит1

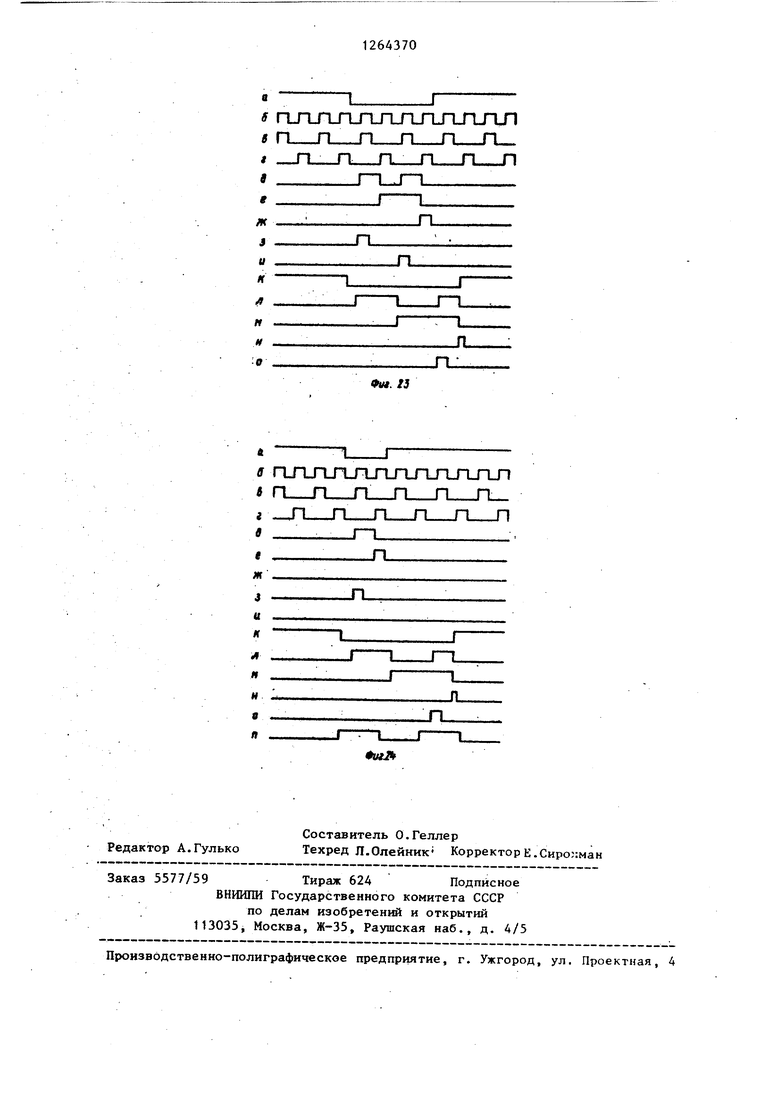

ты формирователи 8, 9,10 строб-импульсов формируют при последовательности импульсрв, поступающих на вхо06ся 32 ноль, если между .импульсами суммы находится импульс переноса, и единица, если импульс отсутствует. Полученные значения полностью, соответствуют четырем нижним строкам приведенной кодировки, т.е такое построение схемы позволяет отождествить код, записанньй в выходном регистре 20, с кодом, образованным одновременно передаваемыми элементарными посылками трех независимых сигналов. Разряды этого кода оказываются разделенными в три отдельных канала и каждьй разряд кода выражает значение принятой элементарной посылки отдельного канала. Далее элементарные посылки каждого канала через отдельный фильтр 13 (14 и 17) нижних частот и выходной блок 15 (16 и 18) сопряжения поступают на отдельный выход приемника. Таким образом, для правильной работы приемника операции в блоке разделения каналов должны выполняться строго определенные моменты времени, определяемью распределителем 11 импульсов. Основу распределителя 11 импульсов составляет делитель 39 частоты (трехразрядньй двоичный счетчик), выходы первьк двух триггеров которого соединены с входами элементов И 40 и 41. Импульсы, проходящие на выходы элементов И 40 и 41, и делитель 39 частоты на два определяют соответственно моменты записи информа- ции в D -триггеры 29 и 30 анализатора 22 и установки измерителя 19 (первой ). Формирования импульсов при манипуляции фазы на 180 и 90° немного различаются. В первом случае импульсы записи информации в триггеры 29 и 30 анализатора 22 первого переноса формируются так, чтобы импульс / на выходе элемента И 40 находился на середине первой половины этого интервала (фиг. 23 а,и.). Импульс на выходе делителя частоты 39 (3) располагается в самом конце интервала анализа после импульсов на выходах элементов И 40, 41 (фиг. 23,«, Ь1). Эти импульсы формируются следующим образом. Из выходных сигналов блока 7 фазовой автоподстройки часто7, 1 ды распределителя It импульсов. Их вид и взаимное расположение, а также расположение относительно сигнала суммы арифметического сумматора 5, поступаницего на третий вход (фиг. 23 показаны соответственно на фиг. 23 6, 5 , г . Такое взаимное расположение обеспечивается работой блока 7 фазовой автоподстройки частоты, фази рукяцего свои выходные сигналы под колебания несущей частоты. Вторая из этих последовательностей поступает на вход делителя 39 частоты, состоящего из трех .счетных триггеров, установочные входы КОТО1ЖХ соединены с третьим входом. При отсутствии манипуля1щи фазы несущих колебаний на третьем входе присутствует постоянная логическая единица, принудительно удерживакндая на выходах триггеров потенциалы логического нуля (фиг. 23а,,е ,1). Это запрещает прохождение импульсов с первого входа на выход элементов И 40 и 41 (фиг. 23 ,и. ). . При смене фазы несущих колебаний на выходе суммы арифметического сумматора 5 появляется потенциал логического нуля (фиг. 23а) на время равное половине периода несущих колебаний, который снимает принудительную установку с триггеров делителя 39 частоты, начинающих деление частоты второй последовательности импульсов. После окончания четвертого импульса этой последовательности на выходе суммы арифметического сумматора 5 появляется снова потенциал логической единицы, за счет чего на выходе третьего триггера делителя 39 частоты формируется узкий импульс (фиг. 23). Элементы 40 и 41, выполняют дешифрацию и стробирование двух состояний делителя 39 частоты. На их выходы приходят стробирующие импульсы

в моменты, когда делитель 39 частоты находится в дешифруемом состоянии.На выход элемейта И 40 он приходит, когда на выходе первого триггера делителя 39 частоты присутствует потенциал логической единицы, а на выходе второго - потенциал логического нуля; :-. . 9 в j На выходе элемента И 41 приходит, когда на выходе второго триггера делителя 39 частоты присутствует потенциал логической единицы (фиг. 23b,(i,u.).

ляется импульс, используемый в приIамнике для записи информации в выходной регистр 20. Затем появится импульс, используемый для установки в исходное состояние измерителя 19 длительности первой суммы и самого одновибратора 37. Поэтому этот импульс имеет малую длительность, определяемую временем задержек срабатывания используемых логических элементов. После установки одновибрато- ра 37 в исходное состояние на его 08 . При манипуляции фазы на 90 схема выполняет те же действия, но за счет того, что потенциал логической единицы на выходе суммы арифметического сумматора 5 восстанавливается после окончания второго импульса входной последовательности делителя 39 частоты (фиг. 24 а, (Г , 6 , г ) , цикл работы делителя 39 частоты укорачивается (фиг. 23 , ч ,TV., фиг. 24 q, е , Tw ) . Из-за зтого импульсы на выходе делителя 39 частоты и элемента И 41 не формируются (фиг. 24 и.), т.е. распределитель 11 импульсов не выдает импульсы записи информации во второй триггер 30 анализатора 22 переноса первого сумматора и установки измерителя 19 длительности сумг мы. При отсутствии в принимаемом сигнале манипуляции фазы на вьиоде одновибратора 37 постоянно присутствует потенциал логической единицы, который по входам установки удерживает счетчик 38 импульсов в исходном сое- тоянии. Это препятствует прохожденшо стробирукнцих импульсов, поступающих со входов распределителя 11 импульсов. Такое состояние является устойчивым за счет действия об-ратной связи с выхода счетчика 38 импульсов на вход одновибратора 37. При появлении манипуляции фазы на выходе cyNWbi арифметического сумматора 5 появится потенциал логического нуля, который установит на выходе одновибратора 37 ток потенциал логического нуля (фиг. 23 о.,к ) и (триггер) счетчик 38 импульсов начи Нает делить частоту входных импуль- сов (фиг. 23 А ,ju. ) . Стробирукяцие импульсы проходят на выходы счетчика 38 импульсов, когда на выходе (обоих триггеров) счетчика 38 импульсов установится потенциал логической единицы, но проходят они в разное время (фиг. 23 6, г ,н ,о ). Сначала появвыходе снова устанавливается потенциал логической единицы, принудительно устанавливающий счетчик 38 импульсов в исходное состояние (фиг. 23 к , л, М.) .

Работа одновибратора 37 никак не зависит от варианта манипуляции фазы несущих колебаний. Моменты появления импульсов подобраны так, чтобы они оказывались за пределами интервалов анализа переноса арифметического сумматора 5 (фиг. 23 а, к, о) и переноса арифметического сумматора 6 (фиг. 24 а, н,0 ), Последнее можно оценить, сравнивая расположение этих импульсов и сигнала суммы арифметического сумматора 6 (фиг. 24 Н , о ,п ) и учитывая, что анализ переноса его завершается в момент появления переднего фронта второго импульса сигнала суммы арифметического сумматора 6.

Формула изобретения

1. Приемник сигналов с двойной фазовой манипуляцией по авт. св. № 1220135, отличающийся тем, что, с целью увеличения объема принимаемой информации путем приема сигналов с тройной фазовой манипуляцией, введены дополнительный фильтр нижних частот, дополнительный выходной блок сопряжения, дополнительный формирователь строб-импульсов , дополнительньй арифметический сумматор и дополнительный элемент задержки, выход которого соединен с первым входом дополнительного арифметического сумматора, второй вход которого подключен к входу блока фазовой автоподстройки частоты, третий выход которого соединен с входом дополнительного формирователя строб-импуАьсов, выход которого соединен с четвертым входом распределителя импульсов, дополнительные выходы которого подключены к дополнительным входам блока распределения сигналов, дополнительные первьй и второй информационные входы которого подключены соответственно к первому и второму входам дополнительного , арифметического сумматора, при этом третий выход блока разделения сигналов соединен через дополнительный фильтр нижних частот с входом дополнительного выходного блока сопряже ния.

2.Приемник по п. 1, о .т л и ч аю щ и и с я тем, что распределитель импульсов содержит одновибратор, счетчик импульсов, делитель частоты

и два элемента И, первые входы которых соединены с первым входом счетчика импульсов, второй вход которого подключен к выходу одновибратора, первый вход которого соединен с первым выходом счетчика импульсов, второй вход одновибратора соединен с первым входом делителя частоты, первый выход которого соединен с вторым входом первого элемента И, третий

5 вход которого подключен к второму выходу делителя частоты, третий выход которого соединен с вторым входом второго элемента И, при этом первый вход первого элемента И, второй вход

0 делителя частоты, второй вход одновибратора и третий вход счетчика импульсов являются соответственно первым, вторым, третьим и четвертым входами распределителя импульсов, вы5 ходами которого являются выходил первого и второго элементов И и второй выход счетчика импульсов, дополнительными выходами распределителя импульсов являются выход делителя час

0 тоты и первый выход счетчика импульсов .

3.Приемник по п. 1, о т л и ч аю щ и и с я тем, что блок разделения сигналов содержит выходной регистр, измеритель длительности|два анализатора и коммутатор, первый вход которого подключен к первому выходу измерителя длительности и к первому входу выходного регистра,второй вход которого подключен к выходу ко1 в4утатора, второй вход которого соединен с первым выходом первого анализатора, второй выход которого соединен с третьим входом выходного регистра, выход второго анализатора соединен с третьим входом коммутатора, четвертьш вход которого подключен к второму выходу измерителя длительности, при этом первьй вход первого анализатора является информационным входом блока разделения сигналов, дополнительными первым и вторым информационными входами которого являются соответственно первый и второй входы второго анализатора,

входами блока разделения сигналов являются второй и третий входы первого анализатора и четвертый вход выходного регистра, третий и четвер 1

тый выходы измерителя длительности являются дополнительными входами блока разделения сигналов, первв1м.

126437012

вторым и третьим выходами которого являются первый, второй и третий выходы выходного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемник сигналов с двойной фазовой манипуляцией | 1983 |

|

SU1220135A1 |

| Преобразователь сдвига фазы в код скорости и ускорения | 1986 |

|

SU1358096A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Приемник сигналов с двойной фазовой манипуляцией | 1986 |

|

SU1443198A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| АВТОКОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ ПСЕВДОСЛУЧАЙНОГО ФАЗОМАНИПУЛИРОВАННОГО СИГНАЛА | 1991 |

|

RU2013005C1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Электронные шахматные часы | 1987 |

|

SU1642443A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| Устройство для преобразования координат | 1984 |

|

SU1179324A1 |

Изобретение относится к телеграфии и (отквт использоваться в моделях среднескоростных систем передачи дискретной информации. В сравнении с изобретением по основному авт. св. № 1220135 увеличивается объем принимаемой информации путем приема сигналов с тройной фазовой манипуляцией. Устр-во содержит полосовой фильтр 1, формирователь 2 импульсов, элементы 3, 4 задержки, арифметические сумматоры 5, 6, блок 7 фазовой автоподстройки частоты, формирователи 8, 9, 10строб-импульсов, распределитель 11импульсов, блок 12 разделения сигналов, фильтры нижних частот (ФНЧ) 13, 14, 17, выходные блоки сопряжения (ВВС) 15, 16, 18. Блок 12 разделения сигналов содержит измеритель 19 дальности, выходной регистр 20, коммутатор 21 и анализаторы 22, 23. Для осуществления приема сигналов с тройной фазовой манипуляцией введены элемент 4 задержки, арифмети(Л ческий сумматор 6, формирователь 10 С строб-импульсов,ФНЧ 17 и ВВС 18. 2 з.п. ф-лы, 24 ил.:

i

и

лог о

Фиг. 3

Фиг. 4 Фиг. 7

Фиг. 9 Фиг. // . 1Q 160 Фиг. 8 О о ft о nru Фиг.и

Фиг. /3

270- т

Фиг. 15

Фиг. 1

I

Фиг. 16

Фиг. /7

Фиг. 18

180- 270

г, г 270- 0

Фиг, 19

иг

П

ПП

Фиг. 20

г

Q огО

и

П

J-L

Фиг. If

- 90- 0

и

Фиг.22

jTjTJTTuiJTrLnjT-rm

«

ж J

U JT

л

н н

в а

П

| Приемник сигналов с двойной фазовой манипуляцией | 1983 |

|

SU1220135A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-10-15—Публикация

1985-06-11—Подача