Изобретение относится к автоматике и вычислительной технике и может быть использовано для передачи информации в автоматизированных системах контроля и управления технологическими процессами и производством

Известно устройство, содержащее датчики контролируемых параметров, соединенные через регистры, первый коммутатор и элемент совпадения с разрядными входами четвертого регистра, вход обнуления которого соединен с выходом второго регистра, а выход - с нулевым входом первого и единичным входом второго триггеров, инверсные выходы соединены с входами элементов совпадения, а прямые выходы - с управляющими входами ключевых элементов, генератор тактовых импульсов, ,

выход которого через один из ключевых элементов подключен к первому входу схемы ИЛИ, а через другой ключевой элемент - к входу второго коммутатора и второму входу схемы ИЛИ, выход которой связан со счетными входами второго и четвертого регистров, а выходы второго коммутатора - с входами третьих регистров.

Информация с выхода опрашиваемого датчика записывается параллельно в четвертый регистр. По поступлении сигнала Запуск на счетные входы четвертого и второго регистров поступают импульсы из генератора. При переполнении четвертого регистра эти импульсы поступают также на счетный вход третьего регистра, соответствующего опрашиваемому датчику. В

со

317

момент переполнения второго регистра а третий регистр записывается код, который присутствовал на выходе указанного датчика в момент запуска.

Недостатком устройства является то, что оно обладает низким быстродействием ввиду наличия двух последовательных переносов одной и той же информации (сначала из входного регистра в промежуточный, а затем из промежуточного в выходной), а так- ч е низкой надежностью, так как вероятность прохождения промехи существует как при первом, так и при втором последовательном переносе информации .

Наиболее близким по технической сущности к предлагаемому является устройство, содеожащее первый комму- татор, информационные входы которого соединены с выходами датчиком контролируемых параметров, а адресный вход является первым адресным входом устройства, реверсивный счетчик, блок начальной установки, элемент ИЛИ, первый вход которого соединен с выходом переполнения реверсивного счетчика, а второй вход - с выходом блока начальной установки, RS-триггер, вход R которого соединен с выходом элемента ИЛИ, а вход S является входом запуска устройства, элемент И второй вход которого соединен с выходом RS-триггера и с входом разрешения предварительной записи ревер- сивного счетчика, а выход со счетным входом реверсивного счетчика, генератор тактовых импульсов, выход которого соединен с вторым входом элемента И, второй коммутатор, информационный вход которого соединен с выходом элемента И, а адресный вход является вторым адресным входом устройства, группа счетчиков, счетные входы которых подключены к выходам второго коммутатора, группа приемных блоков, информационные и тактовые входы, а также выходы сброса которых подключены соответственно к выходам, счетному входу и входу сброса одного из группы счетчиков. Каждый приемный блок содержит последовательно соединенные формирователь тактовых импульсов и элемент ИЛИ-НЕ, формирователь импульсов начальной установки и регистр, информационные входы кото рого являются информационными входами блока, управляющий вход соединен

с вторым выходом формирователя тактовых импульсов, а вход обнуления - с выходом формирователя импульсов начальной установки и первым входом элемента ИЛИ-НЕ, подключенного выходом к выходу сброса блока.

В процессе работы формирователь импульса начальной установки вырабатывает импульс, который устанавливает режим предустановки реверсивного счетчика, запрещает прохождение импульсов, вырабатываемых генератором, на входы счетчиков, и информация с опрашиваемого датчика через первый коммутатор поступает на реверсивный счетчик. Второй коммутатор при этом подключает к приему информацию соответствующего счетчика, и приемного блока группы. По сигналу запуска импульсы генератора поступают на счетный вход реверсивного счетчика и на счетный вход подключенного счетчика группы, что обеспечивает формирование на соответствующем счетчике группы в момент переполнения реверсивного счетчика кода, соответствующего выходному коду опрашиваемого датчика. С выхода счетчика группы этот код с определенной задержкой записывается на регистр приемного блока группы. Время опроса одного датчика при этом определяется формулой:

2К

+ зЈ,

(1)

А

где К - десятичное значение максимально возможного кода из транслируемых устройством; Т1 - период следования импульсов

на выходе генератора; С - длительность импульсов формируемых формирователем тактовых импульсов.

Данное устройство также обладает низким быстродействием. Это связано с тем, что для записи информации необходимо считывание определенного количества импульсов, соответствующих входному коду. Поэтому при больших значениях входного кода устройство обладает низким быстродействием, т.е. время записи входной информации на регистры блоков приемных регистров зависит от значения записываемого кода.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для передачи информации, содержащее два коммутатора, реверсивный счетчик, блок начальной установки, генератор тактовых импульсов, элемент И, RS-триггер, элемент ИЛИ, группу счетчиков,группу приемных блоков, причем группа информационных входов и адресный вход первого коммутатора являются соответственно группой информационных входов и первым адресным входом устройства, вторым адресным входом и группой информационных выходов которого служат соответственно адресный вход второго коммутатора и информационные выходы приемных блоков группы, а входом запуска служит S-вход RS-тригге- ра, первый вход элемента ИЛИ соединен с выходом переполнения реверсивного счетчика, второй вход - с выходом блока начальной установки, а выход - с R-входом RS-триггера, выход которого подключен к входу разрешения предварительной записи реверсивного счетчика и первому входу элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, а выход связан со счетным входом реверсивного счетчика и первым информационным входом второго коммутатора, первая группа выходов которого соединена со счетными входами соответствующих счетчиков группы и тактовыми входами соответствующих приемных блоков группы, информационные входы и выходы сброса которых соединены соответственно с выходами и входами сброса соответствующих счетчиков группы, причем каждый приемный блок группы содержит формирователь тактовых импульсов, элементов ИЛИ-НЕ, Формирователь импульсов начальной установки и регистр, выход формирователя импульсов начальной установки подключен к соответствующим первому входу элемента ИЛИ-НЕ и входу обнуления регистра, причем входы формирователей тактовых импульсов и выходы элементов ИЛИ-НЕ являются соответственно тактовыми входами и выходами сброса соответствующих приемных блоков группы, информационные выходы которых соединены с выходами регистров, дополнительно введены первый алгебраический сумматор и блок памяти номинальных значений, адресный вход которого соединен с первым адресным входом устрой10

15

20

25

360016

ства, а выход - с входом вычитаемого первого алгебраического сумматора, вход уменьшаемого которого соединен е с выходом первого коммутатора, а информационный выход и выход переноса связаны с установочным входом реверсивного счетчика и вторым информационным входом второго коммутатора, причем в каждый приемный-блок группы введен элемент задержки, второй ал гебраический сумматор и задатчик номинального значения, выход формирователя тактовых импульсов связан с тактовым входом второго алгебраического сумматора и с входом элемента задержки, выход которого соединен с входом элемента ИЛИ-НЕ и входом разрешения записи регистра, информационный вход которого подключен к выходу второго алгебраического сумматора, вход обнуления которого подключен к выходу формирователя импульсов начальной установки, вход уменьшаемого связан с выходом задатчика номинального значения, а вход вычитаемого является одним из информационных входов приемного блока группы, выходы управления Сложение-вычитание которого соединены с входами управления Сложение-вычитание второго ал. гебраического сумматора и подключены к второй группе выходов второго коммутатора.

Каждый технологический параметр имеет номинальное значение, и задача автоматизированного контроля и управления при этом заключается в контроле отклонения параметра от номинального значения и управлении технологическим процессом с целью уменьшения этого отклонения до минимального значе- ния, т.е. обеспечение номинального значения контролируемого параметра в технологическом процессе. Поэтому ин45 формативным является не абсолютное значение котролируемого параметра, а отклонение его значения от номинального, которое обычно (при нормальных технологических процессах)

50 намного меньше номинального и абсолютного (текущего) значения. Исходя из этого задачи контроля и управления технологическими процессами можно решать на основе контроля отклонения технологического параметра от номинального значения этого параметра. Последнее позволяет уменьшить время обработки результата контроля,

30

35

40

55

поскольку при этом разрядность вход- ных кодов намного меньше. В этом и заключается сущность предлагаемого устройства, т.е. на реверсивном счет чике записываются коды, соответствующие отклонениям контролируемых параметров от их номинальных значений, полученные в результате вычитания соответствующих кодов на первом алгебраическом сумматоре цифровых кодов. Далее записанная в реверсивный счетчик информация переносится в приемные блоки. В приемных блоках коды, соответствующие отклонениям и номинальным значениям, суммируются с помощью второго алгебраического сумматора, и код, соответствующий значению контролируемого параметра, записывается на регистр.

Исходя из изложенного выше время опроса одного датчика в предлагаемом устройстве может определяться следующим образом:

топ Т,ЬК +Јв +ЈС + С,

где & К - десятичное значение максимально допустимого отклонения кода от номинального; t-б - время вычитания кодов; Ј0 - время суммирования кодов. С учетом того, что Јв Јс 25 не и Т,Ь20 не, можем принять Qu tJc Т, . Тогда

Топ Т1 Л К + 2Т + Ј

Поскольку Т, и &К К - , то получим

т,(к - к„) + 32,

выражений (1) и (3) видно, что

i

on

т

on

Таким образом, сопоставительный анализ с известным устройством позволяет сделать вывод, что предлагаемое устройство обеспечивает повышение быстродействия при увеличении числа датчиков и приемников, обслуживаемых этим устройством.

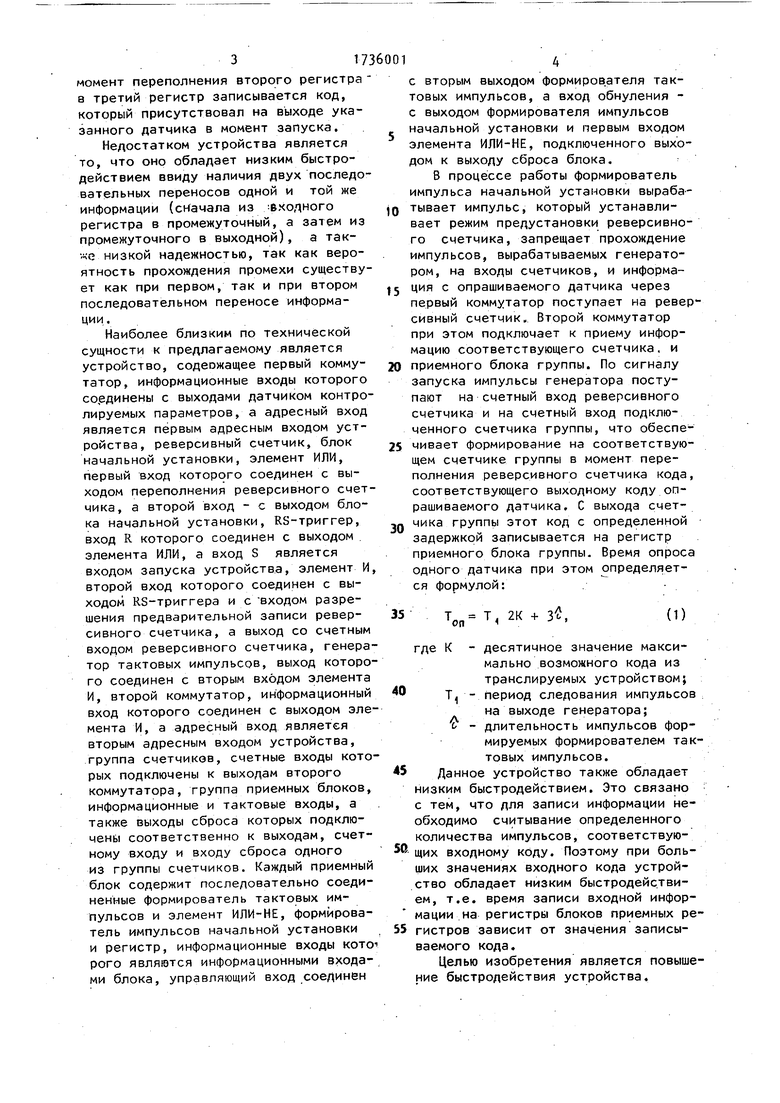

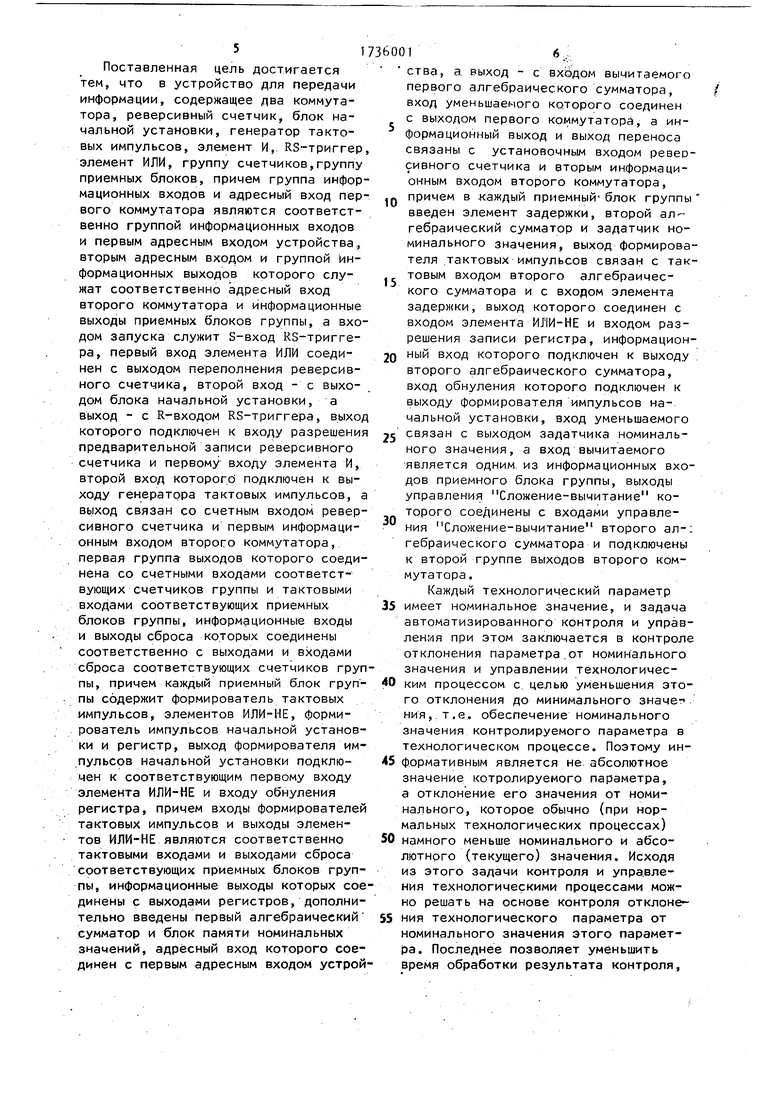

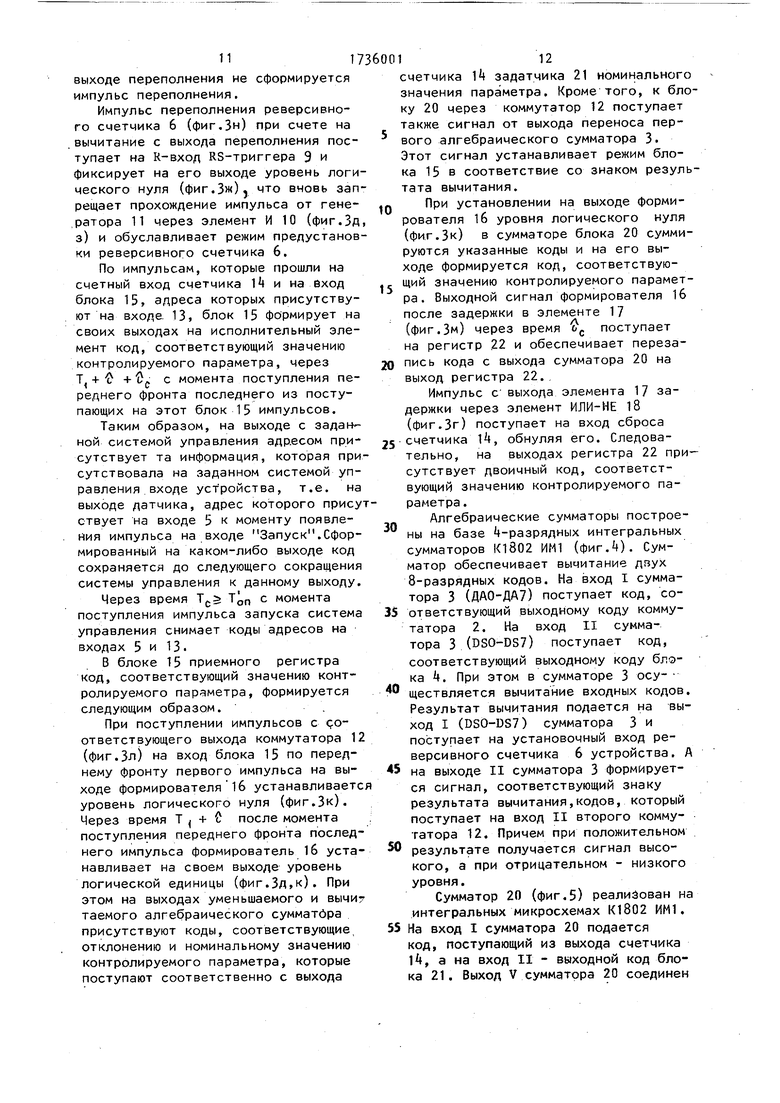

На фиг.1 приведена структурная схема устройства; на фиг.2 - функциональная схема блока приемных регистров; на фиг.З временные диаграммы

сигналов в устройстве; на фиг. - схема первого алгебраического сумматора; на фиг.З - схема второго алгебраического сумматора.

Устройство содержит датчики 1 контролируемых параметров, первый коммутатор 2, информационные входы которого соединены с выходами датчиtO ков контролируемых параметров, первый алгебраический сумматор 3, вход уменьшаемого которого соединен с выходом первого коммутатора 2, блок 4 памяти номинальных значений контро15 лируемых параметров, выход которого соединен с входом вычитаемого первого алгебраического сумматора 3, первый адресный вход 5, реверсивный счетчик 6, установочный вход которого соеди20 нен с выходом первого алгебраического сумматора 3, блок 7 начальной установки, элемент ИЛИ 8, первый вход которого соединен с выходом переполнения реверсивного счетчика 6, а вто25 РОЙ вход - с выходом блока 7 начальной установки, RS-триггер 9, вход которого соединен с выходом элемента ИЛИ 8, а вход соединен с входом запуска устройства, элемент И 10, первый

,Q вход которого соединен с выходом RS-триггера 9 и с входом разрешения предварительной записи реверсивного счетчика 6, генератор 11 тактовых импульсов, выход которого соединен с вторым выходом элемента И 10, вто35 рой коммутатор 12 второй информационный вход которого соединен с выходом переноса первого алгебраического сумматора 3, а первый информационный вход - с выходом элемента И 10, вто рой адресный вход 13, группу счетчиков 1, счетные входы которых подключены к первым выходам второго коммутатора 12, группу приемных блоков 15, информационные и тактовые входы,

5 а также выходы сброса которых подключены соответственно к выходам, счетному входу и входу сброса одного из счетчиков группы. При этом i адресный вход первого коммутатора 2

50 и блока Ц памяти номинальных значений подключены к первому адресному входу 5, адресный вход коммутатора 12 подключен к второму адресному вхо ДУ 13 а вторые выходы коммутатора

55 12 соединены со входами управления Сложение-вычитание приемных блоков 15.

Каждый приемный блок 15 содержит последовательно соединенные формиро атель 16 тактовых импульсов, элемен 17 задержки, а также элемент ИЛИ- НЕ 18, выход которого является выходом сброса блока 15, формирователь 19 импульса начальной установки, выход которого соединен с первым входом элемента ИЛИ-НЕ 18, второй алгебраический сумматор 20, вход вычитаемого которого является одним из информационных входов блока 15, а вход управления Сложение-вычитание соединен с входом управления Сложение-вычитание блока 15. задатчик 21 номинального значения соответствующего контролируемого параметра, выход которого соединен с входом уменьшаемого второго алгебраического сумматора 20, тактовый вход которого соединен с выходом формирователя 16 тактовых импульсов, регистр 22, информационный вход которого соединен с выходом второго алгебраического сумматора 20, а вход обнуления соединен с входом обнуления второго алгебраического сумматора 20 и подключен к выходу формирователя 19 импульса начальной установки, вход разрешения записи регистра 22 соединен с выходом элемента 17 задержки.

Устройство работает следующим образом.

При подаче на устройство питающего напряжения блок 7 начальной установки вырабатывает импульс (фиг.36), который через элемент ИЛИ 8 (фиг.Зв) поступает на R-вход RS-триггера З и фиксирует на его выходе уровень логического нуля (фиг.Зж), что устанавливает режим предустановки реверсивного счетчика 6 и запрещает прохожде- ние импульсов, вырабатываемых генератором 11 на выход элемента И 10 (фиг.). В приемных блоках 15 в это же время формирователи 19 импульса начальной установки вырабатывают импульс (фиг.36), который обнуляет вторые алгебраические сумматоры 20 и регистры 22 и.пройдя через элемент ИЛИ-НЕ 18 (фиг.Зг) на входы сброса счетчиков 1, устанавливает их в нуль.

По истечении времени t (фиг.36) после момента подачи напряжения питания на устройство на выходах бло- )ка 7 и формирователей 19 устанавливается уровень логического нуля, после чего устройство принимает управляющие сигналы от системы управления

ьи (лш

Системой управления, в качестве которой можно использовать ЭВМ, или с диспетчерского пульта сначала задают на выходе 5 адрес того датчика 1, на котором присутствует информация, и на входе 13 адрес выхода,на который требуется перенести эту информацию. При этом информация с опраJQ шиваемого датчика 1 через первый коммутатор 2 поступает на вход уменьшаемого первого алгебраического сумматора 3. На вход вычитаемого первого алгебраического сумматора 3 из блока

.г памяти номинальных значений контролируемых параметров поступает код, соответствующий номинальному значению контролируемого параметра. На выг ходе алгебраического сумматора 3 фор20 мируется код, соответствующий отклонению значения конт-ролируемого параметра от его номинального значения, которой поступает на установочный вход реверсивного счетчика 6. Посколь25 ку реверсивный счетчик 6 находится в режиме предустановки, то в него записывается двоичный код, соответствующий отклонению контролируемого параметра от номинального значения.

Кроме того, второй коммутатор 12 соединяет выход элемента И 10 с входом того из блоков 15 и счетчиков И, которым присвоен адрес, присутствующий на адресном входе 13, а также выход переноса первого алгебраи35 ческого сумматора с входом управления Сложение-вычитание приемного блока 15.

После этого система управления выдает на вход Запуск импульс (фиг.Зс), который фиксирует на выходе RS-триггера 9 уровень логической единицы (фиг.Зг), что обусловливает режим реверсивного счетчика 6 и разрешает прохождение импульсов

5 с генератора 11 через элемент И 10 (фиг.).

Импульсы с выхода элемента И 10 поступают на счетный вход реверсив- «j ного счетчика 6 и через второй коммутатор 12 на вход того из счетчиков 11 и блоков 15, адреса которых присутствуют на входе 13.

С Каждым импульсом, поступающим 55 на счетный-вход, реверсивный счетчик 6 уменьшает свое содержимое на единицу до тех пор, пока все его разряды не станут равными нулю и на его

30

40

И173600

выходе переполнения не сформируется импульс переполнения.

Импульс переполнения реверсивного счетчика 6 (фиг.Зн) при счете на вычитание с выхода переполнения пос- тупает на К-вход RS-триггера 9 и фиксирует на его выходе уровень логического нуля (фиг.Зж). что вновь запрещает прохождение импульса от гене

ратора 11 через элемент И 10 (фиг.Зд з) и обуславливает режим предустановки реверсивного счетчика 6.

По импульсам, которые прошли на счетный вход счетчика И и на вход блока 15, адреса которых присутствуют на входе 13, блок 15 формирует на своих выходах на исполнительный элемент код, соответствующий значению контролируемого параметра, через Т{ + Ј + Dp с момента поступления переднего фронта последнего из поступающих на этот блок 15 импульсов.

Таким образом, на выходе с заданной системой управления адресом при- сутствует та информация, которая присутствовала на заданном системой управления входе устройства, т.е. на выходе датчика, адрес которого присуствует на входе 5 к моменту появления импульса на входе Запуск.Сформированный на каком-либо выходе код сохраняется до следующего сокращения системы управления к данному выходу.

Через время Тс Т оп с момента поступления импульса запуска система управления снимает коды адресов на входах 5 и 13.

В блоке 15 приемного регистра код, соответствующий значению контролируемого параметра, формируется следующим образом.

При поступлении импульсов с соответствующего выхода коммутатора 12 (фиг.Зл) на вход блока 15 по переднему фронту первого импульса на вы- ходе формирователя 16 устанавливаетс уровень логического нуля (фиг.Зк). Через время Т + С после момента поступления переднего фронта последнего импульса формирователь 16 уста- навливает на своем выходе уровень логической единицы (фиг.3д,к). При этом на выходах уменьшаемого и вычиг таемого алгебраического сумматора присутствуют коды, соответствующие отклонению и номинальному значению контролируемого параметра, которые поступают соответственно с выхода

0

, 0

5

5

0

5 0 5

112

счетчика 1 задатчика 21 номинального значения параметра. Кроме того, к блоку 20 через коммутатор 12 поступает также сигнал от выхода переноса первого алгебраического сумматора 3. Этот сигнал устанавливает режим блока 15 в соответствие со знаком результата вычитания.

При установлении на выходе формирователя 16 уровня логического нуля (фиг.Зк) в сумматоре блока 20 суммируются указанные коды и на его выходе формируется код, соответствующий значению контролируемого параметра. Выходной сигнал формирователя 16 после задержки в элементе 17 (фиг.Зм) через время Јс поступает на регистр 22 и обеспечивает перезапись кода с выхода сумматора 20 на выход регистра 22.

Импульс с выхода элемента 1 задержки через элемент ИЛИ-НЕ 18 (фиг.Зг) поступает на вход сброса счетчика И, обнуляя его. Следовательно, на выходах регистра 22 присутствует двоичный код, соответствующий значению контролируемого параметра .

Алгебраические сумматоры построены на базе -разрядных интегральных сумматоров К1802 ИМ1 (фиг.1). Сумматор обеспечивает вычитание дяух 8-разрядных кодов. На вход I сумматора 3 (ДАО-ДА7) поступает код, соответствующий выходному коду коммутатора 2. На вход II сумматора 3 (DSO-DS7) поступает код, соответствующий выходному коду блока k. При этом в сумматоре 3 осу- ществляется вычитание входных кодов. Результат вычитания подается на выход I (DSO-DS7) сумматора 3 и поступает на установочный вход реверсивного счетчика 6 устройства. А на выходе II сумматора 3 формируется сигнал, соответствующий знаку результата вычитания,кодов, который поступает на вход II второго коммутатора 12. Причем при положительном результате получается сигнал высокого, а при отрицательном - низкого уровня.

Сумматор 20 (фиг.5) реализован на интегральных микросхемах К1802 ИМ1. На вход I сумматора 20 подается код, поступающий из выхода счетчика И, а на вход II - выходной код блока 21 . Выход V сумматора 20 соединен

131

с выходом формирователя 16. При поступлении с выхода формирователя 16 сигнала высокого уровня, который подается на управляющие входы STB интегральных сумматоров, входные регистры сумматоров становятся прозрачными и коды, имеющиеся на входах I (DAO - DA7) и II (DBO - DB7), поступают на суммирующие матрицы интегральных сумматоров. При этом на вход IV сумматора 20, который соединен с выходом I коммутатора 12, поступает сигнал знака результата вычитания кодов в сумматоре 3. Если результат i. вычитания отрицательный (положительный) то, на вход IV сумматора 20 поступает сигнал низкого (высокого) уровня, который подается на управляющие входы ОРА интегральных сумматоров. Поскольку на входы ОРА сумматоров поступил сигнал низкого (высокого) уровня, они работают в режиме сложения (вычитания). Таким образом, в зависимости от уровня сигнала, поступающего из выхода I коммутатора 12, в сумматоре 20 устанавливается режим сложения или вычитания.

Обнуление сумматора 20 осуществляется при поступлении от формирователя 19 сигнала высокого уровня. Поскольку вход III сумматора 20 соединен с выходом формирователя 19, этот сигнал поступает на управляющие входы EDB интегральных сумматоров, и поэтому во все разряды вторых регистров сумматоров записываются нули. Кроме этого выходной сигнал формирователя 19 через элемент ИЛИ- НЕ 18 поступает на счетчик k и сбрасывает его. Поэтому на входе I (DAO-DA7) сумматора 20 присутствует нулевой код. Соответственно, во все разряды первых регистров сумматоров также записываются нули. Таким образом обеспечивается обнуление сумматора 20.

В качестве блока памяти номинальных значений контролируемых параметров можно использовать программируем мые логические матрицы или известные интегральные ПЗУ и ППЗУ. Второй коммутатор 12 предлагаемого устройства может быть построен на базе двух параллельно включенных коммутаторов, идентичных второму коммутатору известного устройства. Задатчиками но минальных значений контролируемых na

0

01

14

раметров могут служить программны переключатели типа ПП10-ХВ.

В качестве остальных узлов предлагаемого устройства можно исполь- 1

зовать узлы, идентичные использованным в известном устройстве.

Таким образом, предлагаемое устройство обеспечивает сокращение времени переноса дискретных значений параметров от наперед выбранного датчика на наперед выбранный приемник, что позволяет увеличить число датчиков и приемников, обслуживае- 5 мых этим устройством, или увеличить частоту обращения к каждому датчику, что в свою очередь, позволяет приблизиться к регистрации мгновенных значений параметров,

0

5

0

5

0

5

O

5

Формула изобретения

Устройство для передачи информации, содержащее два коммутатора, реверсивный счетчик, блок начальной установки, генератор тактовых импульсов, элемент И, RS-триггер, элемент ИЛИ, группу -счетчиков, группу приемных блоков, причем группа информационных входов и адресный вход первого коммутатора являются соответственно группой информационных входов и первым адресным входом устройства, вторым адресным входом и группой информационных выходов которого служат соответственно адресный вход второго коммутатора и информационные выходы приемных блоков группы, а входом запуска служит S-вход КЗ-триггера, первый вход элемента ИЛИ соединен с выходом переполнения реверсивного счетчика, второй вход - с выходом блока начальной установки, а выход - с К-входом RS-триггера, выход которого подключен к входу разрешения предварительной записи реверсивного счетчика и первому входу элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, а выход связан со счетным входом реверсивного счетчика и первым информационным входом второго коммутатора, первая группа выходов которого соединена со счетными входами соответствующих счетчиков группы и тактовыми входами соответствую щих приемных блоков группы, информационные входы и выходы сброса которых соединены соответственно с выходами и входами сброса соответствующих счетчиков группы, причем каждый приемный блок группы содержит формирователь тактовых импульсов, элемент ИЛИ-НЕ, формирователь импульсов начальной установки и регистр выход формирователя импульсов начальной установки подключен к соответствующим первому входу элемента ИЛИ-НЕ и входу обнуления регистра, причем вход формирователей тактовых импульсов;и выходы элементов ИЛИ-НЕ являются соответственно тактовыми входами и выходами сброса соответствующих приемных блоков группы, информационные выходы которых соединены с выходами регистров, отличающееся тем, что, с целью повышения быстродействия, в устройство введены первый алгебраический сумматор и блок памяти номинальных значений, адресный вход которого соединен с первым адресным входом устройства, а выход - с входом вычи- таемого первого алгебраического сумматора, вход уменьшаемого которого соединен с выходом первого коммутатора, а информационный выход и выход

5

5

0

переноса связаны с установочным входом реверсивного счетчика и вторым информационным входом второго коммутатора, причем в каждый приемный блок группы введен элемент задержки, второй алгебарический сумматор и задатчик номинального значения, выход формирователя тактовых импульсов связан с тактовым входом второго алгебраического сумматора и с входом элемента задержки, выход которого соединен с входом элемента ИЛИ-НЕ и входом разрешения записи регистра, информационный вход которого подключен к выходу второго алгебраического сумматора, вход обнуления которого подключен к выходу формирователя импульсов начальной установки, вход уменьшаемого связан с выходом задат- чика номинального значения, а вход вычитаемого является одним из информационных входов приемного блока группы, входы управления Сложение-вычитание п которого соединены с входами управления Сложение-вычитание второго алгебраического сумматора и подключены к второй группе выходов второго коммутатора.

I

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство приема телеметрической информации | 1989 |

|

SU1735883A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1361577A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВУХ ПЕРЕМЕННЫХ | 1984 |

|

SU1371306A1 |

| Экстраполятор видеосигнала изображения | 1989 |

|

SU1718246A1 |

Изобретение может быть использовано в автоматизированных системах .контроля и управления технологическими процессами и производством. Цель изобретения - повышение быстродействия устройства. Последнее содержит два коммутатора, реверсивный счетчик, блок начальной установки, генератор тактовых импульсов, элемент И, RS-триггер, элемент ИЛИ, группу счетчиков, первый алгебраический сумматор, блок памяти номинальных значений, группу приемных блоков. Каждый приемный блок содержит формирователь тактовых импульсов, элемент ИЛИ-НЕ, формирователь импульсов начальной установки, регистр, элемент задержки, второй алгебраический сумматор и задатчик номинального значения. 5 ил. S

, )

Kl€

. 2

I

о 13 у;туел

I Г

Л

/3

«

I

т

Рсг. /

07/У

)

4Z w

i и in

-я.Ъ- 010

y/fc/

1009 I

Л 20

J (i&o+ogo) /7 Й

ЈX&iSCj

pats &.tsSxzx-XX

/OJ

/л tw

/tn

JcfO (fcfO

OQS J03 $03 1/03

too

00.4

ЈУО

фг/ I

//

6W

0ЭО

|

ffa

WC

J. tsa-t

г и/о и

(tt/ff- &t/O)l

Q9i У

u

we Ш5 SXi$ n&

Ja.- Jos- J&. J#J

Ocfo J&O 900

003 ЭОЭ 003 УОЭ

Ј00

HO

OOQ

ОЭО

VH

f&Q OQQ

#a

9bz.S

| Устройство для контроля параметров объекта | 1978 |

|

SU697979A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для контроля параметров объекта | 1983 |

|

SU1164670A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| ( УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ | |||

Авторы

Даты

1992-05-23—Публикация

1989-12-06—Подача