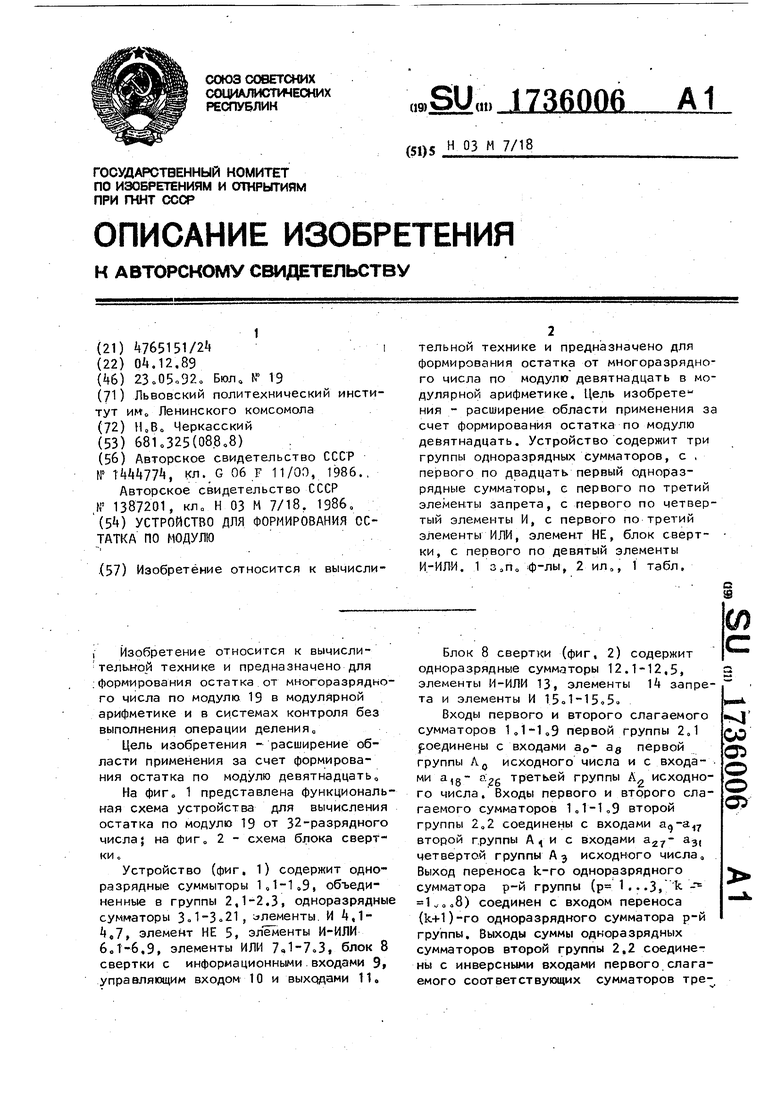

, Изобретение относится к вычислительной технике и предназначено для формирования остатка от многоразрядного числа по модулю 19 в модулярной арифметике и в системах контроля без выполнения операции деления„

Цель изобретения - расширение области применения за счет формирования остатка по модулю девятнадцать,

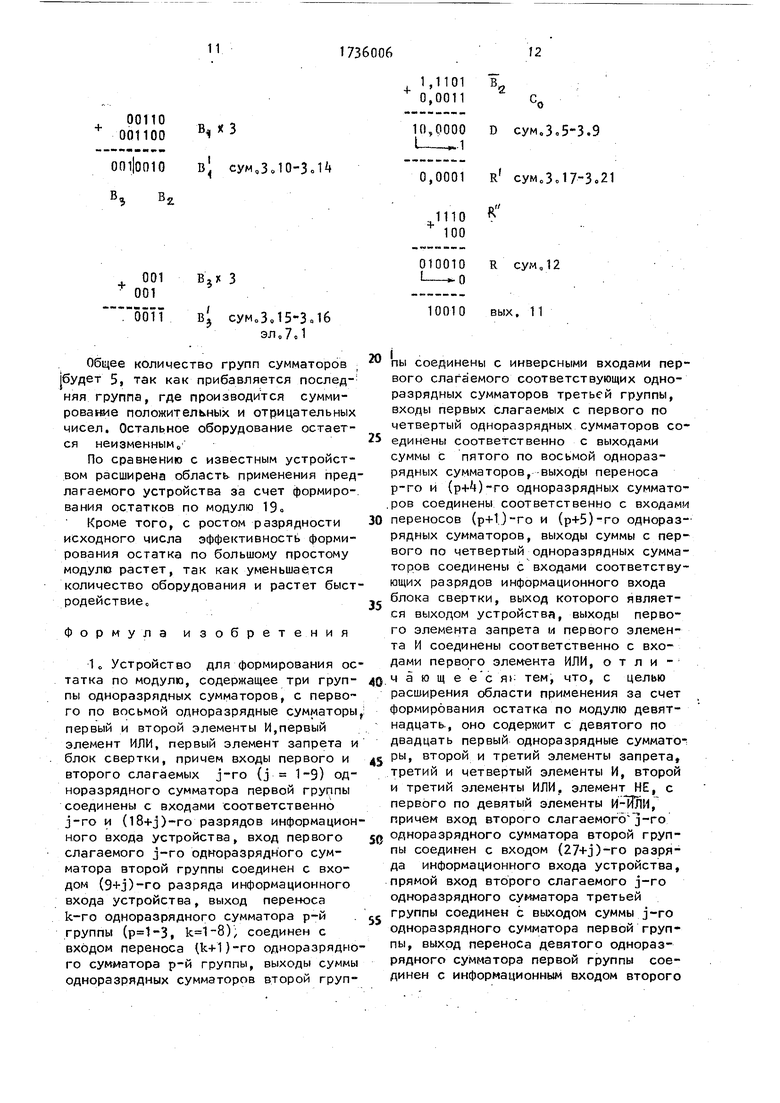

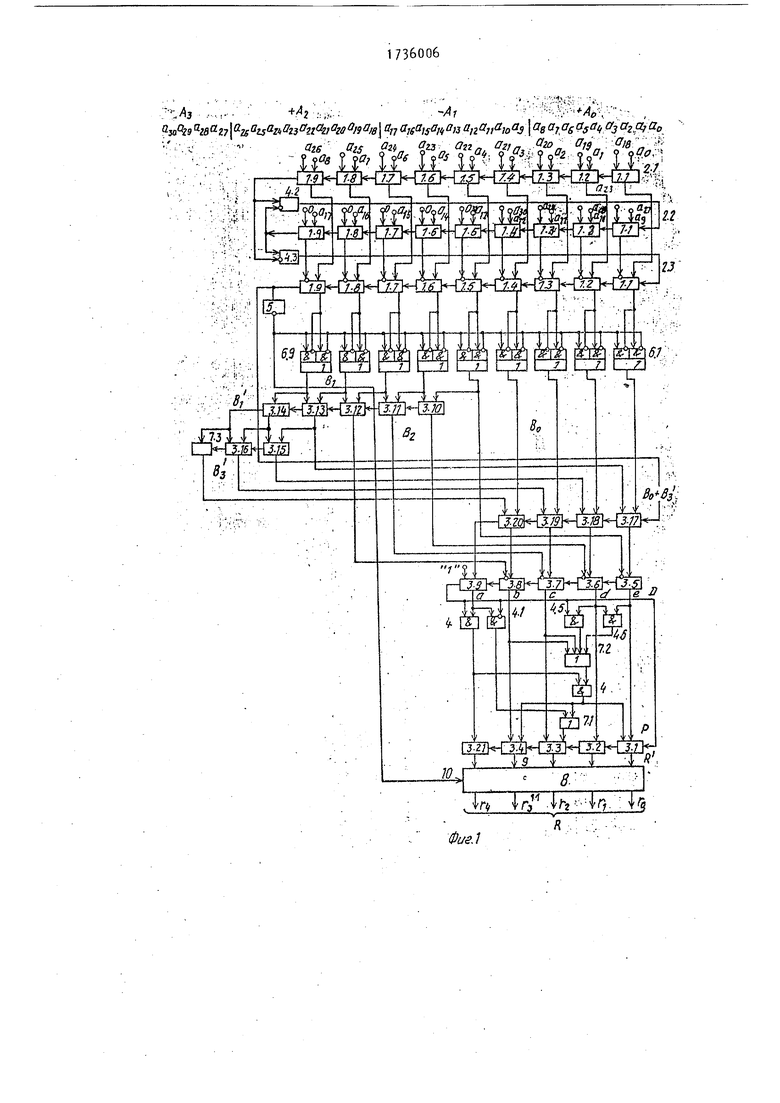

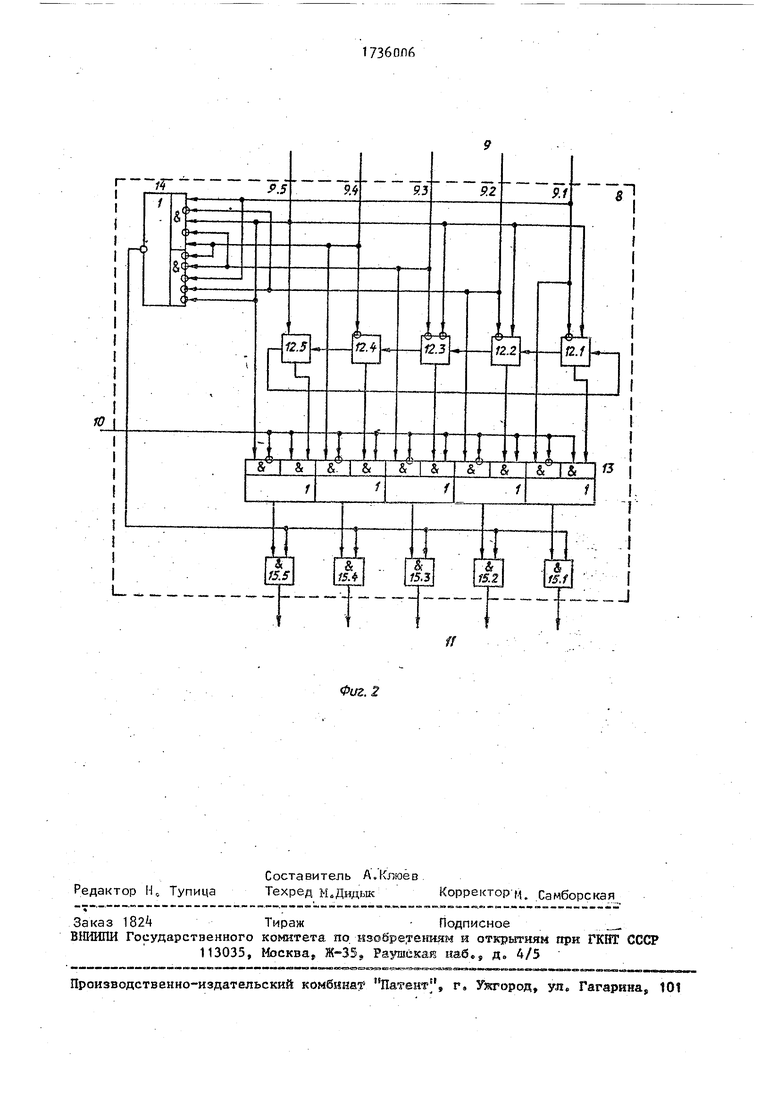

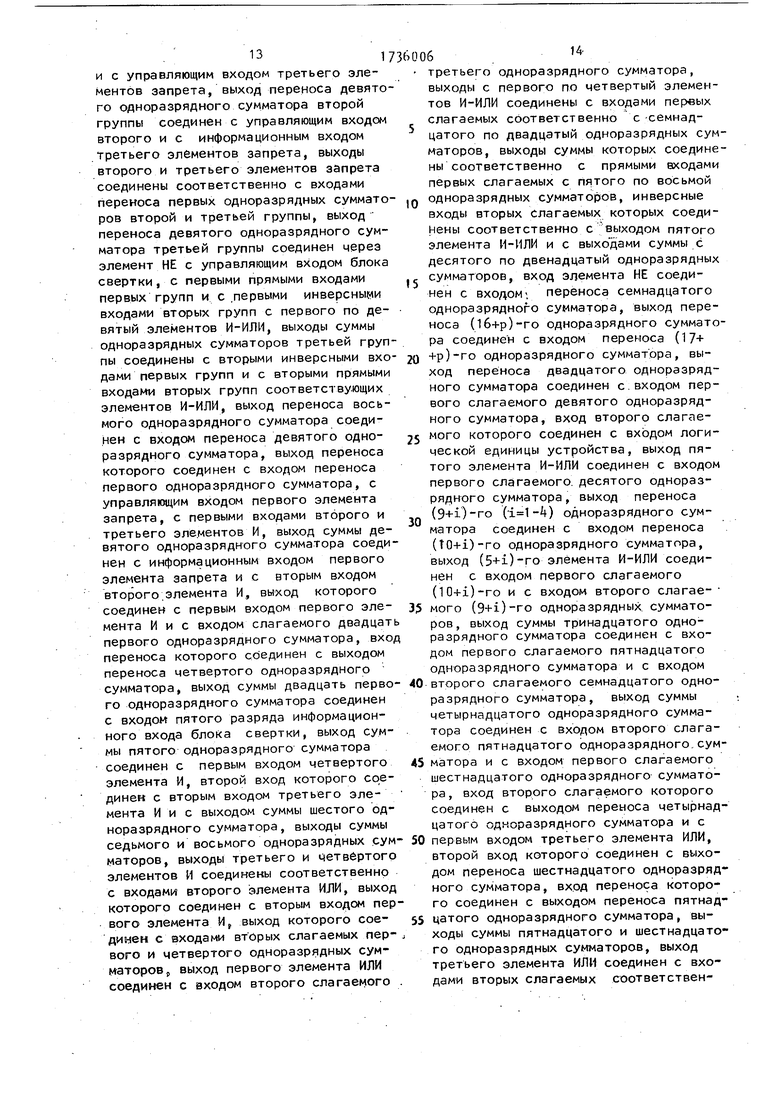

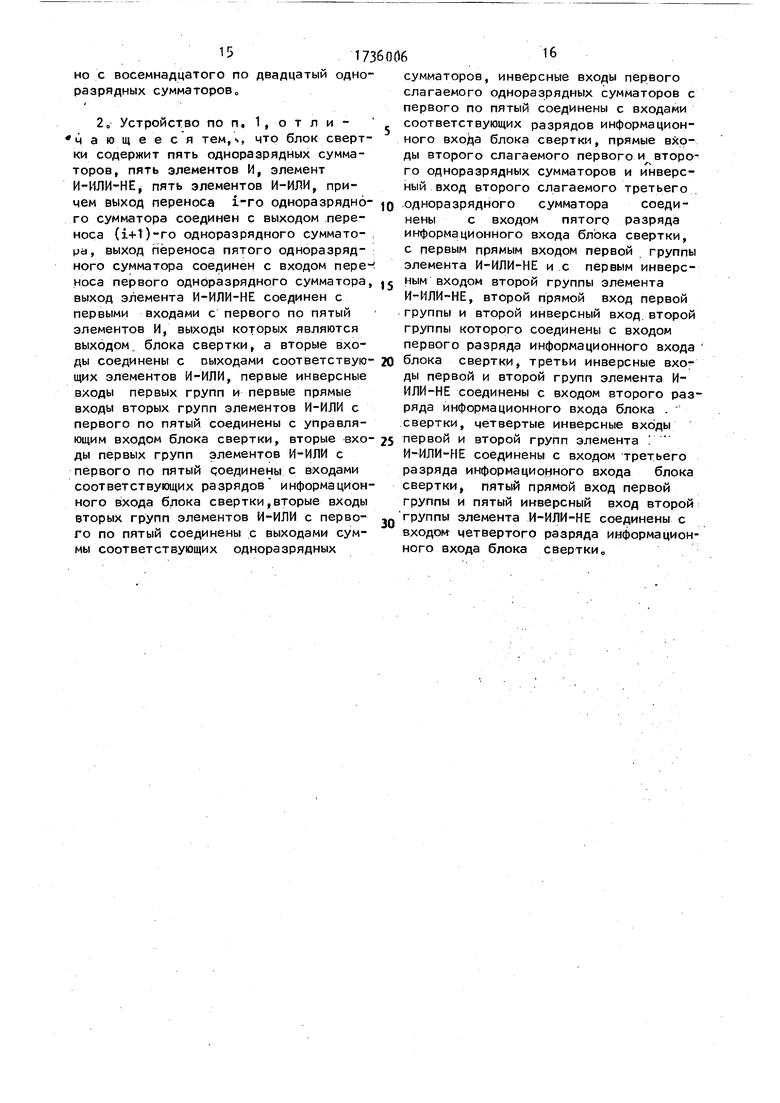

На фиг о 1 представлена функциональная схема устройства для вычисления остатка по модулю 19 от 32-разрядного числа; на фиг 2 - схема блока свертки «

Устройство (фиг, 1) содержит одноразрядные суммыторы 1,1-1,9, объединенные в группы 2,1-2.3, одноразрядные сумматоры , -элементы И 4,1- 4,7, элемент НЕ 5, эл ё менты И-ИЛИ 6.1-6,9, элементы ИЛИ 7J-7..3, блок 8 свертки с информационными входами 9, управляющим входом 10 и выходами 11,

Блок 8 свертки (фиг, 2) содержит одноразрядные сумматоры 12.1-12,5, элементы И-ИЛИ 13, элементы 14 запрета и элементы И 15,1-15,5,

Входы первого и второго слагаемого сумматоров 1,1-1,9 первой группы 2,1 роединены с входами а0- а8 первой группы А0 исходного числа и с входами a1g- о 26 третьей группы А- исходного числа. Входы первого и второго слагаемого сумматоров 1,1-1,9 второй группы 2,2 соединены с входами a j-a17 второй группы А 1 и с входами a3( четвертой группы АЗ исходного числа. Выход переноса k-ro одноразрядного сумматора р-й группы (р 1...3, k - 1,,8) соединен с входом переноса (k+1)-го одноразрядного сумматора р-й группы. Выходы суммы одноразрядных сумматоров второй группы 2,2 соединены с инверсными входами первого слагаемого соответствующих сумматоров тре-vj

оэ CD

о

3173

тьей группы 2,3, входы второго слагаемого сумматора этой группы соединены с выходами сумматоров первой группы 2d, Выход переноса сумматора 1«9 первой группы 2„1 соединен с первым входом элемента И 4.1 и с первым инверсным входом элемента И 402„ Выход элемента И 4d соединен с входом переноса сумматора 1.1 второй группы 2,1„ Выход переноса сумматора 1 .9 второй группы 2.2 соединен с вторым инверс- ь м входом элемента И 4,2, выход которого соединен с входом переноса сумматора 101 третьей группы 203о

Выход переноса сумматора 1„9 третьей группы 203 соединен с входом элемента НЕ 5 и входом переноса сумматора Зс1. Выход элемента НЕ 5 соединен с управляющим входом 10 блока 8 свертки и с первыми прямыми входами первых групп И, и с первыми инверсными входами вторых групп И элементов И-ИЛИ 6.1-6.9. Выходы сумм сумматоров третьей группы 203 соединены с вторыми инверсными входами первых групп И и вторыми прямыми входами вторых групп И элементов И-ИЛИ 6„

Выходы элементов И-ИЛИ 6о1-6,4 соединены с входами первого слагаемого сумматоров Зе1-3.4. Выходы элементов И-ИЛИ бсб-6.9 соединены с входами первого и второго слагаемого соответственно сумматоров 3dO-3d4e Выход элемента И-ИЛИ 6.5 соединен с входом второго слагаемого сумматора и с инверсным входом первого слагаемого сумматора„ В группах сумматоров 3.10-3.Т, 3.15 и 3J6, 3.1-3.,

Выход переноса 1-го одноразрядного сумматора 12,1-12,5 (,«0.,4) блока 8 свертки (фиг0 2) соединен с входом переноса (i+1)-ro сумматора,

Зс5-3°9 и 3J7-3.21 вход переноса пре- 40 Выход переноса сумматора 1205 соедидыдущего сумматора соединен с выходом переноса последующего сумматора. Выходы суммы сумматоров 3d0-3.12 соединены с инверсными входами первых слагаемых сумматоров .8, Выход суммы сумматора 3d3 соединен с первым входом сумматора 3d5 и с входом второго слагаемого сумматора 3d о Выход суммы сумматора 3.14 соединен с

нен с входом переноса сумматора 12010 Выход элемента 14 запрета соединен с первыми входами элементов И 15.1-15.5, выходы которых являются выходами 11 45 устройства, а вторые входы соединены с выходами элементов И-ИЛИ 13 Инверсные управляющие входы первых групп элементов И-ИЛИ 13 и прямые и управляющие входы вторых групп элементов

.входами сумматоров 3d 5 и 3.16. Выход 50 И-ИЛИ 13 соединены с управляющим входом 10. Информационные входы первых групп элементов 13 соединены с информационными входами 9 блока свертки, а информационные входы вторых гру/пп сое- 55 динены с выходами суммы сумматоров Т2„ Инверсные входы первого слагаемого сумматоров 12 соединены с соответствующими информационными входами 9 блопереноса сумматора 3.14 соединен с входом второго слагаемого сумматора 3.16 и с первым входом элемента ИЛИ 7.1, второй вход которого соединен с выходом переноса сумматора 3.1бс Выходы суммы сумматоров 3.15 и 3.16 и выход элемента ИЛИ 7.1 соединены соответственно с входами второго слагаемого сумматоров .4.

Выходы суммы сумматоров 3.1-3.4 соединены с входами второго слагаемого сумматоров . Выход переноса сумматора 3.4 соединен с входом первого слагаемого сумматора 3.9, к второму входу которого подключена Выход переноса сумматора 3.9 соединен с входами элементов И 4,3, 4 „4, 4 „5 и с входом переноса сумматора 3.17. Выход сумматора 3.5 соединен с входом элемента И 4.6 и с входом первого слагаемого сумматора 3d 7.

Выход суммы сумматора Зоб соединен с входами элементов И 4„5 и 4.6 и с входом сумматора 3.18„ Выход сумматора 3.7 соединен с входом первого слагаемого сумматора 3«20 и с первым входом элемента ИЛИ 7.2, второй вход

которого соединен с выходом элемента И 4.5, третий - с выходом элемента И 4.6, а четвертый - с выходом суммы сумматора 3.8 и с входом первого слагаемого сумматора 3,20. Второй вход

слагаемого сумматора 3.20 соединен с входом элемента ИЛИ 7-3, выходом элемента И 4.7 и входом второго слагаемого сумматора 3.17 Выход суммы сумматора 3.9 соединен с вторыми входами элементов И 4„3 и 4.4, а через них - с входом сумматора 3.21, вторым входом элемента И 4„7 и вторым входом элемента ИЛИ 7.3. Выходы суммы сумматоров .2l являются информационными входами 9 блока 8

свертки.

Выход переноса 1-го одноразрядного сумматора 12,1-12,5 (,«0.,4) блока 8 свертки (фиг0 2) соединен с входом переноса (i+1)-ro сумматора,

Выход переноса сумматора 1205 соединен с входом переноса сумматора 12010 Выход элемента 14 запрета соединен с первыми входами элементов И 15.1-15.5, выходы которых являются выходами 11 устройства, а вторые входы соединены с выходами элементов И-ИЛИ 13 Инверсные управляющие входы первых групп элементов И-ИЛИ 13 и прямые и управляющие входы вторых групп элементов

И-ИЛИ 13 соединены с управляющим входом 10. Информационные входы первых групп элементов 13 соединены с информационными входами 9 блока свертки, а информационные входы вторых гру/пп сое- динены с выходами суммы сумматоров Т2„ Инверсные входы первого слагаемого сумматоров 12 соединены с соответствующими информационными входами 9 бло517360066

ка 8, Вход второго слагаемого сумма- мента 14 соединены с информационным торов 12„1 и 12„2 и инверсный вход входом 9«2,

второго слагаемого сумматора 12„3 сое- Четвертые инверсные входы первой динены с информационным входом 9.5, с , .и второй групп элемента 1 соединены ( первым входом первой группы элемента с информационным входом 9оЗа Пятый 14 запрета и с первым инверсным вхо- вход первой группы и пятый инверсный дом второй группы элемента 14, вто- вход второй группы элемента 14 сое- ррй вход первой группы и второй ин- динен с информационным входом 9«4„ версный вход второй группы которого JQ Устройство работает следующим об- соединены с информационным входом 9.1 разом„

Третий инверсный вход первой и второй Пусть задано 32-разрядное число, групп элемента 1 соединены с информа- , 30 4 0 ционным входом 9.2 Четвертые инверс- А а31 2 +aJ023o + .. ,а22 .+ а, 2 +а02 , ные входы первой и второй групп эле- (1)

Можно преобразовать (1)

A(a02°+a,2UaQa+a727+a828)+29(al,20+aAo24oai+a1627+air28) +

АЛЛи)7 л4

+2 (ач82 +ооо+а262 )+2 (а27 2°4-0,0+а 2 ) 0(2)

.

Обозначим числа, заключенные -вНайдем остаток числа А по модулю 19о

скобках, :через символы А0, А,, Аг, А3.

в той последовательности, в которой AQ+2 А, +2 А2+2гГА3 19, ()

они записаны в (2). Тогда

25 В таблице приведены значения А1+2(8А2- -227Азо(3)татков 2. i 1,90.-,31 по модулю 19

..,„.....-.г.-.-...--.----..--;------.-----о--™ 2,8 2,,2zo

+ 1 2 0 8 16 13 7, 14 9 18 17 15 11 3 6+12 5 10 1 2 4 -;10 17 15 11 3 6 12 5 Ю / 1 2 4 8 16 13 -7 И 9 18 17 15В соответствии с данными таблицыДля этого используем полусумматоры

1„1-1о9 первой 2„Т и второй групп A0- Ач+ At- .(5) 35 (фиг, 1) „

Найдем сумму положительных и отри-Каждая в отдельности сумма может

цательных чисел.быть больше 9 разрядного числа на один

разряд F +(А0+А2) и G .-(А(+А3)„

- F f02°+00.+f8.28+f929 f02° + 0,0+fg28- f9,

( G -(g02V004.g823+g929) -(g02°+.0, g9)0

Таким образом, разряд каждой 45 группы 2.2 сумматоров. Если f9 О, суммы, если он существует, имеет вес a ga -1, тр go (выход переноса сум- младшего разряда, так как по. таблице матора Т.,9 второй группы 2,2 суммато- . 2 -1,ров) подсуммируется по младшему разРазность F - G находим, суммируя ряду сумматора 1.1 третьей группы 2.3 содержание сумматоров первой группы 50 сумматоров. Нетрудно убедиться, что 2„1 с офатным кодом на сумматорах использование элементов И 4,1 и 4,2 третьей 2.3 группы. Если f -1, позволяет сократить время суммирова- g -1, то они взаимно компенсируются ния числа на трех сумматорах на 1/3. элементами И 4,1 и 4,2 и в получении

разности F - G не участвуют. Если 55 В результате описанных действий , a gx 0, то f9 (выход пере- получили на выходах сумматоров третьей носа сумматора 1,9 первой группы 2,1 группы 2,3 10-разрядное число - 9 раз- сумматоров) через элемент 4,1 подается РЯДОВ мантиссы и 1 - знак. Сигнал пена вход переноса сумматора 1,1 второй реполнения при суммировании прямого

717360068

и обратного кода (если он существует)Далее производится преобразование

подается на вход сумматора 3«1.9 разрядного числа в 5 разрядное для

После сумматоров третьей группы результат вновь преобразуется в пряполучения остатка по модулю 19

(ЕЦз 10011), Преобразование произвомой код с помощью элемента НЕ 5 и элементов И-ИЛИ 6„

получения остатка по модулю 19

(ЕЦз 10011), Преобразование произвоj

дится по следующему алгоритму„ Представим- число в виде i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования остатков по модулю | 1986 |

|

SU1387201A1 |

| Устройство для формирования остатков по модулю | 1986 |

|

SU1449986A1 |

| Устройство для приведения 1-кода Фибоначчи к минимальной форме | 1989 |

|

SU1665515A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Устройство для формирования остатков по модулю | 1986 |

|

SU1401610A1 |

| Устройство для формирования остатков по модулю | 1985 |

|

SU1397918A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Параллельный комбинационныйСуММАТОР | 1978 |

|

SU798827A1 |

| Устройство для формирования остатков по модулю | 1986 |

|

SU1444774A1 |

| Сумматор кодов с иррациональным основанием | 1991 |

|

SU1837279A1 |

Изобретение относится к вычислительной технике и предназначено для формирования остатка от многоразрядного числа по модулю девятнадцать в модулярной арифметике. Цель изобрете ния - расширение области применения за счет формирования остатка по модулю девятнадцать. Устройство содержит три группы одноразрядных сумматоров, с , первого по двадцать первый одноразрядные сумматоры, с первого по третий элементы запрета, с первого по четвертый элементы И, с первого по третий элементы ИЛИ, элемент НЕ, блок свертки, с первого по девятый элементы И-ЙЛИ. 1 з3п, ф-лы, 2 ил,, 1 табл.

,2t+bl22+b523+b,24+by25+b626+b727+b82e 19 b02°+b,24b22Z-(-b523 +2 (Ц20+Ь52 +Ь622+Ьг2а+Ь824 19

В(

По таблице 2 -3° Учитывая это, пере- j. Перемножение Bjj на 3 производим

на сумматорах 3.10-3,1 if., при этом может получиться 7-разрядное число, В или

пишем (7)

1A,9 dB0 -3В, 19 «СА,0 гв0 - В( 19

связи с этим произведем следующее преобразование

19

20

в; ь42Чь 2ЧЦ22+ь;23 + ъ аПь з +ь;о2

В

: -в2+зв, зв :-вг+Вз

Перемножение Вэ иа 3 производим на этом случае будет всегда положитель- сумматорах 3.15 и-3.16, получаем 4- Ным. Вычитание заменяется суммирова- разрядное произведение Схе- Нием числа D с дополнительным кодом ма ИЛИ 7.1 заменяет одноразрядный числа Т0011, который равен OU01 (13) сумматор. На вход элемента ИЛИ могут 30 Сформулируем условие, когда

0 10011 „ Результат на выходах сумматоров 3. является частичным, так как не учитывает сигнала переноса (переполнения), возникающего в сумма- 35 торе 3.9. Этот сигнал эквивалентен .L

единице младшего числа D, но на вход (сумматора Зо5 он не подключен из-за

А :В0-ЗВ, B0-B, L возможного самовозбуждения сумматоров

Этот сигнал подан на сумма- (10), 40 тор ЗЛ7. Обозначим его через р, Выход старшего разряда числа D (сумматор 3.9) обозначим чеРез а, выходы четырех младших разрядов числа D в порядке убывания его веса обозначим 4S через Ь, с, d, е„ Обозначим конъюнкцию а Л р f о

Выпишем условие х, при котором результат суммирования сумматоров Зо5

подаваться комбинации слагаемых, сумма которых не превышает единицы (0,1} 1,0j 0,0)0 Комбинация 1,1 невозможна, поэтому применяется вместо сумматора двухвходовой элемент ИЛИ.

Перепишем (7) с учетом (8) и (9)

:с0-вг в

Суммируем В0 с В на сумматорах Из полученного 3 разрядного результата С0 вычтем В2 на сумматорах 3., для чего В2 подадим в обратном коде. Число D на выходе этих сумматоров может быть:

а) положительным и большим или равЗс9 превосходит или равен 10011, 50 D 19 (D; отличается от D тем, что учитывает сигнал переполнения р)

х (b+c+de+dp)f.

(Ю

ным- 19 (D 10011),

б)положительным и меньшим 19 (D 10011),

в)дополнением до 15, Необходимо привести варианты представления вычетов а) и в) к единому

формату, а результат должен быть поло- Это логическое уравнение реализуется жительным и наименьшим остатком элементами И 4,5, 4„7 и элементом D 1001 КИЛИ 7.2.

Случай а). Если П s 10011, то необ- Случай в) „ При |В2| С о необходи- ходимо из D вычесть 19. Результат в мо результат о скорректировать дог

(7)

В

на сумматорах 3.10-3,1 if., при этом может получиться 7-разрядное число, В

связи с этим произведем следующее преобразование

„О ., Л

+ 2T(bg2g+b92 +b ,0 2Z) В2-ЗВ5

(9)

Зс9 превосходит или равен 10011, 50 D 19 (D; отличается от D тем, что учитывает сигнал переполнения р)

х (b+c+de+dp)f.

(Ю

полнением S до модуля m 19 Дополнение 8 19-15 (Ю04). Число BЈ является отрицательным по отношению

г

тельного остатка R в положительный

Обозначим входы 9.1-9.5 через г

гг г Г4« Если на входе 9-5 уста.)

ur

С0 1 -разрядным числом. При представ- новлена 1 (г 1), число R преоблении его в обратном коде необходимо к нему прибавить ka Если бы оно превышало 15, то как в случае а) дополнение было бы равно 32-19 13Дополнение D + необходимо при условии

разуется в число R

ff

ряды rl

в котором разинвертированы

г, flflf( I -, ; , ,

R г„ г, г, г. r0 - R r4 rj г,г„

- L Ltl-l

10

и к числу R

к

.1

прибавляется rA весом младшего разряда 2°„ В результате имеем

3 с

g - а А р

Так как дополнения ОТ101 и 100 имеют единицы в третьем разряде, то на второй вход сумматора с весом 100 сигнал от дополнения (условие 11) передается через схему ИЛИ 7. 5о

При у слови и 0 что lB2. аАр --1. Это логическое уравнение реализуется элементом И k,k В этом случае единица старшего разряда, снимаемая с выхода а сумматора 3,3, не должна поступать на вход сумматора 3.21 старшего разряда. Единица на этот вход поступает только при выполнении условия

f а Лр 1.

Это логическое уравнение реализуется на элементе И kfS,

На выходе,сумматоров 3.17-3.21 получаем 5-разрядный остаток R 10011. Знак остаУка z , определяется состоянием элемента НЕ 5, выход которого является управляющим сигналом 100 В блоке 8 при поступлении на вход 10 нулевого сигнала положительный остаток R проходит через элементы И-ИЛИ 13 и И 15 на выход 11 устройства, В этом случае R R.

Если на входе 10 единичный сигнал, го производится преобразование отрицаА« + 101001111

Аг 4- 110110011 1100000010

сум, 2,1

сум,2.3 эл. 6

6006

10

г

тельного остатка R в положительный

Обозначим входы 9.1-9.5 через г

гг г Г4« Если на входе 9-5 уста.)

ur

новлена 1 (г 1), число R преобновлена 1 (г 1), число R преобразуется в число R

ff

ряды rl

в котором разинвертированы

г, flflf( I -, ; , ,

R г„ г, г, г. r0 - R r4 rj г,г„

- L Ltl-l

10

и к числу R

к

.1

прибавляется rA весом младшего разряда 2°„ В результате имеем

3 с

V

Г4:

. 11

r +r +rV-f

«i2%

11

го

Rr 0 R + 100,

Если на входе образуется нуль (г 0), то к инвертированным четырем разрядам подсуммируется дополнение 100о Операция суммирования чисел

11 и 100 производится на сумматорах 12.1-12.3, на вторые входы которых подается сигнал от входа 9. 5. Результат суммирования попадает на выход устройства через вторые группы эле мента И-ИЛИ 13 и элементы И 15,

В случае, когда на выходах 9 образуются комбинации 10011 и 00000, на выход 11 устройства поступает сигнал 00000 через элемент }Ц запрета и .

элементы 15,

Пример. Пусть А 1111011011- 0011101000011101001111. Обычным способом остаток от деления этого числа на 19 равен 18 to 10010,,$ По предлагаемому алгоритму разобъем число А на группы, содержащие по 9 разрядов. Тогда А0 101001111, -А4 101000011, - Ai 11110. А, - 101000011

А3 11110

-.+1

0,101100010 сум.2.2

С0 сум.3.1-3.4

в, x 3

B| сум0ЗоЮ-ЗоН

в5 3

СУМоЗ, 15-3J6

эл,7.1

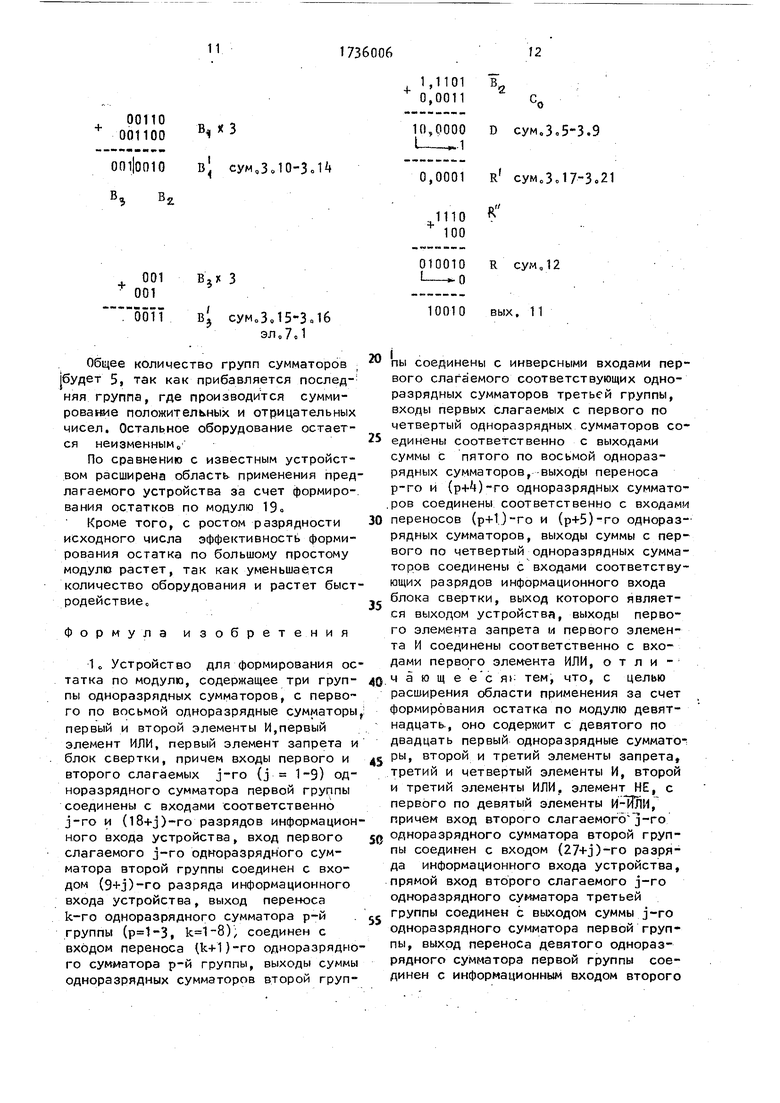

Общее количество групп сумматоров |будет 5, так как прибавляется последняя группа, где производится суммирование положительных и отрицательных чисел. Остальное оборудование остается неизменным0

По сравнению с известным устройством расширена область, применения предлагаемого устройства за счет формирования остатков по модулю 19

Кроме того, с ростом разрядности исходного числа эффективность формирования остатка по большому простому модулю растет, так как уменьшается количество оборудования и растет быстродействие о

Формула изобретения

1С Устройство для формирования остатка по модулю, содержащее три труп- пы одноразрядных сумматоров, с перво™ го по восьмой одноразрядные сумматоры первый и второй элементы И,первый элемент ИЛИ, первый элемент запрета и блок свертки, причем входы первого и второго слагаемых j-го (j 1-9) одноразрядного сумматора первой группы соединены с входами соответственно j-ro и (l8+j)-ro разрядов информационного входа устройства, вход первого слагаемого j-ro одноразрядного сумматора второй группы соединен с входом (9+j)-ro разряда информационного входа устройства, выход переноса k-ro одноразрядного сумматора р-й группы (, ), соединен с входом переноса (k+1)-ro одноразрядного сумматора р-й группы, выходы суммы одноразрядных сумматоров второй груп1,1101 В, 0,0011

10,0000 D сум„3 о 5-3.9

0,0001 R1 cyM.3J7-3.21

010010 R сум„12

10010 вых. 11

5

0

5

0 § 0 $

пы соединены с инверсными входами первого слагаемого соответствующих одноразрядных сумматоров третьей группы, входы первых слагаемых с первого по четвертый одноразрядных сумматоров соединены соответственно с выходами суммы с пятого по восьмой одноразрядных сумматоров, выходы переноса р-го и (р+)-го одноразрядных сумматоров соединены соответственно с входами переносов (р+Ото и (р+5)-го одноразрядных сумматоров, выходы суммы с первого по четвертый одноразрядных сумматоров соединены с входами соответствующих разрядов информационного входа блока свертки, выход которого является выходом устройства, выходы первого элемента запрета и первого элемента И соединены соответственно с входами первого элемента ИЛИ, отличающееся тем, что, с целью расширения области применения за счет формирования остатка по модулю девятнадцать , оно содержит с девятого по двадцать первый одноразрядные сумматоры, второй и третий элементы запрета, третий и четвертый элементы И, второй и третий элементы ИЛИ. элемент НЕ, с первого по девятый элементы И-ЙЛИ, причем вход второго слагаемого -го одноразрядного сумматора второй группы соединен с входом (27-t-j)-ro разряда информационного входа устройства, прямой вход второго слагаемого j-ro одноразрядного сумматора третьей группы соединен с выходом суммы j-ro одноразрядного сумматора первой группы, выход переноса девятого одноразрядного сумматора первой группы соединен с информационным входом второго

и с управляющим входом третьего элементов запрета, выход переноса девятого одноразрядного сумматора второй группы соединен с управляющим входом второго и с информационным входом третьего элементов запрета, выходы второго и третьего элементов запрета соединены соответственно с входами

переноса первых одноразрядных суммато- (Q одноразрядных сумматоров, инверсные

ров второй и третьей группы, выход переноса девятого одноразрядного сумматора третьей группы соединен через элемент НЕ с управляющим входом блока свертки, с первыми прямыми входами первых групп и с первыми инверсными входамм вторых групп с первого по девятый элементов И-ИЛИ, выходы суммы одноразрядных сумматоров третьей трупвходы вторых слагаемых которых соединены соответственно с выходом пятого элемента И-ИЛИ и с выходами суммы с десятого по двенадцатый одноразрядных . 5 сумматоров, вход элемента НЕ соединен с входом-, переноса семнадцатого одноразрядного сумматора, выход переноса (1б+р)-го одноразрядного сумматора соединен с входом переноса (17+

пы соединены с вторыми инверсными вхо- 20 +р)го одноразрядного сумматора, выход переноса двадцатого одноразрядного сумматора соединен с входом первого слагаемого девятого одноразрядного сумматора, вход второго слагае- 25 мого которого соединен с входом логической единицы устройства, выход пятого элемента И-ИЛИ соединен с входом первого слагаемого десятого одноразрядного сумматора, выход переноса (9+i)-ro () одноразрядного сумматора соединен с входом переноса (T0+i)-ro одноразрядного сумматора, выход (5+i)-ro элемента И-ИЛИ соединен с входом первого слагаемого (10+1)-го и с входом второго слагав-дами первых групп и с вторыми прямыми входами вторых групп соответствующих элементов И-ИЛИ, выход переноса восьмого одноразрядного сумматора соединен с входом переноса девятого одноразрядного сумматора, выход переноса которого соединен с входом переноса первого одноразрядного сумматора, с управляющим входом первого элемента запрета, с первыми входами второго и третьего элементов И, выход суммы девятого одноразрядного сумматора соединен с информационным входом первого элемента запрета и с вторым входом второго элемента И, выход которого

30

соединен с первым входом первого эле- 35 мого (9+i)-ro одноразрядных суммато- мента И и с входом слагаемого двадцать ров выход суммы тринадцатого одно- первого одноразрядного сумматора, вход переноса которого соединен с выходом

разрядного сумматора соединен с входом первого слагаемого пятнадцатого одноразрядного сумматора и с входом

переноса четвертого одноразрядного

сумматора, выход суммы двадцать перво- 40 второго слагаемого семнадцатого одного одноразрядного сумматора соединен с входом пятого разряда информационного входа блока свертки, выход суммы пятого одноразрядного сумматора соединен с первым входом четвертого элемента И, второй вход которого соединен с вторым входом третьего элемента И и с выходом суммы шестого одноразрядного сумматора, выходы суммы

разрядного сумматора, выход суммы четырнадцатого одноразрядного сумматора соединен с входом второго слагаемого пятнадцатого одноразрядного сум- 45 матора и с входом первого слагаемого шестнадцатого одноразрядного сумматора, вход второго слагаемого которого соединен с выходом переноса четырнадцатого одноразрядного сумматора и с седьмого и восьмого одноразрядных сум- 50 первым входом третьего элемента ИЛИ, маторов, выходы третьего и четвёртого второй вход которого соединен с выходом переноса шестнадцатого одноразрядного сумматора, вход переноса которого соединен с выходом переноса пятнад- 55 цатого одноразрядного сумматора, выходы суммы пятнадцатого и шестнадцатого одноразрядных сумматоров, выход третьего элемента ИЛИ соединен с входами вторых слагаемых соответственэлементов И соединены соответственно с входами второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, выход которого соединен с входами вторых слагаемых пер-j вого и четвертого одноразрядных сумматоров, выход первого элемента ИЛИ соединен с входом второго слагаемого .

третьего одноразрядного сумматора, выходы с первого по четвертый элементов И-ИЛИ соединены с входами первых слагаемых соответственно с семнадцатого по двадцатый одноразрядных сумматоров, выходы суммы которых соединены соответственно с прямыми входами первых слагаемых с пятого по восьмой

входы вторых слагаемых которых соединены соответственно с выходом пятого элемента И-ИЛИ и с выходами суммы с десятого по двенадцатый одноразрядных сумматоров, вход элемента НЕ соединен с входом-, переноса семнадцатого одноразрядного сумматора, выход переноса (1б+р)-го одноразрядного сумматора соединен с входом переноса (17+

20 25

30

мого (9+i)-ro одноразрядных суммато- ров выход суммы тринадцатого одно-

разрядного сумматора соединен с входом первого слагаемого пятнадцатого одноразрядного сумматора и с входом

но с восемнадцатого по двадцатый одноразрядных сумматоров о

1

о т л и 2, Устройство по п чающееся тем,ч, что блок свертки содержит пять одноразрядных сумматоров, пять элементов И, элемент И-ИЛИ-НЕ, пять элементов И-ИЛИ, причем выход переноса 1-го одноразрядного сумматора соединен с выходом переноса (i+1)-ro одноразрядного сумматора, выход переноса пятого одноразрядного сумматора соединен с входом пере-1 носа первого одноразрядного сумматора, выход элемента И-ИЛИ-НЕ соединен с первыми входами с первого по пятый элементов И, выходы которых являются выходом блока свертки, а вторые входы соединены с выходами соответствующих элементов И-ИЛИ, первые инверсные входы первых групп и первые прямые входы вторых групп элементов И-ИЛИ с первого по пятый соединены с управляющим входом блока свертки, вторые вхо- 25 первой и второй групп элемента ды первых групп элементов И-ИЛИ с И-ИЛИ-НЕ соединены с входом третьего первого по пятый соединены с входами разряда информационного входа блока соответствующих разрядов информацией- свертки, пятый прямой вход первой ного входа блока свертки,вторые входы группы и пятый инверсный вход второй вторых групп элементов И-ИЛИ с перво- ,- группы элемента И-ИЛИ-НЕ соединены с го по пятый соединены с выходами сум- входом четвертого разряда информацион- мы соответствующих одноразрядных ного входа блока свертки„

сумматоров, инверсные входы первого слагаемого одноразрядных сумматоров с первого по пятый соединены с входами соответствующих разрядов информационного входа блока свертки, прямые входы второго слагаемого первого и второго одноразрядных сумматоров и инверсный вход второго слагаемого третьего одноразрядного сумматора соединены с входом пятого разряда информационного входа блока свертки, с первым прямым входом первой группы элемента И-ИЛИ-НЕ и с первым инверсным входом второй группы элемента И-ИЛИ-НЕ, второй прямой вход первой группы и второй инверсный вход второй группы которого соединены с входом первого разряда информационного входа блока свертки, третьи инверсные входы первой и второй групп элемента И- ИЛИ-НЕ соединены с входом второго разряда информационного входа блока . свертки, четвертые инверсные входы

ь4,

-Лз „.-Л г . М,

aieaZ7 aisaisaKfft}ffiz b iffaf9ff« % йпапаюаэ ае о-,о6а5а1, а3 ага, а0

9%. 9, 9%, 1 , %&5 , f,,

L У tf- У У. f/ /у m /-g // ... /-от с .-ym л JrH/FrH 77 j

ЬзЙ

«

J

ФГдИ fc IГ; |j§

Л

Фие.1

| Авторское свидетельство СССР № , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1992-05-23—Публикация

1989-12-04—Подача