Изобретение относится к вычислительной технике и предназначено для извлечения квадратного корня из чисел, представленных в Р-ичной системах счисления.

Цель изобретения - расширение : класса решаемых задач за счет вычисления квадратного-корня из чисел с произвольными основаниями.

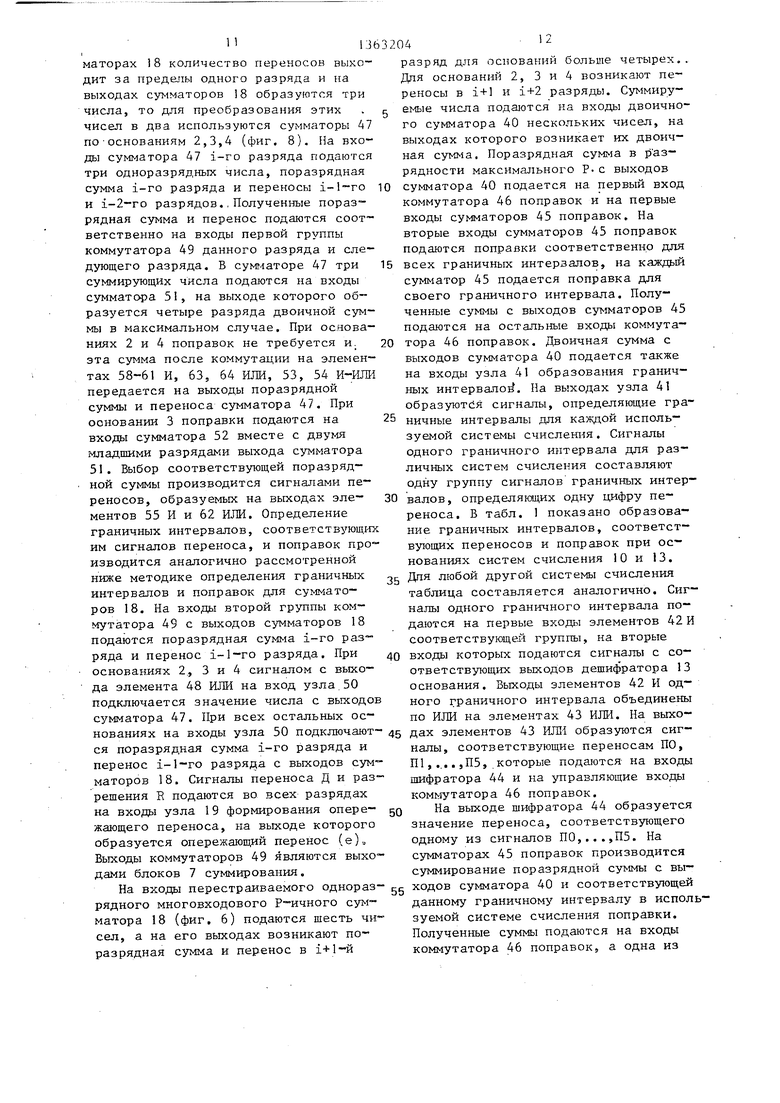

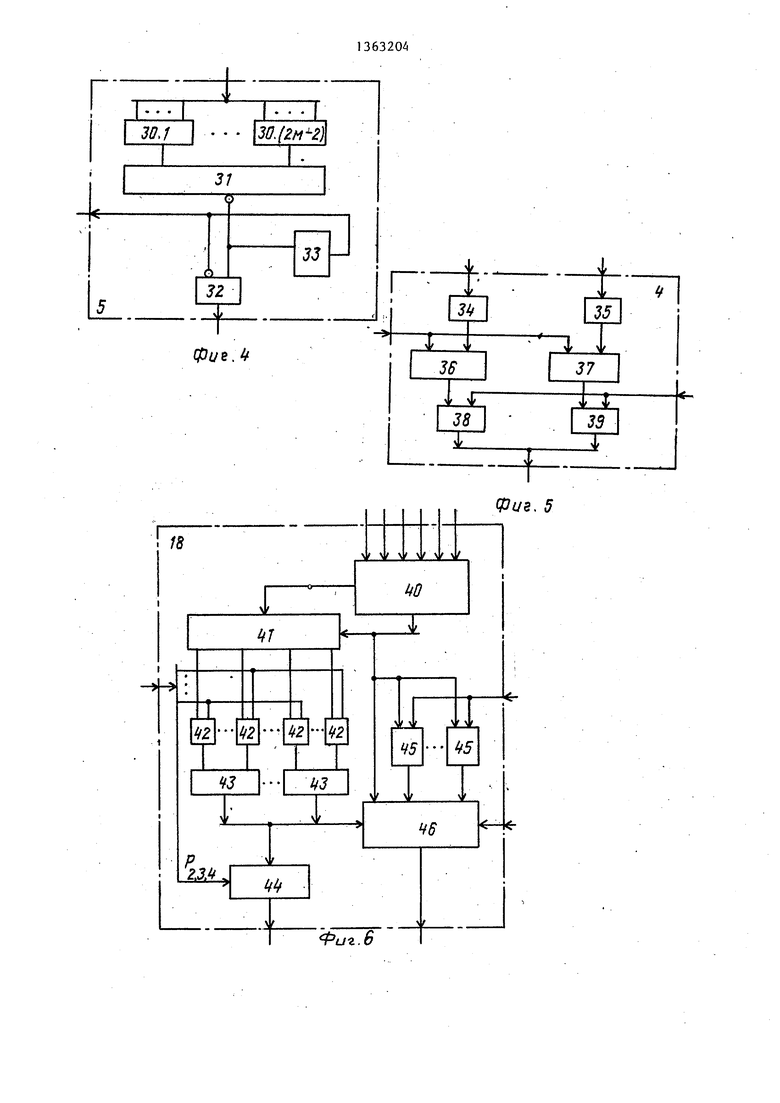

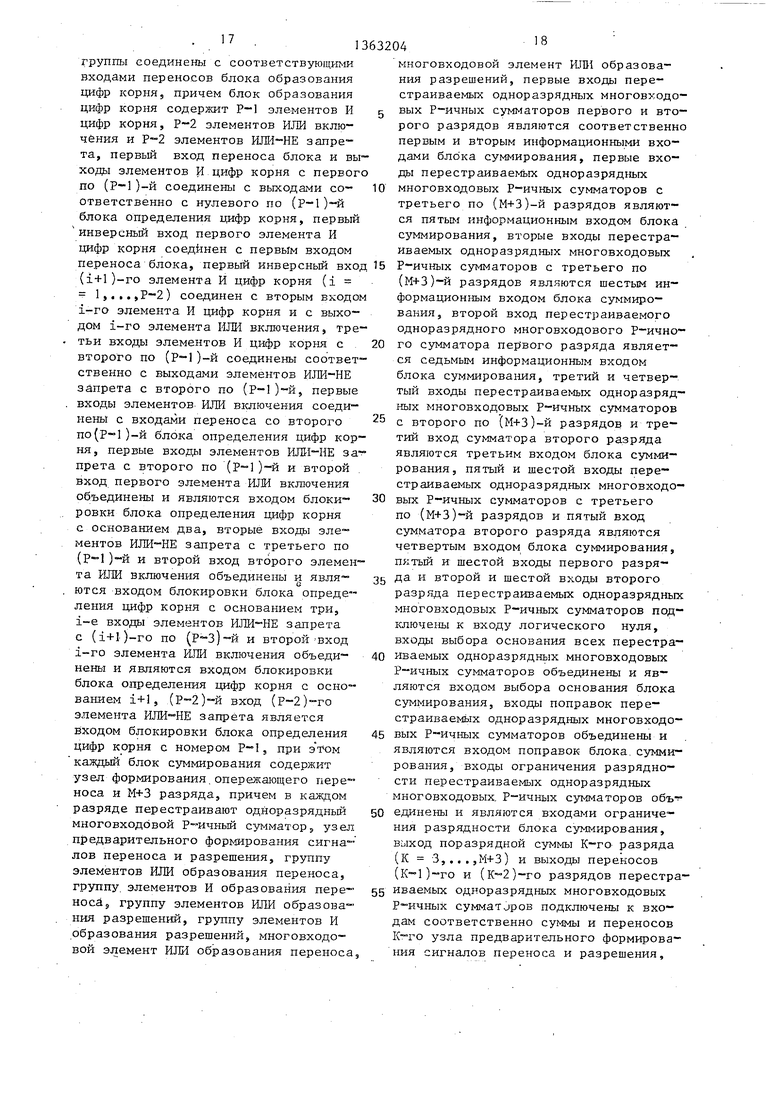

На фиг. 1 изображена функциональная схема устройства для извлечения квадратного корня с перестраиваемым основанием системы счисления; на фиг. 2 - функциональная схема блока суммирования; на фиг. 3 - схема блок образования цифр корня; на фиг. 4 - схема блока коррекции; на фиг. 5 - схема блока поразрядного дополнения; на фиг. 6 - функциональная схема перестраиваемого одноразрядного много- входового Р ичного сумматора; на фиг. 7 - функциональная схема блока предварительного формирования сигналов переноса и разрешения; на фиг. 8 - схема одноразрядного сумматора по основаниям 2, ЗиЛ; на фиг. 9 - схема шифр атора переносов.

Устройство (фиг. I) содержит ре гистр 1 корня, регистр 2 подкоренного выражения, блок 3 дешифраторов, содержащий М-1 дешифраторов, блок 4 поразрядного дополнения, блок 5 коррекции, блок 6 формирования кратных, Р-1 блоков 7 суммирования 7.1-7.(p-l двухканальный коммутатор 8, первый 9 и второй 10 регистры, блок II образования цифр корня, шифратор 12 цифр корня, дешифратор 13 основания, вы

читатель 14 единицы, блок 15 формирования поправок, блок 16 ограничения разрядности, шины 17 кбда разрядности. Блок 7 суммирования (фиг. 2) содержит перестраиваемых однораз40 N О представлено в любой Р-ичной системе счисления и может быть правильной дробью, смешанной дробью или целым числом. Пусть при Р 10, Р - основание системы счисления, квадратрядных многовходовых Р-ичных суммато- 4g ньй корень равен Ы;; 4и 0,2341. ров 18.1-18.1, узел 19 формированияТогда точное подкоренное выражение

М+3

опережающего переноса, M+J групп содержащих для каждого разряда, блок 20 предварительного формирования сигналов переноса и разрешения, группу элементов 21 ИЛИ образования переноса, группу элементов 22 И образования переноса, многовходовой элемент 23 ИЛИ образования переноса группу элементов 24 ИЛИ образования разрешения, группу элементов 25 И образования разрешения, многовходовой элемент 26 ИЖ образования разрешения. Блок 11 образования цифр корня

можно найти из диаграммы умножения.

50

55

00 000

0

(фиг. 3) содержит Р-1 элемент 27 И цифр корня, р-2 элемента 28 ИЛИ вклю чения, Р-2 элемента 29 ИЛИ-НЕ запрета. Блок 5 коррекции (фиг. 4) содержит элементы 30.1 - 30.(2М-2) ИЛИ коррекции, элемент 31 ИЛИ-КЕ совпадения, элемент 32 И, триггер 33. Блок

4 поразрядного дополнения (фиг. 5) содержит первую 34 и вторую 35 группы элементов НЕ, первый 36 и второй 37 двоичные сумматоры, первую 38 и вторую 39 группы элементов И. Перестраиваемый одноразрядный многовходовой

5 Р-ичньш сумматор 18 (фиг. 6) содержит двоичный сумматор 40 нескольких чисел, узел 41 образования сигналов граничных интервалов, группы элементов 42 и граничных интервалов, эле0 менты 43 ИЛИ гра ничных интервалов, шифратор 44 переносов, группу 45 двоичных сумматоров поправок, коммутатор 46 поразрядной суммы. Блок 20 предварительного формирования сигна-

5 лов переноса и разрешения (фиг. 7) содержит одноразрядный сумматор 47 по основаниям 2, 3 и 4, элемент 48 ИЛИ выбора, коммутатор 49, узел 50 предварительного формирования сигналов переноса и разрешения. Одноразрядный сумматор 47 по основаниям 2, 3, 4 содержит трехвходовой сумматор 51, двоичньй сумматор 52, элементы 53, 54 И-ИЛИ, элементы 55-61 И, элементы 62-64 ИЛКГ. Шифратор 44 переносов содержит элементы 65-74 и 75 - 78 ИЛИ.

Рассмотрим работу устройства. Подкоренное выражение положительно,

0 N О представлено в любой Р-ичной системе счисления и может быть правильной дробью, смешанной дробью или целым числом. Пусть при Р 10, Р - основание системы счисления, квадрат0

можно найти из диаграммы умножения.

00 000

Результат, № l0.054 80281

2 0. О 5,4 80281

30. 054 80281 Ю

4 0. О 5 4

8 О 2,8

50. 054 80281

:-

Точкой в Ш и N отделены знаковые разряды. Запятой в результату умножения отделены целая и дробная части полученные в зависимости от положени запятой в значении квадратного корня ill. Для результата № 1 запятая в Ш совпадает с точкой, для остальных результатов (2,...,5) запятая в Ш пе ремещается на один разряд слева направо. Для результата 5 Ш-целое число. Как видно из диаграммы умножения положение запятой в квадратном корне Ш однозначно связано с положением запятой в подкоренном выражении К, Количество разрядов в N от точки до запятой может быть .только четным, а это количество разделенное пополам является количеством разрядов целой части квадратного корня Ш, расположенных от точки до запятой. Квадратный корень может быть вычислен из подкоренного.вьфажения разрядностью как 2М, так и М. В одном такте образуется одна Р-ичная цифра М-разряд- ного квадратного корня. Основание системы счисления Р задается кодом

:-

Диаграмма извлечения квадратного корня Ш О, (7) (12) (11)

Ш

О, (7) (12) (11)

Ю

20

, 2563204

основания, подаваемым на шины 17 в двоично-Р-ичной форме.

Получение одной Р-ичной формы квадратного корня производится по алгоритму:

-одновременно вычисляются Р-1 положительных углов yl-y(P-l), ггред- ставляющих собой удвоенное произведение всех ранее полученных цифр на соответствующую цифру-т 1ножитель из ряда 1,2,,,,,(Р-1) плюс произведение цифры-множителя на саму себя, с учетом весов;

15 - одновременно определяются Р-1 разность вида В, У, -В , ,.,., В(Р-1)У(Р-1)-Вд, где Вд - очередной сдвинутьй реальный отрицательный остаток предьщущего такта плюс приращение N;

- определяются знаки полученных разностей;

-формируют ся сигналы, определяющие значёйия цифр корня для данного используемого основания системы счисления ;

-по сигналам цифр корня выбирается реальный отрицательный остаток данного такта и определяется соответст-

30 вующая цифра корня;

-производится сдвиг полученного реального отрицательного остатка на два Р-ичных разряда влево и запись в два младших разряда приращения подко-

5

35

ренного выражения.

Б следующих тактах операции алгоритма повторяются. Приведем диаграмму извлечения квадратного корня для где подкоренное выражение является мешанной дробью N 0,(4) fll), (И). Квадратньй корень от данного N Ш 0,(7), (12) (11), а точное подкоренное вьфажение будет N Ш.Ш О,(4) (11), (10) (7) (0) (4),

3-й угол

N

0. (4) (Г) (10) (7) (0) (4)

0. (4) (II) (И)

Номер разряда М

1-й такт

2-й такт 2-й угол

3-й такт

3-й угол

(12) (12) (12) (12) (8) (1) Приращение (0) (0) (0) (0) ХО) (0)

(12) (12) (11) (11) (I) (12) Приращение

и сдвиг

(0) (0) (0) (0)(I) ДСП, единица (6) -(6)

(11)(О

.(6) (6)

(12) (12) СП) (10) (11)(1)

(0)(0) (1) (1) (1) Ш2-(12)

(И) (10) (11) (1) (0) (0) Приращение

и сдвиг

(1)(1) (1) (0)

(5) (12) (10) (2)

(9) (4) (10) (2)

(5) (12) (12) (11) (9) (6) (0) (4)

(0) (1) (3) (1) (0) ШЗ(П)

Вверху диаграммы извлечения показано образование углов, где показаны только углы, суммирование которых с отрицательным остатком предыдущего такта дает реальньй отрицательный остаток данного такта. Внизу

(2)

(9) (4)

(2)

диаграммы извлечения показан процесс 55 извлечения-квадратного корня. Для любой другой системы счисления диаграмма извлечения строится аналогично. Регистр 2 подкоренного выражения содержит 2М разрядов. Если подкорен-

ное выражение содержит М разрядов, то оно записывается в М старших разрядов регистра 2, а в младшие разряд записываются нули. Код основания системы счисления шин 17 подается на входы дешифратора 13 основания, блок 4 поразрядного дополнения, вычитате- ля 14 единицы, блока 16 ограничения разрядностиi На выходах вычитателя 14 единицы образуется значение старшей цифры используемой системы счисления Р-1 в двоично-Р-ичном коде, которое подается на первые входы первого регистра 9. На первые входы вто рого регистра 10 подаются нули. Первым тактом в регистр 2 записывается подкоренное выражение, регистр 1 кор ня обнуляется, в каждый разряд регистра 9 записывается значение цифры Р-1, а в каждый разряд регистра 10 записыв.аются нули. Два старших разряда подкоренного выражения подаются на входы блока 4 (фиг. 5), в котором образуется их дополнение до старшей цифры используемой системы счисления по формуле flj Р + Н;. Полученные дополнения подаются на вхо/ц 1 двух младших разрядов всех блоков 7 суммирования и на коммутатор 8. На аналогичные входы остальных разрядов блоков 7 суммирования с выходов регистров 9,. 10 подаются цифры Р-1 и О для получения дополнительного кода отрицательного приращения N, После перво го такта в регистре 1 записаны все нули, поэтому на выходах дешифраторов блока 3 сигналов нет. В первом такте в блоках 7,.(Р-1) в соответствии с диаграммой извлечения происходит суммирование в используемой системе счисления двух старших разрядов подкоренного выражения в виде дополнения с положительными значениями углов первого такта ,..., (Р-1).(Р-1), вырабатываемых в блоке 6 в виде констант. Полученные суммы в виде двух Р-ичных чисел, поразрядных сумм и переносов с выходов блоков 7.1-7.(Р-1) подаются на соответствующие входы двухканального коммутатора 8. На выходах опережающего переноса (е) всех блоков 7 суммирования образуются значения опережающих переносов, которые .подаются на первую группу входов блока 11 образования цифр корня (фиг. 3). Если опережающий перенос равен единице, то остаток (+} если - нулю, то ос

10

20

25

30

1563204°

таток (-). На одном из 0,1,,..(Р-1) выходов блока 11 образуется сигнал, определяющий соответствующую цифру корня данного такта в используемой системе исчисления. Например, для Р 13 могут быть получены только сигналы, определяющие цифры корня от О до 12. Блокировка сигналов цифр корня больших Р-1 произв одится с помощью элементов 29 ИЛИ-НЕ, на которые соответственным образом подаются сигналы с выходов дешифратора 13 основания. ЕСЛИ на выходе с номером 13 дешифратора 13 основания есть сигнал, то блокируются все выходы блока 11, определяющие сигналы цифр корня старше 12. Элементы 28 ИЛИ определяют старшую цифру корня при заданном основании системы счисления. Сигналы цифр корня с выходов блока 11 подаются на входы шифратора 12, который производит их кодирование в двоично- -Р-ичную форму, и на управляюш ге входы двухканального коммутатора 8, где по этим сигналам выбирается соответствующий реальный отрицательный остаток данного такта в используемой системе счисления. Вторым тактом в регистр 1 запишется значение полученной цифры корня с выходов шифратора 12, в регистры 9, 10 с выходов коммутатора 8 запишется значение реального отрицательного остатка данного такта в используемой системе счисления, подкоренное выражение в регист эе 2 сдвигается влево на два Р-ичных разряда. Значение первой цифры корня подается из первого разряда регистра 1 на входы дешифратора первого разряда блока 3 и на его выходе, соответствующем первой цифре, появляется сигнал, который поступает на соответствующей шине на соответствуюш 1Й вход блока 6 формирования кратных. На соответствующих входах блоков 7.1-7.(Р-1) суммирования образуются значения вторых

40

45

углов соответственно для каждой из

цифр множителей 1,2,..,,(Р-1). Полученные углы суммируются в блоках 7.1г7.(Р-1) -суммирования, соответствующих данным цифрам множителям, со сдвинутым на два разряда влево предыдущим остатком и приращением подкоренного выражения. На выходах блоков суммирования образуются опережающие переносы и остатки в виде двух чисел и используемой системе счисления. По значениям опережающих переносов в

блоке 11 определяется сигнал цифры корня, по которому на шифраторе 12 определяется вторая цифра корня и реальный отрицательньш остаток .на вы ходе коммутатора 8, В следующих тактах все действия повторяются по аналогии с первым и вторым тактами до получения всех цифр квадратного корня. В том такте, в котором во всех разрядах регистра 2 подкоренного выражения, кроме двух старших, будут нули, блок 5 коррекции (фиг. 4) вы- р.абатывает корректирующую единицу, которая подается в младшие разряды блоков 7 суммирования. Следующим тактом триггер 39 включается в единицу и блокирует выходы блока 4 поразрядного дополнения.

В блоках суммирования 7.1-7.(Р-1) (фиг. 2) производится суммирование отрицательного остатка предыдущего такта и значения положительного угла, соответствующего данному блоку

суммирования. В каждом Р-ичном разряде в максимальном случае суммируются шесть одноразрядных Р-ичных чисел, которые подаются.на входы перестраиваемого одноразрядного многовходово- го Р-ичного сумматора 18. Каждый блок 7 суммирования содержит М+3 сумматора 18, которые могут перестраиваться для работы в любой Р-ичной системе счисления. Дпя этого на входы сумматоров 18 подаются сигналы с выходов дешифратора 13 основания, поправки - с выходов блока 15 формирования поправок и сигналы - с выходов блока 16 Ограничения разрядности. На выходах блоков 18 для систем счисления с основанием больше четырех образуются два многоразрядных числа, а для систем счисления с основаниями 2, 3, 4 три многоразрядных числа в используемой системе счисления, которые в соответствуюш х разрядах подаются на входы блоков 20 предварительного формирования сигналов переноса и разрешения (фиг. 2). Коммутация сигналов переноса и разрешения для различных систем счисления осуществляется на элементах 22 И, 23 ИЛИ и на элементах 25 И, 26 ИЛИ соответствующими сигналами с выходов дешифратора 13 основания. На элементах 21 ИЛИ группы и 24 ИЛИ группы производится образование сигналов переноса и разрешения для различных систем счисления из предварительных сигналов, вырабатыва-

10

g

6320410

емых в блоке 20 предварительного формирования сигналов переноса и разрешения. На входь: блока 20 i-ro разряда подаются значения поразрядной суммы i-ro разряда и значения переносов 1-1-го и i-2-го разрядов, поскольку для оснований 2, 3 и 4 иг выходах сумматоров 18 в совокупности образуется три числа. При суммировании шести одноразрядных чисел для оснований больше четырех количество переносов не превысит пяти. Для основания Р 13 функция переноса Д образуется из условия С; + К;, 12, где С значение поразрядной суммы, К - значение переноса. Дпя рассматриваемого случая это условие выполняется при следующих 12 +5, 12 + 4, 12 + +1, 11+5, 11+4, 10+5, 10+4, 10 +

+ 4,9 5, чему соответствует логичес- , кое выражения.Д С4.СЗ.(КЗ+К2+К1) + 25 + С4.С2.К2.(С1+К1)+ С4.КЗ.(C2+CI+K1), которое образуется на выходе соответствующего элемента 21 ИЛИ. Цифры при значениях С и К обозначают номера двоичных разрядов в гутри Р-ичного раз15

20

значениях С + К: 3, 12 +2, 12 + 11+ 3, 11 + 2, 3, 9 + 5,9 +

ряда, в данном случае определяющего основание Р 13, младший разряд имеет номер 1. Функция разрешения R образуется из условия С, 12, а для упрощения логического выражения может быть использовано условие 12. Дпя рассматриваемого случая эти.усовия вьшолняются при следующих значениях Си К, 12+0, 1 + 1, 10+2, 9+3, 8 + 4 и допускается использование значений 12+1, 12+2, 12+ + 3, 12 + 4, 12 + 5, 11 + 2, 11 + 3, 11+4, 11+5, 10+3, 10+4, 10 + + 5, 9 + 4, 9 + 5, 8 + 5, чему соответствует логическое выражениеР С4.СЗ + С4.С2.С1.К1 + С4.С1.К2.К1+ + С4.С2.К2 + С4.КЗ. Данное логическое выражение образуется на выходе соответствующего элемента 24 ИЛИ. Дпя остальных используемых систем счислений

образование сигналов переноса и разрешения производится аналогично. В узле 50 блока 20 (фиг. 7) образуются предварительные сигналы переноса и разрешения согласно с рассмотренными

выражениям11 для Д и Р, которые затем подаются на входы соответствующих элементов 21 ИЛИ, 24 ИЛИ.

Поскольку для оснований Р 2,3,4 при шести суммируемых числах на сум

I 1

маторах 18 количество переносов выхо дит за пределы одного разряда и на выходах сумматоров 18 образуются три числа, то для преобразования этих чисел в два используются сумматоры 4 по-основаниям 2,3,4 (фиг, 8). На входы сумматора 47 i-ro разряда подаютс три одноразрядных числа, поразрядная сумма i-ro разряда и переносы i-1-го и i-2-го разрядов.,Полученные поразрядная сумма и перенос подаются соот ветственно на входы первой группы коммутатора 49 данного разряда и следующего разряда. В сумг-iaTOpe 47 три суммирующих числа подаются на входы сумматсфа 51, на выходе которого образуется четыре разряда двоичной суммы в максимальном случае, При основаниях 2 и 4 поправок не требуется и. эта сумма после коммутации на элементах 58-61 И, 63, 64 ИЖ, 53, 54 И-ИЛ передается на выходы поразрядной суммы и переноса сумматора 47. При основании 3 поправки подаются на входы сумматора 52 вместе с двумя младшими разрядами выхода сумматора 51. Выбор соответствующей поразрядной суммы производится сигналами переносов, образуемых на выходах эле ментов 55 И и 62 ИЛИ. Определение граничных интервалов, соответствующи им сигналов переноса, и поправок производится аналогично рассмотренной ниже методике определения граничных интервалов и поправок для сумматоров 18. На входы второй группы коммутатора 49 с выходов сумматоров 18 подаются поразрядная сумма i-ro раз ряда и перенос i-1-го разряда. При основаниях 2, 3 и 4 сигналом с выхода элемента 48 ИЛИ на вход узла,50 подключается значение числа с выходо сумматора 47. При всех остальных основаниях на входы узла 50 подключаются поразрядная сумма i-ro разряда и перенос i-1-го paзpя Ja с выходов сумматоров 18. Сигналы переноса Д и разрешения R подаются во всех разрядах на входы узла 19 формирования опере- жающего переноса, на выходе которого образуется опережающий перенос (е). Выходы коммутаторов 49 являются выходами блоков 7 суммирования.

На входы перестраиваемого одноразрядного многовходового Р-ичного сумматора 18 (фиг, 6) подаются шесть чи сел, а на его выходах возникают поразрядная сумма и перенос в i+1-й

2-

10

15

25

63204

разряд для 20QQ 30

12

оснований больше четырех.. Для оснований 2, 3 и 4 возникают переносы в i+1 и i+2 разряды. Суммируемые числа подаются на входы двоичного сумматора 40 нескольких чисел, на выходах которого возникает их двоичная , Поразрядная сумма в р аз- рядности максимального Р.с выходов сумматора 40 подается на первый вход коммутатора 46 поправок и на первые входы сумматоров 45 поправок. На вторые входы сумматоров 45 поправок подаются поправки соответственно для всех граничных интерзалов, на каждый сумматор 45 подается поправка для своего граничного интервала. Полученные суммы с выходов сумматоров 45 подаются на остальные входы коммутатора 46 поправок. Двоичная сумма с выходов сумматора 40 подается также на входы узла 41 образования граничных интервалов. На выходах узла 41 образуются сигналы, определяющие граничные интервалы для каждой используемой системы счисления. Сигналы одного граничного интервала для различных систем счисления составляют одну группу сигналов граничных интервалов, определяющих одну цифру переноса. В табл. 1 показано образование граничных интервалов, соответствующих переносов и поправок при основаниях систем счисления 10 и 13. 35 Для любой другой системы счисления таблица составляется аналогично. Сигналы одного граничного интервала подаются на первые входы элементов 42 И

азряд для

соответствукщеи группы, на вторые

разряд для

входы которых подаются сигналы с соответствующих выходов дешифратора 13 основания. Выходы элементов 42 И одного граничного интервала объединены по ИЛИ на элементах 43 ИЛИ. На выхо- Дах элементов 43 WEi образуются сигналы, соответствующие переносам ПО, П1,..,. ,П5, .которые подаются на входы шифратора 44 и на управляющие входы коммутатора 46 поправок.

На выходе шифратора 44 образуется значение переноса, соответствующего одному из сигналов ПО,...,П5. На сумматорах 45 поправок производится суммирование поразрядной суммы с выходов сумматора 40 и соответствующей данному граничному интервалу в используемой системе счисления поправки. Полученные суммы подаются на входы коммутатора 46 поправок, а одна из

этих сумм выбирается сигналом ПО,..., П5, подаваемым с выкода одного из элементов 43 ИЛИ на соответствующий правляющий вход коммутатора 46 поправок согласно с табл. 1. Для основания Р 13 сигналы переноса ПО,...,П5, определяющие граничные интервалы, описываются выражениями:

ПО(13)АЗ А2 Г1 / В4 + В4 ВЗ + В4 ВЗ В2 В1/

П1(13) /А В4 ВЗ В2 Ш + + А1 В4 ВЗ В2 + А1 Б4 + + А1 В4 ВЗ В2/

П2(13) /А В4 + А1 В4 ВЗ/ + +АВ А2 / ВЗ + ВЗ :- В2 + ВЗ Б 2 В1 /

ПЗ(13)АЗ А2/А1 В4 + + А1 В4 + А1 В4 БЗ/

П4(13)В А2 А1/В4 + В4/ + A3 А2 А1 В4 ВЗ В2 Б1

П5(3) .А1/В4 31 + В4 ВЗ + В4 ВЗ + В4 + В4 В2/.

+

БЗ В2 +

Для всех других используемых систем счисления выражения, определяющие сигналы переносов П и граничные ин тервалы, составляются аналогично. При основаниях 2, 3 и 4 на выходе шифратора 44 переносов образуется два разряда переносов, при остальных основаниях один разряд переносов. Поправки, подаваемые на входы сумматоров 45, образуются для любой используемой системы счисления согласно с табл. 1 в блоке 15 формирования поправок. Блок 15 формирования поправок содержит многовходовые элементы ИЛИ, на входы которых подаются сигналы с выходов дешифратора 13 основания таким образом, чтобы на входах соответствующих сумматоров 45 поправок при данном основании бьши бы значения поправок соответствуклцег граничного интервала определяемого табл. 1. Смена кода основания на шинах 17 вызывает соответствующее изменение поправок на выходах MHoroi ходовых элементов ИЛИ блока 15 формиро вания поправок.

Для ограничения действующей разрядности кавдого Р-ичного разряда при работе в системах счисления с . разрядностью основания меньше максимального применяется блокировка неис пользуемых при данном основании двоичных разрядов внутри каждого Р-ично- го разряда. Соответствующие сигналы блокировки образуются на выходах бло™ ка 16 ограничения разрядности и определяются выражениями Б Р(Р,, +Р. ,...,

10

V, ,

(Рт-г+Рт-,+ ..

,+Р,+Р,)

Б ., ,,..,,(,)

,

+ Р

5 . . . ,Г

.

15

0

25

30

где Т - разрядность одного Р-ичного разряда. Сигналы блокировки Б неиспользуемых при данном основании разрядов с выходов блока 16 подаются на соответствующие входы кoм ryтaтopoв 46 поправки всех сумматоров 18. Шифратор 44 переносов (фиг. 9) производит в сумматоре 18 образование Р-ичных переносов по сигналам П1,...,П5 с вы ходов соответствующих элементов 43 ИЛИ. При суммировании шести чисел могут образоваться два Р-ичных разряда переносов, если основание системы счисления 2, 3 или 4. Образование Р-ичных сигналов переносов при основаниях 2, 3 и 4 можно описать в табл. 2. При основании 2 образуются только сигналы ПО,...,ПЗ, при основании 3 на выходах элементов 43 ИЛИ образуются только .сигналы ПО,...5П4,

35 при основании 4 также только сигналы ПО...П4. Для основания два максимальное значение суммы шести чисел равно 6, для основания три - 12, для основания четыре - 18. Логика образования

40 р-ичных переносов при основаниях 2, 3, 4 отличается от логики из образования при основаниях больше четырех, поэтому для коммутации сигналов П2, ПЗ, П4 и для образования второго,

5 старшего, Р-ичного разряда переносов на соответствующие входы элементов 65-74 И подаются сигналы с выходов 2, 3, 4 дешифратора 13 основания. Младший р-ичиьш разряд переносов образуется на элементах 70-74 И, 76-78 ИЛИ, а старший разряд - на элементах 65- 69 И, 75 ИЛИ.

50

55

Формула изобретения

Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления, содержащее первьй и второй регистры, регистр

10

20

25

подкоренного выражения, регистр корня, блок дешифраторов, первый блок формирования кратных, блок поразрядного дополнения, блок коррекции, двухканальный коммутатор, шифратор цифр корня и группу блоков суммирования, выходы первого и второго разрядов регистра подкоренного выражения подключены соответственно к первому и второму информационным входам блока поразрядного дополнения, остальные выходы регистра подкоренного выражения подключены к входам блока коррекции, выход блокирующего сигнала 15 блока коррекции подключен к входу блокировки блока поразрядного дополнения, первый и второй выходы блока поразрядного дополнения подключены соответственно к первому и второму, информационным входам всех блоков суммирования группы и к соответствующим разрядам первого информационного входа двухканального коммутатора, выход й группы разрядов Р-ичной цифры (где Р - основание системы

счисления, j 1,.,.,М-1, где М - разрядность аргумента) регистра корня подключен к входу j-ro дешифрато- ра блока, выход j-ro дешифратора блока подключен к j-му информационному входу первого блока формирования кратных, первая группа разрядов г-го выхода (г 2,„.,,Р-) первого блока формироваршя кратных подключена к третьему информационному входу г-го блока суммирования группы, вторая группа разрядов г-го выхода первого блока формирования -кратных подключена к четвертому информационному вхо ду г-го блока суммирования,, третий информационный вход первого блока

суммирования подключен к входу логического нуля устройства, М-1 старших разрядов четвертого информационного входа первого блока суммирования подключены к вьгходам М-1 старших разря- дов регистра корня соответственно, младший разряд четвертого информа

25

30

40

45

ционного входа первого блока суммиро- 50 1-го блока суммирования, выход дешифвания подключен к шине Р ичного числа ед 1ницы устройства, выход первого регистра подключен к пятому информационному входу всех блоков суммирования группы и к старшим, начиная с третьего, разрядам первого информационного входа двухканального коммутатора, выход второго регистра подключен к шестО1 гу информационному вхо

0

0

5

5

ду всех блоков суммирования и к старшим, начиная с третьего, разрядам второго информационного входа двух- - канального коммутатора, выход корректирующей единицы блока коррекции подключен к седьмым информагщонным входам всех блоков суммнрован ет и к младшему разряду второго-информационному входа двухканального коммутатора, первый выход двухканально- го коммутатора подключен к информационному входу первого регистра, второй выход двухканального коммутатора подключен к информационному входу второго регистра, первый выход 1-го блока суммирования группы (1 1,..., ) подключен к (21+1)-му информационному входу двухканального коммутатора, второй выход 1-го блока суь1ми- рования подключен к (21+2)-му информационному входу двухканального ком-

мутатора, вход регистра корня соединен с выходом шифратора цифр корня, установочный вход второго регистра соединен с входом установки в О устройства, отличающее, ся тем, что, с целью расширения класса решаемых задач за счет вычисления квадратного корня из чисел с произвольными основаниями, в устройство введены дешифратор основания, блок образования цифр корня, вычитатель единицы, блок ограничения разрядности 25 и второй блок формирования кратных, причем вход дешифратора основания соединен с входом кода основания, соединенного с входом основания блока поразрядного дополнения, входом вычитателя единицы и входом блока ограничения разрядности, выходы разрядов вычитателя единицы соединены с установочными Бхода п-1 соответствую™ разрядов первого регистра, выход блока ограничения разрядности соединен с входами ограничения разрядности всех блоков суммирования группы, 1-й выход второго блока формирования кратных соединен с входами поправок

30

40

45

5

ратора основания соединен с входами выбора основания всех блоков суммирования группы, входом второго блока формирования кратных и входом блокировки блока определения цифр корня, выход которого соединен с входом шифратора цифр корня и с управляющим входом двухканального коммутатора, выходы переносов блоков суммирования

17

группы соединены с соответствующими входами переносов блока образования цифр корня, причем блок образования цифр корня содержит Р-1 элементов И цифр корня, Р-2 элементов ИЛИ включения и Р--2 элементов запрета, первый вход переноса блока и выходы элементов И цифр корня с первого по (Р-1)-й соединены с выходами соответственно с нулевого по (Р-1)й блока определения цифр корня, первый инверсный вход первого элемента И цифр кор ня соединен с первым входом

переноса блока, первый инверсньш вход 15 Р-ичных сумматоров с третьего по

25

30

(i+1)-го элемента И цифр корня (1 1,...,Р-2) соединен с вторым входом i-ro элемента И цифр корня и с выходом i-го элемента ИЛИ включения, третьи входы элементов И цифр корня с . 20 второго по (Р-1)-й соединены соответственно с выходами элементов ИЛИ-НЕ запрета с второго по ()-и, первые входы элементов. ШМ включения соединены с входами переноса со второго по(Р-1)-й блока определения цифр корня, первые входы элементов ИЛИ-НЕ прета с второго по (P-l)-й и второй вход первого элемента ИЛИ включения объединены и являются входом блокировки блока определения цифр корня с основанием два, вторые входы элементов ИЛИ-НЕ запрета с третьего по (Р-1)-и и второй вход второго элемента ШМ включения объединены и являются входом блокировки блока определения цифр корня с основанием три, i-e входы элементов ИЛИ-НЕ запрета с (i+l)-ro по (Р-з) и второй ВХОД i-ro элемента ИЛИ включения объединены и являются входом блокировки блока определения цифр корня с основанием i+, ()-й вход (Р-2)-го элемента запрета является входом блокировки блока определения цифр корня с номером , при aVoM каждьй блок суммирования содержит узел формирования,опережающего пере носа и М+3 разряда, причем в каждом разряде перестраивают одноразрядньш многовходовой Р- Ичный сумматорS узел:с предварительного формирования сигналов переноса и разрешения, группу элементов ИЛИ образования переноса, группу, элементов И образования пере™ носи5 группу элементов ИЛИ образования разрешений, группу элементов И образования разрешений, многовходо- вой элемент ИЛИ образования переноса.

(М+3)-й разрядов являются шестьм формационным входом блока суммиро вания, второй вход перестраиваемо одноразрядного многовходового Р-и го сумматора пер вого разряда явля ся седьмым информационным входом блока суммирования, третий и четв тый входы перестраиваемых однораз ных многовходовых Р-ичных суммато с второго по (М+3)-й разрядов и т тий вход сумматора второго разряд являются третьим входом блока сум рования, пятый и шестой входы пер страиваемых одноразрядных многовх вых Р-ичных сумматоров с третьего по (М+3)-й разрядов и пятый вход сумматора второго разряда являютс четвертым входом блока суммирован пятый и шестой входы первого разр

35 да и второй и шестой входы второг разряда перестраиваемых одноразря многовходовых Р-ичных сумматоров ключены к входу логического нуля входы выбора основания всех перес

40 иваемых одноразряднь1Х многовходов Р ичных сумматоров объединены и я ляются входом выбора основания бл суммирования, входы поправок пере страиваемьгх одноразрядных многовк

45 вых Р-ичных сумматоров объединены являются входом поправок блока, су рования, входы ограничения разряд сти перестраиваемых одноразрядных многовходовых, Р-ичных сумматоров единены и являются входами ограни ния разрядности блока суммировани выход поразрядной суммы К-го разр (К 3,,,.,М+3) и выходы переносо (К-П-го и (К-2)-го разрядов пере иваемых одноразрядных многовходов Р ичных cyMMaTjpoB подключены к в дам соответственно суммы и перено Кто узла предварительного формир ния сигналов переноса и разрешени

50

55

о

363204

многовходовой элемент ШШ образования разрешений, первые входы перестраиваемых одноразрядных многовходо- с вых Р-ичных сумматоров первого и второго разрядов являются соответственно первым и вторым информационными входами блока суммирования, первые входы перестраиваемьгх одноразрядных 10 многовходовых Р-ичных сумматоров с третьего по (М+3)-й разрядов являются пятым информационным входом блока суммирования, вторые входы перестраиваемых одноразрядных многовходовых

5

0

(М+3)-й разрядов являются шестьм информационным входом блока суммирования, второй вход перестраиваемого одноразрядного многовходового Р-ично- го сумматора пер вого разряда является седьмым информационным входом блока суммирования, третий и четвертый входы перестраиваемых одноразрядных многовходовых Р-ичных сумматоров с второго по (М+3)-й разрядов и третий вход сумматора второго разряда являются третьим входом блока суммирования, пятый и шестой входы перестраиваемых одноразрядных многовходовых Р-ичных сумматоров с третьего по (М+3)-й разрядов и пятый вход сумматора второго разряда являются четвертым входом блока суммирования, пятый и шестой входы первого разря-

5 да и второй и шестой входы второго разряда перестраиваемых одноразрядных многовходовых Р-ичных сумматоров подключены к входу логического нуля, входы выбора основания всех перестра0 иваемых одноразряднь1Х многовходовых Р ичных сумматоров объединены и являются входом выбора основания блока суммирования, входы поправок пере- страиваемьгх одноразрядных многовкодо-

5 вых Р-ичных сумматоров объединены и являются входом поправок блока, суммирования, входы ограничения разрядности перестраиваемых одноразрядных многовходовых, Р-ичных сумматоров объ- единены и являются входами ограничения разрядности блока суммирования, выход поразрядной суммы К-го разряда (К 3,,,.,М+3) и выходы переносов (К-П-го и (К-2)-го разрядов перестраиваемых одноразрядных многовходовых Р ичных cyMMaTjpoB подключены к входам соответственно суммы и переносов Кто узла предварительного формирования сигналов переноса и разрешения.

0

5

выходы сигналов переносов v разрешений которого подключены к соответст- входам элементов ИЛИ образования переносов и элементов ИЛИ образования разрешений К-го разряда, выход элементов ИТИ образования переносов соединены с первьпчи входами соответствующих элементов И образования переносов, выходы элементов ИЛИ образования разрешений соединены с первыми входами соответствующих элементов И образования разрешений, вторые входы соответствующих элементов И образования переносов и элементов И образования разрешений i-ro разряда объединены попарно и соединены с со- oтвeтcтвyюш ми разрядами входа выбора основания блока суммирования, ВЫХОДЫ элементов И образования переноса соедине1-1ы с соответствующими входами многовходового элемента ИЛИ образования переноса, выходы элементов И образования разрешения соединены с входами многовходового элемента ИЛИ образования разрешения, выходы многовходовых элементов ИЛИ образования переносов и многовходовы элементов ИЛИ образования разрешений всех разрядов соединены с входами соответствующего разряда узла образования опережающего переноса, вьжод которого является выходом опережающего переноса блока суммирования, входы выбора основания всех узлов предварительного формирования сигналов переноса и разрешения соединены с соответствующими разрядами входа выбора основания блока суммирования, Ш -1еющими соответственно основания два, три и четьфе, выход переносов узла предварительного формирования сигналов переноса и разрешения К-го разряда соединен с входом переноса узла предварительного формирования сигналов переноса и разращения (К+1) го разряда, первые и вторые выходы всех узлов предварительного форми рования сигналов переноса и разре- ще1-1ия являются соот-ветственно первым и вторым выходами блока суммирования, узел предварительного формирования сигналов переноса и разрешения содержит элемент ИЛИ выбора, сумматор по основаниям два, три и четыре, коммутатор и схему формирования сигнала переноса, первый и второй информационные входы коммутатора объединены в соответствующих разрядах

5

0

с первым и вторым входами сумматора по основаниям два, три и четыре и являются первым и вторым входами узла предварительного формирования сигналов переноса и разрешения, третьим входом которого является третий вход сумматор по основаниям два, три и четыре, выход поразрядной суммы которого соединен с третьим- информационным входом коммутатора, выход переноса сумматора по основаниям два, три и четыре является выходом переноса узла предварительного формирования сигналов переноса и разрешения, I

входом переноса которого является четвертый информационный вход коммутато ра, первый и второй выходы коммутатора соединены с входами схемы формирования сигнала переноса и являются первым и вторым выходами узла предварительного формирования сигналов переноса и разрешения, выходами сигналов переноса и разрешения которого 5 являются выходы схемы формирования сигнала переноса, управляющими вход коммутатора соединен с выходом элемента ИЛИ выбора, входы которого соединены с соответствующими входами выбора основания сумматора по основаниям два, три и четыре и являются входами выбора основания узла предварительного формирования сигналов переноса и разрешения, причем перестраиваемый одноразрядный многовходо-. вой Р-ичкый сумматор содержит двоичный сумматор нескольких чисел, узел образования сигналов граничных интервалов, шифратор переносов, группу элементов И и группу элементов ИЛИ граничных интервалов, группу двоичных сумматоров поправок и коммутатор поразрядной суммы, входы двоичного сумматора нескольких чисел являются входами перестраиваемого одноразрядного многовходового Р-ичного сумматора, выходы поразрядной суммы двоичного сумматора нескольких чисел соединены с первым информационным входом коммутатора поправок, с входами первой группы узла образования сигналов граничных интервалов и с первыми входами соответствующих сумматоров поправок группы, вторые -входы которых являются соответств-ующими входами поправок перестраиваемого одноразрядного многовходового Р-ичного сумматора, выходы сумматоров поправок соединены с соответствующими разрядами

0

5

0

5

0

5

второго ийформационного входа коммутатора поразрядной суммы, начиная со второго, выход и вход блокировки которого соединены соответственно с выходом поразрядной суммы и входом ограничения разрядности,перестраиваемого одноразрядного многовходового Р ичного сумматора, выходы переносов двоичного сумматора нескольких чисел соединены с второй группой входов узла образования сигналов граничных интервалов, выходы которого соединены

ляются входами выбора основания перестраиваемого одноразрядного многовходового Р-ичного сумматора, выходы элементов И одного граничного интервала соединены с входами элемента ИЛИ соответствующего граничного интерва-. ла, выходы которых подключены к управляющему входу коммутатора поразрядных сумм и к первому входу шифратора переносов, второй вход и выход которого соединены соответственно с входом выбора основания и выходом переносов перестраиваемого одноразсоответственно с первыми входами элементов И соответствующего граничного g рядного многовходового Р-ичного сум- интервала, вторые входы которых яв- матора.

Т а б л и ц а 1

000

000

000

000

000

О О 1

О О 1

О О 1

О О 1

О О 1

О О 1

010

01 О

0000

1001

1 0„ 1 О

I1 00

IIо 1

0011 0100

1001 1010

1101 1110

0110 0111

ляются входами выбора основания перестраиваемого одноразрядного многовходового Р-ичного сумматора, выходы элементов И одного граничного интервала соединены с входами элемента ИЛИ соответствующего граничного интерва-. ла, выходы которых подключены к управляющему входу коммутатора поразрядных сумм и к первому входу шифратора переносов, второй вход и выход которого соединены соответственно с входом выбора основания и выходом переносов перестраиваемого одноразрядного многовходового Р-ичного сум- матора.

0000 П0(13) ОООО (0)(0)

оно

(-10)

П1(13) ООП (-13)

1100 (-20)

П2(13) оно (-26)

0010 (-30)

П3(13) 1001 (-39)

23

36320А

24 Продолжение табл.1

О 01 10

О 01 П

О1000 П2(4)

О1001

О1010

О1011

О 1000 П2(3)

01001

О1010

10000 П3(3) 1 0001

1 0010

о1100 П3(4)

О1101

О1110.

О1.JЛ

10000 П4(4) -10001

10010

1 01 00 П4(3)

Продолжение табл.2

1 01 00 П3(2)

Ци

L

г f / « р-г

. 7

фиг. 8

Фаг. 9

Составитель А, Зорин Редактор А. Долинич Техред Л.Крлппук Корректор И. Муска

6363/40

Тираж 671 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий - 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно п6лиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Делительное устройство | 1986 |

|

SU1335980A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| Делительное устройство | 1984 |

|

SU1239711A1 |

| Устройство для суммирования нескольких Р-ичных чисел | 1983 |

|

SU1188730A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Сумматор-вычитатель | 1988 |

|

SU1536373A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для вычисления степенных функций | 1985 |

|

SU1282120A1 |

| Преобразователь кода | 1989 |

|

SU1619401A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1987 |

|

SU1413627A1 |

Изобретение относится к вычислительной технике. Цель изобретения расширение класса решаемых задач за счет перестройки систем счисления. Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления может работать в любых системах счисления с натуральным основанием. Цикл извлечения квадратного корня состоит из М тактов. В каждом такте оиределяется одна Р-ич- нал цифра-квадратного корня. Устройство содержит регистр 1 корня, регистр 2 подкоренного выражения, блок 3 дешифраторов, содержащий М-дешиф- раторов, блок 4 поразрядного дополнения, блок 5 коррекции, блок 6 формирования кратных, Р-1 блоков 7 суммирования 7.1-7. (Р-1)., двухканальный коммутатор 8, регистры 9, 10, блок И образования цифр корня, шифратор 12 корня, дешифратор 13 основания, вы- читатель единицы 14, блок 15 формирования поправок, блок 16 ограничения разрядности, шину 17 кода разрядности. 9 ил,, 2 табл. S (Л

| Устройство для извлечения квадратного корня | 1984 |

|

SU1233144A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1985-12-11—Подача