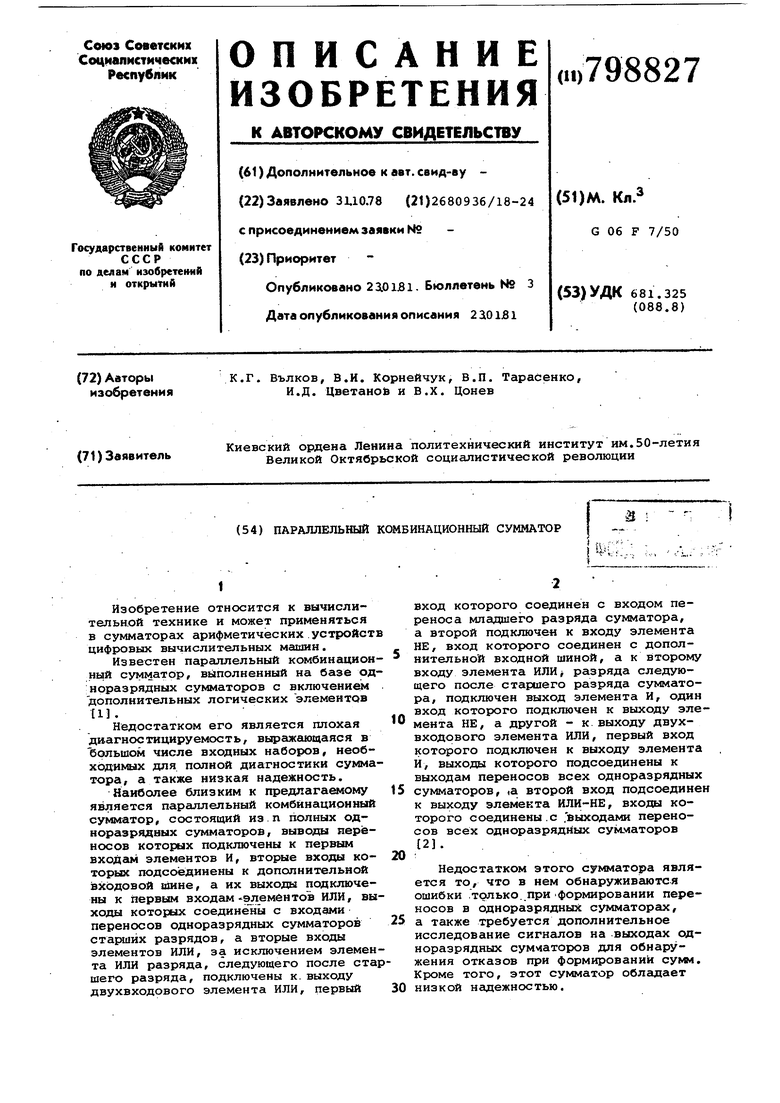

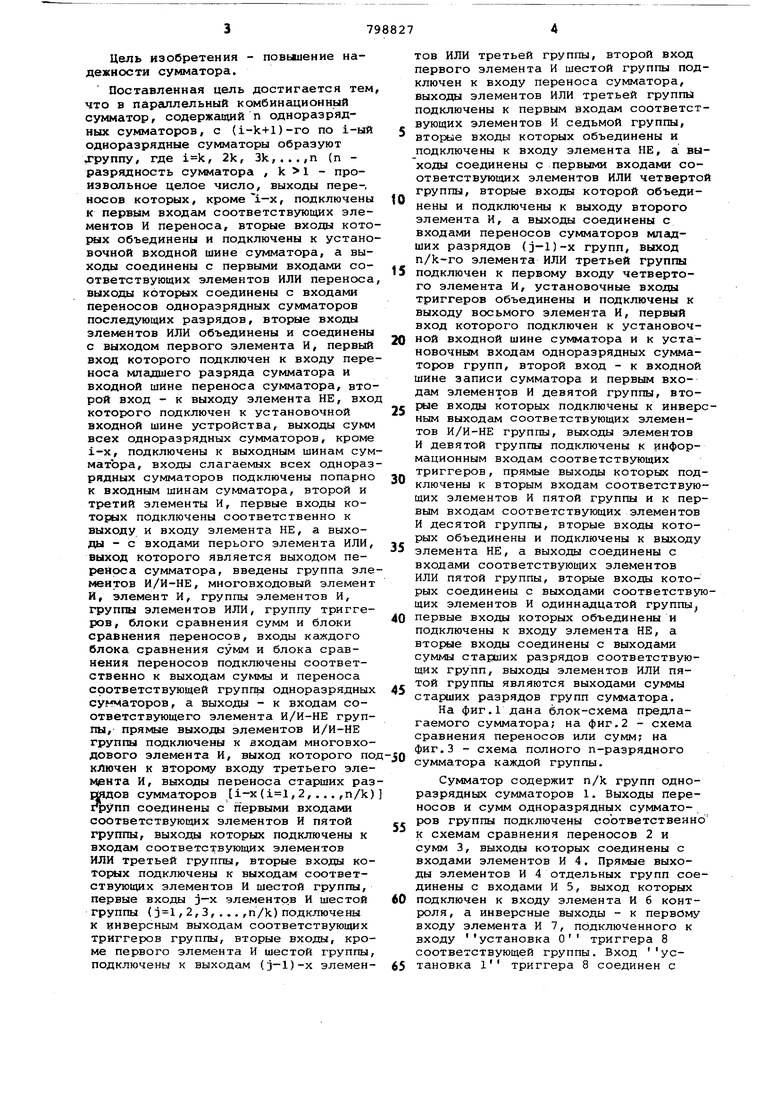

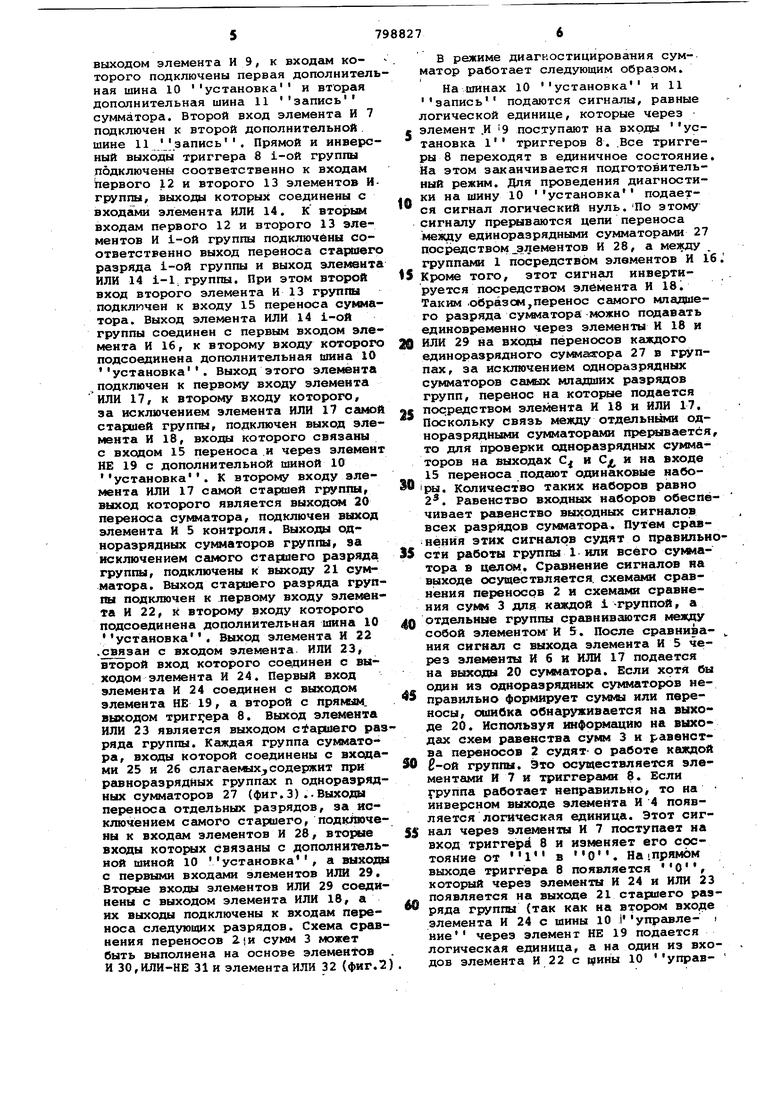

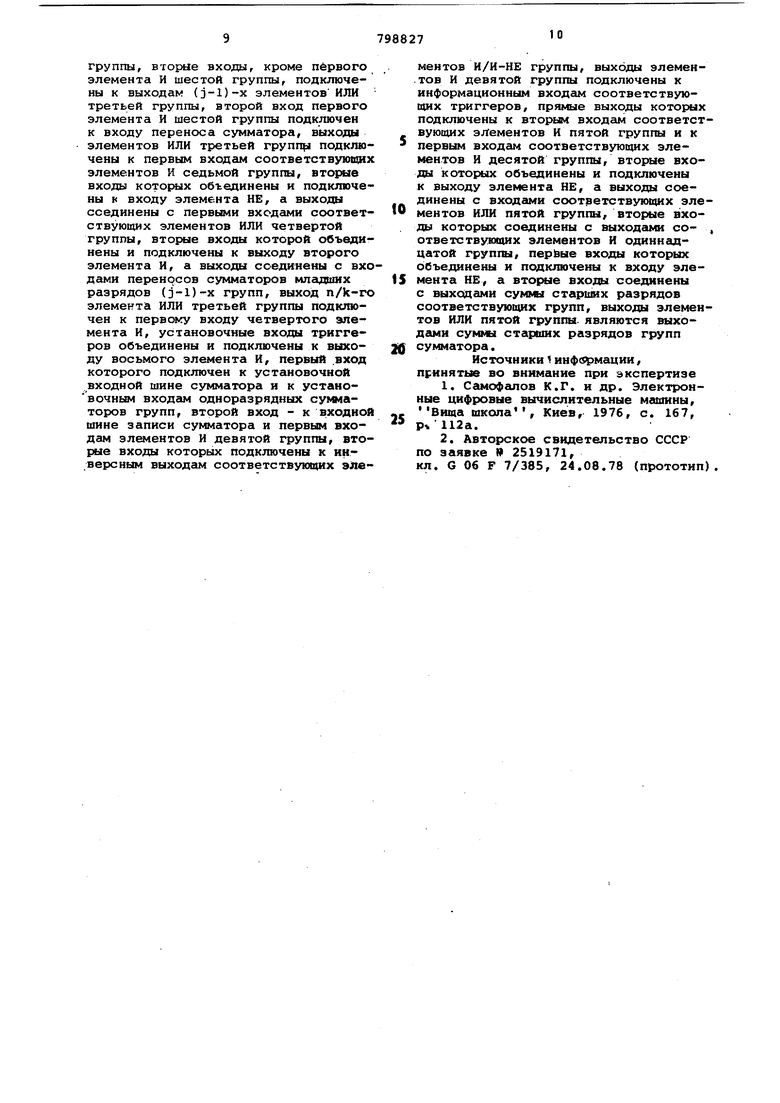

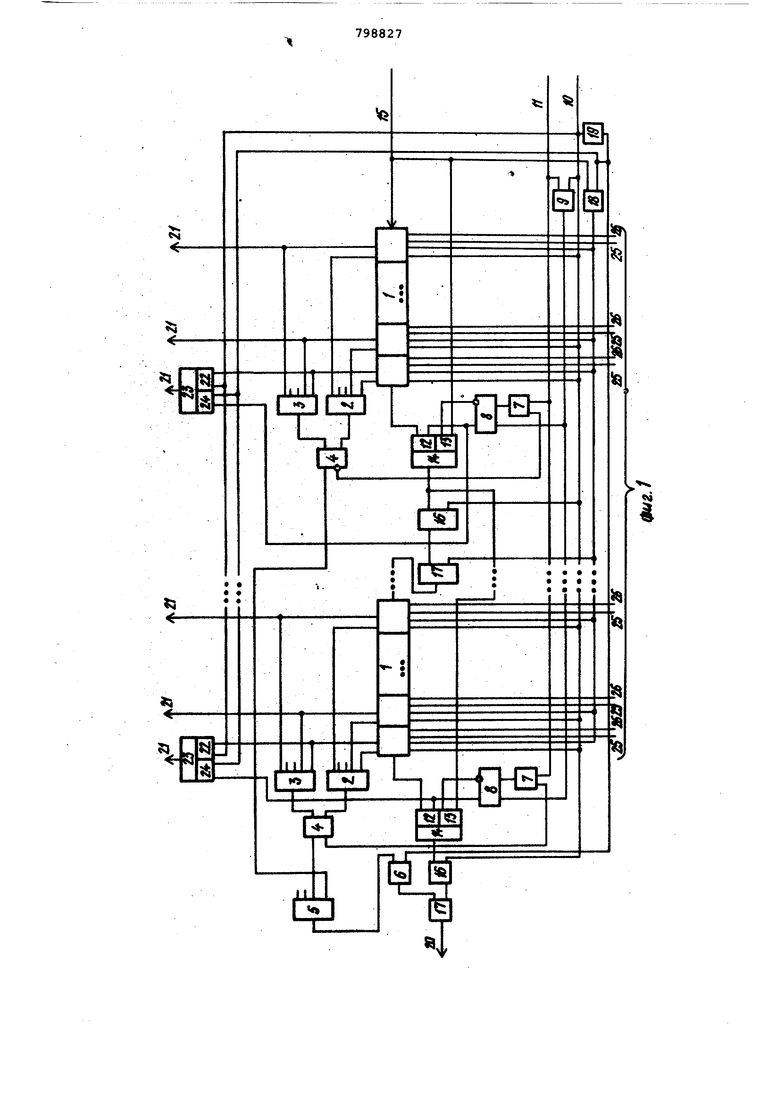

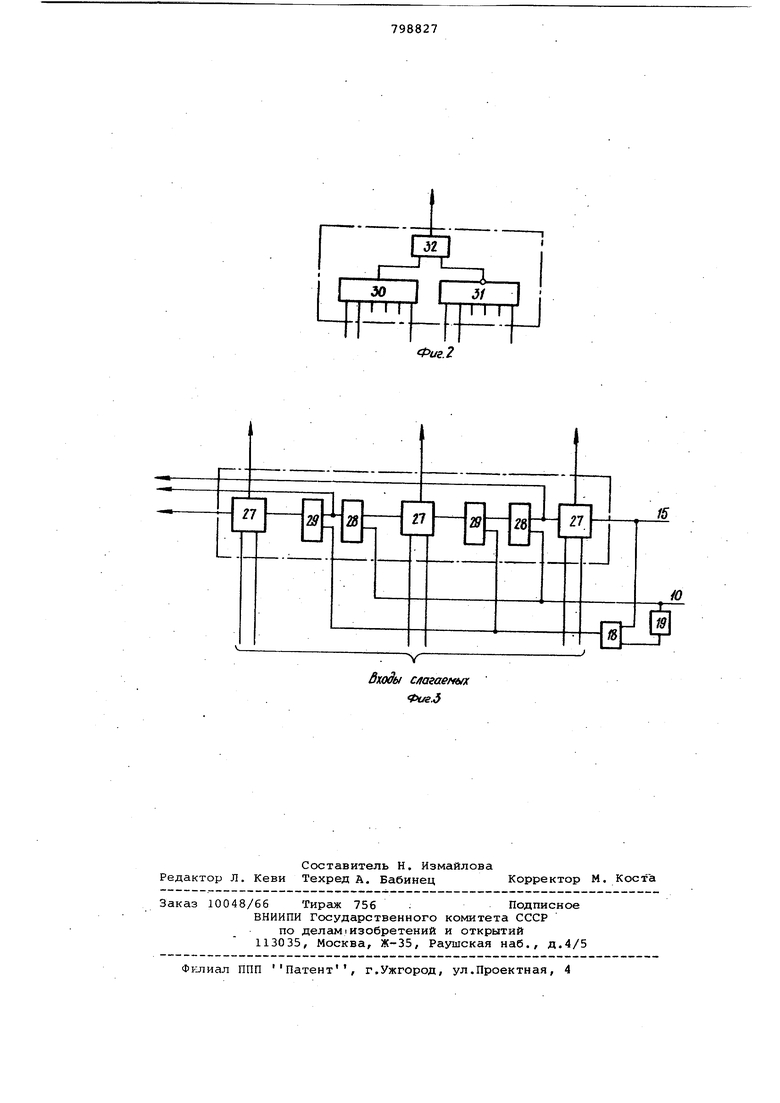

Изобретение относится к вычислительной технике и может применяться в сумматорах арифметических устройст цифровых вычислительных машии. Известен параллельный комбинацион ный сумматор, выполненный на базе од норазрядных сумматоров с включением дополнительных логических элементов 1. Недостатком его является плохая диагностицируемость, выражающаяся в большом числе входных наборов, необходимых для полной диагностики сумма тора, а также низкая надежность. Наиболее близким к предлагаемому является параллельный комбинационный сумматор, состоящий из п полных одноразрядных сумматоров, выводы переносов которых подключены к первым входам элементов И, вторые входы которых подсоединены к дополнительной входовой шине, а их выходы подключены к первым входам элементов ИЛИ, вы ходы которых соединены с входами переносов одноразрядных сумматоров стаЕяийх разрядов, а вторые входы элементов ИЛИ, за исключением элемен та ИЛИ разряда, следующего после ста шего разряда, подключены к. выходу двухвходового элемента ИЛИ, первый вход которого соединен с входом переноса младшего разряда сумматора, а второй подключен к входу элемента НЕ, вход которого соединен с дополнительной входной шиной, а к второму входу элемента ИЛИ разряда следующего после старшего разряда сумматора, подключен выход элемента И, один вход которого подключен к выходу элемента НЕ, а другой - к выходу двухвходового элемента ИЛИ, первый вход которого подключен к выходу элемента И, выходы которого подсоединены к выходам переносов всех одноразрядных сумматоров, ta второй вход подсоединен к выходу элемента ИЛИ-НЕ, входы которого соединены.с выходами переносов всех одноразрядных сумматоров 2. Недостатком этого сумматора является то, что в нем обнаруживаются ошибки .только, приформировании переносов в одноразрядных сумматорах, а также требуется дополнительное исследование сигналов на выходах одноразрядных сум 4аторов для обнаружения отказов при формировании сумм. Кроме того, этот сумматор обладает низкой надежностью. Цель изобретения - повьшение надежнсюти сумматора. Поставленная цель достигается тем что в параллельный комбинационный сумматор, содержащий п одноразрядных сумматоров, с (i-k+l)-ro по i-ый одноразрядные сумматоры образуют .группу, где , 2k, 3k,...,n (n разрядность сумматора , k 1 - произвольное целое число, выходы пере-, носов которых, кромеi-x, подключены к первым входам соответствующих элементов И переноса, вторые входы кото 1ИЛХ объединены и подключены к устано вочной входной шине сумматора, а выходы соединены с первыми входё1ми соответствующих элементов ИЛИ переноса выходы которых соединены с входами переносов одноразрядных сумматоров последующих разрядов, вторые входы элементов ИЛИ объединены и соединены с выходом первого элемента И, первый вход которого подключен к входу пере носа младшего разряда сумматора и входной шине переноса сумматора, второй вход - к выходу элемента НЕ, вхо которого подключен к установочной входной шине устройства, выходы сумм всех одноразрядных сумматоров, кроме i-x, подключены к выходным шинам сум матора, входы слагаемых всех однораз рядных сумматоров подключены попарно к входным шинам сумматора, второй и третий элементы И, первые входы которых подключены соответственно к выходу и входу элемента НЕ, а выходы - с входами перього элемента ИЛИ, выход которого является выходом переноса сумматора, введены группа эле ментов И/И-НЕ, многовходовый элемент И, элемент И, группы элементов И, группы элементов ИЛИ, группу триггеров, блоки сравнения сумм и блоки сравнения переносов, входы каждого блока сравнения сумм и блока сравнения переносов подключены соответственно к выходам суммы и переноса соответствующей группы одноразрядных сумматоров, а выходы - к входам соответствующего элемента И/И-НЕ группы, прямые выходы элементов И/И-НЕ группы подключены к входам многовходового элемента И, выход которого по ключен к второму входу третьего элемента И, выходы переноса старших раз оядов сумматоров i-x(,2,,..,n/k) групп соединены с первыми входами соответствующих элементов И пятой группы, выходы которых подключены к входам соответствующих элементов ИЛИ третьей группы, вторые входы которых подключены к выходам соответствующих элементов И шестой группы, первые входы J-X элементр.в И шестой группы (,2,3,...,n/k)подключены к инверсным выходам соответствующих триггеров группы, вторые входы, кроме первого элемента И шестой группы, подключены к выходам (j-1)-х элементов или третьей группы, второй вход первого элемента И шестой группы подключен к входу переноса сумматора, выходы элементов ИЛИ третьей группы подключены к первым входам соответствующих элементов И седьмой группы, вторые входы которых объединены и подключены к входу элемента НЕ, а выходы соединены с первыми входами соответствующих элементов ИЛИ четвертой группы, вторые входы которой объединены и подключены к выходу второго элемента И, а выходы соединены с входами переносов сумматоров млащших разрядов (j-l)-x групп, выход n/k-ro элемента ИЛИ третьей группы подключен к первому входу четвертого элемента И, установочные входы триггеров объединены и подключены к выходу восьмого элемента И, первый вход которого подключен к установочной входной шине сумматора и к установочным входам одноразрядных сумматоров групп, второй вход - к входной шине записи сумматора и первым входам элементов И девятой группы, вторые входы которых подключены к инверсным выходам соответствующих элементов И/И-НЕ группы, выходы элементов И девятой группы подключены к информационным входам соответствующих триггеров, прямые выходы которых подключены к вторым входам соответствующих элементов И пятой группы и к первым входам соответствующих элементов И десятой группы, вторые входы которых объединены и подключены к выходу элемента НЕ, а выхода соединены с входами соответствующих элементов ИЛИ пятой группы, вторые входы которых соединены с выходами соответствующих элементов И одиннадцатой группыд первые входы которых объединены и подключены к входу элемента НЕ, а вторие входы соединены с выходами суммы старших разрядов соответствующих групп, выходы элементов ИЛИ пятой группы являются выходами суммы старших разрядов групп сумматора. На фиг.1 дана блок-схема предлагаемого сумматора; на фиг.2 - схема сравнения переносов или сумм на фиг.З - схема полного п-разрядного сумматора каждой группы. Сумматор содержит n/k групп одноразрядных сумматоров 1. Выходы переносов и сумм одноразрядных сумматоров группы подключены соответственно к схемам сравнения переносов 2 и сумм 3, выходы которых соединены с входами элементов И 4. Прямые выходы элементов И 4 отдельных групп соединены с входами И 5, выход которых подключен к входу элемента И 6 контроля , а инверсные выходы - к первому входу элемента И 7, подключенного к входу установка О триггера 8 соответствующей группы. Вход установка 1 триггера 8 соединен с выходом элемента И 9, к входам которого подключены первая дополнител ная шина 10 установка и вторая дополнительная шина 11 запись сумматора. Второй вход элемента И 7 подключен к второй дополнительной шине 11 запись. Прямой и инверс ный выходы триггера 8 i-ой группы подключены соответственно к входам первого 12 и второго 13 элементов И группы, выходы которых соединены с входами элемента ИЛИ 14. К BTOpiAt входам первого 12 и второго 13 элементов И i-ой группы подключены соответственно выход переноса старшего разряда 1-ой группы и выход элемент ИЛИ 14 1-1 группы. При этом второй вход второго элемента И 13 группы подключен к входу 15 переноса сумматора. Выход элекюнта ИЛИ 14 1-ой группы соединен с первым входом эле мента И 16, к второму входу которого подсоединена дополнительная шина 10 установка. Выход этого элемента ,подключен к первому входу элемента ИЛИ 17, к второму входу которого, за исключением элемента ИЛИ 17 самой старшей групгвы, подключен выход элемента И 18, входы которого связаны с входом 15 переноса .и черев элемент НЕ 19 с дополнительной шиной 10 установка. К второму входу элемента ИЛИ 17 старшей группы, выход которого является выходом 20 переноса сумматора, подключен выход элемента И 5 контроля. Выходы одноразрядных сумматоров rpynmi, за исключением самого старшего разрада группы, подключены к выходу 21 сумматора. Выход старшего разряда группы подключен к первому входу элемента И 22, к второму входу которого подсоединена дополнительная шина 10 установка. Выход элемента И 22 .с&яэан с входом элемента ИЛИ 23, второй вход которого соединен с выходом элемента И 24. Первый вход элемента И 24 соединен с выходом элемента НЕ 19, а второй с прямым, выходом триппера 8. Выход элемента ИЛИ 23 является выходом с- аршего раз ряда группы. Каждая группа сумматора, входы которой соединены с входами 25 и 26 елагаемлх содержит при ргшноразрядных группах п одноразрядных сумматоров 27 (фиг.3)..Выходы переноса отдельных разрядов, за исключением самого старшего, подк чены к входам элементов И 28, вторые входы которых связаны с дополнительной шиной 10 установка, а выходы с первыми входами элементов ИЛИ 29. Вторые входы элементов ИЛИ 29 соединены с выходом элемента ИЛИ 18, а их выходы подключены к входам переноса следующих разрядов. Схема сравнения переносов 2{и сумм 3 может быть выполнена на основе элементов И 30,ИЛИ-НЕ 31 и элемента ИЛИ 32 (фиг.2 в режиме диагкостицирования сумматор работает следующим образом. На шинах 10 установка и 11 запись подаются сигналы, равные логической единице, которые через элемент ,И 9 поступают на входы установка 1 триггеров 8. .Все триггеры 8 переходят в единичное состояние. На этом зёжанчивается подготовительный режим. Для проведения диагностики на шину 10 установка подается сигнал логический нуль.По этому сигналу прерялваются цепи переноса между едйноразрядными сумматорами 27 посредством.элементов И 28, а между группами 1 посредством элементов И 16, Кроме того, этот сигнал инвертируется посредством элемента И 18. Таким .образом,перенос самого младшего разряда сумматора можно подавать единовременно через элементы И 18 и ИЛИ 29 на входы переносов каждого единоразрядного суьолаягора 27 в группах, за исключением одноразрядных сумматоров самых млашиих разрядов групп, перенос на которые подается посредством элемента И 18 и ИЛИ 17. поскольку связь между отдельными одноразрядными сумматорами пре нлвается, то для проверки одноразрядных сумматоров на выходах С и Cj и на входе 15 переноса подают одинаковые набоip:i. Количество таких наборов равно 2. Равенство входных наборов обеспечивает равенство выходных сигналов всех разрядов суюлатора. Путем сравнения этих сигналов судят о правильности работы группы 1 или всего сумматора в цепсм. Сргшнение сигиалов па выходе осуществляется, схемами сравнения переносов 2 и схемами сравнения суьм 3 ДЛ8 каждой 1-группой, а отдельные группы сравниваются между собой элементом И 5. После сравнивания сигвгш с выхода элемеита И 5 через элемент И 6 и ИЛИ 17 подается на выходы 20 сумматора. Если хотя бы один иэ одноразрядных сумматоров неправильно формирует суммы или переносы, ошибка обнаруживается на выходе 20. Используя информацию на выходах схем реюешства сумм 3 и равенства переносов 2 судят- о работе каждой В-о(1 группы. Это осуществляется элементами И 7 и триггерами 8. Если группа работает неправильно, то на инверсном выходе элемента И 4 появляется логическая единица. Этот сигнал через элементы И 7 поступает на вход триггере 8 и изменяет его сосНа(Прямом тояние от выходе триггера 8 появляется О, который через элементы И 24 и ИЛИ 23 появляется на выходе 21 старшего разряда группы {так как на втором входе элемента И 24 с шины 10 I управле- i ние через элемент НЕ 19 подается логическая единица, а на один из входов элемента И 22 с Ц1ины 10 управление подается логический нуль в режиме диагностики). Если сумма и пе реносы в группе формируются правильн jro на выходе старшего разряда сумм группы образуется логическая единиц Если в процессе диагностики обнаруж на ошибка в группе,и триггер изменил свое состояние от 1 в О,то он ос тается в этом состояНИИ.Кроме того, если завершена диагностика и суммато работает в режиме сум1«1ирования, при наличии отказа в группе, с инверсного выхода триггера 8 группы подается логическая единица на один из вхо дов элемента И 13, ас прямого выхода триггера 8 подается логический нуль на один из входов элемента И 12 Это по воляет подать перенос от предьщущей исправно работающей группы на следующую исправно работающую группу, обходя неисправно работающую группу или группы. Если неисправно работает -первая (младшая) группа С, то перенос подается на следующую исправно работающую группу. Это осуществляется элементом И 13 и ИЛИ 14 группы. При правильной работе группы на прямом и обратном выходах триггера 8 стоят соответственно логические 1 и О , которые подаются соответственно на выходы элементов И и И 13. Это позволяет подать перенос с выхода переноса старшего раз ряда группы через элементы И 12 и ИЛИ 14, на вход переноса следующей группы. Схема сумматора позволяет производить диагнозирование при помощи минимального числа наборов. На выходе 20 сумматора получаем информацию о правильности работы сумматора в целом, а на выходе 21 сумм стар ших разрядов каждой группы информацию о правильности работы этой же группы. Кроме этого автоматически отключаются неисправно работающие группы Это позволяет при малом числе отказов применять тот же сумматор, weпол1,зуя только исправно работающие группы. Разбиение группы осуществляют произвольным образом. При исследовании для 16-разрядного сумматора оптимальные результаты дает разбивни на четыре группы. В этом случае дополнительное оборудование, посчитанное на базе двухвходовых элементов,достигает 20%, Аналогично находят максимум для cy Фfaтopa другой разрядности. Данный сумматор позволяет путем введения дополнительного оборудования сократить существенно количество наборов для полной диагнозируемости а отсюда и время диагностики, упростить диагнозирующее устройство, вводя при этом только одну дополнительную шину. При проектировании сумматора предусматривают одну или несколько дополнительных резервных групп, при помощи которых заменяются группы с неисправностями и при этом сумматор не изменяет свою разрядность. Формула изобретения Параллельный комбинационный сумматор, содержащий п одноразрядных сумматоров, с (i-k+l)-ro по i-ый юдноразрядные сумматоры образуют группу, где , 2k, 3k ...n {п - разрядность сумматора, k 1 - произвольное целое число, выходы переносов которых, кроме i-X, подключены к первым входам соответствующих элементов И переноса, вторые входы которых объединены и подключены к установочной входной шине сумматора, а выходы соединены с первыми входами соответствующих элементов ИЛИ переноса, выходы которых соединены с входами переносов одноразрядных сумматоров последующих разрядов, вторые входы элементов ИЛИ объединены и соединены с выходом первого элемента И, первый вход которого подключен к входу переноса младшего разряда сумматора и входной шине переноса сумматора, второй вход к выходу элемента НЕ, вход которого подключен к установочной входной шине устройства, выходы сумм всех одноразрядных сумматоров, кроме 1-х, подключены к выходным шинам сумматора, входы слагаемых всех одноразрядных сумматоров подключены попарно к входным шинам сумматора, второй и трютий элементы И, первые входы которых подключены соответственно к выходу и входу элемента НЕ, а выходы - с входами первого элемента ИЛИ, выход которого является выходом переноса сумматора, ртличающийс я тем, что, с целью повышения надежности, в него введена группа элементов И/И-НЕ, многовходовой элемент И, элемент И, группы элементов И, группы элементов ИЛИ, группу триггеров, блоки сравнения сумм и блоки сравнения переносов, входы каждого блока сравнения сумм и блока сравнения переносов подключены соответственно к выходам суммы и переноса соответствующей группы одноразрядных cyMvjaTopOB, а выходы - к входам соответствующего элемента И/И-НЕ группы, пря1«1е выходы элементов И/И-НЕ группы подключены к входам многовходового элемента И, выход которого подключен к второму входу третьего элемента И, выходы переноса старших разрядов сумматоров (i-x(,2,...n/k)J групп соединены с первыми входами соответствующих элементов И пятой группы, выходы которых подключены к входам соответствующих элементов ИЛИ третьей группы, вторые входы которых подключены к выходам соответствующих элементов И шестой группы,первые входы J-X элементов И шестой группы (J l/2, 3,.. .n/k), подключены к инверсИым выходам соответствующих триггеров

группы, вторые входы, кроме первого элемента И шестой группы, подключены к выходам (j-l)-x элементов ИЛИ третьей группы, второй вход первого элемента И шестой группы подключен к входу переноса сумматора, выходы элементов ИЛИ третьей групщл подключены к первым входги4 соответствуюидах элементов И седьмой групгш, вторые входы которых объединены и подключены к входу элемента НЕ, а выходы соединены с первыми входами соответствующих элементов ИЛИ четвертой группы, вторые входы которой объединены и подключены к выходу второго элемента И, а выходы соединены с входами переносов сумматоров младших раэрядов (j-l)-x групп, выход n/k-ro элемента ИЛИ третьей группы подключен к первоку входу четвертого элемента И, установочные входы триггеров объединены и подключены к выходу восьмого элемента И, первый .вход которого подключен к установочной входной шине сумматора и к установочным входам одноразрядных сумматоров групп, второй вход - к входной шине записи сумматора и первым входам элементов И девятой группы, вторые входы которых подключены к ик.версным выходг1м соответствующих элементов И/И-НЕ группы, выходы эяемен.тов И девятой группы подключены к информационным входам соответствующих триггеров, прямые выходы которых подключены к вторъм входам соответствующих элементов И пятой группы и к первым входам соответствующих элементов И десятой группы, вторые входы которых объединены и подключены к выходу элемента НЕ, а выходы соединены с входами соотэетствующих эле ментов ИЛИ пятой группы, вторые вхо. ды которых соединены с выходами со- , ответствующих элементов И одиннадцатой груптщ, пер&ые входы которых объедшиены и подключены к входу элеS мента НЕ, а вторые входы соединены с выходами суммы старших разрядов соответствующих групп, выходы элемеитов ИЛИ пятой группы, являются выходгми cyi««ii старших разрядов групп

g су о1атора.

Источники 1 информации, принятые во внимание при экспертизе

1. Самофалов К.Г. и др. Электронные цифровые вычислительные машины, Вища школа , Киев, 1976, с. 167,

р 112а.

2. Авторское свидетельство СССР по заявке 9 2519171, кл. G 06 F 7/385, 24.08.78 (прототип)

гТГ:

4

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU955088A1 |

| Множительно-делительное устройство | 1980 |

|

SU920712A1 |

| Цифровой фильтр | 1987 |

|

SU1474676A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

т

та

15

27

26

28

дкоды caaeaefMX .d

Авторы

Даты

1981-01-23—Публикация

1978-10-31—Подача