VI

СО

VI VI ю

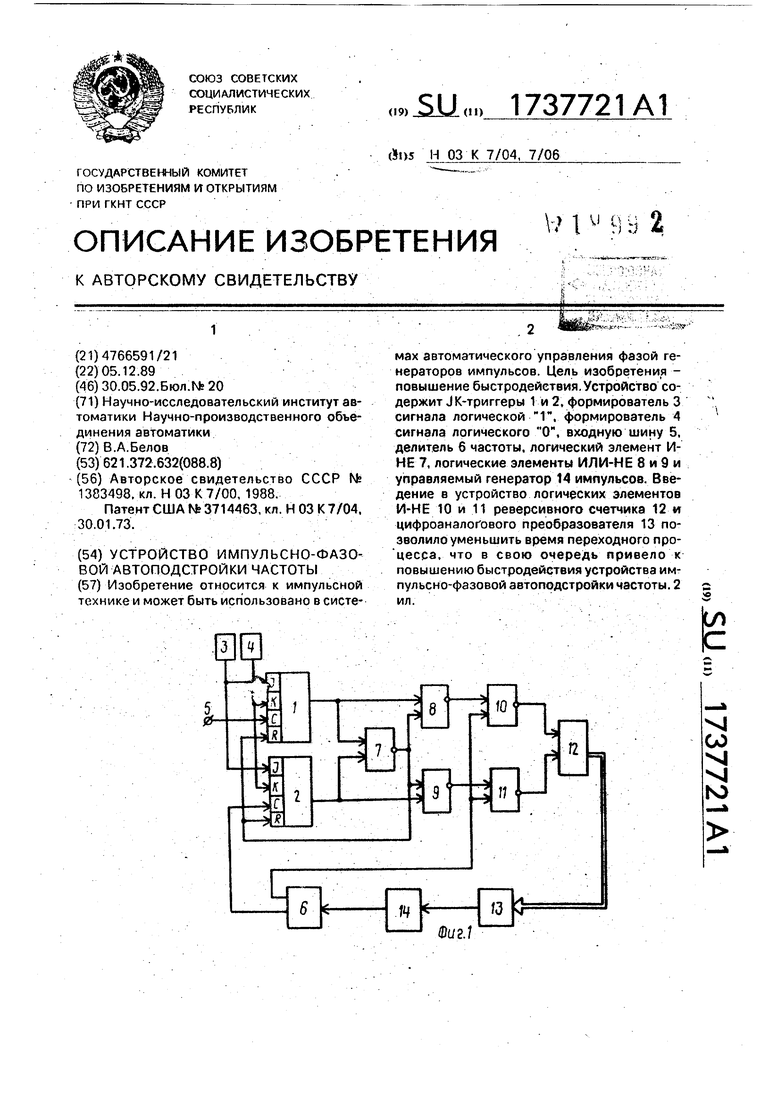

Изобретение относится к устройствам автоматического управления фазой генераторов электронных импульсов и может найти применение в электронике и радиотехнике.

Целью изобретения является повышение быстродействия устройства.

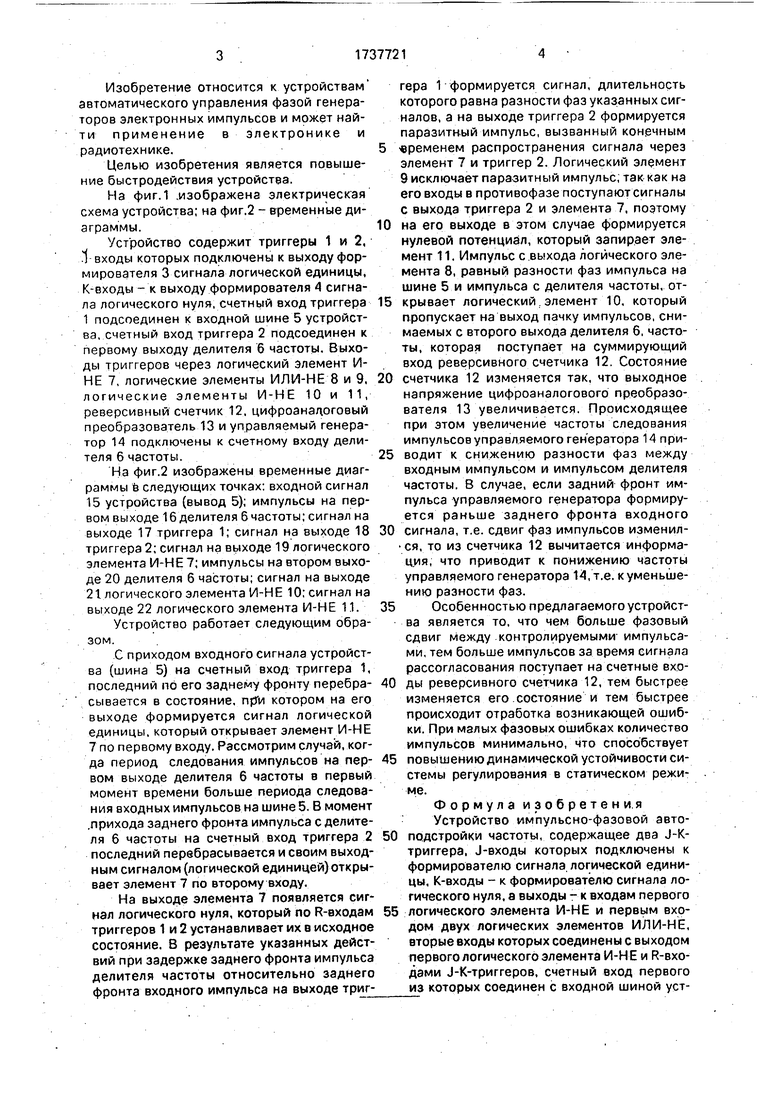

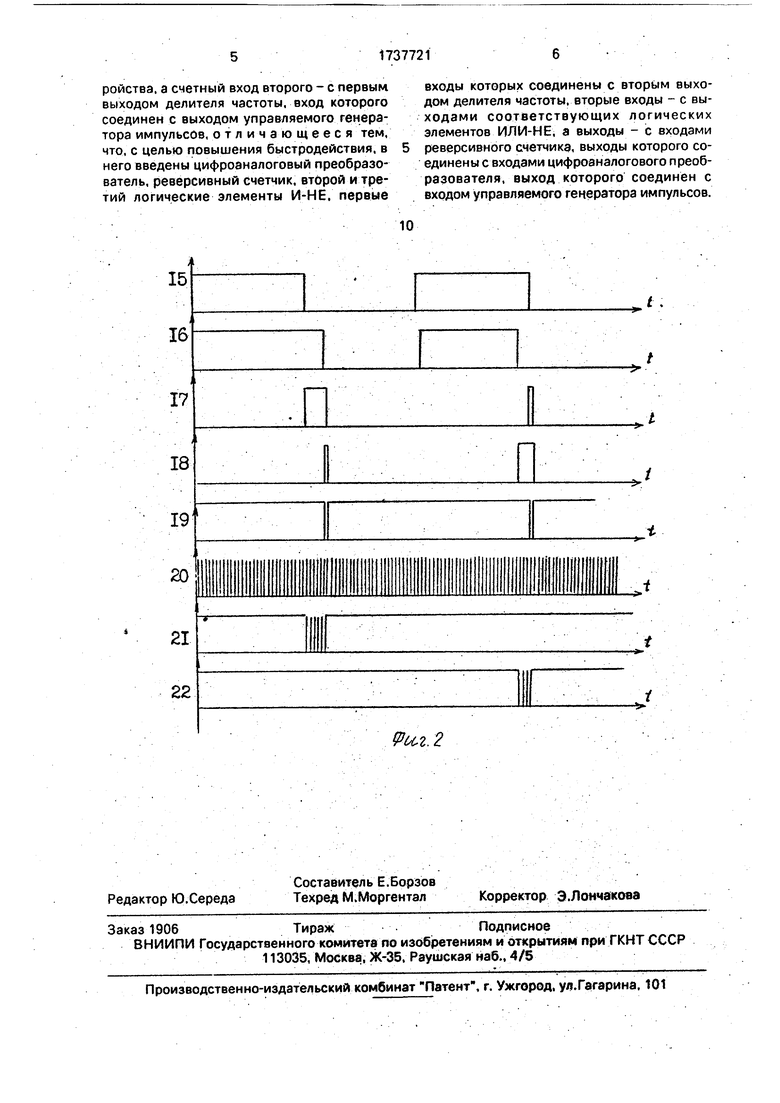

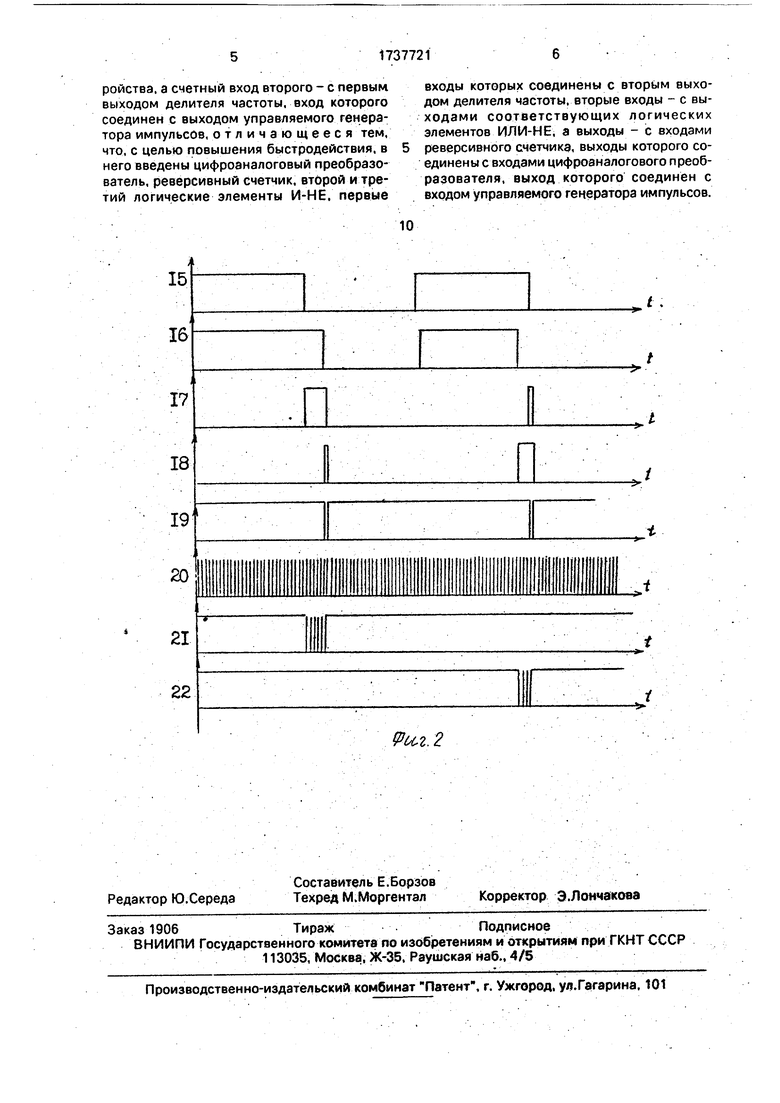

На фиг.1 изображена электрическая схема устройства; на фиг.2 - временные диаграммы.

Устройство содержит триггеры 1 и 2, 1 входы которых подключены к выходу формирователя 3 сигнала логической единицы, К-входы - к выходу формирователя А сигнала логического нуля, счетный вход триггера 1 подсоединен к входной шине 5 устройства, счетный вход триггера 2 подсоединен к первому выходу делителя 6 частоты. Выходы триггеров через логический элемент И- НЕ 7, логические элементы ИЛИ-НЕ 8 и 9, логические элементы И-НЕ 10 и 11, реверсивный счетчик 12. цифроанадоговый преобразователь 13 и управляемый генератор 14 подключены к счетному входу делителя 6 частоты.

На фиг.2 изображены временные диаграммы в следующих точках: входной сигнал 15 устройства (вывод 5); импульсы на первом выходе 16 делителя 6 частоты; сигнал на выходе 17 триггера 1; сигнал на выходе 18 триггера 2; сигнал на выходе 19 логического элемента И-НЕ 7; импульсы на втором выходе 20 делителя 6 частоты; сигнал на выходе 21 логического элемента И-НЕ 10; сигнал на выходе 22 логического элемента И-НЕ 11.

Устройство работает следующим образом.

С приходом входного сигнала устройства (шина 5) на счетный вход триггера 1, последний по его заднему фронту перебрасывается в состояние, npVi котором на его выходе формируется сигнал логической единицы, который открывает элемент И-НЕ 7 по первому входу. Рассмотрим случай, когда период следования импульсов на первом выходе делителя 6 частоты в первый момент времени больше периода следования входных импульсов на шине 5. В момент .прихода заднего фронта импульса с делителя 6 частоты на счетный вход триггера 2 последний перебрасывается и своим выходным сигналом (логической единицей) открывает элемент 7 по второму входу.

На выходе элемента 7 появляется сигнал логического нуля, который по R-входам триггеров 1 и 2 устанавливает их в исходное состояние. В результате указанных действий при задержке заднего фронта импульса делителя частоты относительно заднего фронта входного импульса на выходе триг

гера 1 формируется сигнал, длительность которого равна разности фаз указанных сигналов, а на выходе триггера 2 формируется паразитный импульс, вызванный конечным

«ременем распространения сигнала через элемент 7 и триггер 2. Логический элемент 9 исключает паразитный импульс, так как на его входы в противофазе поступают сигналы с выхода триггера 2 и элемента 7, поэтому

0 на его выходе в этом случае формируется нулевой потенциал, который запирает элемент 11. Импульс с выхода логического элемента 8, равный разности фаз импульса на шине 5 и импульса с делителя частоты, от5 крывает логический элемент 10, который пропускает на выход пачку импульсов, снимаемых с второго выхода делителя 6, частоты, которая поступает на суммирующий вход реверсивного счетчика 12. Состояние

0 счетчика 12 изменяется так, что выходное напряжение цифроаналогового преобразователя 13 увеличивается. Происходящее при этом увеличение частоты следования импульсов управляемого генератора 14 при5 водит к снижению разности фаз между входным импульсом и импульсом делителя частоты. В случае, если задний фронт импульса управляемого генератора формируется раньше заднего фронта входного

0 сигнала, т.е. сдвиг фаз импульсов изменил- ся, то из счетчика 12 вычитается информация, что приводит к понижению частоты управляемого генератора 14, т.е. к уменьшению разности фаз.

5 Особенностью предлагаемого устройства является то, что чем больше фазовый сдвиг между контролируемыми импульсами, тем больше импульсов за время сигнала рассогласования поступает на счетные вхо0 ды реверсивного счетчика 12, тем быстрее изменяется его состояние и тем быстрее происходит отработка возникающей ошибки. При малых фазовых ошибках количество импульсов минимально, что способствует

5 повышению динамической устойчивости системы регулирования в статическом режиме.

Формула изобретения Устройство импульсно-фазовой авто0 подстройки частоты, содержащее два J-K- триггера, J-входы которых подключены к формирователю сигнала логической единицы, К-входы - к формирователю сигнала логического нуля, а выходы - к входам первого

5 логического элемента И-НЕ и первым входом двух логических элементов ИЛИ-НЕ, вторые входы которых соединены с выходом первого логического элемента И-НЕ и R-вхо- дами J-K-триггеров, счетный вход первого из которых соединен с входной шиной устройства. а счетный вход второго - с первым выходом делителя частоты, вход которого соединен с выходом управляемого генератора импульсов, отличающееся тем, что, с целью повышения быстродействия, в него введены цифроаналоговый преобразователь, реверсивный счетчик, второй и третий логические элементы И-НЕ. первые

входы которых соединены с вторым выходом делителя частоты, вторые входы - с выходами соответствующих логических элементов ИЛИ-НЕ, а выходы - с входами реверсивного счетчика, выходы которого соединены с входами цифроаналогового преобразователя, выход которого соединен с входом управляемого генератора импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР СИНУСОИДАЛЬНЫХ СИГНАЛОВ | 1991 |

|

RU2010414C1 |

| Устройство для синхронизации многоканального воспроизведения с носителя магнитной записи | 1984 |

|

SU1150660A1 |

| Электропривод постоянного тока | 1986 |

|

SU1661951A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2024194C1 |

| Умножитель частоты следования импульсов | 1986 |

|

SU1403356A1 |

| Устройство для воспроизведения цифровой информации с носителя магнитной записи | 1987 |

|

SU1427419A2 |

| Устройство для передачи и приема информации по двупроводной линии связи | 1990 |

|

SU1836709A3 |

| Устройство для измерения параметров радиоимпульсов | 1980 |

|

SU938206A1 |

| Цифровой фазометр | 1977 |

|

SU989489A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

Изобретение относится к импульсной технике и может быть использовано в системах автоматического управления фазой генераторов импульсов. Цель изобретения - повышение быстродействия.Устройство содержит JK-триггеры 1 и 2, формирователь 3 сигнала логической 1. формирователь 4 сигнала логического О, входную шину 5, делитель 6 частоты, логический элемент И- НЕ 7, логические элементы ИЛИ-НЕ 8 и 9 и управляемый генератор 14 импульсов. Введение в устройство логических элементов И-НЕ 10 и 11 реверсивного счетчика 12 и цифроаналогового преобразователя 13 позволило уменьшить время переходного про- цесса, что в свою очередь привело к повышению быстродействия устройства им- пульсно-фазовой автоподстройки частоты. 2 ил. у Ё

18

20

п

/

Фи.г.2

| Устройство фазовой автоподстройки частоты | 1985 |

|

SU1383498A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 3714463, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

Авторы

Даты

1992-05-30—Публикация

1989-12-05—Подача