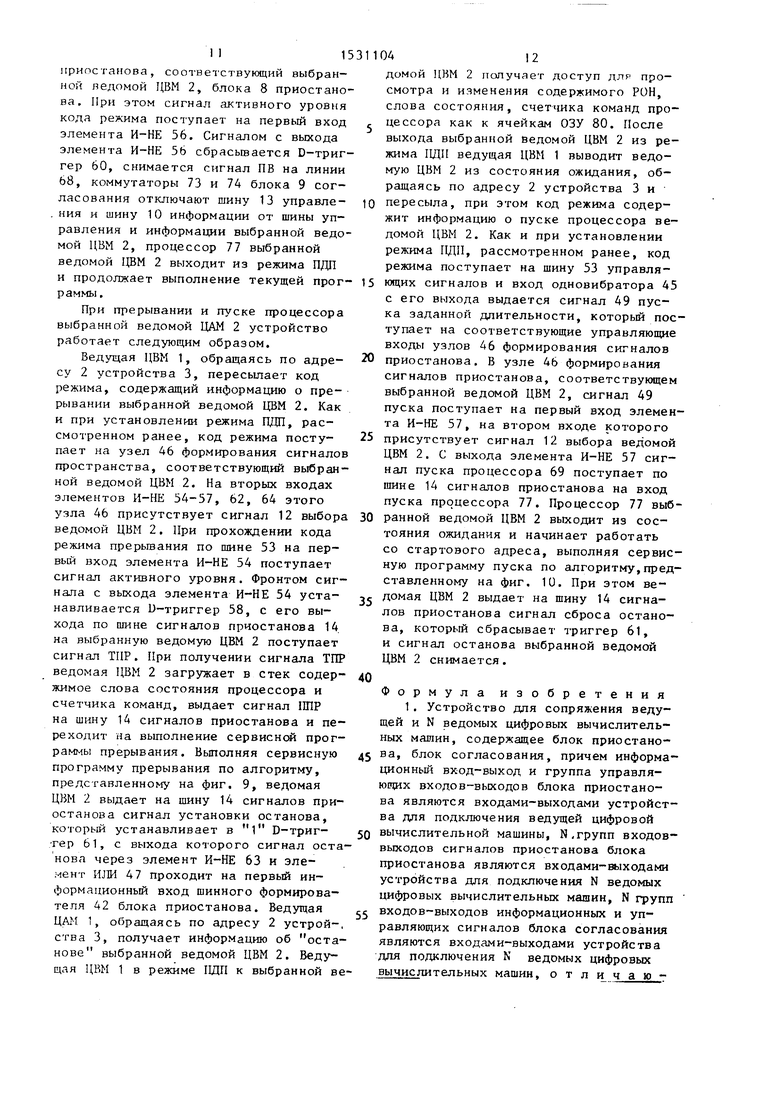

Изобретение относится к вычислительной технике и может быть использовано для сопряжения цифровых вычислительных машин, например, при откладке многомашинной системы.

Целью изобретения является расширение функциональных возможностей устройства для сопряжения ведущей и К ведомых ЦВК за счет реализации доступа ко всему адресному пространству ведомых ЦВМ.

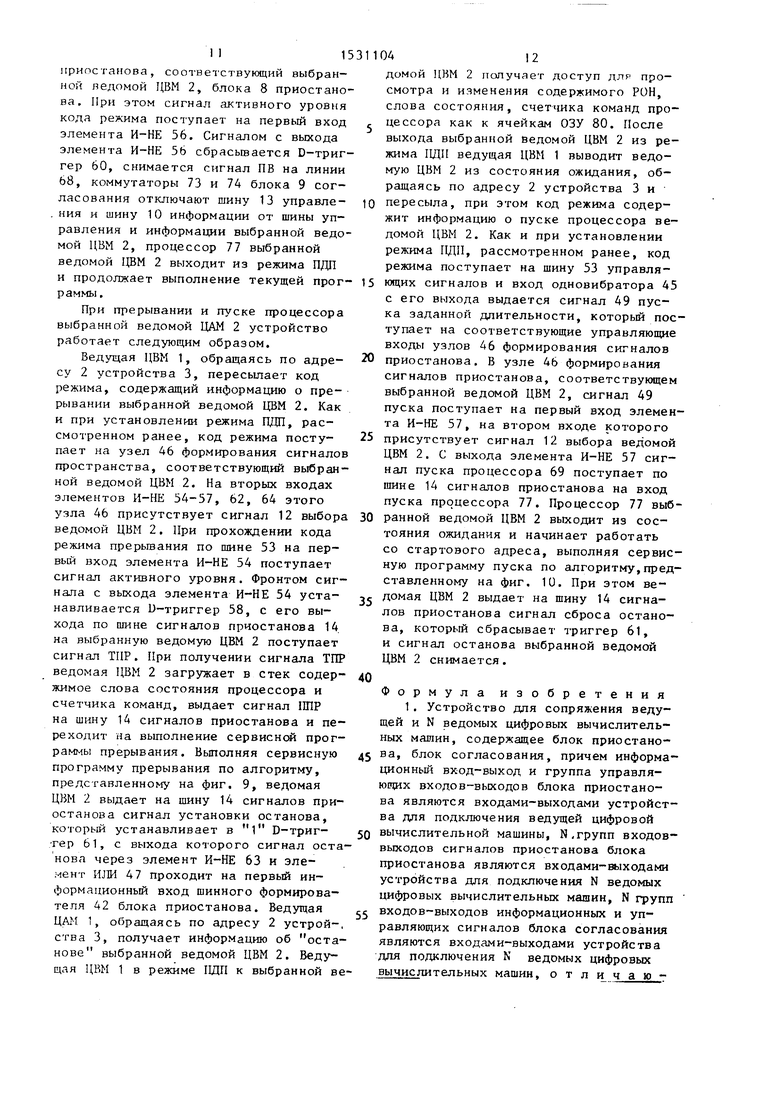

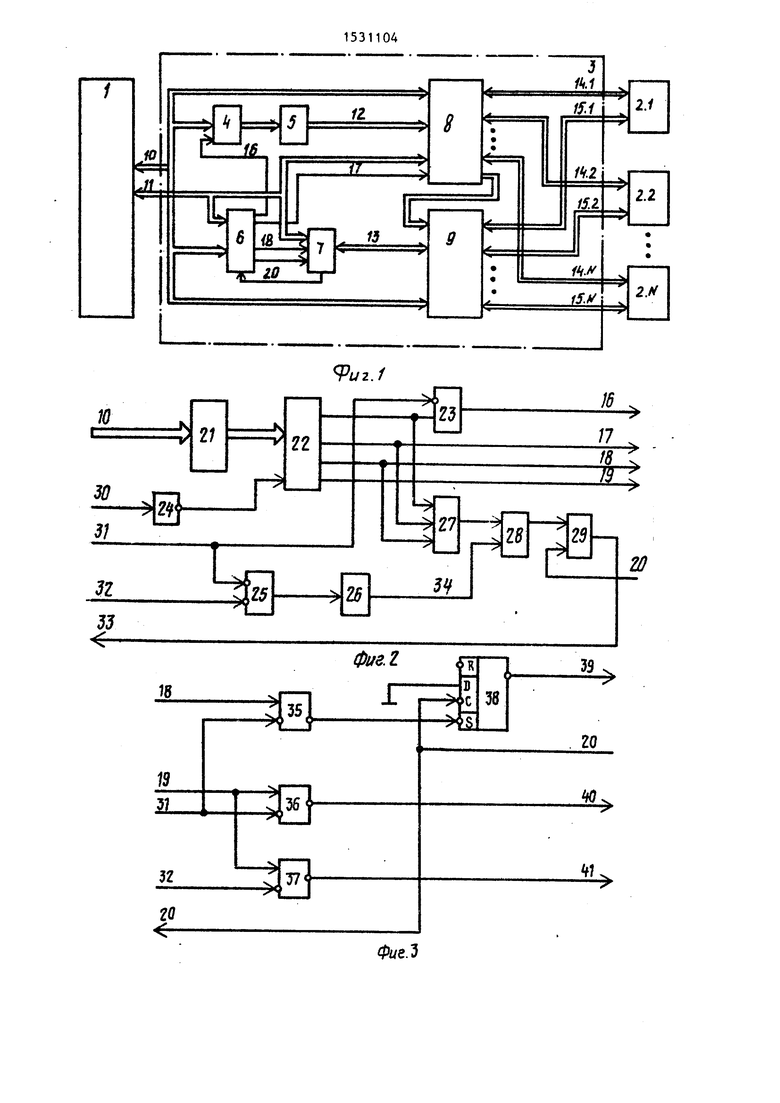

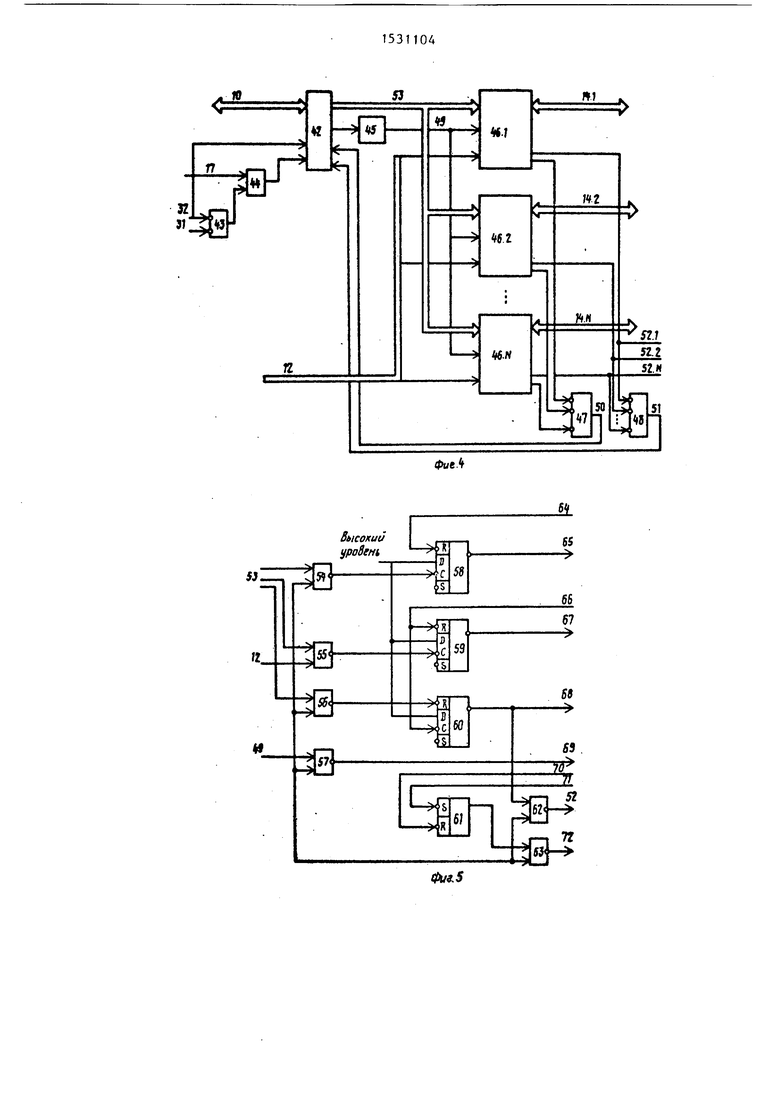

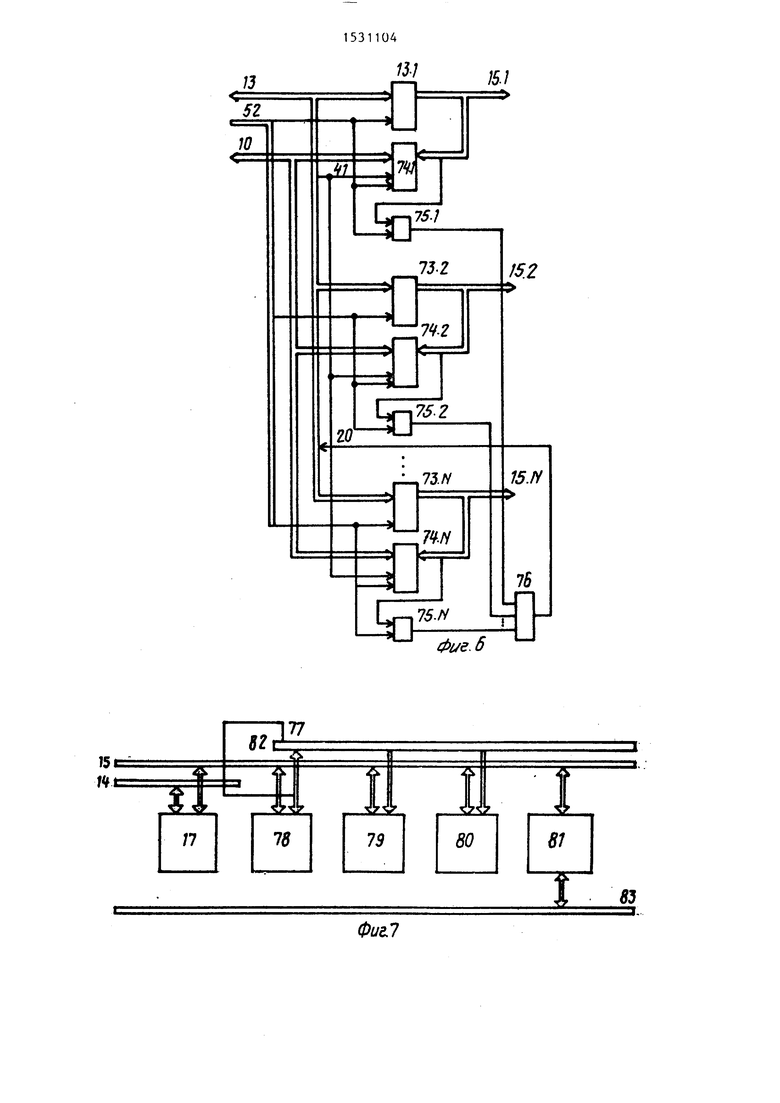

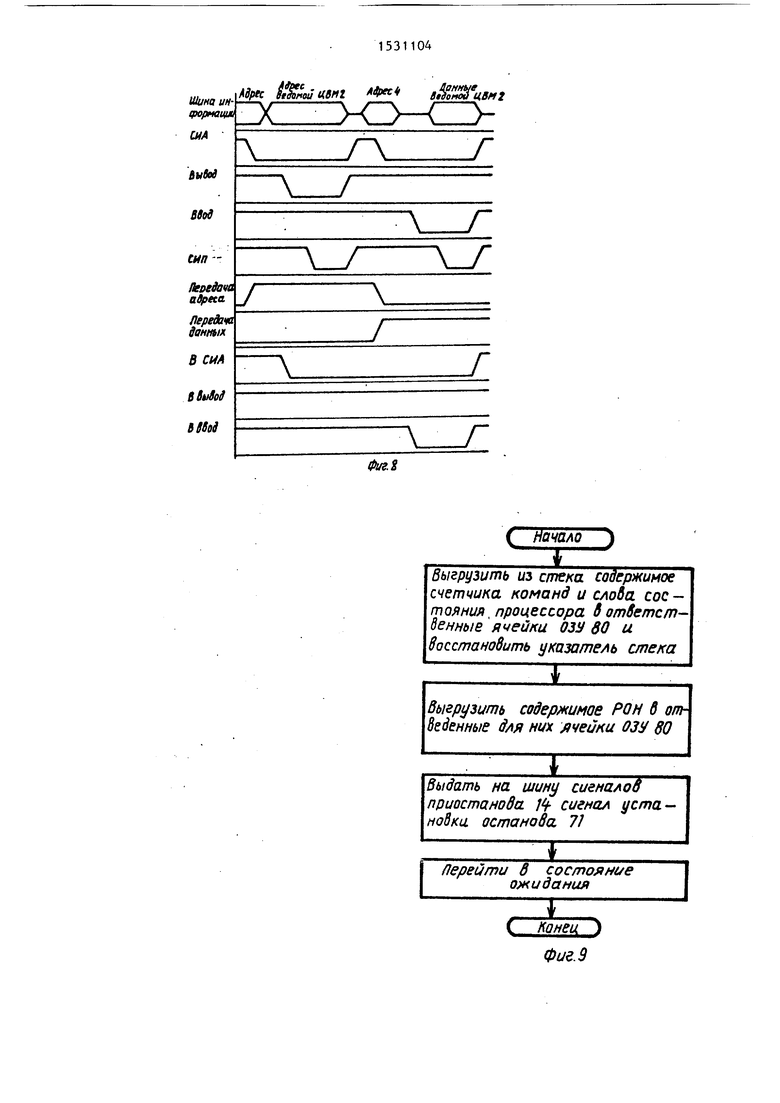

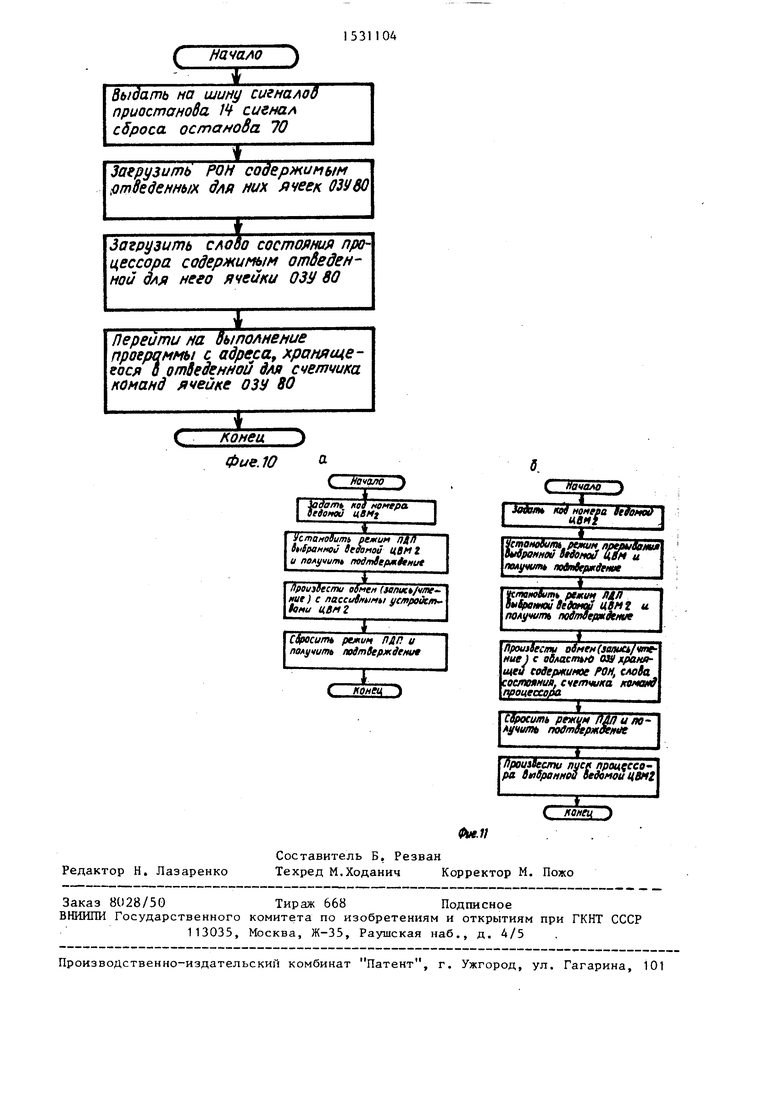

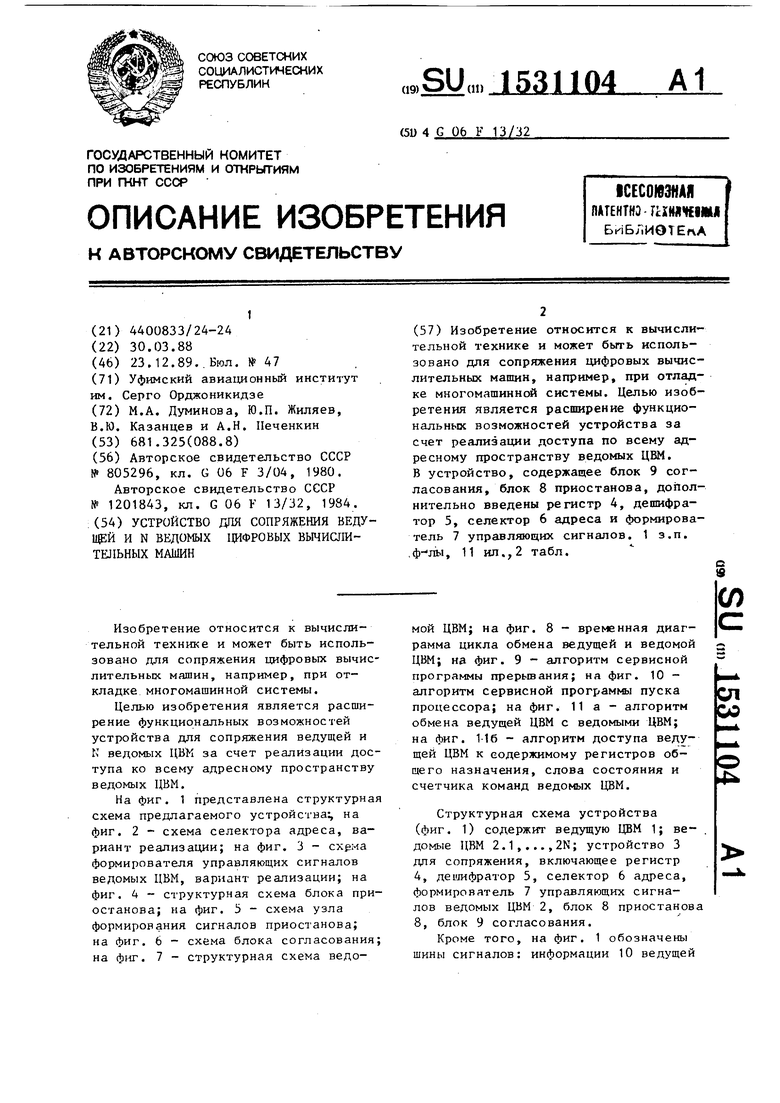

На фиг. 1 представлена структурная схема предлагаемого устройства:, на фиг. 2 - схема селектора адреса, вариант реализации; на фиг. 3 - схема формирователя управляю-щих сигналов ведомых ЦВМ, вариант реализации; на фиг. 4 - структурная схема блока при- останова; на фиг. 5 - схема узла формирования сигналов приостанова; на фиг. 6 - схема блока согласования; на фиг. 7 - структурная схема ведомой ЦВМ; на фиг. 8 - временная диаграмма цикла обмена ведущей и ведомой ЦВМ; на фиг. 9 - алгоритм сервисной программы прерьшания; на фиг. 10 - алгоритм сервисной программы пуска процессора; на фиг. 11 а - алгоритм обмена ведущей ЦВМ с ведомыми ЦВМ; на фиг. 1-16 - алгоритм доступа ведущей ЦВМ к содержимому регистров общего назначения, слова состояния и счетчика команд ведомых ЦВМ.

Структурная схема устройства (фиг. 1) содержит ведущую ЦВМ 1; ведомые ЦВМ 2.1,...,2N; устройство 3 для сопряжения, включающее регистр 4, деишфратор 5, селектор 6 адреса, формирователь 7 управляющих сигналов ведомых ЦВМ 2, блок 8 приостанова 8, блок 9 согласования.

Кроме того, на фиг. 1 обозначены шины сигналов: информации 10 ведущей

tn

Со

ВМ 1, управления 11 ведущей ЦВМ 1, ыбора 12 ведомой ЦВМ 2, управления 13 ведомой ЦВМ 2, приостанова 14.1, ...14.N ведомых ЦВМ 2.12.N, информации и управления 15.1,...15.N ведомых ЦВМ 2.1,...,2.N; а также цепи сигналов: записи 16 в регистр 4; обращения 17 к блоку 8 приостанова; передачи адреса 18; передачи данных 19; готовности 20.

Схема селектора адреса (фиг. 2) еализована для ведущей ЦВМ с интерфейсом по ОСТ 11.305.903-80. Она содержит дешифратор 21, регистр 22, первый элемент И 23, элемент НЕ 24, первый элемент ИЛИ 25, элемент 26 задержки, второй элемент ИЖ 27, второй элемент И 28, третий элемент ИЛИ 29. Кроме того, на фиг. 2 обозначены цепи сигналов тины 11 управления ведущей ЦВМ 1, которые являются стандартными сигналами интерфейса по ОСТ П.305.903-80: СНА 30, вывод 31, ВВОД 32, СИП 33, а также сигнал готовности селектора адреса (ГС) 34. Схема формирователя управляющих сигналов ведомых ЦВМ (фиг. 3) также реализована для ведомых ЦВМ с интерфейсом по ОСТ 11.305.903-80. Она содержит первый, второй, третий элементы И-НЕ 35-37, 1)-триггер 38.

Кроме того, на фиг. 3 обозначены цепи сигналов шины 13 управления ведомых ЦВМ 2, являющиеся стандартными сигналами интерфейса по ОСТ 11.305. 903-80: в СИЛ 39; В ВЫВОД 40; В ВВОД 41.

Структурная схема блока приостано- ва(фиг. 4) содержит шинный формирователь 42, первый элемент ИЛИ 43, элемент И 44, одновибратор 45, узлы 46.1,...46.N формирования сигналов приостанова, второй 47 и третий 48 элементы ИЛИ.

Кроме того, на фиг. 4 обозначены цепи сигнала пуска 49, суммарного сиг нала останова 50, суммарного сигнала подтверждения выбора 51 ведомой ЦВМ 2 цепи сигналов подтверждения выбора 52.1,...,52.N ведомых ЦВМ 2,. а также шина управлящих сигналов 53 узла формирования сигналов приостанова 46.

Схема узла формирования сигналов приостанова (фиг. 5) содержит с первого по четвертый элементы И-НЕ 54- 57, с первого, по четвертый U-тригге- ры 58-61, пятый 62 и шестой 63 элементы И-НЕ,

0

5

0

5

0

5

0

5

Кроме того, на фиг. 5 обозначены цепи сигналов, составляющие шину 14 сигналов приостанова ведомой ЦВМ 2: подтверждения прерьюания (ППР) 64, требования прерывания (ТПР) 65, подтверждения прямого доступа к памяти (ШЩ) 66, требования прямого доступа (Т11Д) 67, подтверждения выбора СПВХ 68, пуска 69 процессора ведомой ЦВМ 2, сброса останова 70, установки останова 71, а также цепь сигнала останова 72.

Схема блока согласования и управления памятью содержит (фиг. 6) коммутаторы 73.1,...,73.N шины управления ведомых ЦВМ 2; коммутаторы 74,1, ,..,74,N шины информации ведомых ЦВМ 2; элементов И 75.1,...,75.N; элемент ИЛИ 76.

Структурная схема ведомой ЦВМ (фиг, 7) включает в себя процессор 77, регистр адреса и селектор адреса 78, постоянное запоминающее устройство (ЦЗУ) 79, оперативное запоминающее устройство (ОЗУ) 80, блок 81 сопряжения с внешней магистралью.

Кроме того, на фиг. 7 обозначены юша адреса 82 ведомой ЦВМ 2, внешняя магистраль 83 ведомой ЦВМ 2, к которой могут быть подключены внешние устройства и другие ведомые ЦВМ 2,

Устройство 3 совместно с ведущей ЦВМ 1 и ее программным обеспечением предназначено для отладки, диагностики и контроля функционирования многомашинной системы, содержащей ЦВМ 2. Отладка многомашинной системы включает в себя: отладку ЦВМ 2.1,,.,,2,N; отладку внешних устройств ЦВМ 2,1,.,. 2.N, отладку программного обеспечения ЦВМ 2.1,.,.,2.N, отладку функционирования многомашинной системы в целом в реальном масштабе времени.

На время отладки ЦВМ 2,1,,,.,2,N и их программного обеспечения постоянное запоминающее«устройство 79 отлаживаемой ЦВМ 2 заменяется на эмулятор ПЗУ (ЭПЗУ) - оперативное запоминающее устройство. Эта позволяет оперативно записывать сервисные отладочные и рабочие программы и корректировать программное обеспечение ЦВМ 2 в процессе его отладки.

Устройство 3 занимает четыре адреса из адресного пространства ведущей, ЦВМ 1. В процессе работы ведущая ЦВМ 1, обращаясь к четырем адресам устройства 3, управляет его работой.

Обра1цаясь по адресам устройства 3 ведугдая ЦЬМ 1 может:

задать код номера ведомой ЦВМ 2 (выбрать одну из N ведомых ЦВМ 2); задать режим работы блока 8 приоста- нова с выбранной ведомой ЦВМ 2. Возможные режимы работы сведены в табл. 1.

Таблица 1 10

Режимные работы блока 8 приостанова

Установление режим прямого доступа к памяти (ЩЩ) ведомой ЦВМ 2 Сброс режима ПДП ведомой ЦВМ 2 Режима прерывания ведомой ЦВМ 2 Пуск процессора ведомой ЦВМ 2

Ведущая ЦВМ также может произвести обмен информацией с пассивными устройствами (ПЗУ 79, ОЗУ 80, ВУ) через .блок 81 сопряжения ведомой ЦВМ 2, находящейся в режиме ПДП.

Селектор 6 адреса предназначен для распознавания четырех адресов устройства 3. Выходные сигналы селектора 6 адреса и логика их формирования из сигналов шин управления 11 и информации 10 ведущей ЦВМ 1 представлены в табл. 2.

Таблица 2

Выходные сигналы селектора 6 адреса

Логика формирования

17 ан

Адрес 1 Л СИЛ ЗОЛ ВЫВОД 31 Адрес 2 СИА 30

Адрес 3 СИА 30

50

Адрес 4 СКА 30 (запись 16 V обраще-55 ние 17 V передача адреса 18) Л ГС готовность 20

0

5

0

5

0

5

0

5

0

5

Сигнал ГС 34 $юрмируется по следующей логике: (ВЫВОД 31 V ВВОД 32)Лс на элементе ШШ 25 и элементе 26 задержки, (cj, - время задержки переднего фронта сигнала).

Регистр 4 и дешифратор 5 предназначен для хранения и дешифрации кода выбора номера ведомой ЦВМ 2.

Блок приостанова 8 предназначен для организации различных режимов ра- боты выбранной ведомой ЦВМ 2.

Режим ПДП предназначен для организации обмена информацией между ведущей ЦВМ 1 и пассивными устройствами выбранной ведомой ЦВМ 2, находящейся в режиме ПДП. В режиме ПДП процессор 77 ведомой ЦВМ 2 остановлен и отключен от шины 15 управления и информации, при этом ведущая ЦВМ 1 имеет возможность управлять работой пассивных устройств ведомой ЦВМ 2 (эмулировать функции процессора 77 ЦВМ 2).

Режим прерьшания и режим пуска процессора 77 ведомой ЦВМ 2 предназначены для обеспечения доступа ведущей ЦВМ 1 к содержимому РОН, слова состояния и счетчика команд процессора 77 ведомой ЦВМ 2. Причем предварительно в ЭПЗУ 79 ведомой ЦВМ 2 в режим ПДП должны быть загружены сервисные программы обслуживания прерывания и пуска процессора, которые помещаются туда на время отладки аппаратуры и ПО ведомой ЦВМ 2.

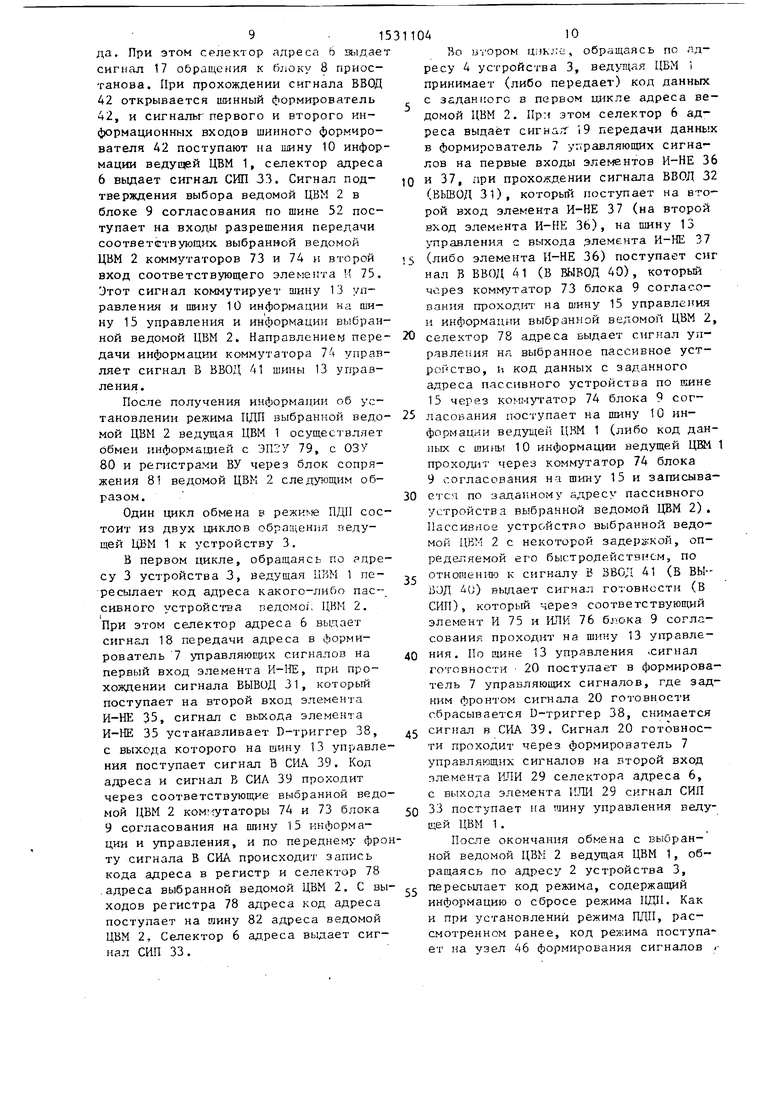

Выполнение сервисной программы прерывания (фиг. 9) обеспечивает выгрузку в отведенную область ОЗУ 80 содержимого РОН, слова состояния и счетчика команд процессора 77 и переход ведомой ЦВМ 2 в состояние ожидания. Таким образом, ведущая ЦВМ 1 получает возможность просмотра или изменения содержимого РОН, слова состояния и счетчика команд процессора 77 ведомой ЦВМ 2 как ячеек ОЗУ 80.

Выполнение сервисной программы пуска процессора (фиг. 10) обеспечивает загрузку РОН, слова состояния и счетчика команд содержимым отведенной области ОЗУ 80 и возвращение ЦВМ 2 к выполнению прерванной программы либо по новому заданному адресу счетчика команд.

Блок приостанова 8 также предназначен дли выдачи ведущей ЦВМ 1 информации об установлении (снятии) режима ПДП и режима прерывания выбранной ведомой ЦВМ 2.

Блок 9 согласования предназначен для коммутации шин управления 13 и информации 10 на шину 15 управления и информации выбранной ведомой ЦВМ 2, находящейся в режиме 1ЩП.

Формирователь 7 управляющих сигналов обеспечивает доступ ведущей 1Д4М 1 к всему адресному пространству ведомой ЦВМ 2. Для организации такого доступа использованы всего два адреса из адресного пространства ведущей ЦВМ 1 (адрес 3 и адрес 4 устройства 3). Цричем один цикл обмена с ведомой ЦВМ 2 содержит два цикла обмена ведущей ЦВМ 1 с устройства 3 (фиг. 8). Первый цикл предназначен для передачи кода адреса ведомой ЦВМ 2, второй - для обмена данными с ведомой ЦВМ 2,

Формирователь 7 управляющих сигна- лов Предназначен для формирования сигналов шины 13 управления ведомой ЦВМ 2 из сигналов управления двух циклов обмена ведущей ЦВМ 1 и сигна- лов передачи адреса 18 и передачи данных 19 селектора адреса 6.

Ведущая ЦВМ 1 осуществляет обмен с ведомым ЦВМ 2 по алгоритму,, представленному на фиг. Па, доступ к со держимому РОН ,слову состояния и счетчику команд ведомых ЦВМ 2 осуществляется по алгоритму, представленному на фиг. 116.

Устройство 3 работает следующим образом.

Ведущая ЦВМ 1, обращаясь по адресу 1 устройства 3, пересылает по шине 10 код выбора номера ведомой ЦВМ При этом селектор адреса 6 формирует сигнал записи 16, по которому код выбора с шины 10 информации ведущей ЦВМ 1 записывается в регистр 4. Сигнал выбора ведомой ЦВМ 2 по шине 12 поступает в блоке приостанова 8.

Ведущая ЦВМ 1, обращаясь по адресу 2 устройства 3, пересылает код режима работы с выбранной ведомой ЦВМ При этом селектор адреса 6 выдает си нал 17 обращения в блок 8 приостанова. При прохождении сигнала ВЫВОД 31 по шине 11 управления код режима работы с шины 10 информации ведущей ЦВМ 1 через открытый шинный формирователь 42 проходит на шину управляющих сигналов 53 и вход :одновибратор 45 блока 8 приостанова. Направлением передачи шинно-го формирователя 42 уп равляет сигнал ВВОД 32 шины 11 управ

о

5

0

5

ления ведущей ЦВМ 1, а сигнал разрешения передачи формируется по логике: обращение 17 Л (ВЫВОД 32 V ВВОД 31) на элементах ИЛИ 43 и И 47. Сигналы кода режима по шине 53 и цепи 49 поступают на выходы узлов формирования сигналов приостанова 46. Активный уровень сигнала выбора 12 ведомой ЦВМ 2 есть на выходе только одного узла 46 формирования сигналов приостанова, соответствующего выбранной ведомой ЦВМ 2. Сигнал выбора присутствует на вторых входах элементов И-НЕ 54-57 и разрешает прохождение сигналов кода режима через эти элементы И-НЕ. Пусть код режима несет информа- цию об установлении режима ПДП выбранной ведомой ЦВМ 2, тогда во время прохождения сигнала ВЫВОД 31 на первый вход элемента И-НЕ 55 поступает активный уровень сигнала кода режима. D-триггер 59 фронтом сигнала с выхода элемента И-НЕ 55 устанавливается, и с выхода триггера 59 на шину сигналов приостанова 14 выбранной ведомом- ЦВМ 2 поступает сигнал ТПД 67. Селектор адреса 6 выдает сигнал СИП 33. По сигналу ТПД 67 процессор 77 выбранной ведомой ЦВМ 2 приостанавливает выполнение текущей программы, отключается от шины 15 информации и управления и выдает сигнал ШЩ 66 на шину 14 сигналов приостанова. Сигнал ППД 66 сбрасывает U-триггер 59, при этом снимается сигнал ТПД 67, а также фронтом сигнала ПОД 66 устанавливается D-триггер 60, с выхода которого на шину 14 сигналов приостанова выбранной ведомой ЦВМ 2 выдается сигнал ПВ 68. Наличие сигнала ЦБ 68 на шине 14 сигналов приостанова означает установление режима ПДП выбранной ведомой ЦВМ 2. Сигнал ПВ 69 поступает также на первый вход элемента И-НЕ 62, на втором входе которого присутствует сигнал 12 выбора ведомой ЦВМ 2. С выхода элемента И-НЕ 62 сигнал подтверждения выбора ведомой ЦВМ 2 поступает по шине 52 на блок 9 согласования, а также на соответствующий вход элемента ИЛИ 48, с выхода которого суммарный сигнал 51 подтверждения выбора поступает на второй информационный вход шинного формирователя 42.

Ведущая ЦВМ 1 получает информацию об установлении (либо снятии) режима ПДП выбранной ведомой ЦВМ 2, обращаясь по адресу 2 устройства 3 в цикле ввода. При этом селектор адреса 6 сигнал 17 обращения к блоку 8 приос- танова. При прохождении сигнала ВВОД 42 открывается шинный формирователь 42, и сигналы первого и второго информационных входов шинного формирователя 42 поступают на шину 10 информации ведущей ЦВМ 1, селектор адреса 6 выдает сигнал СИП 33. Сигнал подтверждения выбора ведомой ЦВМ 2 в блоке 9 согласования по шине 52 поступает на входы разрешения передачи соответствующих выбранной ведомой ЦВМ 2 коммутаторов 73 и 74 и второй вход соответствующего элемента И 75. Этот сигнал коммутирует шину 13 управления и шину 10 информации на шину 15 управления и информации выбранной ведомой ЦВМ 2. Направлением передачи информации коммутатора 74 управляет сигнал В ВВОД 41 шины 13 управления.

После получения информации об установлении режима ИДИ выбранной ведомой ЦВМ 2 ведущая ЦВМ 1 осуществляет обмен информацией с ЭПЗУ 79, с ОЗУ 80 и регистрами ВУ через блок сопряжения 81 ведомой ЦВМ 2 следующим образом.

Один цикл обмена в peKHNse ПДЦ состоит из двух циклов обращения ведущей ЦВМ 1 к устройству 3,

В первом цикле, обращаясь по адресу 3 устройства 3, ведущая ЦКМ 1 пе- ресылает код адреса какого-либо пассивного устройства ведомо ; ЦВМ 2. При этом селектор адреса 6 выдает сигнал 18 передачи адреса в формирователь 1 управляюЕщх сигналов на первый вход элемента И-НЕ, при прохождении сигнала ВЫВОД 31, который поступает на второй вход элемента И-НЕ 35, сигнал с выхода элемента И-НЕ 35 устанавливает D-триггер 38, с выхода которого на шину 13 управления поступает сигнал В СНА 39. Код адреса и сигнал В СИЛ 39 проходит через соответствующие выбранной ведомой ЦВМ 2 ком тутаторы 74 и 73 блока 9 согласования на шину 15 информации и управления, и по переднему- фронту сигнала В СИЛ происходит запись кода адреса в регистр и селектор 78 .адреса выбранной ведомой ЦВМ 2. С выходов регистра 78 адреса код адреса поступает на шину 82 адреса ведомой ЦВМ 2, Селектор 6 адреса выдает сигнал СИП 33.

Во B l OpoM цикле, обращаясь по лд- ресу 4 устройства 3, вeдyп aя ЦВМ 1 принимает (либо передает) код данных с заданного в первом илкле адреса ведомой ЦВМ 2. При этом селектор 6 адреса выдаёт сигна;г (9 передачи данных в формирователь 7 управляющих сигналов на первые входы элементов И-НЕ 36

и 37, при прохождении сигнала ВВОД 32 (ВЬШОД 31), которьш поступает на второй вход элемента И-НЕ 37 (на второй вход элемента И-НЕ 36), на шину 13 управления с выхода элемента И-НЕ 37

(либо элемента И-НЕ 36) поступает сиг нал В ВВОД 41 (В №ВОД 40), которьй через коммутатор 73 блока 9 согласования проходит на шину 15 управле1 ия и информации выбранной ведомой ЦВМ 2,

селектор 78 адреса выдает сигнал управления ня. выбранное пассивное устройство, и код данных с заданного адреса пассивного устройства по шине 15 через коммутатор 74 блока 9 согласования поступает на шину 10 информации ведущей ЦВМ 1 (либо код данных с шины 10 информации ведущей ЦШ 1 проходит через коммутатор 74 блока 9 согласования на шину 15 и записыва-

ется по заданному адресу пассивного устройства выбранной ведомой ЦВМ 2). Пассивное устройство выбранной ведомой ЦВМ 2 с некоторой задера- кой, определяемой его быстродействием, по

отношению к сигналу В ВВОД 41 (В ВЫ-- БЭД 40) выдает сигна: готовности (В СИП), который череэ соответствующий элемент И 75 и 1ШИ 76 блока 9 согласования проходит на шику 13 управления. По щине 13 управления 1сигнал готовности 20 поступает в формирователь 7 управляющих сигналов, где задним фронтом сигнала 20 готовности сбрасывается D-триггер 38, снимается

сигнал в СИЛ 39. Сигнал 20 готовности проходит через формирователь 7 управляющих сигналов на второй вход элемента ИЛИ 29 селектора адреса 6, с выхода элемента ИЛИ 29 сигнал СИП

33 поступает на тайну управления ведущей ЦВМ 1 .

После окончания обмена с выбранной ведомой ЦВМ 2 ведущая ЦВМ 1, обращаясь по адресу 2 устройства 3,

пересылает код режима, содержагций информацию о сбросе режима 1ЩП. Как и при установлений режима ПДП, рассмотренном ранее, код режима поступает на узел 46 формирования сигналов /

11

ириостанова, соответствующий выбранной ведомой ЦВМ 2, блока 8 приостано- ва. При этом сигнал активного уровня кода режима поступает на первый вход элемента И-НЕ 56. Сигналом с выхода элемента И-НЕ 56 сбрасьшается D-триггер 60, снимается сигнал ПВ на линии 68, коммутаторы 73 и 74 блока 9 согласования отключают шину 13 управления и шину 10 информации от шины управления и информации выбранной ведомой ЦВМ 2, процессор 77 выбранной ведомой ЦВМ 2 выходит из режима ПДП и продолжает выполнение текущей программы ,

При прерывании и пуске процессора выбранной ведомой ДАМ 2 устройство работает следующим образом.

Ведущая ЦВМ 1, обращаясь по адресу 2 устройства 3, пересылает код режима, содержащий информацию о прерывании выбранной ведомой ЦВМ 2. Как и при установлении режима ПДП, рассмотренном ранее, код режима поступает на узел 46 формирования сигналов пространства, соответствующий выбранной ведомой ЦВМ 2. На вторых входах элементов И-НЕ 54-57, 62, 64 этого узла 46 присутствует сигнал 12 выбора ведомой ЦВМ 2. При прохождении кода режима прерьшания по шине 53 на первый вход элемента И-НЕ 54 поступает сигнал активного уровня. Фронтом сигнала с выхода элемента И-НЕ 54 устанавливается D-триггер 58, с его выхода по шине сигналов приостанова 14 на выбранную ведомую ЦВМ 2 поступает сигнал ТПР. При получении сигнала ТОР ведомая ЦВМ 2 загружает в стек содержимое слова состояния процессора и счетчика команд, выдает сигнал ШР на шину 14 сигналов приостанова и переходит на выполнение сервисной программы прерывания. Вьшолняя сервисную программу прерывания по алгоритму, представленному на фиг, 9, ведомая ЦВМ 2 выдает на шину 14 сигналов приостанова сигнал установки останова, который устанавливает в 1 D-триг- тер 61, с выхода которого сигнал останова через элемент И-НЕ 63 и элемент ИЛИ 47 проходит на первый информационный вход шинного формирова теля 42 блока приостанова. Ведущая ЦАМ I, обращаясь по адресу 2 устрой-. ства 3, получает информацию об останове выбранной ведомой ЦВМ 2. Ведущая ЦВМ 1 в режиме 1ЩП к выбранной ве153110412

домой ЦВМ 2 получает доступ для просмотра и изменения содержимого РОН, слова состояния, счетчика команд процессора как к ячейкам ОЗУ 80. После выхода выбранной ведомой ЦВМ 2 из режима 1ЩП ведущая ЦВМ 1 выводит ведомую ЦВМ 2 из состояния ожидания, обращаясь по адресу 2 устройства 3 и

10 пересыла, при этом код режима содержит информацию о пуске процессора ведомой ЦВМ 2. Как и при установлении режима ГЩП, рассмотренном ранее, код режима поступает на шину 53 управля15 ющих сигналов и вход одновибратора 45 с его выхода выдается сигнал 49 пуска заданной длительности, который поступает на соответствующие управляющие входы узлов 46 формирования сигналов

20 приостанова. В узле 46 формирования сигналов приостанова, соответствукщем выбранной ведомой ЦВМ 2, сигнал 49 пуска поступает на первый вход элемента И-НЕ 57, на втором входе которого

25 присутствует сигнал 12 выбора ведомой ЦВМ 2. С выхода элемента И-НЕ 57 сигнал пуска процессора 69 поступает по щине 14 сигналов приостанова на вход пуска процессора 77. Процессор 77 выб30 ранкой ведомой ЦВМ 2 выходит из состояния ожидания и начинает работать со стартового адреса, выполняя сервисную программу пуска по алгоритму,представленному на фиг. 10. При этом ве,, домая ЦВМ 2 выдает на шину 14 сигналов приостанова сигнал сброса останова, который сбрасывает триггер 61, и сигнал останова выбранной ведомой ЦВМ 2 снимается.

40

Формула изобретения 1. Устройство для сопряжения ведущей и N ведомых цифровых вычислительных мащин, содержащее блок приостано45 ва, блок согласования, причем информационный вход-выход и группа управляющих входов-выходов блока приостанова являются входами-выходами устройства для подключения ведущей цифровой

50 вычислительной машины, N,групп входов- выходов сигналов приостанова блока приостанова являются входами-выходами устройства для подключения N ведомых цифровых вычислительных машин, N групп

55 входов-выходов информационных и управляющих сигналов блока согласования являются входами-выходами устройства для подключения N ведомых цифровых вычислительных машин, о т л и чаю1315

щ е е с я тем, что, с целью расширения функциональных возможностей за счет реализации доступа ведур;ей цифровой вычислительной машины по всему адресному пространству ведомых цифровых вычислительных машин, введены селектор адреса, формирователь управляющих сигналов, регистр и дешифратор, причем информационный вход-выход блока приостанова соединен с одноименными входами-выходами блока согласования регистра и селектора адреса, группа управляющих входов-выходов блока ири- остйнова соединена с одноименными

входами-выходами группы селектора адреса и формирователя управляющих сигналов, группа входов-выходов управления ведущей цифровой вычислительной машины которого соединена с одно- именными входами-выходами группы блока согласования, выход записи селектора .адреса соединен с одноименным входом регистра, информационный выход которого соединен с одноименным вхо- дом дешифратора, выходы которого соединены с входами выбора ведущей цифровой вычислительной машины, блока приостанова, выход обращения селектора адреса соединен с одноименным входом блока приостанова, вьсходы Передача адреса и Передача данных селектора адреса соединены с одноименными входами формирователя сигналов, выход готовности которого соединен с входом селектора адреса, группа входов-выходов управления ведомыми цифровыми вычислительньми машинами устройства .соединена с одноименныг-ш входами-выходами группы блока согласова- ния, группа входов подтверждения выбора которого соединена с одноименными выходами группы блока приостанова.

2. Устройство по п. 1, о т л и ч а

ю щ е е с я тем, что блок приостано

.. ,

20 25 зо .Q

5

5

0414

ва содержит шинный формирователь, одновибратор, N узлов формирования сигналов приостанова, с первого по третий элементы ИЛИ, элементы И, при этом группа информационных входов-выходов шинного формирователя является информационными входами-выходами группы блока приостанова, первый вход элемента И является входом обращения блока приостанова, первый и второй входы первого элемента ИЛИ являются входами ввода и вывода блока приостанова соответственно,, N входов выбора которого являются соответственно с первого по N-й входами узлов формирования сигналов приостанова, группы входов-выходов приостанова которых являются выходами групп блока приостанова, выход Пуск шинного формирователя подключен к входу одновибрато- ра, выход которого подключен к входам Пуск узлов формирования с первого по N-й,выходы подтверждения выбора которых подключены к входам с первого по N-й второго элемента ИЛИ соответственно и являются одноименными выходами блока приостанова, выход второго элемента ИЛИ подключен к входу подтверждения выбора шинного формирователя, вход обращения которого подключен к выходу элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, первый вход которого соединен с входом Ввод шинного формирователя, вход останова которого подключен к выходу третьего элемента ИЛИ, с первого по N-й которого подключены к входам останова узлов формирования сигналов приостанова с первого по N-й соответственно, группа выходов сигналов управления режимами шинного формирователя подключена к одноименным входам группы узлов формирования сигналов приостанова с первого по N-й.

.f

| название | год | авторы | номер документа |

|---|---|---|---|

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ДИАГНОСТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ | 1994 |

|

RU2097827C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМИ ОБЪЕКТАМИ | 1993 |

|

RU2018944C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1725223A1 |

| Устройство для связи процессоров | 1984 |

|

SU1193682A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1534509A2 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Электронная вычислительная машина с прямым доступом в память | 1987 |

|

SU1529240A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения цифровых вычислительных машин, например, при отладке многомашинной системы. Целью изобретения является расширение функциональных возможностей устройства за счет реализации доступа по всему адресному пространству ведомых ЦВМ. В устройство, содержащее блок 9 согласования, блок 8 приостанова, дополнительно введены регистр 4, дешифратор 5, селектор 6 адреса и формирователь 7 управляющих сигналов. 1 з.п. ф-лы, 11 ил.

фцг. З

-

/5

П

IZL

15 с Wt

/7

75

/j.;

J5.J

.6

75

SO

;

I

«3

Фие.9

f Начало

-.

Выдать на шину сигналов приостанови /V сигнал сброса, останова 70

Загрузить РОН соаер имб(м flmSedeHHb/) ля них ячеек. ОЗУвО

ТОО

Загрузить слово состоятя про- цессора содержимым отведенной длл него ячейки ОЗУ 80

Перейти на Оыполмение программы с адреса храмяще- еося в omSede HHou для счетчика команд ячейке ОЗУ 80

коней

Фие. Ю

с начало 1

L

Ов I

маать нов номерл atioHOu ЦВМ

Установить oemui ПЛП ttiSpaMHOu ffooMou nSMt и naAyvum nodmtepM ttut

Произвести обмен (зопис /чте - ние) е пасс1гвнини устройств lOHu цлмг

CSpocumt ptjKUH и получить nodmSepMiem/t

С коней, 1

Редактор Н. Лазаренко

Составитель Б, Резван

Техред М.Ходанич Корректор М. Пожо

пачиАо

W нонеой tttOHOit йМ/

жтанооипл

Мронной вНОноИ ЦВН и

лмуммм пеМгр денае

режим ЩП wSpaHMOu 8едону ЦвН2 и получить nodnaefo KHUt

npoutSecini авмен (зааии/чте- Hue) с eSfOcmtfu cutf лрамя- щеи todepmuHOe РОН, слова foe/nmiftM, счетчика, мг«нд процессора

соросить резким ПЛП иао- лучить повтВертоетл

проиаести nucf процессора дибранноа Ведомой ЦВН1

С пеней J

| Устройство для сопряжения двух вычислитель-НыХ МАшиН | 1979 |

|

SU805296A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1201843, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| И N ВЕДОМЫХ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН | |||

Авторы

Даты

1989-12-23—Публикация

1988-03-30—Подача