VI

СО v| v|

СА СлЭ

Ю

Изобретение относится к импульсной технике и может быть использовано в системах дискретной передачи звуковых, телеметрических и других электрических сигналов.

По основному звт.св,№ 1501269 известно устройство для кодирования электрическихсигналов,содержащее аналого-цифровой преобразователь (АЦП), первый и второй регистры, аналоговое запоминающее устройство, первый вход которого является входной шиной, последовательно соединенные тактовый генератор и блок управления, первый выход которого подключен к первому входу генератора пилообразного напряжения и второму входу аналогового запоминающего устройства, последовательно соединенные первый элемент запрета и счетчик, второй и третий выходы блока управления подсоединены соответственно к второму входу счетчика и первым входам первого и второго регистров, а вторые входы первого и второго регистров соединены соответственно с выходами счетчика и АЦП. выходы первого и второго регистров являются первой и второй выходными шинами, а также измерительный дифференциальный усилитель, второй и третий элементы запрета, элемент задержки и элемент ИЛИ, входы которого подключены к соответствующим выходам АЦП, а выход - к первым входам первого, второго и третьего элементов запрета, второй вход первого элемента запрета соединен с выходом элемента задержки вход которого объединен с вторым входом второго элемента запрета и подключен к четвертому выходу блока управления, пятый выход которого подключен к второму входу третьего элемента запрета, выход которого подключен к второму входу генератора пилообразного напряжения, выход которого подключен к первому входу измерительного дифференциального усилителя,второй вход которого подключен к выходу аналогового запоминающего устройства, а выход - к первому входу АЦП, второй вход которого подключен к выходу второго элемента запрета.

В данном устройстве на определение кода преобразуемого электрического сигнала влияет его задержка в измерительном дифференциальном усилителе, вызванная инерционностью последнего. Эта задержка является постоянной и, следовательно, может быть определена и учтена известным способом. Для этого необходимо осуществить либо запуск пилы генератора пилообразного напряжения за несколько тактовых импульсов до начала обработки входного

сигнала в АЦП тл счетчика, либо запуск счетчика на несколько тактовых импульсов позже запуска генератора пилообразного напряжения, АЗУ и АЦП.

у Кроме того, при работе устройства перепад сигналов на входах измерительного дифференциального усилителя при значительных амплитудах преобразуемого сигнала может достигать достаточно больших

величин, при которых операционный усилитель в измерительном дифференциальном усилителе, на который поступает через повторители напряжения преобразуемый сигнал и сигнал с генератора пилообразного

напряжения, входить в режим насыщения, обусловленный накоплением неосновных носителей в р-п переходах транзисторов. Время выхода из режима насыщения оказывается в прямой зависимости от величин

напряжения на втором входе измерительного дифференциального усилителя.

Эта задержка является непостоянной и зависит от количества накопившихся неосновных носителей Наличие переменной задержки, не учтенной в рассматриваемом устройстве, снижает точность кодирования электрических сигналов.

Цель изобретения - повышение точности аналого-цифрового преобразования за

счет исключения задержки сигнала в измерительном дифференциальном усилителе, зависящей от величины преобразуемого напряжения.

Поставленная цель достигается тем, что

в устройство для кодирования электрических сигналов по авт.ев № 1501269 введены дополнительно последовательно соединенные датчик порога, компаратор, триггер и коммутатор, второй вход которого объединен с вторым входом компаратора и подключен к второму выходу измерительного дифференциального усилителя, третий и четвертый входы которого подключены к первому и второму выходам коммутатора

соответственно, а второй вход триггера подключен к первому выходу блока управления.

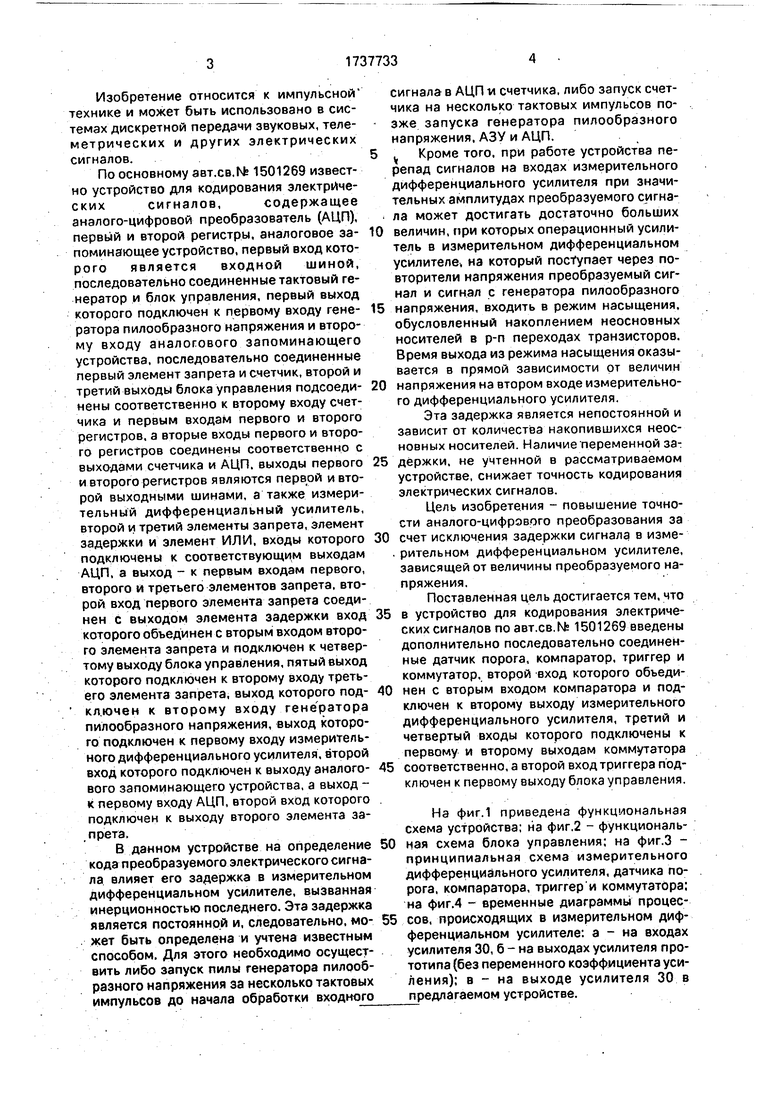

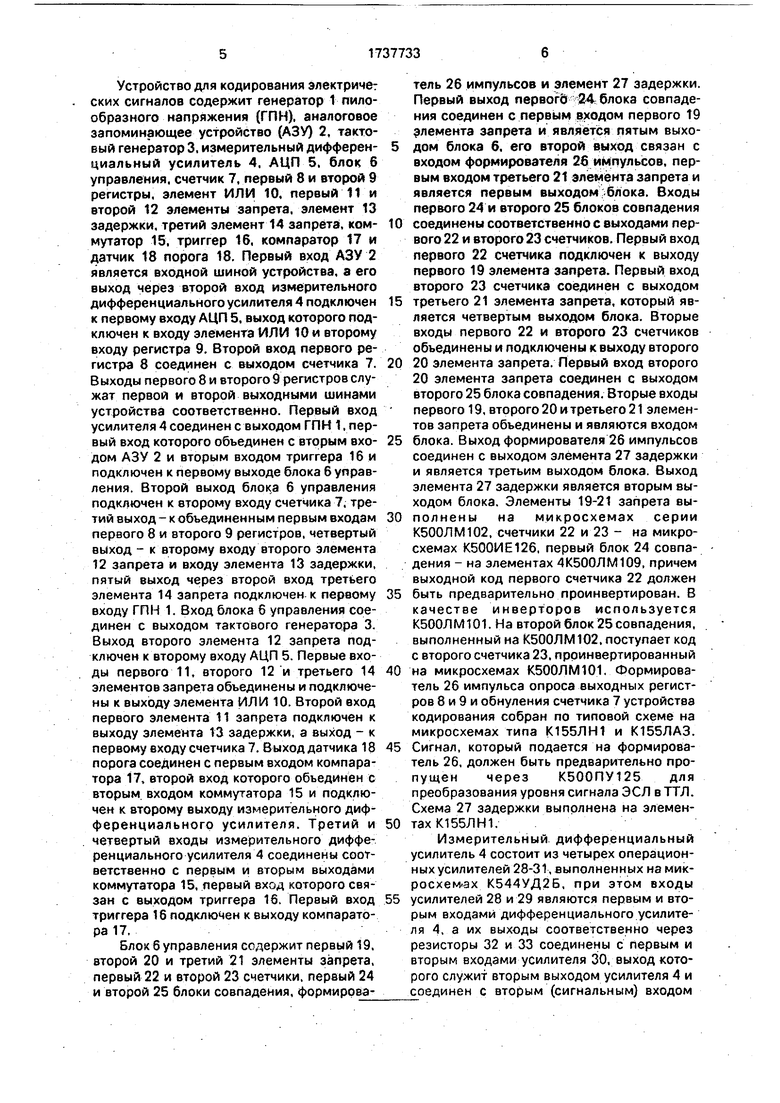

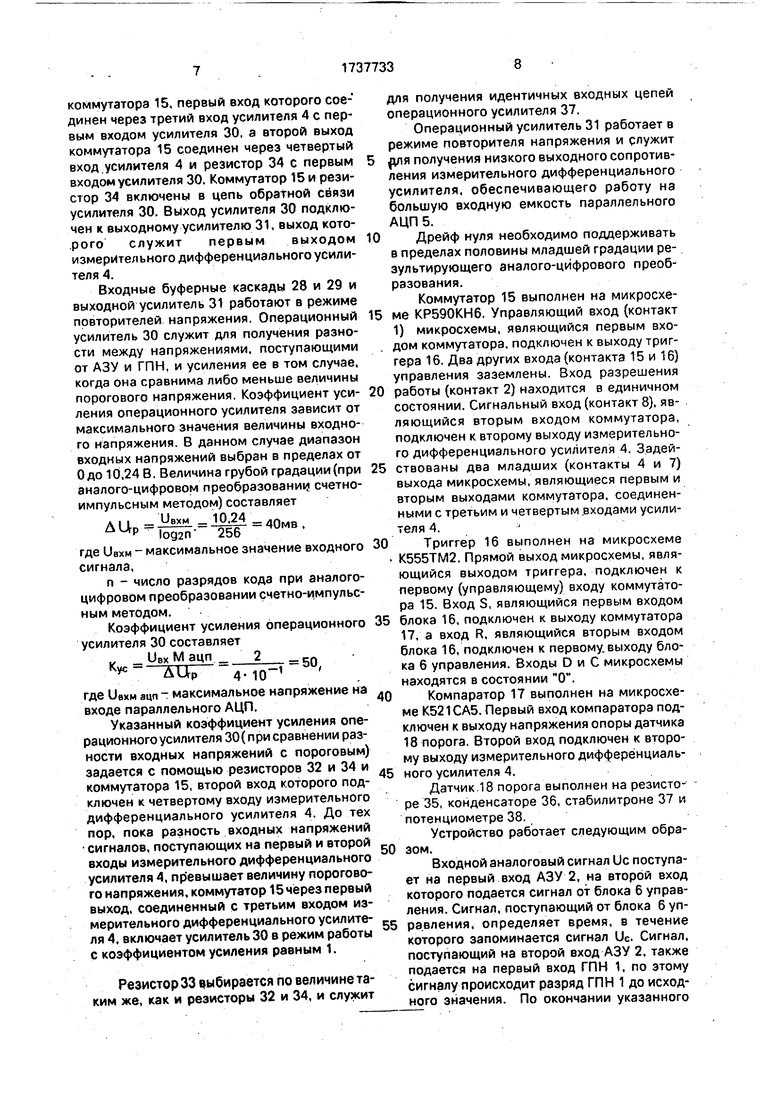

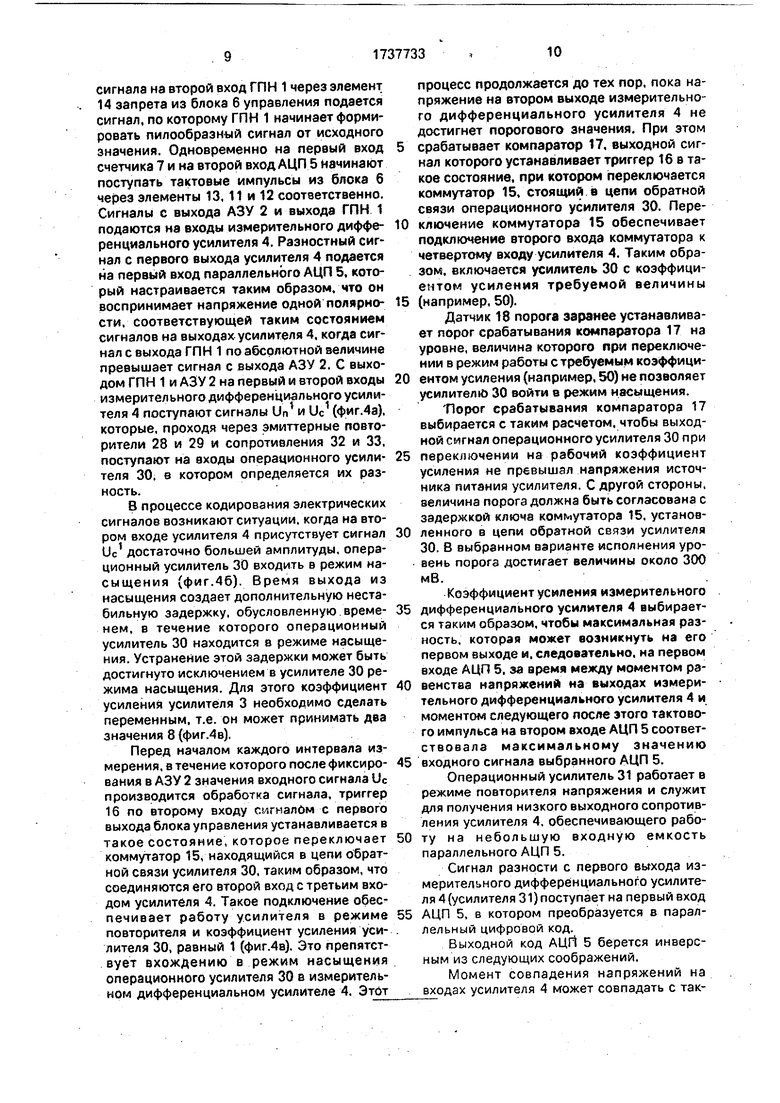

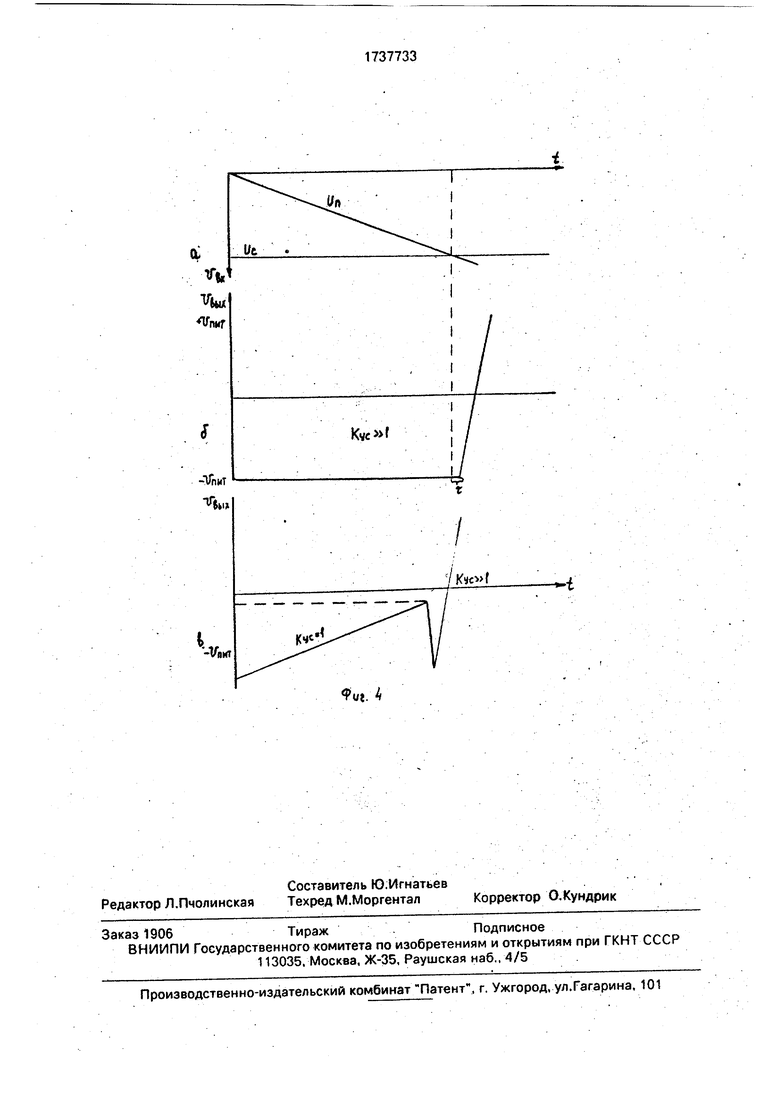

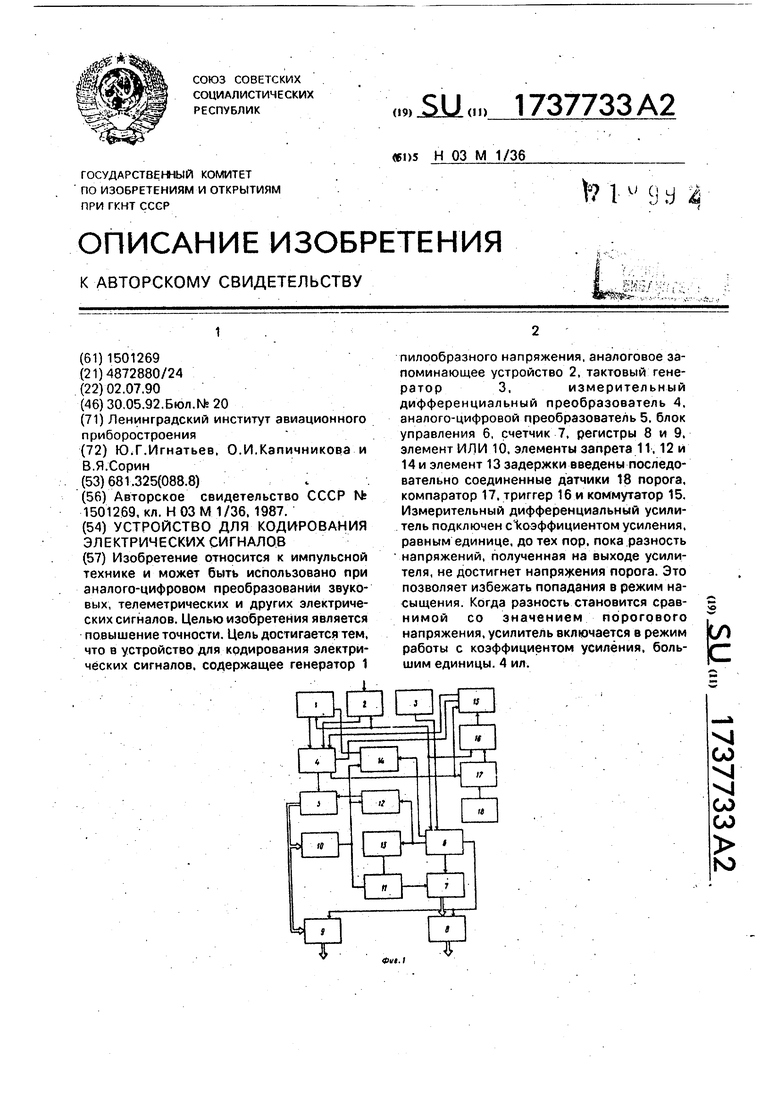

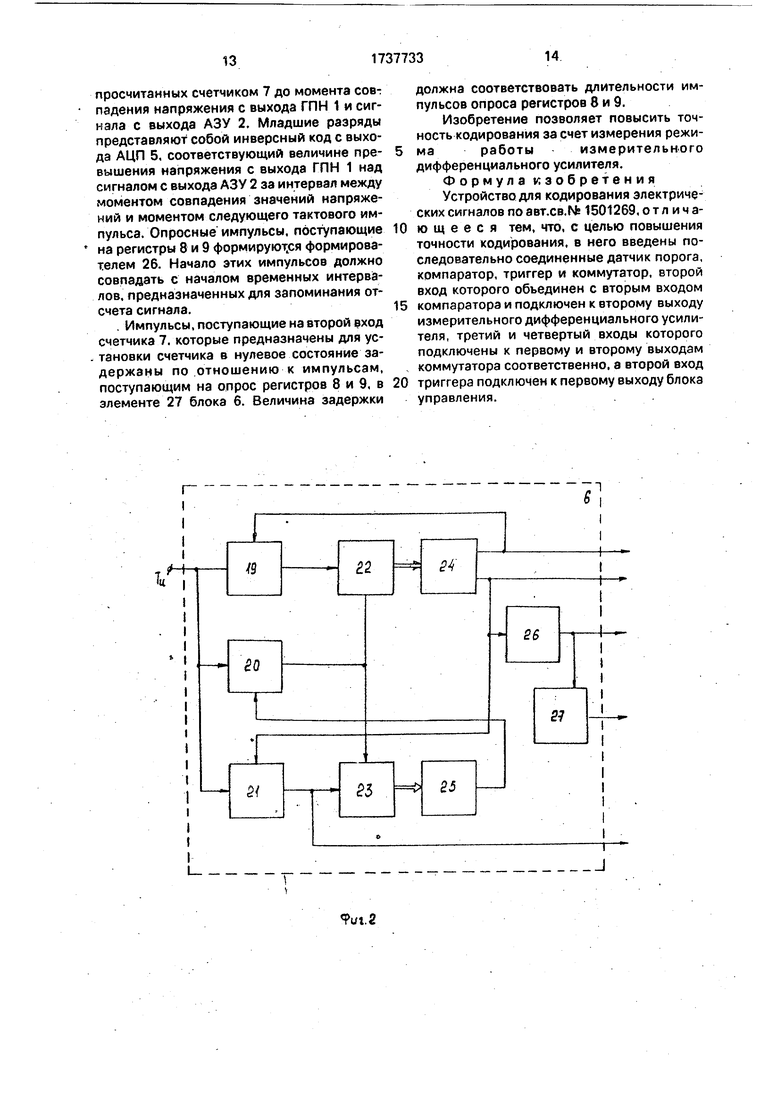

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема блока управления; на фиг.З - принципиальная схема измерительного дифференциального усилителя, датчика порога, компаратора, триггер и коммутатора; на фиг.4 - временные диаграммы процессов, происходящих в измерительном дифференциальном усилителе: а - на входах усилителя 30, б - на выходах усилителя прототипа (без переменного коэффициента усиления); в - на выходе усилителя 30 в предлагаемом устройстве.

Устройство для кодирования электриче ских сигналов содержит генератор 1 пилообразного напряжения (ГПН), аналоговое запоминающее устройство (АЗУ) 2, тактовый генератор 3, измерительный дифференциальный усилитель 4. АЦП 5. блок 6 управления, счетчик 7, первый 8 и второй 9 регистры, элемент ИЛИ 10, первый 11 и второй 12 элементы запрета, элемент 13 задержки, третий элемент 14 запрета, коммутатор 15. триггер 16, компаратор 17 и датчик 18 порога 18. Первый вход АЗУ 2 является входной шиной устройства, а его выход через второй вход измерительного дифференциального усилителя 4 подключен к первому входу АЦП 5, выход которого подключен к входу элемента ИЛИ 10 и второму входу регистра 9. Второй вход первого регистра 8 соединен с выходом счетчика 7. Выходы первого 8 и второго 9 регистров служат первой и второй выходными шинами устройства соответственно. Первый вход усилителя 4 соединен с выходом ГПН 1, первый вход которого объединен с вторым входом АЗУ 2 и вторым входом триггера 16 и подключен к первому выходе блока 6 управления. Второй выход блока 6 управления подключен к второму входу счетчика 7. третий выход - к объединенным первым входам первого 8 и второго 9 регистров, четвертый выход - к второму входу второго элемента 12 запрета и входу элемента 13 задержки, пятый выход через второй вход третьего элемента 14 запрета подключен к первому входу ГПН 1. Вход блока 6 управления соединен с выходом тактового генератора 3. Выход второго элемента 12 запрета подключен к второму входу АЦП 5. Первые входы первого 11, второго 12 и третьего 14 элементов запрета объединены и подключены к выходу элемента ИЛИ 10. Второй вход первого элемента 11 запрета подключен к выходу элемента 13 задержки, а выход - к первому входу счетчика 7. Выход датчика 18 порога соединен с первым входом компаратора 17, второй вход которого объединен с вторым входом коммутатора 15 и подключен к второму выходу измерительного дифференциального усилителя. Третий и четвертый входы измерительного дифференциального усилителя 4 соединены соответственно с первым и вторым выходами коммутатора 15, первый вход которого связан с выходом триггера 16. Первый вход триггера 16 подключен к выходу компаратора 17.

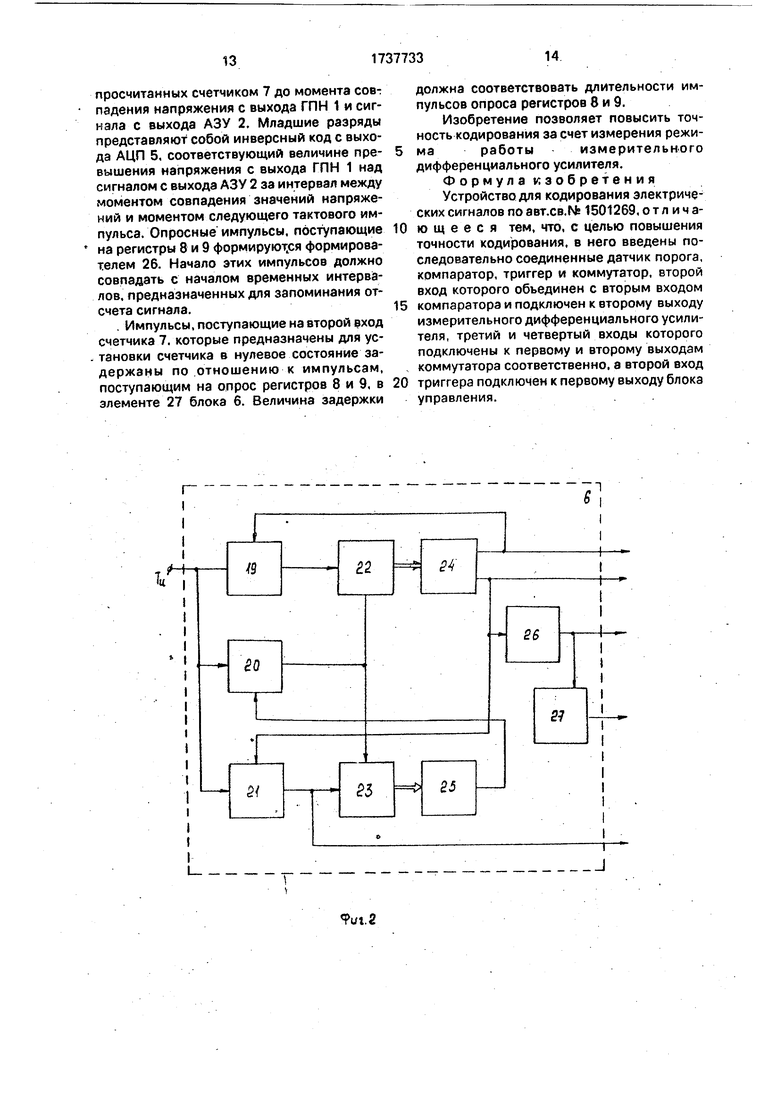

Блок 6 управления содержит первый 19, второй 20 и третий 21 элементы запрета, первый 22 и второй 23 счетчики, первый 24 и второй 25 блоки совпадения, формирователь 26 импульсов и элемент 27 задержки. Первый выход первого 24 блока совпадения соединен с первым входом первого 19 элемента запрета и является пятым выхо- 5 дом блока 6. его второй выход связан с входом формирователя 26 импульсов, первым входом третьего 21 элемента запрета и является первым выходом .блока. Входы первого 24 и второго 25 блоков совпадения

0 соединены соответственно с выходами первого 22 и второго 23 счетчиков. Первый вход первого 22 счетчика подключен к выходу первого 19 элемента запрета. Первый вход второго 23 счетчика соединен с выходом

5 третьего 21 элемента запрета, который является четвертым выходом блока. Вторые входы первого 22 и второго 23 счетчиков объединены и подключены к выходу второго

0 20 элемента запрета. Первый вход второго 20 элемента запрета соединен с выходом второго 25 блока совпадения. Вторые входы первого 19, второго 20 и третьего 21 элементов запрета объединены и являются входом

5 блока. Выход формирователя 26 импульсов соединен с выходом элемента 27 задержки и является третьим выходом блока. Выход элемента 27 задержки является вторым выходом блока. Элементы 19-21 запрета еы0 полнены на микросхемах серии К500ЛМ102, счетчики 22 и 23 - на микросхемах К500ИЕ126, первый блок 24 совпадения - на элементах 4К500ЛМ109, причем выходной код первого счетчика 22 должен

5 быть предварительно проинвертирован. В качестве инверторов используется К500ЛМ101. На второй блок 25 совпадения, выполненный на К500ЛМ102, поступает код с второго счетчика 23, проинвертированный

0 на микросхемах К500ЛМ101. Формирователь 26 импульса опроса выходных регистров 8 и 9 и обнуления счетчика 7 устройства кодирования собран по типовой схеме на микросхемах типа К155ЛН1 и К155ЛАЗ.

5 Сигнал, который подается на формирователь 26, должен быть предварительно пропущен через К500ПУ125 для преобразования уровня сигнала ЭСЛ в ТТЛ. Схема 27 задержки выполнена на элемен0 тахК155ЛН1.

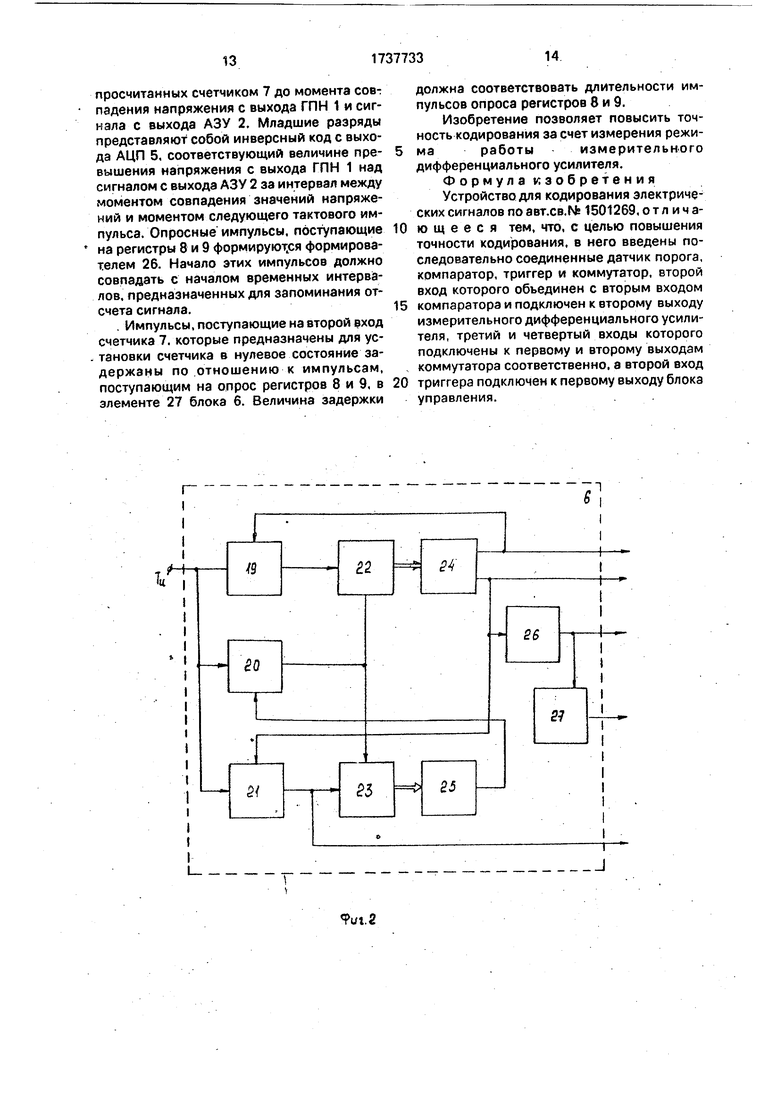

Измерительный дифференциальный усилитель 4 состоит из четырех операционных усилителей 28-31, выполненных на мик- росхем-эх К544УД2Б, при этом входы

5 усилителей 28 и 29 являются первым и вторым входами дифференциального усилителя 4. а их выходы соответственно через резисторы 32 и 33 соединены с первым и вторым входами усилителя 30, выход которого служит вторым выходом усилителя 4 и соединен с вторым (сигнальным) входом

коммутатора 15, первый вход которого соединен через третий вход усилителя 4 с первым входом усилителя 30, а второй выход коммутатора 15 соединен через четвертый вход усилителя 4 и резистор 34 с первым входом усилителя 30. Коммутатор 15 и резистор 34 включены в цепь обратной связи усилителя 30. Выход усилителя 30 подключен к выходному усилителю 31, выход которого служит первым выходом измерительного дифференциального усилителя 4.

Входные буферные каскады 28 и 29 и выходной усилитель 31 работают в режиме повторителей напряжения. Операционный усилитель 30 служит для получения разности между напряжениями, поступающими от АЗУ и ГПН, и усиления ее в том случае, когда она сравнима либо меньше величины порогового напряжения. Коэффициент усиления операционного усилителя зависит от максимального значения величины входного напряжения. В данном случае диапазон входных напряжений выбран в пределах от О до 10,24 В. Величина грубой градации (при аналого-цифровом преобразовании, счетно- импульсным методом) составляет

AIL- UBXM - 10.24 A Urp

40мв

1од2П 256 где UBXM - максимальное значение входного сигнала,

л - число разрядов кода при аналого- цифровом преобразовании счетно-импульсным методом.

Коэффициент усиления операционного усилителя 30 составляет

UBX М ацп 2

диР

Кус -

1-1

50,

4- 10

где UBXM ацп максимальное напряжение на входе параллельного АЦП.

Указанный коэффициент усиления операционного усилителя 30 (при сравнении разности входных напряжений с пороговым) задается с помощью резисторов 32 и 34 и коммутатора 15, второй вход которого подключен к четвертому входу измерительного дифференциального усилителя 4. До тех пор, пока разность входных напряжений сигналов, поступающих на первый и второй входы измерительного дифференциального усилителя 4, превышает величину порогового напряжения, коммутатор 15черезпервый выход, соединенный с третьим входом измерительного дифференциального усилителя 4, включает усилитель 30 в режим работы с коэффициентом усиления равным 1.

Резистор 33 выбирается по величине таким же, как и резисторы 32 и 34, и служит

для получения идентичных входных цепей операционного усилителя 37.

Операционный усилитель 31 работает в режиме повторителя напряжения и служит

рля получения низкого выходного сопротивления измерительного дифференциального усилителя, обеспечивающего работу на большую входную емкость параллельного АЦП 5.

0 Дрейф нуля необходимо поддерживать в пределах половины младшей градации результирующего аналого-цифрового преобразования.

Коммутатор 15 выполнен на микросхе5 ме КР590КН6. Управляющий вход (контакт 1) микросхемы, являющийся первым входом коммутатора, подключен к выходу триггера 16. Два других входа (контакта 15 и 16) управления заземлены. Вход разрешения

0 работы (контакт 2) находится в единичном состоянии. Сигнальный вход (контакт 8), являющийся вторым входом коммутатора, подключен к второму выходу измерительного дифференциального усилителя 4. Задей5 ствованы два младших (контакты 4 и 7) выхода микросхемы, являющиеся первым и вторым выходами коммутатора, соединенными с третьим и четвертым входами усилителя 4.

0 Триггер 16 выполнен на микросхеме К555ТМ2. Прямой выход микросхемы, являющийся выходом триггера, подключен к первому (управляющему) входу коммутатора 15. Вход S, являющийся первым входом

5 блока 16, подключен к выходу коммутатора 17, а вход R, являющийся вторым входом блока 16, подключен к первому, выходу блока 6 управления. Входы D и С микросхемы находятся в состоянии О.

0 Компаратор 17 выполнен на микросхеме К521СА5. Первый вход компаратора подключен к выходу напряжения опоры датчика 18 порога. Второй вход подключен к второму выходу измерительного дифференциал ь5 ного усилителя 4,

Датчик 18 порога выполнен на резисторе 35, конденсаторе 36, стабилитроне 37 и потенциометре 38.

Устройство работает следующим обра0 зом.

Входной аналоговый сигнал Uc поступает на первый вход АЗУ 2, на второй вход которого подается сигнал от блока 6 управления. Сигнал, поступающий от блока 6 уп5 равления, определяет время, в течение которого запоминается сигнал Uc. Сигнал, поступающий на второй вход АЗУ 2, также подается на первый вход ГПН 1. по этому сигналу происходит разряд ГПН 1 до исходного значения. По окончании указанного

сигнала на второй вход ГПН 1 через элемент 14 запрета из блока б управления подается сигнал, по которому ГПН 1 начинает формировать пилообразной сигнал от исходного значения. Одновременно на первый вход счетчика 7 и на второй вход АЦП 5 Начинают поступать тактовые импульсы из блока 6 через элементы 13,11 и 12 соответственно. Сигналы с выхода АЗУ 2 и выхода ГПН 1 подаются на входы измерительного диффе- ренциального усилителя 4. Разностный сигнал с первого выхода усилителя 4 подается на первый вход параллельного АЦП 5, который настраивается таким образом, что он воспринимает напряжение одной полярно- сти, соответствующей таким состоянием сигналов на выходах усилителя 4, когда сигнал с выхода ГПН 1 по абсолютной величине превышает сигнал с выхода АЗУ 2. С выходом ГПН 1 и АЗУ 2 на первый и второй входы измерительного дифференциального усилителя 4 поступают сигналы Un и Uc1 (фиг.4а), которые, проходя через эмиттерные повторители 28 и 29 и сопротивления 32 и 33, поступают на входы операционного усили- теля 30. в котором определяется их разность.

8 процессе кодирования электрических сигналов возникают ситуации, когда на втором входе усилителя 4 присутствует сигнал Uc1 достаточно большей амплитуды, операционный усилитель 30 входить в режим насыщения (фиг.46). Время выхода из насыщения создает дополнительную нестабильную задержку, обусловленную време- нем, в течение которого операционный усилитель 30 находится в режиме насыщения. Устранение этой задержки может быть достигнуто исключением в усилителе 30 режима насыщения. Для этого коэффициент усиления усилителя 3 необходимо сделать переменным, т.е. он может принимать два значения 8 (фиг.4в).

Перед началом каждого интервала измерения, в течение которого после фиксиро- вания в АЗУ 2 значения входного сигнала Uc производится обработка сигнала, триггер 16 по второму входу сигналим с первого выхода блока управления устанавливается в такое состояние, которое переключает коммутатор 15, находящийся в цепи обратной связи усилителя 30, таким образом, что соединяются его второй вход с третьим входом усилителя 4. Такое подключение обеспечивает работу усилителя в режиме повторителя и коэффициент усиления уси- лителя 30, равный 1 (фиг.4в). Это препятствует вхождению в режим насыщения операционного усилителя 30 в измерительном дифференциальном усилителе 4. Этот

процесс продолжается до тех пор, пока напряжение на втором выходе измерительного дифференциального усилителя 4 не достигнет порогового значения. При этом срабатывает компаратор 17, выходной сигнал которого устанавливает триггер 16 в такое состояние, при котором переключается коммутатор 15, стоящий в цепи обратной связи операционного усилителя 30. Переключение коммутатора 15 обеспечивает подключение второго входа коммутатора к четвертому входу усилителя 4. Таким образом, включается усилитель 30 с коэффициентом усиления требуемой величины (например, 50).

Датчик 18 порога заранее устанавливает порог срабатывания компаратора 17 на уровне, величина которого при переключении в режим работы с требуемым коэффициентом усиления (например, 50) не позволяет усилителю 30 войти в режим насыщения.

Порог срабатывания компаратора 17 выбирается с таким расчетом, чтобы выходной сигнал операционного усилителя 30 при переключении на рабочий коэффициент усиления не превышал напряжения источника питания усилителя. С другой стороны, величина порога должна быть согласована с задержкой ключа коммутатора 15. установленного в цепи обратной связи усилителя 30. В выбранном варианте исполнения уровень порога достигает величины около 300 мВ.

Коэффициент усиления измерительного дифференциального усилителя 4 выбирается таким образом, чтобы максимальная разность, которая может возникнуть на его первом выходе и, следовательно, на первом входе АЦП 5, за время между моментом равенства напряжений на выходах измерительного дифференциального усилителя 4 и моментом следующего после этого тактового импульса на втором входе АЦП 5 соответ- ствовалз максимальному значению входного сигнала выбранного АЦП 5.

Операционный усилитель 31 работает в режиме повторителя напряжения и служит для получения низкого выходного сопротивления усилителя 4, обеспечивающего работу на небольшую входную емкость параллельного АЦП 5.

Сигнал разности с первого выхода измерительного дифференциального усилителя 4(усилителя 31)поступает на первый вход АЦП 5, в котором преобразуется в параллельный цифровой код.

Выходной код АЦГ1 5 берется инверсным из следующих соображений.

Момент совпадения напряжений на входах усилителя 4 может совпадать с таковым импульсом на втором входе АЦП 5 ли может возникнуть в любой момент времени между соседними тактовыми импульсами. Если совпадение напряжений на входах усилителя 4 произойдет одновременно с приходом тактового импульса, то младшие разряды выходного кода равны нулю. 8 этом случае выходной код устройства определяется количеством импульсов, просчитанных счетчиком 7 до момента совпадения напряжений на входах измерительного дифференциального усилителя 4. В этом случае появление кода, отличного от нуля, на выходе АЦП 5 возможно только с подачей следующего тактового импульса на второй тактовый вход АЦП 5 и при указанном согласовании коэффициента усиления измерительного дифференциального усилителя 4 с диапазоном входного напряжения АЦП 5 напряжение на выходе усилителя 4 изменяется на величину, соответствующую максимальному значению входного напряжения АЦП 5, что приводит к появлению единицы во всех разрядах кода АЦП 5. Но младшие разряды кода должны быть равны нулю. Следовательно, коды с выхода АЦП 5 необходимо брать с инверсией.

Код АЦП, характеризующий превышение сигнала ГПН 1 над входным сигналом Uc1 между моментом совпадения этих напряжений на выходах измерительного дифференциального усилителя 4 и первым тактовым импуьсом, фиксирующим это превышение в АЦП 5, соответствует значению, которое необходимо вычесть из максимального значения кода АЦП 5, а результат такой разности является инверсным кодом.

Тактовые импульсы, поступающие на счетный вход счетчика 7, должны быть задержаны по отношению к тактовым импуль- сам, поступающим на тактовый вход АЦП 5, на время, которое обеспечивает возможность непоступления тактового импульса, фиксирующего первое появление единиц на выходе АЦП 5, на вход счетчика, для чего служит элемент 13 задержки. Величина указанной задержки зависит от элементной ба- зы, применяемой для реализации предлагаемого устройства.

Рассмотрим работу блока 6 в комплекса с работой устройства.

Импульсы с выхода тактового генератора 3 поступают на вторые входы элементов 19-21 запрета. Пусть счетчики 22 и 23 обнулены. В этом случае сигнал с первого выхода блока 24 совпадения разрешает прохождение импульсов тактового генератора через элемент 19 на первый вход счетчика 22, а сигнал с второго-выхода блока 24. который является инверсным по отношению к сигналу, взятому с первого выхода, запрещает прохождение импульсов тактового генератора на первый вход счетника 23 через элемент 21. Код совпадения на блохе 25

выбирается в зависимости от точности измерения счетным методом, Например, при шестнадцатиразрядном аналого-цифровом преобразовании восемь старших разрядов кода можно определить счетным методом, а

0 восемь младших - с помощью восьмиразрядного параллельного АЦП. В указанном случае код совпадения на блоке 25 соответствует числу 256 в двоичном коде. В других вариантах построения устройства это число

5 может быть изменено. Код совпадения на блоке 24 выбирается из соотношения временных интервалов: интервала, необходимого для запоминания отсчета преобразуемого сигнала, и интервала, необ0 ходимого для измерения сигнала. При появлении на выходах счетчика 22 кода совпадения на первом выходе блока 24 и одновременно на 5 выходе блока появляется сигнал, запрещающий дальнейшее про5 хождение импульсов тактового генератора на первый вход счетчика 22. В то же время на втором выходе блока 24 появляется сигнал, разрешающий прохождение импульсов тактового генератора через элемент 21 на

0 первый вход счетчика 23. Одновременно им- пульсы с выхода элемента 21 блока 6 поступают на элемент 12 запрета и.через элемент 13 задержки на элемент 11 запрета. С выхода элемента 11 импульсы поступают на пер5 вый вход счетчика 7, а с выхода элемента 12

- на второй вход АЦП 5. На первые входы

элементов 11 и 12 поступает сигнал запрета.

При появлении хотя бы одной единицы по

отношению к инверсному коду - хотя бы

0 одного нуля) в выходном коде АЦП 5 на элементе ИЛИ 10 разрабатывается сигнал запрета. По этому сигналу прекращается подача импульсов тактового генератора на АЦП 5 и счетчик 7. Одновременно, этим же

5 сигналом, через элемент 14 прекращается заряд ГПН 1, что предотвращает перегрузку АЦП 5 по входу. При появлении на выходах счетчика 23 кода совпадения на выходе блока 25 появляется сигнал, разрешающий про0 хождение импульса тактового генератора через элемент 20 на вторые входы счетчиков 22 и 23. Этим импульсом счетчики, 22 и 23 сбрасываются в нулевое состояние Затем цикл работы блока управления повторя5 ется и т.д. На выходах блоков 24 и 25 вырабатываются сигналы, предназначенные для управления работой АЗУ 2 и ГПН 1. Таким образом, выходной код получается следующим путем. Старшие разряды кода представляют собой количество импульсов,

просчитанных счетчиком 7 до момента совпадения напряжения с выхода ГПН 1 и сигнала с выхода АЗУ 2. Младшие разряды представляют собой инверсный код с выхода АЦП 5, соответствующий величине пре- вышения напряжения с выхода ГПН 1 над сигналом с выхода АЗУ 2 за интервал между моментом совпадения значений напряжений и моментом следующего тактового импульса. Опросные импульсы, поступающие на регистры 8 и 9 формируются формирователем 26. Начало этих импульсов должно совпадать с началом временных интервалов, предназначенных для запоминания отсчета сигнала.

Импульсы, поступающие на второй вход счетчика 7. которые предназначены для установки счетчика в нулевое состояние задержаны по отношению к импульсам, поступающим на опрос регистров 8 и 9, в элементе 27 блока б. Величина задержки

должна соответствовать длительности импульсов опроса регистров 8 и 9.

Изобретение позволяет повысить точность кодирования за счет измерения режимаработыизмерительногодифференциального усилителя. Формула изобретения Устройство для кодирования электрических сигналов по авт.св.Мг 1501269, отличающееся тем, что, с целью повышения точности кодирования, в него введены последовательно соединенные датчик порога, компаратор, триггер и коммутатор, второй вход которого объединен с вторым входом компаратора и подключен к второму выходу измерительного дифференциального усилителя, третий и четвертый входы которого подключены к первому и второму выходам коммутатора соответственно, а второй вход триггера подключен к первому выходу блока управления.

6

У

I I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования электрических сигналов | 1987 |

|

SU1501269A1 |

| Спектрометр | 1991 |

|

SU1800291A1 |

| Третьоктавный спектральный анализатор | 1985 |

|

SU1308927A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКОЙ ЕМКОСТИ ХИМИЧЕСКИХ ИСТОЧНИКОВ ТОКА | 2007 |

|

RU2354985C2 |

| Устройство контроля аналого-цифровых преобразователей | 1990 |

|

SU1757100A2 |

| Измерительный преобразователь для тензорезисторных весоизмерительных устройств | 1990 |

|

SU1830463A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1983 |

|

SU1109848A1 |

| Тензоизмеритель | 1990 |

|

SU1798635A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Система экстремального регулирования | 1985 |

|

SU1352452A1 |

Изобретение относится к импульсной технике и может быть использовано при аналого-цифровом преобразовании звуковых, телеметрических и других электрических сигналов. Целью изобретения является повышение точности. Цель достигается тем, что в устройство для кодирования электрических сигналов, содержащее генератор 1 пилообразного напряжения, аналоговое запоминающее устройство 2, тактовый генератор3,измерительный дифференциальный преобразователь 4, аналого-цифровой преобразователь 5, блок управления 6, счетчик 7, регистры 8 и 9. элемент ИЛИ 10, элементы запрета 11,12 и 14 и элемент 13 задержки введены последовательно соединенные датчики 18 порога, компаратор 17, триггер 16 и коммутатор 15. Измерительный дифференциальный усилитель подключен с Коэффициентом усиления, равным единице, до тех пор, пока разность напряжений, полученная на выходе усилителя, не достигнет напряжения порога. Это позволяет избежать попадания в режим насыщения. Когда разность становится сравнимой со значением порогового напряжения, усилитель включается в режим работы с коэффициентом усиления, большим единицы. 4 ил.

-VB

акт

Л

9«. 4

| Устройство для кодирования электрических сигналов | 1987 |

|

SU1501269A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-05-30—Публикация

1990-07-02—Подача