к второму входу блока управления реверсом, при этом выход первого элемента ИЛИ подключен к второму входу блока памяти, выход которого подключен к второму входу блока формирования признака смены шкалы и первому входу блока запрета записи, выход которого подключен к третьему входу блока памяти, причем второй и третий выходы блока реверсивного счета являются соответственно вторым :и первым выходами блока определения кода шкалы, а вход первого элемента ИЛИ, второй вход блока запрета счетных импульсов, второй вход блока запрета обнуления памяти, второй, третий и четвертый входы блока формирования импульса запрета, второй вход блока запрета записи являются соответственно информадаонным входом, входом счетных импульсов, знаковым входом, входом установки триггера, входом обнуления памяти и входом синхронизации памяти блока определения кода шкалы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

| Устройство для цифрового компандирования звуковых сигналов | 1981 |

|

SU1030975A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1984 |

|

SU1197085A1 |

| Устройство для кодирования звуковых сигналов | 1980 |

|

SU944102A2 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1987 |

|

SU1450113A2 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

| Устройство для вычисления функции линеаризации | 1980 |

|

SU905831A1 |

| Следящее цифровое измерительное стробоскопическое устройство | 1978 |

|

SU771554A1 |

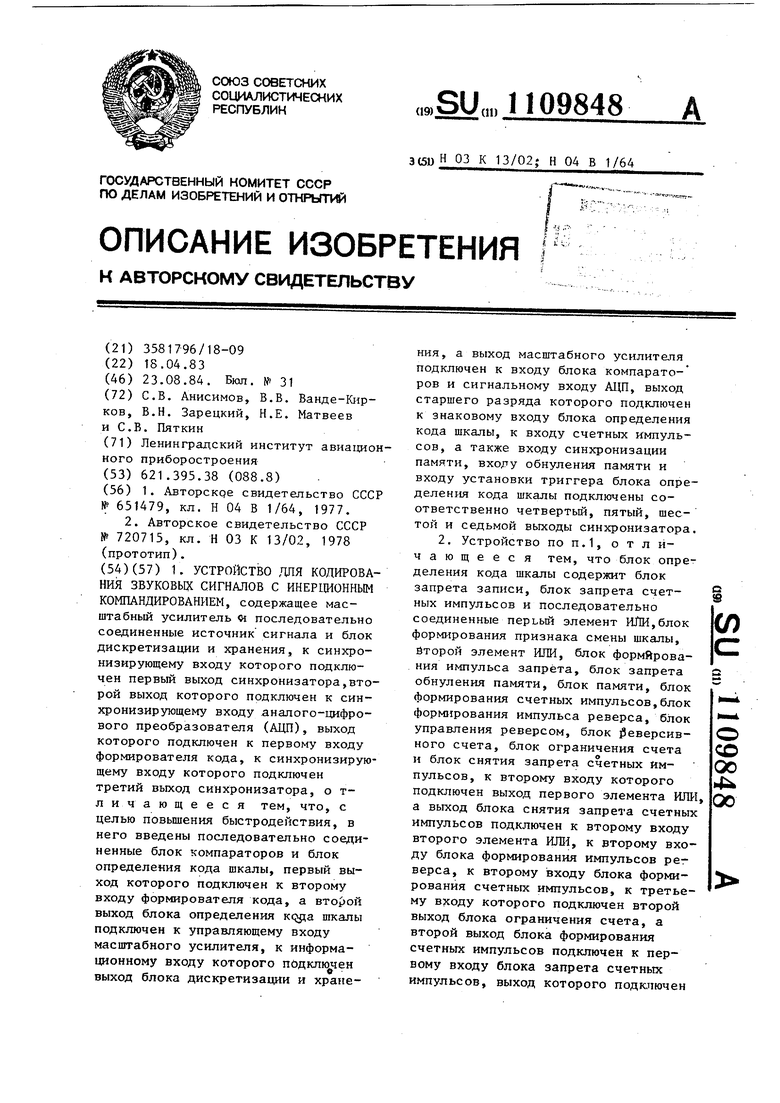

1. УСТРОЙСТВО ,ТЛЯ КОДИРОВАНИЯ ЗВУКОВЫХ СИГНАЛОВ С ИНЕРЦИОННЬИ КОМПАНДИРОВАНИЕМ, содержащее масштабный усилитель d последовательно соединенные источник сигнала и блок дискретизации и хранения, к синхронизирующему входу которого подключен первый выход синхронизатора,второй выход которого подключен к синхронизирующему входу аналого-цифрового преобразователя (АЦП), выход которого подключен к первому входу формирователя кода, к синхронизирующему входу которого подключен третий выход синхронизатора, о тличающееся тем, что, с целью повьшения быстродействия, в него введены последовательно соединенные блок компараторов и блок определения кода шкалы, первый выход которого подключен к второму входу формирователя кода, а второй выход блока определения KQfta шкалы подключен к управляющему входу масштабного усилителя, к информационному входу которого подкпкмен выход блока дискретизации и хранеf, ti,:/ ния, а выход масштабного усилителя подключен к входу блока компараторов и сигнальному входу А1Щ, выход старшего разряда которого подключен к знаковому входу блока определения кода шкалы, к входу счетных импульсов, а также входу синхронизации памяти, входу обнуления памяти и входу установки триггера блока определения кода шкалы подключены соответственно четвертый, пятый, шестой и седьмой выходы синхронизатора. 2. Устройство по П.1, отличающееся тем, что блок определения кода шкалы содержит блок i запрета записи, блок запрета счетных импульсов и последовательно СЛ соединенные перьый элемент ЯЛИ,блок формирования признака смены шкалы, йторой элемент ИЛИ, блок формирования импульса запрета, блок запрета обнуления памяти, блок памяти, блок формирования счетных импульсов,блок формирования импульса реверса, блок о :о управления реверсом, блок реверсивного счета, блок ограничения счета 00 4:; и блок снятия запрета счетных импульсов, к второму входу которого подключен выход первого элемента ИЛИ, 00 а выход блока снятия запрета счетных импульсов подключен к второму входу второго элемента ИЛИ, к второму входу блока формирования импульсов per верса, к второму входу блока формирования счетных импульсов, к третьему входу которого подключен второй выход блока ограничения счета, а второй выход блока формирования счетных импульсов подключен к первому входу блока запрета счетных импульсов, выход которого подключен

Изобретение относится к технике передачи информации и предназначено для использования в системах дискретной обработки высококачественных звуковых сигналов.

Известно устройство для кодирования звуковых сигналов с компандированием, содержащее последовательно соединенные усилитель, коммутатор, аналого-цифровой преобразователь (АЦП), выходной регистр, а также решающий блок и синхронизатор Cl 3Однако известное устройство обладает низким быстродействием за счет того,что кодирование сигнала происходит в два цикла.

Наиболее близким к предлагаемому техническим решением является устройство для кодирования звуковых сигналов, содержащее масштабный усилитель и последовательно соединенные источник сигнала и блок дискретизации и хранения, к синхронизирующему входу которого подключен первый выход синхронизатора, второй выход которого подключен к синхронизирующему входу АЦП, выход которого подключен к первому входу формирователя кода, к синхронизирующему входу которого подключен третий выход синхронизатора, а также блок запрета сдвига, блок преобразования позиционного кода, последовательно соединенные регистр кода, решающий блок, блок запрета младшего разряда и универсальный регистр, и последовательно соединенные усилитель, блок формирования импульсов сдвига и вентиль, к второму ВХОДУ которого подключен первый выход блока запрета сдвига, второй выход которого подключен к второму входу блока запре5 та младшего разряда и через блок преобразования позиционного кода к второму входу формирователя кода, к третьему входу которого подключен первый выход усилителя, к входу

0 которого подключен выход блока дискретизации и хранения, а второй выход усилителя подключен к первому входу масштабного усилителя и первому входу блока коммутаторов,

S выход которого подключен к входу АЦП, при этом выход вентиля подключен к второму входу универсального регистра, выход которого подключен к второму входу масштабного

0 усилителя, выход которого подключен к второму входу блока коммутаторов, к синхронизирующему входу которого подключен четвертьй выход синхронизатора, пятый, шестой, седьмой и

5 восьмой выходы которого подключены соответственно к синхронизирующим входам универсального регистра, блока запрета сдвига, решающего блока регистра кода, к входу кото0 рого подключен выход АЦП CZ.

Недостатком известного устройства является низкое быстродействие, связанное с необходимостью обработки каящого отсчета сигнала в двух циклах и значительной задержкой распространения сигнала в устройстве. Цель изобретения - псвьпиение быстродействия . Дня достижения поставленной цели в устройство для кодирования звуковых сигналов с инерционным компандированием, содержащее масштабньй усилитель и последовательно соединенные источник сигнала и блок дискретизации и хранения, к синхронизирующему входу которого подключен первый выход синхронизатора, второй выход которого подключен к синхронизирующему входу АЦП, выход которого подключен к пер вому входу формирователя кода, к синхронизирующему входу которого подключен третий выход синхронизатора, введены последовательно соединенные блок компараторов и блок определения кода шкалы, первьй выход которого подключен к второму входу формирователя кода, а второй выход блока определения кода шкалы подключен к управляющему входу масштабного усилителя, к информационному входу которого подключен выход блока дискретизации и хранени а выход масштабного усилителя подключен к входу блока компараторов и сигнальному входу АЦП, выход старше го разряда которого подключен к знаковому входу блока определения кода шкалы, к входу счетных импульсов, а также входу синхронизации па мяти, входу обнуления памяти и входу установки триггера блока определения кода шкалы подключены соответственно четвертый, пятьй, шестой и седьмой выходы синхронизатора. .Блок определения кода шкалы содержит блок запрета записи, блок запрета счетных импульсов и последовательно соединенные первый элемент ИЛИ, блок формирования признак смены шкалы, второй элемент ИЛИ,бло формирования импульса запрета, блок запрета обнулеМя памяти, блок памяти, блок формирования счетных им пульсов, блок формирования импульса реверса, блок управления реверсом, блок реверсивного счета, блок огра ничения счета и блок снятия запрета счетных импульсов, к второму входу которого подключен выход первого элемента ИЛИ, а выход блoйk снятия запрета счетных импульсов подключе к второму входу второго элемента И к второму входу блока фор мир импульсов ревбрса к второму входу лока формироват.ил счетных импульсов, третьему входу которого подключен торой выход блока ограничения счеа, а второй выход блока формирования счетных импульсов подключен к ервому входу блока запрета счетных мпульсов, выход которого подключен второму входу блока управления реерсом, при этом выход первого элеента ИЛИ подключен к второму входу блока памяти, выход которого подключен к второму входу блока формирования признака смены шкалы и первому входу блока запрета записи, выход которого подключен к третьему входу блока памяти, причем второй и третий вьпсоды блока реверсивного счета являются соответственно вторым и первым выходами блока определений кода шкалы, а вход первого элемента ИЛИ, второй вход блока запрета счетных импульсов, второй вход блока запрета обнуления памяти, второй, третий и четвертый входы блока формирования импульса запрета, второй вход блока запрета записи являются соответственно информационным входом, входом счетных импульсов, знаковым входом, входом установки триггера, входом обнуления памяти и входом синхронизации памяти блока определения кода шкалы. На фиг.1 представлена структурная схема устройства для кодирования звуковых сигналов с инерционным компандированием; на фиг.2 - струк урная электрическая схема б/ьока определения кода шкалы. Устройство для кодирования звуковых сигналов с инерционным компандированием содержит источник 1 сигнала, блок 2 дискретиза щи и хранения, масштабный усилитель 3, АЦП 4, формирователь , блок 6 компараторов, блок 7 определения кода шкалы, синхронизатор 8. Блок 7 определения кода шкалы содержит первый элемент ИЛИ 9, блок 10 формирования признака смены шкалы, второй элемент ИЛИ 11, блок 12 формирования импульса запрета, блок 13 запрета обнуления памяти,блок 14 памяти, блок 15 формирования счетных импульсов, блок 16 формирования импульсов реверса, блок 17 зшравления реверсом, блок 18 реверсивного счета, блок 19 ограничения счета, блок 20 снятия запрета счетных импульсов. блок 22 за блок 21 запрета записи и рета счетных импульсов. Устройство работает следующим образом. Изменение коэффицие1Ла усиления масштабного усилителя 3 происходит только в двух случаях: если величин отсчета сигнала прёвьшаст диапазон квантования АЦП 4, то коэффициент передачи масштабного усилителя умен шается в два раза, если за интервал времени между двумя последовательны ми переходами сигнала через средний уровень не произошло подтверждения коэффициента передачи масштабного усилителя 3, установленного в преды дущий временной интервал, хотя бы один раз, то коэффициент передачи масштабного усилителя 3 увеличивается в два раза. Этот алгоритм работы реализован в блоке 7 определения кода шкалы. Звуковой аналоговый сигнал с выхода источника 1 сигнала поступает на вход блока 2 дискретизации и хранения, в котором при поступлении синхроимпульса от синхронизатора 8 происходит его дискретизация, а величина отсчета запоминается на врем полного преобразования в цифровой эквивалент. Время хранения равно 20,8 МКС. Далее постоянное напряжен отсчета сигнала через масштабный усилитель 3 подается на сигнальньй вход АЦП 4 и на вход блока 6 компараторов. В начальный момент времени коэффициент передачи масштабного ус лителя 3 может иметь любое разрешенное значение (1,2,4,8). При появлении на синхронизирующем входе АЦП 4 nespBoro тактового импульса с второго входа синхронизатора 8 АЦП 4 определяет значение старшего разряда кода, которое фиксируется с приходом второго тактового импульса в регистре последовательно уравновешивания этого блока. Значение ста шего разрям кодового слова характеризует полярность отсчета сигнала а момент его изменения - переходы сигнала через среднее значение. Информация с выхода старшего разряда АЦП 4 поступает на знаковый вход блока 7 определения кода шкапы. Через время задержки компараторов на выходе блока 6 компараторов появляется информация, соответствующая попаданию величины отсчета сигнала либо мезвду порогами срабатывания 8 компараторов, либо за диапазон квантования. При этом возможны три ситуации: величина отсчета меньше порогового напряжения на всех компараторах для одной полярности сигнала, величина отсчета находится между порогами, отсчет сигнала клиппируется. В первом случае на выходе блока 6компараторов устанавливается кодовая комбинация 00, во втором и в третьем - 11. Комбинация 00 говорит о том, что величина отсчета меньше четверти диапазона квантования АЦП 4 и ее следует увеличить. Комбинация 10 является разрешенной и указывает, что отсчет сигнала занимает большую часть диапазона квантования, т.е. АЦП 4 используется наилучшим образомi Комбинация 11 соответствует клиппированию сигнала, которое необходимо немедленно предотвратить, приоритетно уменьшая коэффициент передачи масштабного усилителя 3. Информация с блока 6 компараторов поступает на информационный вход блока 7 определения кода шкалы, где обрабатывается по указанному алгоритму, в результате чего на втором выходе блока 7 устанавливается такой сигнал, который, поступая на управляющий вход масштабного усилителя 3, устанавливает требуемый коэффициент передачи. После интервала времени, необходимого для окончания переходных процессов в масштабном усилителе 3, на синхронизирующий вход АЦП 4 с второго выхода синхронизатора 8 поступают еще десять тактовых импульсов, необходимых для завершения цикла поразрядного уравновешивания величины отсчета. Цифровой код с выхода АЦП 4 поступает на первый вход формирователя 5 кода, на втором входе которого установлен код масштаба отсчета с первого выхода блока 7определения кода шкалы. По импульсу, приходящему с третьего выхоа синхронизатора 8 на синхронизирующий вход формирователя 5 коа, информация с входа последнего ереписывается в регистр памяти форирователя 5 кода и поступает на ыход устройства. Блок 7 определения кода шкалы аботает следующим образом. Информация с блока 6 компаратоов через первый элемент ИЛИ 9,

объединяющий информации для положительных и отрицательных отсчетов сигнала, поступает одновременно на второй вход блока 14 памяти, на второй вход блока 20 снятия запрета счетных импульсов и на первьй вход блока 10 формирования признака смены шкалы. В случае клиппирования сигнала в квантователе АЦП 4 на выходе первого элемента ИЛИ 9 появляется кодовая комбинация 11, которая приводит к тому, что на выходе элемента совпадения ЗИ-НЕ в блоке 20 снятия запрета счетных импульсов появляется уровень логического нуля. Этот сигнал воздействует на блок 15 формирования счетных импульсов и на блок формирования импульса реверса таким образом, что на втором выходе блока формирования импульсов появляется уровень логической единицы, который открьшает блок 22 запрета счетных импульсов. На выходе блока 16 формирования импульса реверса устанавливается уровень логической единицы, который переключает блок 17 управления реверсом таким образом, что счетный импульс, поступая на вход вычитания реверсивного счетчика блока 18 реверсивного счета, уменьшает состояние счетчика на единицу. Код с второго выхода блока 18 реверсивного счета поступает на управляющий вход масштабного усилителя 3, коэффициент которого : еньшается вдвое. После окончания переходных процессо в масштабном усилителе АЦП 4 заканчивает уравновешивание измененного напряжения отсчета сигнала, а цифровой эквивалент поступает на первый вход формирователя 5 кода. При поступлении на синхронизирующий вхо формирователя кода тактового импульса с третьего выхода синхронизатора 8 код величины отсчета с первого входа формирователя 5 кода и код шкапы с его второго входа записывается в регистр памяти и далее поступают на выход всего устройства Если для следующего отсчета сигнала информация на выходе первого элемента ИЛИ 9 не изменилась, то аналогичная работа блока 7 определения кода шкалы продолжается до тех спор, пока на выходе первого элемента ИЛИ 9 не появится разрешенная комбинация 10

Статистические свойства сигнала таковы, что последний случай может

ггроисходить только в момент включения устройства. В режиме слежения оказьгеается достаточным одно переключение масштаба отсчета, так как крутизна изменения амплитуды звукоВого сигнала имеет конечную величину.

Пусть величина напряжения отсчета сигнала на выходе масштабного усилителя 3 стала такой, что попадает между порогами ртсчета выходного сигнала. В этом случае на выходе первого элемента ИЛИ 9 появляется кодовая комбинация ТО хотя бы один раз за время перехода сиг5нала через среднее значение. При этом информация с выхода первого элемента ИЛИ 9 поступает на второй вход блока 14 памяти, куда записывается с приходом импульса синзфо0низации памяти, поступающим на третий вход блока 14 памяти через открытый блок 21 запрета записи. Как только кодовая комбинация 10 появится на выходе блока 14 памяти,

5 блок 21 запрета записи запирается, предотвращая таким образом перезапись кода в блоке 14 памяти. При этом срабатывает схема совпадения в блоке 10 формирования признака

0 смены шкалы и на его выходе появляется уровень логического нуля, которьй подается на первый вход второго элемента ИЛИ 11. На выходе второго элемента ИЛИ 11 возникает отрица5тельньш импульс, воздействуюшрий на триггер в блоке 12 формирования импульса запрета 7-4, который, срабатывая, фиксирует факт появления разрешенной комбинации 10 и запре0щает обнуление блока 14 памяти с приходом импульса смены зн,ака, так как на первом входе блока 13 запрета обнуления памятен появляется уровень логического нуля. Одновре5менно на выходе блока 20 снятия запрета счетного импульса устанавливается уровень логической единицы, который поступает на второй вход блока 15 формирования счетного им50пульса, на втором выходе которого возникает уровень логического нуля. Этот уровень, поступая на первый вход блока 22 запрета счетных импульсов, запирает последний, вслед55ствие чего пришедший с четвертого выхода синхронизатора 8 счетный импульс на блок 17 управления реверсом остается в прежнем состоянии 9 независимо от состояния блока 17 управления реверсом, т.е. независимо от команды управления, которая поступает с выхода блока 16 формирования импульса реверса. Таким образом, на выходе блока 18 реверсивного счета информация не меняется, а коэффициент передачи масштабного усилителя 3 остается величиной постоянной. Напряжение отсчетов сигнала с выхода масштабного усилит ля 3 поступает на сигнальный вход АЦП 4, которьй производит их аналого-цифровое преобразование, а выходные коды с первого выхода АЦП 4 поступают на первый вход формирователя 5 кода, куда записьшаются по тактовым импульсам, поступающим на его синхронизирующий вход с третьего выхода синхронизатора 8 Если уровень входного сигнала уменьшится, то величина напряжения отсчетов сигнала может стать такой, что пороги срабатьгоания компараторов для любой полярности отсчета не достигаются. При этом на выходе первого элемента ИЛИ 9 ни разу за время между последовательными переходами сигнала через среднее значение не появится разрешенная кодова комбинация 10. Блок 10 формирования признака смены шкалы в этом случае ни разу не сработает, а блок 12 формирования импульса запрета ни разу не изменит своего состояния. Поэтому с приходом импульса смены знака отсчета с выхода старшего разряда АЦП 4 блок 14 памяти обнуляется через открытый блок 13 запрета обнуления памяти. После этого срабатывает блок 10 формирова ния признака смены шкалы, т.е. на его выходе появляется уровень логического нуля, который через второй элемент ИЛИ 1.1 фиксируется в блоке 12 формирования импульса запрета, запирая таким образом блок 13 запре обнуления памяти. Одновременно срабатывает блок 15 формирования счетного импульса, воздействуя на блок 16 формирования импульса реверса и на блок 22 запрета счетных импульсов. Блок 16 формирования импульса реверса вьщает на блок 17 управлени реверсом уровень логического нуля, под воздействием которого счетный импульс с выхода открытого блока 22 запрета счетных импульсов поступит на вход суммирования реверсив8него счетчика в блоке 18 реверсивного счета, выходной код которого увеличится на единицу, что приведет к соответствующему увеличению коэффициента передачи масштабного усилителя 3 в два раза. Коэ(Ьфищ1ент усиления напряжения отсчета сигнала до прихода следующего импульса изменения знака отсчета не изменяется. Однако с приходом отсчета с новым знаком на третий вход обнуления памяти блока 12 формирования импульса запрета поступает отрицательный импульс с шестого выхода синхронизатора 8, При этом RS-триггер обнуляется, чем обеспечивается подготовка блока 7 определения кода шкалы к анализу следующего .периода времени между последовательными переходами сигнала через средний уровень. Импульс обнуления памяти поступает на вход блока 12 формирования импульса запрета в каждый отсчет сигнала. Но триггер обнуляется только для отсчета с новым знаком. Это достигается тем, что требуемый импульс выделяется элементом совпадения 2И-НЕ, на другой вход которого поступает положительный импульс, формируемый вторым RS-триггером, который устанавливается в единицу импульсом смены знака, приходящим со знакового выхода АЦП 4, и направляется в ноль импульсом установки треггера, приходящим на третий выход блока 12 формирования импульса запрета с синхронизатора 8. Работа устройства в описанном режиме продолжается до тех пор, пока за время анализа, т.е. за время между последовательными изменениями знака отсчетов, на выходе первого элемента не появится хотя бы один раз кодовая комбинация 10 или блок 18 реверсивного счета полностью не заполнится. Граничные значения чисел в реверсивном счетчике задаются блоком 19 ограничения счета. При появлении на выходе реверсивного счетчика комбинаций 00 и 11 блок 19 ограничения счета вьщает уровни логического нуля на блок 20 снятия запрета счетных импульсов и на блок 15 формирования счетных импульсов, запрещая таким образом дальнейшие изменения кода управления на выходе блока 7 определения кода шкалы, т.е. возникновение паразитнбй амплитудной модуляции сигнала. Если в следующий интервал времени между последовательными изменениями знака отсчета сигнала на выходе пер вого элемента ИЛИ 9 появляется хотя бы одна комбинация 10, то блок 10 формирования признака смены шкалы через второй элемент ИЛИ 11 и блок 12 формирования импульса запрета вьщает на блок 13 запрета обнуления памяти уровень логического нуля, запрещая тем самым обнуление блока 14 памяти с приходом импульса смены знака на блок 12 формирования импульса запрета и блок 13 запрета обнуления памяти. При этом блок 15 формирования счетных импуль сов запрещает прохождение счетного импульса через блок 22 запрета счет ных импульсов и состояние блока 18 реверсивного счета не изменяется (как и требует алгоритм преобразова ния) . Состояние блока 18 реверсивно го счёта будет оставаться неизменным до тех пор, пока не произойдет либо клиппирование сигнала, т.е. на выходе блока 6 компараторов не появится комбинация 11, либо уровень сигнала уменьшится так, что на выходе блока 6 компараторов устаГ

н 48 новится комбинация 00 на весь период анализа отсчетов сигнала в блоке 7 определения кода шкалы. В обоих случаях работа блока 7 определения кода шкалы будет осущестгшяться так, как описано, до тех пор,пока не появится разрешенная комбинация 10, которая запишется в блоке 14 памяти. Наличие кодовой комбинации 10 в блоке 14 памяти свидетельствует о наличии режима слежения за подобластью изменения огибающей звукового сигнала. Таким образом, осуществляется инерционное компандирование отсчетов. Предлагаемое устройство для кодирования звуковых сигналов с инерционным компандированием имеет меньшее время полного преобразования отсчета сигнала. Это связано с тем, что обработка информации с выхода блока 6 компараторов по инерционному алгоритму преобразования, не прибегая к аналого-цифровому преобразованию сигнала в первом цикле кодирования, всегда занимает меньшее время, а следовательно, повьшается быстродействие устройства. К блоки 3 Лпбяояаб К блоку 5 ОтКлояаЛ От SJIOM.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство исправления стираний | 1977 |

|

SU651479A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для кодирования звуковых сигналов | 1978 |

|

SU720715A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-08-23—Публикация

1983-04-18—Подача