Изобретение относится к вычислительной технике, а именно к устройствам контроля запоминающих устройств, и может быть использовано для повышения надежности запоминающих устройств.

Известны устройства декодирования для контроля памяти, содержащие блок вычисления синдрома, дешифратор синдрома, селекторы ошибок, корректирующие сумматоры по модулю два, позволяющие произво- дить коррекцию ошибок в любом одном разряде кодового слова на основе использования кодов Хемминга.

Однако подобные устройства не позволяют корректировать ошибки в модулях (подблоках кодового слова с известными границами), которые возникают при отказах многоразрядных БИС ЗУ.

Наиболее близким по технической сущности к изобретению является устройство декодирования для контроля модуля ошибок, содержащее блок вычисления синдрома, входы которого соединены с контрольными и информационными в хода- ми устройства и первыми входами блока корректирующих сумматоров по модулю два, первые выходы блока вычисления синдрома соединены с первыми входами блока сравнения, вторыми входами соединенного с выходами блока вычисления частичных синдромов, выходы блока сравнения соединены с первыми входами блока элементов И, вторыми входами соединенного с входами блока вычисления частичных синдромов и вторыми выходами блока вычисления син- дрома, выходы блока элементов И соедине- ны с вторыми входами блока корректирующих сумматоров по модулю два, выходы блока корректирующих сумматоров по модулю два являются выходами устройства.

Известное устройство позволяет исправить модуль ошибок длины п и может быть реализовано только для проверочных матриц, содержащих в верхней нижней полови- не единичные подматрицы размера Ь и Ь, Это существенно ограничивает область применения устройства.

Цель изобретения - расширение области применения устройства за счет коррек- ции модуля ошибок для кодов, не содержащих в информационных модулях проверочных матриц единичных подматриц.

Поставленная цель достигается тем, что устройство декодирования для коррекции модуля ошибок, содержащее блок вычисления синдрома, входы которого соединены с контрольными и информационными входами устройства и первыми входами блока

сумматоров по модулю два, первые выходы блока вычисления синдрома соединены с первыми входами блока сравнения, вторыми входами соединенного с выходами блока вычисления частичных синдромов, выходы блока сравнения соединены с первыми входами блока элементов И, выходы которого соединены с вторыми входами блока сумматоров по модулю два, выходы блока сумматоров по модулю два являются выходами устройства, дополнительно содержит блок определения местоположения ошибочных разрядов в модулях, входы которого соединены с вторыми выходами блока вычисления синдрома, а выходы - с входами блока вычисления частичных синдромов и вторыми входами блока элементов И.

Предлагаемое устройство позволяет декодировать различные модульные коды как коды с единичными подматрицами в проверочных матрицах, так и без них, что существенно расширяет функциональные возможности устройства по контролю ошибок.

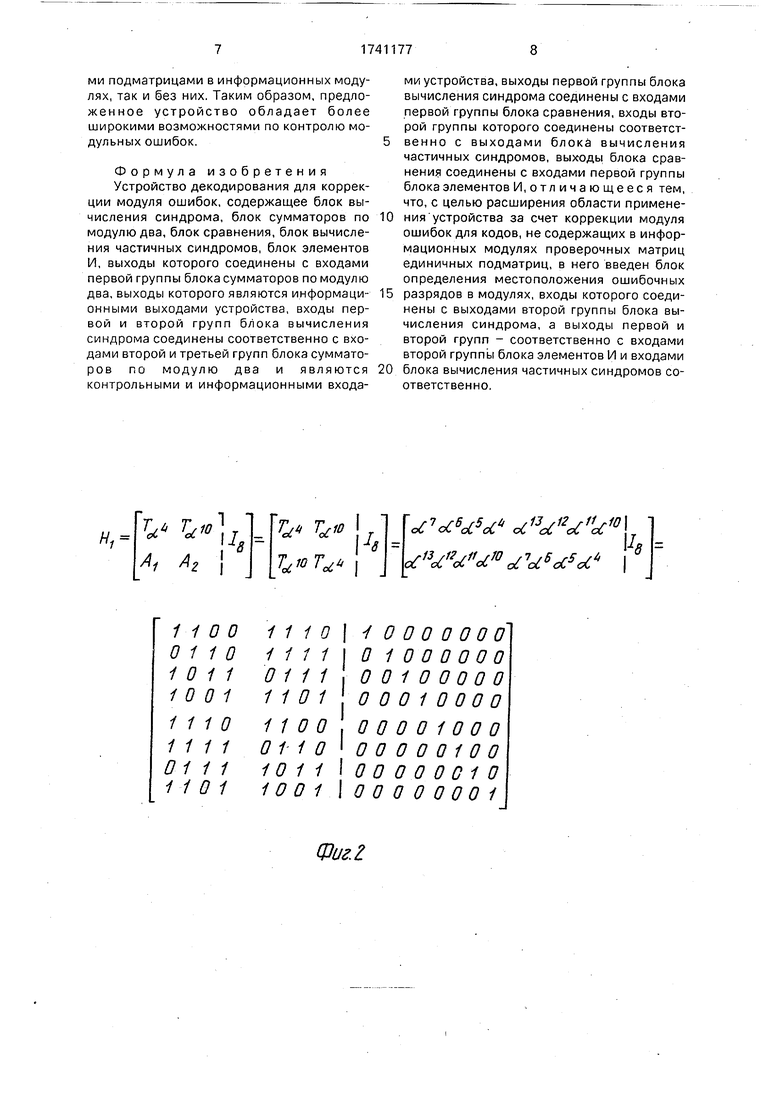

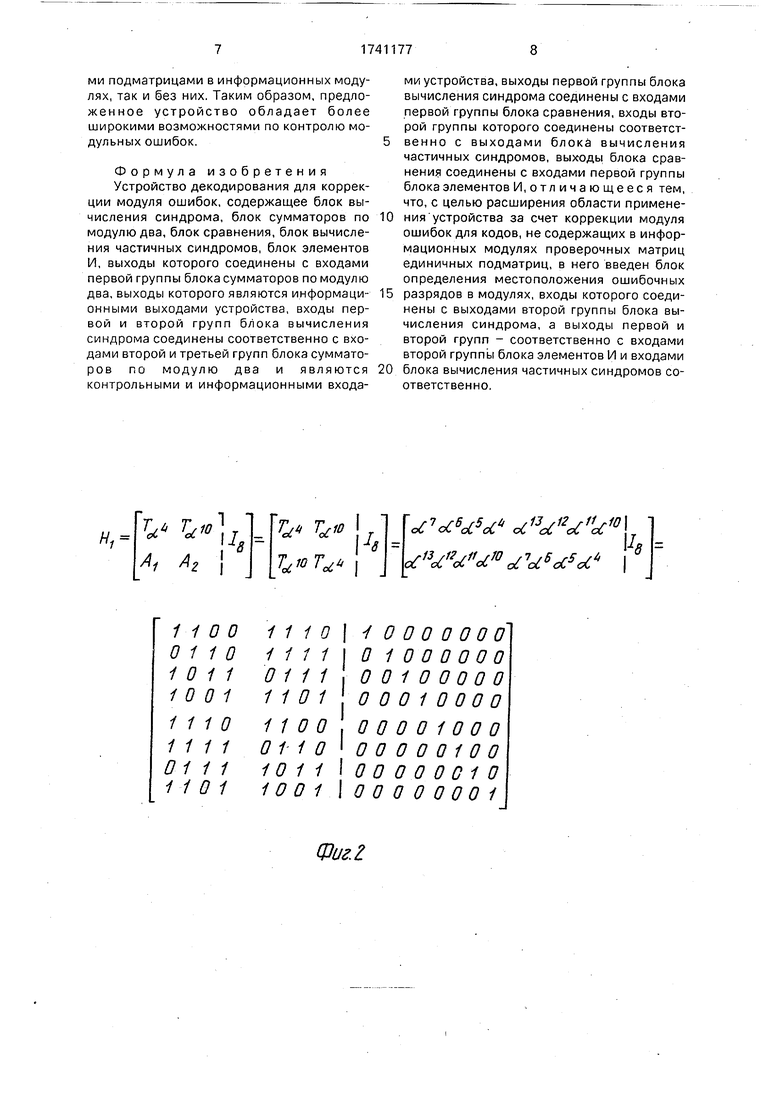

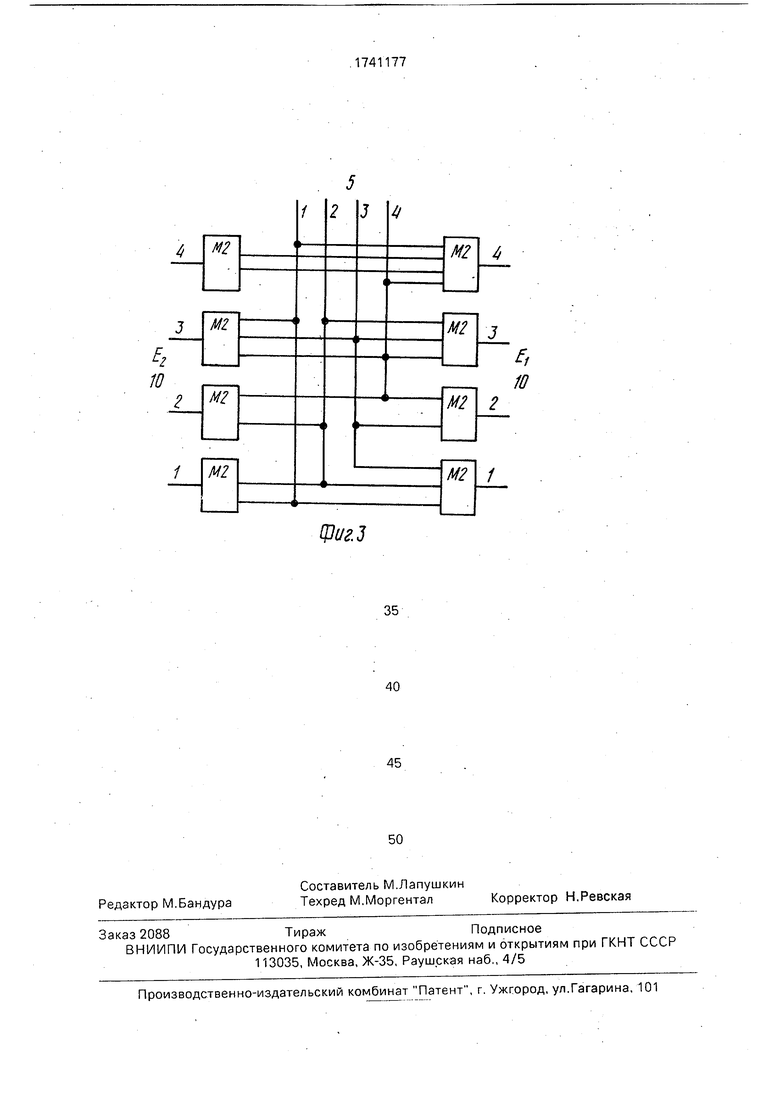

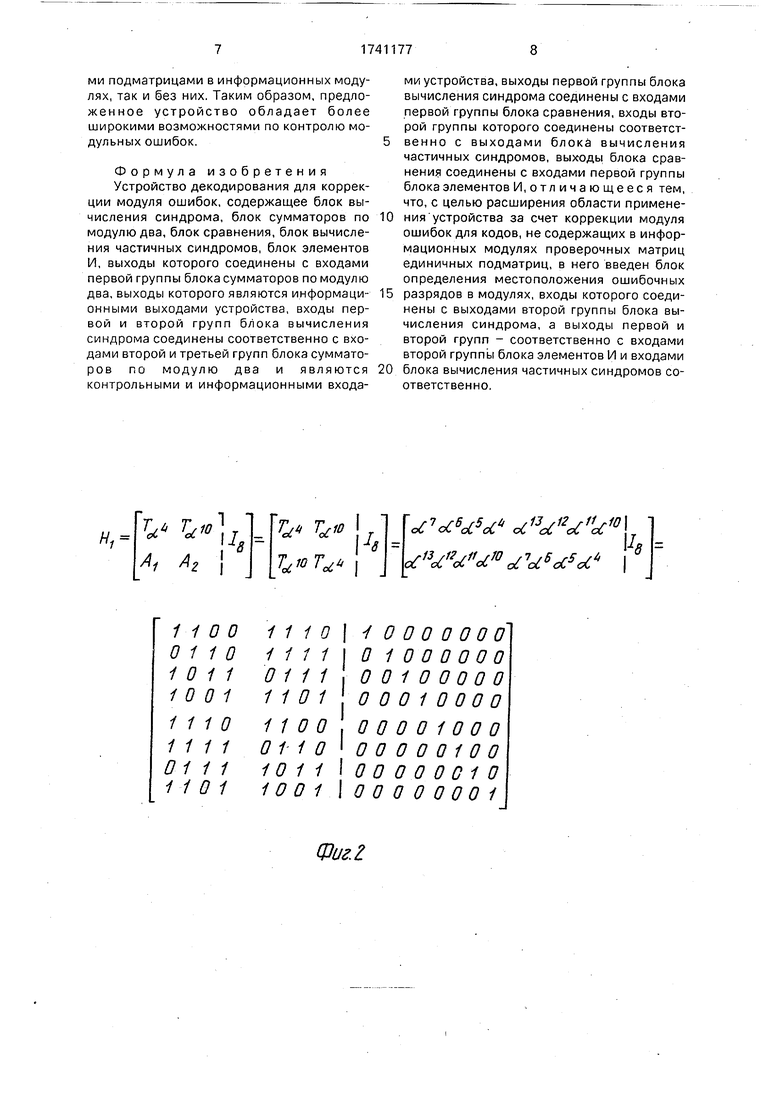

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - проверочная матрица Н1 кода (16,8) для коррекции модуля ошибок длины Ь, построенного в поле Галуа с порождающим полиномом Р(Х) х +Х+1; на фиг. 3 - реализация блока определения местоположения ошибочных разрядов в модулях для кода с проверочной матрицей HI.

Реализация блоков вычисления синдрома, вычисления частичных синдромов сравнения известна. В этих блоках используются элементы И, ИЛИ, НЕ и сумматоры по модулю два.

Устройство декодирования для контроля ошибок, содержит блок 1 вычисления синдрома, входы 2 которого соединены с контрольными и информационными входами устройства и первыми входами блока 3 сумматоров по модулю два, первые 4 и вторые 5 выходы блока вычисления синдрома соединены соответственно с первыми входами блока 6 сравнения и входами блока 7 определения местоположения ошибочных разрядов в модулях, вторыми входами 8 блок сравнения соединен с выходами блока

9вычисления частичных синдромов, входы

10которого соединены с выходами блока определения местоположения ошибочных разрядов в модулях и вторыми входами блока элементов И 11, первые входы 12 блока элементов И соединены с выходами блока сравнения,-а выходы 13 - с BTOJ, ..ми входами блока сумматоров по модулю два, выходы 14 которых являются выходами устройства.

В предложенном устройстве используются проверочная матрица модульного кода, не содержащая в информационных модулях единичных подматриц. В качестве конкретного выполнения на фиг. 2 представлена проверочная матрица Ж кода (16,8), задаваемого полиномом Р(Х) х +Х+1, позволяющая корректировать модуль ошибок длины b $4. Возможности это- го кода по коррекции модуля ошибок известны, поэтому доказательства коррекции кодом модуля ошибок длины b в обрабатываемых словах можно не приводить.

В примере конкретного исполнения на фиг. 3 рассматривается реализация блока определения местоположения ошибочных разрядов в модулях для верхних подматриц матрицы Hi.

Устройство работает следующим обра- зом.

Кодовое слово поступает на входы 2 блока 1 вычисления синдрома. На выходах 5 и 4 блока 1 в соответствии с проверочными уравнениями, полученными из матрицы Н, формируются разряды синдрома, S(Si 82). Например, для применяемого кода фиг. 2 эти разряды вычисляются следующим образом:

31+32+35+36+37+39

С2 32+33+35+36+37+38+310 Si )Сз 31 33+34+36+37+38+311 1С4 31+34+35+36+38+312 С С5 31+32+33+35+36+313 S2 ) Сб 31+32+33+34+37+38+314 /С 32+33+34+35+37+38+315 ( Св 31+32+34+35+38+316

где аЈ (0,1) - рэзряды слова, поступающие на входы 2 Ьлока 1, из них аэ-16 являются контрольными, остальные информэционны- ми.

Сигналы на выходах Ю блока 7 представляют собой векторы ошибки для каждого информзционного модуля и вычисляются по синдрому Si (выход 5 блокэ 1), э именно Е| Т«н $1.гдеТа н -Та (2m-1)-i T a представляет собой мэтрицу размером mxm, построенную в поле Галуа GFT2rr) Та Ца aj+1 аА

Для применяемого кода (фиг. 2).

-4,

Si.

11

-10

Si-Та Si.E2-Ta - SiДопустим, произошлз ошибка во вто- ром и третьем рэзрядах первого модуля, тогда Si 1010, 82 0001. На выходах 10 блока 7 будут присутствовать сигналы:

о г ,V14 ,,,13 12 1 1 т . о

bi - a a a a Jbi

Е1-ТЦ

Местоположение ошибочного модуля определяетсячгпутем вычисления чэстичных синдромов Si AI Ei в блоке 9 по сигналам Ei для каждого модуля (сигналы на выходах 10 блока 7) и сравнения в блоке 6 сигналов на выходах 8 блока 9 с синдромом S2, поступающим с выходов 4 блока 1. Для рассматриваемого кода

Равенство Si Sa 0001 указывает на то, что ошибки произошли в первом модуле, а вектор ошибки Еч 0110 (информация искажена во втором и третьем разрядах). Сигналы о векторе с выходов 13 блока 11 поступают на входы блока 3, где происходит коррекция в ошибочном модуле считываемой из входов 2 информзции. Испрэвленная информэция поступэет нэ выходы 14 устройства.

При ошибках в проверочных разрядах на выходах 13 блока 11 будут нулевые сигналы и информация с входов 2 поступит без изменения на выходы 14 устройства. Если в кэчестве верхних информэционных подмзт- риц в мэтрице Н используются единичные подматрицы, то сигнэлы с входа 5 блока 7 проходят без изменения на выход 10. В дальнейшем схема работает аналогично описанному.

Технико-экономические преимущество предложенного устройстве декодирования для контроля модуля ошибок по срэвнению с прототипом заключаются в расширении функциональных возможностей устройства по контролю ошибок. А именно: известное устройство позволяет исправить модуль ошибок длины b с помощью кодов, содержащих в проверочной матрице единичные подматрицы размером b x b, тогда как предложенное устройство - как с помощью кодов,-задаваемых матрицей Н с единичными подматрицами в информационных модулях, так и без них. Таким образом, предложенное устройство обладает более широкими возможностями по контролю модульных ошибок.

Формула изобретения Устройство декодирования для коррекции модуля ошибок, содержащее блок вычисления синдрома, блок сумматоров по модулю два, блок сравнения, блок вычисления частичных синдромов, блок элементов И, выходы которого соединены с входами первой группы блока сумматоров по модулю два, выходы которого являются информаци- онными выходами устройства, входы первой и второй групп блока вычисления синдрома соединены соответственно с входами второй и третьей групп блока сумматоров по модулю два и являются контрольными и информационными входами устройства, выходы первой группы блока вычисления синдрома соединены с входами первой группы блока сравнения, входы второй группы которого соединены соответственно с выходами блока вычисления частичных синдромов, выходы блока сравнения соединены с входами первой группы блока элементов И,отличающееся тем, что, с целью расширения области применения устройства за счет коррекции модуля ошибок для кодов, не содержащих в информационных модулях проверочных матриц единичных подматриц, в него введен блок определения местоположения ошибочных разрядов в модулях, входы которого соединены с выходами второй группы блока вычисления синдрома, а выходы первой и второй групп - соответственно с входами второй группы блока элементов И и входами блока вычисления частичных синдромов соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство декодирования для коррекции модулей ошибок | 1990 |

|

SU1737515A1 |

| Устройство декодирования для коррекции двойных ошибок | 1991 |

|

SU1833968A1 |

| Декодер циклического кода | 1988 |

|

SU1599996A1 |

| Устройство для контроля блоков памяти | 1978 |

|

SU765883A1 |

| Матричное вычислительное устройство | 1990 |

|

SU1833890A1 |

| Устройство для исправления пакета ошибок длины два | 1988 |

|

SU1578812A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1226536A1 |

| СПОСОБ И ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ДВУХ ОШИБОК В ПРИНИМАЕМОМ КОДЕ | 2006 |

|

RU2336559C2 |

| Устройство для исправления ошибок в блоках памяти | 1981 |

|

SU1070605A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

Изобретение относится к вычислительной технике, а именно к устройствам контI роля запоминающих устройств, и может быть использовано для повышения надежности запоминающих устройств. Целью изобретения является расширение области применения устройства за счет коррекции модуля ошибок для кодов, не содержащих в информационных модулях проверочных матриц единичных подматриц. Устройство содержит блок 1 вычисления синдрома, блок 3 сумматоров по модулю два, блок 6 сравнения, блок 7 определения местоположения ошибочных разрядов в модулях Устройство позволяет осуществлять коррекцию модуля ошибок с помощью кодов, задаваемых проверочными матрицами, содержащими произвольные подматрицы в информационных модулях. 3 ил. xj XI Ill

Ь«

I J. .

А, А,

8

ъ ъ

Т

Фиг. г

ct oCWcC оС13оС12 сС10

cC bW 10

И

в

5

10

2

Щи&З

J

ft

10

| Каган Б.М., Мкртумян И.Б | |||

| Основы эксплуатации ЭВМ | |||

| М.: Энергоатомиздат, 1988, с | |||

| Приспособление для удержания и защиты диафрагмы в микрофонной коробке | 1925 |

|

SU431A1 |

| Конопелько В.К., Лосев В.В | |||

| Надежное хранение информации в полупроводниковых запоминающих устройствах М.: Радио и связь, 1986, с | |||

| Способ прикрепления барашков к рогулькам мокрых ватеров | 1922 |

|

SU174A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-06-15—Публикация

1990-06-04—Подача