Изобретение относится к автоматике и вычислительной технике и может быть использовано в информационно-измерительных системах для построения аналого-цифровых преобразователей угловых перемещений.

Цель изобретения - упрощение преобразователя.

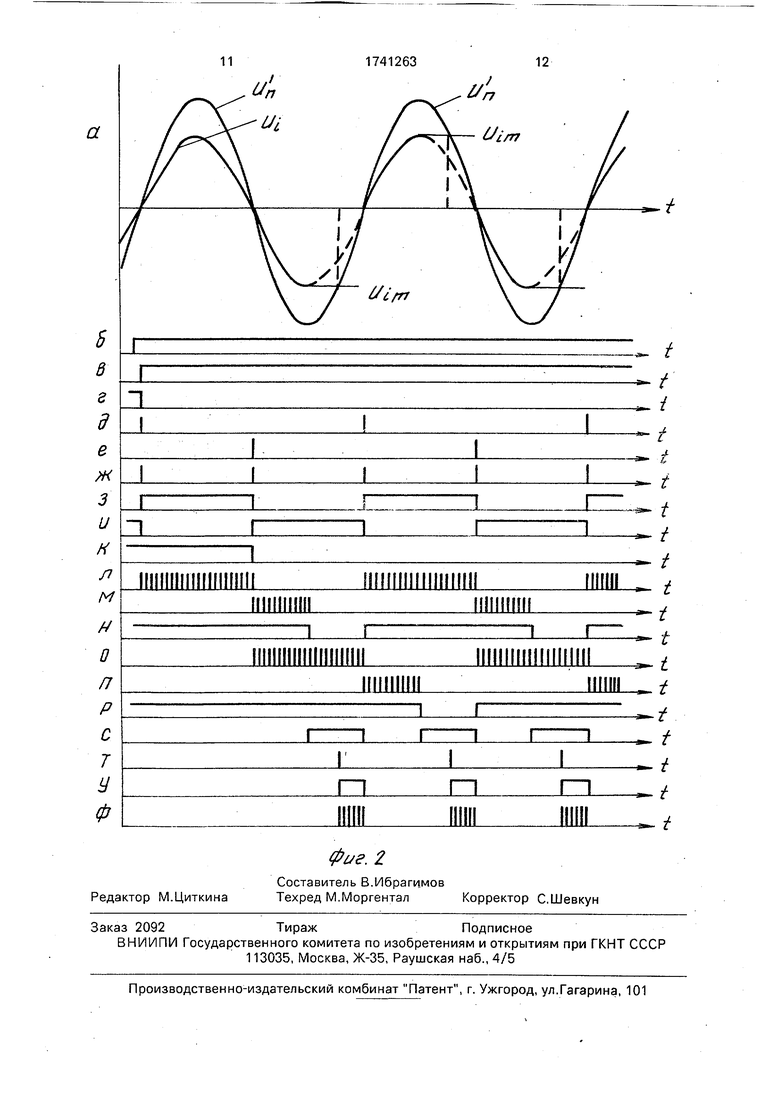

На фиг. 1 показана структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы его работы,

Преобразователь угла поворота вала в код содержит (фиг.1) сельсин 1, вход которого подключен к выходу источника 2 напряжения питания и к опорному входу блока 3 грубого отсчета (БГО), а выходы соединены с информационными входами коммутатора 4 и БГО, группа выходов которого соединена с управляющими входами коммутатора, выход которого подключен к информационному входу блока 5 памяти и к входу первого компаратора 6, выходы которого соединены

с входами элемента ИЛИ 7 и первого триггера 8, прямой выход Q которого соединен с первыми входами первого 9 и второго 10 элементов И, а инверсный выход Q - с первыми входами третьего 11 и четвертого 12 элементов И, генератор 13 импульсов, выход которого подключен к вторым входам второго и третьего элементов И и к счетному входу второго триггера 14, прямой выход которого подключен к вторым входам первого и четвертого элементов И, первый счетчик 15, информационные входы (входы сложения и вычитания) которого соединены с выходами первого и третьего элементов И, а выход - с третьим входом третьего элемента И и с первым входом пятого элемента И

16,выполненного с инверсным выходом (т.е. в виде элемента И-НЕ), второй счетчик

17,информационные входы которого соединены с выходами четвертого и второго элементов И, а выход - с третьим входом второго элемента И и с вторым входом пято(Л

С

ч|

N

,д

ГО

о

со

го элемента И, выход которого подключен к управляющему входу блока памяти, третий триггер 18, первый вход D которого является управляющим входом преобразователя Пуск, второй вход С подключен к прямому выходу первого триггера, инверсный выход - к управляющему входу R первого счетчика, а прямой выход- к первому входу D четвертого триггера 19, второй вход С которого подключен к инверсному выходу первого триггера, а инверсный выход - к управляющему входу второго счетчика, и фазоинвер- тор -20, сигнальный вход которого подключен к выходу источника напряжения питания, управляющий вход - к соответствующему выходу Б ГО, а выход - к первому входу второго компаратора 21, второй вход которого подключен к выходу блока памяти, третий (стробирующий) вход - к выходу пятого элемента И, а выход - к первому входу S пятого триггера 22, второй вход R которого соединен с выходом элемента ИЛИ, а прямой выход - с первым входом шестого элемента И 23, второй вход которого подключен к выходу генератора импульсов, а выход - к информационному входу третьего счетчика 24, управляющий вход которого соединен с инверсным выходом четвертого триггера, а выход является выходом младших разрядов преобразователя.

Устройство работает следующим образом.

Напряжения Ui,U2,U3 вторичных обмоток сельсина 1 поступают на блок 3 грубого отсчета. Этот блок в зависимости от знака фазы указанных напряжений относительно напряжения Un питания сельсина, снимаемого с выхода источника 2, формирует, во- первых, код NI грубого отсчета угла поворота 6ротора сельсина, который изменяется с дискретностью AQ K-60° (где ,1,25) и является кодом старших разрядов преобразователя (на фиг.1 не показан), во-вторых, сигналы управления коммутатором 4, который подключает к входу компаратора 6 одно из фазных напряжений сельсина Ui (в 1 и 4 сектантах , во 2 и 5 , в 3 и 6 ), в-третьих, сигнал управления фазоинвертором 20, который в зависимости от номера сектанта инвертирует напряжение Un питания или пропускает его на вход компаратора 21 без изменения полярности, что необходимо для обеспечения синфазности напряжений Ui и Un1, где Un напряжение на выходе фазоинвертора (фиг.2а).

В исходном состоянии устройства триггеры 18,19 и 22 находятся в положении О, счетчики 24,15 и 17 заблокированы (принудительно установлены в нуль) потенциалом высокого уровня, соответствующего уровню логической 1, с инверсных выходов триггеров 18 и 19 (фиг.2г,к). Триггер 14, выпол5 няющий функции делителя частоты fi тактовых импульсов генератора 13 на два, поочередно перебрасывается из одного положения в другое этими импульсами, а триг- гер 8 - выходными импульсами

10 компаратора 6, срабатывающего в моменты времени, соответствующие переходу напряжения Ui из отрицательной области в положительную (фиг. 2д) и обратно (фиг. 2е). Процесс измерения начинается с мо15 мента подачи разрешающего потенциала 1 на управляющий вход Пуск устройства (фиг.2б), при этом ближайшим перепадом потенциала 0-1 (S) с прямого выхода триггера 8 (фиг. 2з) триггер 18 устанавливается

0 в положение, соответствующее уровню потенциала на его D-входе, т.е. в положение 1, при котором на его прямом выходе потенциал 1(фиг,2в), а на инверсном- потенциал низкого уровня, соответствующего

5 уровню логического О (фиг. 2г). Потенциал 1 с прямого выхода триггера 18 подается на D-вход триггера 19, подготавливая его, а потенциал О с инверсного выхода - на управляющий вход реверсивного счетчика

0 15, разблокируя его, с этого момента времени (t0) указанный счетчик готов к подсчету импульсов тактовой частоты. Поскольку данный момент времени приходится на начало очередного прямоугольного импульса с

5 прямого выхода триггера 8 (фиг. 2з), оказывается открытым элемент И 9, который пропускает выходные импульсы триггера 14 с частотой f-r/2 на информационный вход сложения реверсивного счетчика 15 (фиг.2л).

0 Этот счетчик работает в режиме Сложение импульсов в течение интервала времени, пропорционального длительности первого полупериода напряжения Ui (реверсивный счетчик 17 остается пока блокированным

5 потенциалом 1 с инверсного выхода триггера 19, фиг.2к).

В момент времени, соответствующий переходу этого напряжения из положительной области в отрицательную (фиг.2а), им0 пульс с соответствующего выхода компаратора 6 (фиг. 2е) устанавливает триггер 8 в положение О, при котором на прямом выходе триггера потенциал О (фиг.2з), а на инверсном - потенциал 1 (фиг.2и).

5 Перепадом потенциала О -1 (S) с инверсного выхода указанного триггера триггер 19 устанавливается в положение 1 (т.к , на его D-входе присутствует потенциал 1 с прямого выхода триггера 18, фиг. 2в) и потенци- ал О с его инверсного выхода (фиг. 2к)

снимает блокировку счетчиков 17 и 24. С установкой триггера 8 в положение О элемент И 9 закрывается (прекращая доступ тактовых импульсов с частотой fr/2 на информационный вход сложения реверсивного счетчика 15, фиг. 2л), а элементы И 11 и

12оказываются открытыми, при этом тактовые импульсы с частотой fr/2 с выхода триггера 14 проходят через элемент И 12 на информационный вход сложения реверсивного счетчика 17 в течение второго полупериода напряжения Ui (фиг.2б), а тактовые импульсы с частотой f с выхода генератора

13через элемент И 11 - на информационный вход вычитания реверсивного счетчика 15 (фиг.2м).

Так как в режиме вычитания тактовые импульсы на реверсивный счетчик 15 поступают с частотой вдвое большей, чем в режиме сложения, он устанавливается в нулевое состояние за интервал времени, равный Т/4 (где Т - период напряжения Ui) с момента перехода Ui из положительной области в отрицательную, при этом потенциал О с выхода реверсивного счетчика 15 (фиг. 2н), во-первых, блокирует элемент И 11 (прекращается поступление тактовых импульсов с частотой fr на информационный вход вычитания реверсивного счетчика 15, который остается в нулевом состоянии до начала следующего периода напряжения Ui, фиг.2м), во-вторых, подается на один из входов элемента И-НЕ 16, на другом входе которого потенциал 1 с выхода другого реверсивного счетчика 17(фиг.2р). Потенциал на выходе указанного элемента И-НЕ скачком изменяется до уровня 1 (фиг. 2с), переводя блок 5 памяти в режим запоминания (фиксации) амплитудного значения и«ц напряжения Ui, поступающего на его информационный вход с выхода коммутатора 4 (фиг. 2,а). В момент времени, когда значение Dim напряжения Ui становится равным текущему значению напряжения Un1 (), срабатывает компаратор 21, импульс с выхода которого (фиг. 2т) устанавливает триггер 22 в положение 1, и потенциал 1 с прямого выхода последнего (фиг. 2у) открывает элемент И 23, разрешая прохождение тактовых импульсов генератора 13 на информационный вход счетчика 24 (фиг.2чф). Чтобы уменьшить вероятность ложных срабатываний компаратора 21, желательно предусмотреть возможность его включения в рабочий режим (режим сравнения напряжений) в узком временном окне (например, в интервале, равном Т/4, т.е. в течение длительности выходного импульса элемента И-НЕ 16, фиг.2с) и выключения (блокировки) вне его пределов, для чего выполняют

компаратор21 стробируемыми подключают его третий (стробирующий) вход к выходу элемента И-НЕ 16 (соответствующая связь на фиг. 1 показана пунктиром).

В момент времени, соответствующий

переходу напряжения Ui из отрицательной области в положительную, вновь срабатывает компаратор 6, импульс с первого выхода которого (фиг.2,д), пройдя через элемент

0 ИЛИ 7 (фиг. 2ж), возвращает триггер 22 в положение О (фиг. 2у), при этом элемент И 23 закрывается, поступление тактовых импульсов на счетчик 24 прекращается (фиг. 2ф) и в нем остается код, пропорциональный

50в диапазоне 60° (код младших разрядов преобразователя). Этим же импульсом триггер 8 устанавливается в положение 1, при этом потенциал 1 с его прямого выхода (фиг.2з) открывает элементы И 9 и 10. Такто0 вые импульсы с частотой tV /2 с выхода триггера 14 проходят через открытый элемент И 9 на информационный вход сложения реверсивного счетчика 15 в течение третьего (с момента времени to) полупериода напря5 жения Ui (фиг.2л), при этом с первым же тактовым импульсом, подсчитанным счетчиком, на его выходе появляется потенциал 1 (фиг.2н), а на выходе элемента И-НЕ 16 - потенциал О (фиг. 2с), переводящий блок

0 5 памяти в режим сложения (фиг.2а). Одновременно тактовые импульсы с частотой fr с выхода генератора 13 проходят через открытый элемент И 10 на информационный вход вычитания реверсивного счетчика 17

5 (фиг.2п). Так как в режиме вычитания тактовые импульсы на реверсивный счетчик 17 поступают с частотой вдвое большей, чем в режиме сложения, он устанавливается в нулевое состояние за интервал времени, рав0 ный Т/4, с момента перехода напряжения Ui из отрицательной области в положительную. Нулевое состояние указанного счетчика (потенциал О на его выходе обнуления, фиг. 2р) соответствует моменту достижения

5 амплитудного значения Uim в области положительных значений Ui (фиг. 2а) и вызывает появление потенциала 1 на выходе элемента И-НЕ 16 (фиг. 2с), вновь переводящего блок 5 памяти в режим запоминания

0 (фиксации) Uim. В момент времени, когда выполняется равенство , срабатывает компаратор21, импульсе выхода которо- . го (фиг. 2т) устанавливает триггер 22 в положение 1 (фиг. 2у), элемент И 23 откры5 вается и начинается заполнение счетчика 24 тактовыми импульсами генератора 13 (фиг.2ф). В конце рассматриваемого полупериода напряжения Ui очередной импульс с второго выхода компаратора 6 (фиг.2е), пройдя через элемент ИЛИ 7 (фиг.2ж), возвращает триггер 22 в положение О (фиг.2у), и поступление тактовых импульсов в счетчик 24 прекращается (фиг.2ф). Этим же импульсом триггер 8 устанавливается в положение О при этом потенциал 1 с его инверсного выхода (фиг. 2и) открывает элементы И 11 и 12. Дальнейшая последовательность операций аналогична рассмотренной выше.

Ф о р м у л а и з о б р е т е н и я

Преобразователь угла поворота вала в код, содержащий сельсин, вход которого подключен к выходу источника напряжения питания и опорному входу блока грубого отсчета, а выходы соединены с информаци- онными входами коммутатора и блока грубого отсчета, группа выходов которого соединена с управляющими входами коммутатора, выход которого соединен с информационным входом блока памяти и с входом первого компаратора, выходы которого соединены с входами элемента ИЛИ и первого триггера, прямой выход которого соединен с первыми входами первого и второго элементов И, а инверсный выход - с первыми входами третьего и четвертого элементов И, генератор импульсов, выход которого соединен с вторыми входами второго и третьего элементов И и со счетным входом второго триггера, прямой выход которого соединен с вторыми входами первого и четвертого элементов И, выходы первого и третьего элементов И соединены с информационными входами первого счетчика, выходы второго и четвертого элементов И соединены с информационными входами второго счетчика, пятый элемент И, третий триггер, первый

вход которого является управляющим входом преобразователя, а второй вход подключен к прямому выходу первого триггера, четвертый триггер, фазоинвертор, сигнальный вход которого подключен к выходу источника напряжения питания, управляющий вход - к соответствующему выходу блока грубого отсчета, а выход соединен с первым входом второго компаратора, второй вход которого подключен к выходу блока памяти, а выход соединен с первым входом пятого триггера, прямой выход которого соединен с первым входом шестого элемента И, второй вход которого подключен к выходу генератора импульсов, а выход соединен с информационным входом третьего счетчика, выход которого является выходом младших разрядов преобразователя, отличающийся тем, что, с целью упрощения преобразователя, в нем выход элемента ИЛИ соединен с вторым входом пятого триггера, выходы первого и второго счетчиков соединены с входами пятого элемента И, выход которого соединен с управляющим входом блока памяти и с третьим входом второго компаратора, инверсные выходы третьего и четвертого триггеров соединены с управляющими входами первого и второго счетчиков соответственно, выходы которых соединены с третьими входами третьего и второго элементов И соответственно, прямой- выход третьего триггера соединен с первым входом четвертого триггера, второй вход которого подключен к инверсному выходу первого триггера, а инверсный выход соединен с управляющим входом третьего счетчика.

t

а

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1982 |

|

SU1035629A1 |

| Преобразователь угла поворота антенны радиолокационной станции в код | 1983 |

|

SU1119052A1 |

| Преобразователь угла поворота валаВ КОд | 1979 |

|

SU836643A1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1125643A1 |

| Аналого-цифровой преобразователь узкополосных сигналов | 1983 |

|

SU1115224A2 |

| Цифровой вольтметр | 1981 |

|

SU970675A1 |

| Следящий аналого-цифровой преобразователь | 1990 |

|

SU1802413A1 |

| Преобразователь переменного напряжения в код | 1985 |

|

SU1297226A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1991 |

|

RU2014740C1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в информационно-измерительных системах для построения аналого-циф- ровых преобразователей угловых перемещений. Целью изобретения является упрощение преобразователя. С этой целью в преобразователе угла поворота вала в код, содержащем сельсин, источник напряжения питания, блок грубого отсчета, коммутатор, блок памяти, два компаратора, элемент ИЛИ, шесть элементов И, пять триггеров, генератор импульсов, три счетчика, фазоин- вертор, изменены связи между элементами, благодаря чему сохраняются все основные параметры преобразователя при меньшем количестве входящих в него элементов. 2 ил.

в

.

ZL

IHIIIIHIIIIIIHiHII

li

шипит

JZL

Ж

Фиг. 2

Редактор М.Циткина

Составитель В.Ибрагимов Техред М.Моргентал

t

.

t

t

liiHlliliMlHIIIII

MiiiHifM

iimiUKiniiiini

-i

t

JH

-t t

-t

Корректор С.Шевкун

| Преобразователь угла поворота вала в код | 1982 |

|

SU1035629A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-06-15—Публикация

1989-11-09—Подача