(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового управления тиристорным регулятором | 1986 |

|

SU1427515A1 |

| Устройство для цифрового управления тиристорным регулятором | 1980 |

|

SU860266A1 |

| Устройство для управления регулируемым преобразователем переменного напряжения в переменное | 1990 |

|

SU1739452A1 |

| Устройство для управления тиристорным преобразователем | 1980 |

|

SU921033A1 |

| Цифровое устройство для управления многофазным тиристорным преобразователем | 1978 |

|

SU782125A1 |

| Устройство для цифрового управления @ -фазным широтно-импульсным преобразователем | 1983 |

|

SU1138902A1 |

| Устройство для управления @ -фазным автономным инвертором напряжения | 1983 |

|

SU1089753A1 |

| Устройство для управления тиристорным преобразователем | 1978 |

|

SU714619A1 |

| Цифровое устройство для управления тиристорным преобразователем с дискретным сдвигом импульсов | 1976 |

|

SU736341A1 |

| Устройство для цифрового управления @ -фазным преобразователем | 1981 |

|

SU970626A1 |

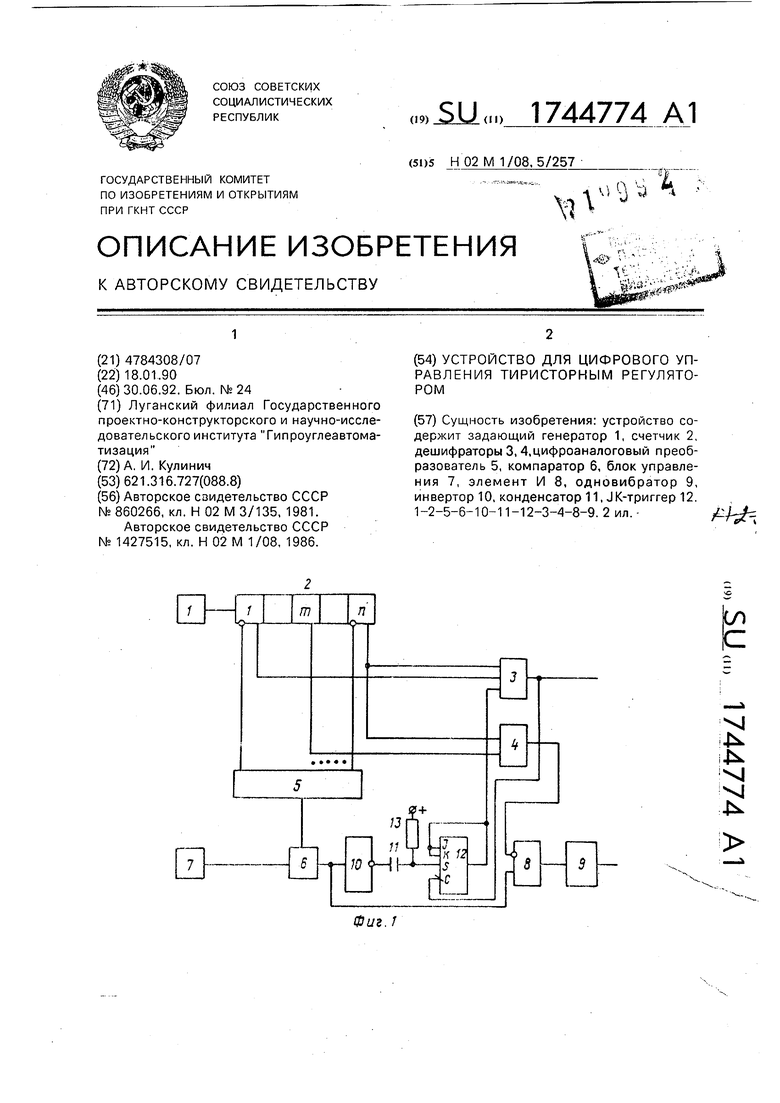

Сущность изобретения: устройство содержит задающий генератор 1, счетчик 2 дешифраторы 3, 4,цифроаналоговый преобразователь 5, компаратор 6, блок управления 7, элемент И 8, одновибратор 9, инвертор 10, конденсатор 11, JK-триггер 12 1-2-5-6-10-11-12-3-4-8-9 2 ил ЯтЬ

XI

Ьь

,4 vj vj 4

Изобретение относится к электротехнике, а именно к устройствам для управления полупроводниковыми преобразователями.

Известно устройство для цифрового управления тиристорным регулятором, содержащее задающий генератор, соединенный со счетным входом тактового счетчика на триггерах, тактовый счетчик информационного блока, дешифраторы, блок управления, элементы И, усилители сдвигаемой и несдвигаемой последовательности импульсов.

Однако данное устройство обладает рядом существенных недостатков, снижающих надежность работы.

В известном устройстве импульсы сдвигаемой и несдвигаемой последовательностей поступают на соответствующие тиристоры импульсного регулятора, Однако для устойчивой работы регулятора, т. е. для полного перезаряда коммутирующей емкости и надежного запирания тиристоров, устройство управления должно не допускать сближения импульсов сдвигаемой и несдвигаемой последовательностей на время менее определенного минимального времени, величина которого рассчитывается для каждого конкретного тиристорного регулятора. Такой минимальный сдвиг известное устройство не обеспечивает.

Кроме того, заложенное в данном устройстве решение позволяет регулировать длительность выходного импульса преобразователя только последовательно-от минимальной до максимально возможной, а затем от максимальной - до минимальной. Если длительность импульса имеет величину 0,1-0,2 от максимальной, то при подаче сигнала на уменьшение ее сначала произойдет скачек длительности до величины 0,9- 0,8 от максимальной и с этого значения начнется ее уменьшение. Это связано с тем, что для прямого и обратного счета используется один тактовый счетчик, а для перехода с одного направления на другое используются два дешифратора, один из которых подключен к прямым выходам счетчика, а второй - к инверсным. Одно и то же состояние счетчика в прямом и инверсном выходах соответствует разным длительностям выходного импульса, а следовательно, на регулирование наложены указанные ограничения во избежание скачков длительности выходного импульса.

Наиболее близким к изобретению по технической сущности является устройство для цифрового управления тиристорным регулятором, содержащее задающий генератор, соединенный со счетным входом n-разрядного счетчика на триггерах, прямые выходы которого с 1-го по n-й разряд соединены с входами первого дешифратора, выход которого является выходом импульсов несдвигаемой последователь

ности, прямые выходы с т-го по n-й разряд соединены с входами второго дешифратора, а инверсные выходы всех разрядов подключены к входам цифроаналогового преобразователя, выход которого подключен к

0 первому входу компаратора, второй вход ко-, торого подключен к выходу блока управления, а выход г к прямому входу элемента И, инверсный вход которого подключен к выходу второго дешифратора, а выход - к входу

5 одновибратора, выход которого является выходом импульсов сдвигаемой последовательности.

Однако в начале диапазона регулирования напряжения, когда напряжение с блока

0 управления только начинает касаться снизу пилообразного напряжения, на выходе компаратора образуется короткий импульс, который не всегда запускает элемент задержки, разрешающий формирование га5 сящих импульсов.

Поэтому в начале регулирования возможен срыв коммутации, что ведет к нарушению работоспособности устройства.

Кроме того, в известном устройстве эле0 мент задержки вырабатывает по положительному фронту напряжения на выходе компаратора импульс напряжения логической 1, который по длительности всегда больше периода следования импульсов на

5 выходе дешифратора. При изменении частоты следования импульсов на выходе дешифратора необходимо изменять и длительность импульса элемента задержки. Цель изобретения - повышение надеж0 ности работы устройства управления.

Поставленная цель достигается тем, что устройство для цифрового управления тиристорным регулятором снабжено дифференцирующей RC-цепочкой, JK-триггером и

5 инвертором, вход которого подключен к выходу компаратора, а выход через конденса- тор дифференцирующей RC-цепочки, резистор которой подключен к плюсовой клемме питания, - к установочному входу

0 JK- риггера, тактовый вход которого подключен к выходу первого дешифратора. (п+1)-й вход которого вместе с J- и К-входа- ми JK-триггера подключен к выходу JK-триг- гера.

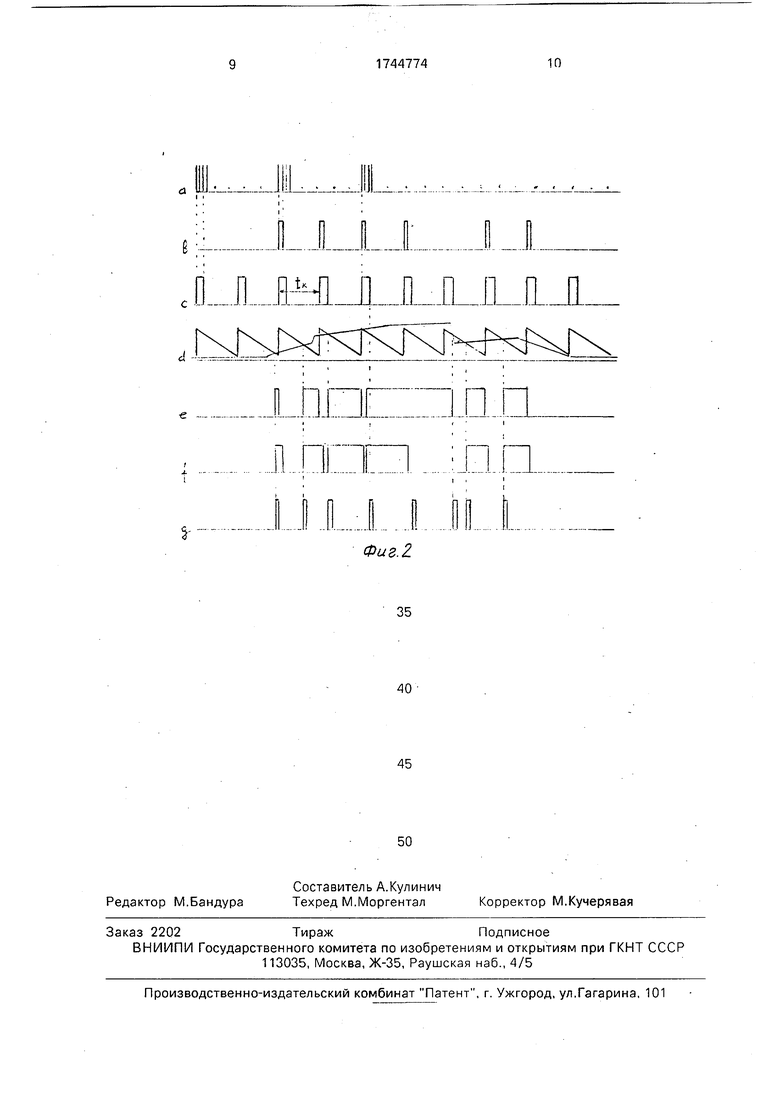

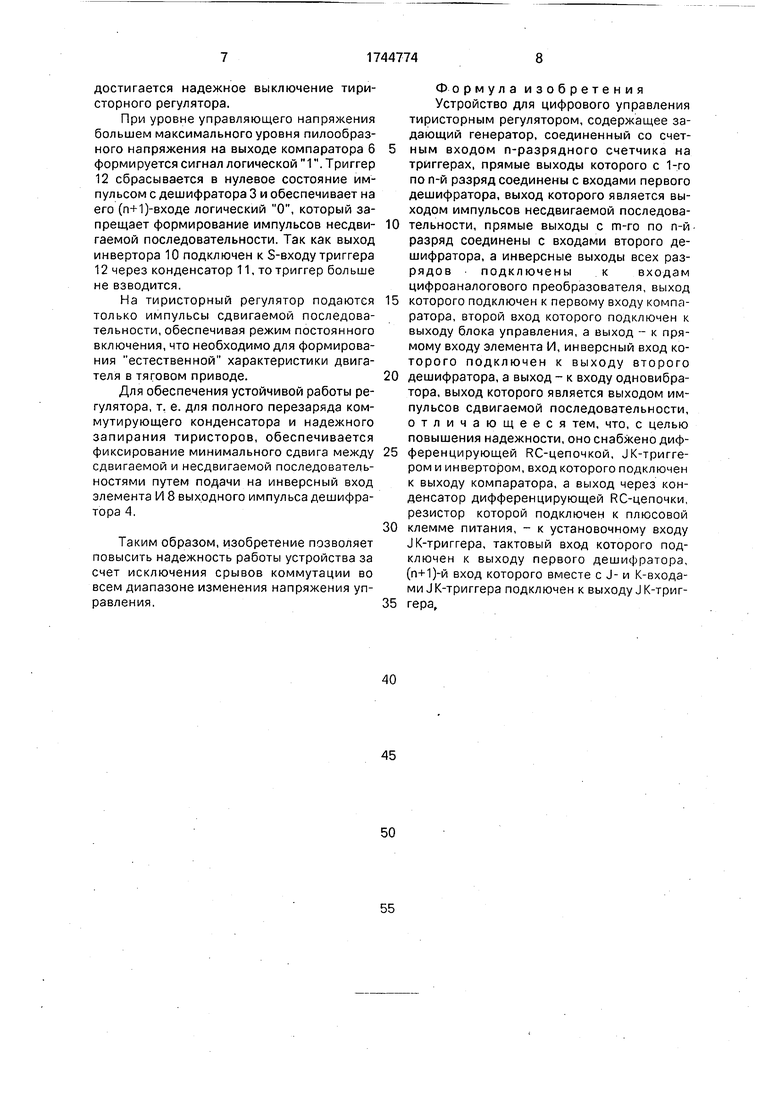

5На фиг. 1 представлена функциональная схема устройства управления; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Устройство для цифрового управления тиристорным регулятором содержит задающий генератор 1, соединенный со счетным входом n-разрядного счетчика 2 на триггерах, прямые выходы которого с 1-го по п-й разряд соединены с входами первого дешифратора 3, выход которого является выходом импульсов несдвигаемой последовательности, прямые выходы с m-ro по n-й разряд соединены с входами второго дешифратора 4, а инверсные выходы всех разрядов подключены к входам цифроана- логового преобразователя 5, выход которого подключен к первому входу компаратора 6, второй вход которого подключен к выходу блока 7 управления, а выход - к прямому входу элемента И 8, инверсный вход которого подключен к выходу второго дешифратора, а выход - к входу одновибратора 9, выход которого является выходом импульсов сдвигаемой последовательности.

Устройство дополнительно снабжено дифференцирующей RC-цепочкой 11, 13, JK-триггером 12, инвертором 10, вход которого подключен к выходу компаратора 6, а выход через конденсатор 11 дифференцирующей RC-цепочки, резистор 13 которой подключен к плюсовой клемме питания, - к установочному входу JK-триггера 12, тактовый вход которого подключен к выходу первого дешифратора 3, (п+1)-й вход которого вместе с J- и К-входами J К-триггера подключен к выходу JK-триггера.

Устройство работает следующим образом.

С генератора 1 на счетный вход тактового счетчика 2 непрерывно поступают тактовые импульсы (фиг. 2а), приводящие к изменению состояния его триггеров.

В соответствии с состоянием триггеров коды в виде двоичных сигналов поступают на входы первого дешифратора 3 и второго дешифратора 4, При наличии на (п+1)-входе дешифратора 3 логической 1 на его выходе присутствуют импульсы длительностью tu-i (фиг. 2в) равной

tui j- ТГ i

где fr - частота импульсов генератора 1;

Тг - период следования импульсов генератора.

Период следования импульсов равен

2П где п - число разрядов счетчика 2.

Таким образом, на выходе дешифратора 3 образуются импульсы длительностью tu-| и периодом следования Тк, которые являются импульсами несдвигаемой последовательности.

Аналогичным образом на выходе дешифратора 4 образуются импульсы длительностью tua и периодом Тк (фиг 2 с) tujrlr ,

где n-m - число старших разрядов счетчика 2, подключенных к дешифратору.

Цифроаналоговый преобразователь 5 преобразует код на инверсных выходах счетчика 2 в аналоговое пилообразное напряжение (фиг. 2d), которое поступавi на первый вход компаратора 6 и сравнивается там с напряжением, поступающим на второй вход с выхода блока 7 управления. В момент равенства мгновенных значений поступающих на входы напряжений компаратор 6 переключается и на его выходе образуется импульсное напряжение (фиг. 2е), которое поступает на инвертор 10 и на прямой вход элемента И 8.

Спадом синвертированного сигнала через дифцепочку С11-Р13 триггер 12 устанавливается в состояние логической 1 на выходе и на своих J- и К-входах (фиг 2f). Таким образом устанавливается разрешающий сигнал на (п-Н)-входе дешифратора 3.

При наличии нулевого уровня напряжения на выходе дешифратора 4 на выходе элемент И 8 появляется сигнал логической

1, запускающий одновибратор 9, который на своем выходе формирует импульс сдвигаемой последовательности (фиг. 2д) длительностью .

Импульс с выхода дешифратора 3 постулает на С-вход триггера 12 и сбрасывает его в нулевое состояние.

На (п+1)-входе дешифратора 3 устанавливается запрещающий сигнал.

Импульсы с выхода одновибратора 9

сдвигаемой последовательности и с дешифратора 3 несдвигаемой последовательности поступают на соответствующие тиристоры импульсного регулятора, при этом сдвигаемые импульсы используются для включения

основных тиристоров, а несдвигаемые - для включения гасящих тиристоров. Изменением уровня напряжения управления с выхода блока 7 осуществляется регулирование длительности выходного импульса напряжения

регулятора.

При уменьшении уровня напряжения управления с выхода блока 7 управления ниже минимального уровня пилообразного напряжения цифроаналогового преобразователя компаратор 6 не переключается и не взводит триггер 12, который сбрасывается в нулевое состояние импульсом с дешифратора 3, что обеспечивает формирование последними гасящих импульсов, чем

достигается надежное выключение тири- сторного регулятора.

При уровне управляющего напряжения большем максимального уровня пилообразного напряжения на выходе компаратора 6 формируется сигнал логической 1. Триггер 12 сбрасывается в нулевое состояние импульсом с дешифратора 3 и обеспечивает на его (п+1)-входе логический О, который запрещает формирование импульсов несдвигаемой последовательности. Так как выход инвертора 10 подключен к S-входу триггера 12 через конденсатор 11, то триггер больше не взводится.

На тиристорный регулятор подаются только импульсы сдвигаемой последовательности, обеспечивая режим постоянного включения, что необходимо для формирования естественной характеристики двигателя в тяговом приводе.

Для обеспечения устойчивой работы регулятора, т. е. для полного перезаряда коммутирующего конденсатора и надежного запирания тиристоров, обеспечивается фиксирование минимального сдвига между сдвигаемой и несдвигаемой последовательностями путем подачи на инверсный вход элемента И 8 выходного импульса дешифратора 4.

Таким образом, изобретение позволяет повысить надежность работы устройства за счет исключения срывов коммутации во всем диапазоне изменения напряжения управления.

Формула изобретения Устройство для цифрового управления тиристорным регулятором, содержащее задающий генератор, соединенный со счетным входом n-разрядного счетчика на триггерах, прямые выходы которого с 1-го по n-й разряд соединены с входами первого дешифратора, выход которого является выходом импульсов несдвигаемой последовательности, прямые выходы с m-ro по п-й разряд соединены с входами второго дешифратора, а инверсные выходы всех разрядов подключены к входам цифроаналогового преобразователя, выход

которого подключен к первому входу компаратора, второй вход которого подключен к выходу блока управления, а выход - к прямому входу элемента И, инверсный вход которого подключен к выходу второго

дешифратора, а выход - к входу одновибра- тора, выход которого является выходом импульсов сдвигаемой последовательности, отличающееся тем, что, с целью повышения надежности, оно снабжено дифференцирующей RC-цепочкой, JK-тригге- ром и инвертором, вход которого подключен к выходу компаратора, а выход через конденсатор дифференцирующей RC-цепочки, резистор которой подключен к плюсовой

клемме питания, - к установочному входу JK-триггера, тактовый вход которого подключен к выходу первого дешифратора, (п+1)-й вход которого вместе с J- и К-входа- ми JK-триггера подключен к выходу JK-триггера,

JiU,

O..J JMJLILlLiLLJL

...шпстгтп

п

in

Фиг 2.

| Устройство для цифрового управления тиристорным регулятором | 1980 |

|

SU860266A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для цифрового управления тиристорным регулятором | 1986 |

|

SU1427515A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-06-30—Публикация

1990-01-18—Подача