/

т.

п

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового управления тиристорным регулятором | 1990 |

|

SU1744774A1 |

| Устройство для цифрового управления тиристорным регулятором | 1980 |

|

SU860266A1 |

| Устройство для управления @ -фазным автономным инвертором напряжения | 1983 |

|

SU1089753A1 |

| Цифровое устройство для управления многофазным тиристорным преобразователем | 1978 |

|

SU782125A1 |

| Устройство для цифрового управления @ -фазным преобразователем | 1981 |

|

SU970626A1 |

| Устройство для управления тиристорным преобразователем | 1978 |

|

SU714619A1 |

| Устройство для цифрового управления @ -фазным широтно-импульсным преобразователем | 1983 |

|

SU1138902A1 |

| Устройство для управления тиристорным преобразователем | 1980 |

|

SU921033A1 |

| Устройство для регулирования температуры | 1986 |

|

SU1403025A1 |

| Цифровое устройство для управления тиристорным преобразователем с дискретным сдвигом импульсов | 1976 |

|

SU736341A1 |

Изобретение относится к электротехнике и может быть использовано при управлении статическими преобразователями. Цель изобретения - улучшение динамических характеристик и повышение надежности. За счет введения цифроаналогового преобразователя 6, компаратора 7, элемента 8 задержки и формирователя 9 импульсов сдвигаемой последовательности обеспечивается фиксирование минимального сдвига между сдвигаемой и несдвигаемой последовательностями. 2 ил.

в 9

I4D

Oi

ЙВ|&

СД

Фиг.1

Изобро гелше относится к электротехнике, а именно к устройствам управления полупроводниковыми преобра- з0вателям5 1с

i Цель изобретения - улучшение дц- н вд ческгос характеристик и повышение надежности; работы устройства управ- л4ния.

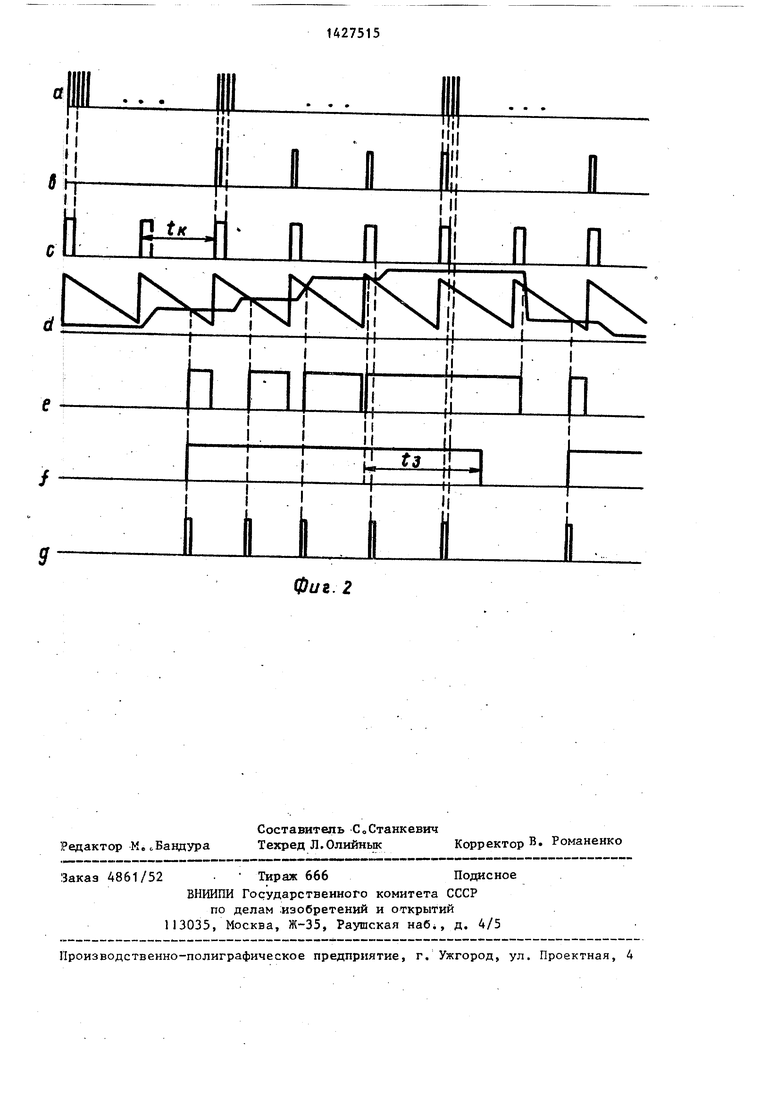

; На фиг, 1 представлена функционал нал схема устройства з равления; на фиг, 2 - временные диаграммы, поясняющие работу з стройства9

Устройство для цифрового управления тиристорным регулятором содержит задающий генератор 1, соединенньй со сметным входом п-разрядного счетчи- .к4 2 на триггерах, имегоЕЩх прямые и ищверсные выходы,, прямые выходы ко- тррого с t-ro по п-й разряд соедине- 1-й с в:-:одамн первого дешифратора 3, а тгрямые выходы с т-го по п-и разряд с;входами второго дешифратора 4, блок 5 зшравления,

I Устройство дополнительно снабжено ЦИФРоаналоговым преобразователем 6,. компаратором 7, элементом 8 задерж- Kiis формирователем 9 импульсов сдвигаемой последовательности, выполнен- mjiM на элементе И 10 и одыовибраторе Its причем входы цифроаналогового щ еобразователя поразрядно подключены к инверсньЕ входам счетчика 2, а вьЕчод подк.пгочен к первому входу компаратора 7, второй вход которого подключен к выходу блока 5 управления 5 а выход к входу элемента 8 задержки и к прямом - входу элемента И 1-0J икверсньй вход которого подклю чей к выходу второго дешифратора 4, выход элемента И 10 соединен с входом од ковибратор а 11, выход которого яззляется выходом импульсов сдвигаемо последовательности, а выход элемен™ та 8 задержки соединен с п-ь1-входом первого деишфратора 3, выход которого я:вляется вьпсодом импульсов несдви гаемой последовательности.

Устройство работает следующим образом,

С генератора 1 на счетный вход тового счтчика 2 непрерывно поступают тактовые импульсы (фиг.2а), приводящие к изменению с остояния его триггеровс, В соответствии с- состояни ем триггеров коды в виде двоичных сигналов поступают на входы первого дехикфратора 3 и второго дешифратора При наличии на п+1-входе первого де

та

щифратора 3 логической 1 на его выходе присутствуют импульсы длительностью tf (фиг. 2Ь), равной

-ПА

-П1

-г Т

2

где fj - частота импульсов генератора 1j Tj - период следования импульсов

генератора.

Период следования импульсов равен ,п . ,

гр

Tf.2

где п - число разрядов счетчика 2.

Таким образом на выходе дешифратора 3 образзтотся импульсы длительностью t , и периодом следования Т,, которые являются несдвигаемой последовательностью.

Аналогичным образом на выходе дешифратора 4 образуются импульсы длительностью периодом TK (фиг.2с)„ n-m

-ft.

Т 2

где n-m - число старших разрядов

счетчика 2, подключенных к дешифратору.

Цифре/аналоговый преобразова.тель 6 преобразует код на инверсных выходах счетчика 2 в аналоговое пилообразное напряжение (фиГо 2а), которое посту™ пает на первьш вход компаратора 7 и сравнивается там с напряжением, поступающим -на второй вход с выхода блока 5 управления. В момент равенства мгновенных значений поступающих на входы напряжений, компаратор 7 переключается и на его выходе образуется импульсное напряжение (фиг.2е), которое поступает на вход формирователя 9 импульсов сдвигаемой последо- §зательности и на вход элемента 8 за- . держки. Элемент 8 задержки вырабатывает по положительному фронту напряжения на выходе компаратора 7 импульс напряжения логической 1 длительностью tj (фиг, 2f), npn -ieM tj Т|, . т.е. длительность импульса логической 1 на выходе элемента 8 задержки всегда больше периода следования им-- пульсов на выходе дешифратора 3.

Напряжение с выхода компаратора 7 поступает на прямой вход элемента И 1 При наличии нулевого уровня напряжения на выходе дешифратора 4 на выходе элемента И 10 появляется напряжение логической 1, запускающее одновибратор 11, который на своем выходе формрует импульс сдвигаемой последователности (фиг,2g) длительностью tn,j Тг

Импульсы с выхода блока 9 сдвига- емой последовательности и с выхода дешифратора 3 несдвигаемой последовательности поступают на соответствующие тиристоры импульсного регулятора, при этом сдвигаемые импульсы ис- пользуются для включения основных тиристоров, а несдвигаемые - для включения гасящих тиристоров. Изменением уровня напряжения управления с выхода блока 5 осуществляется регулирова- ние длительности выходного импульса напряжения регулятора.

При уменьшении уровня напряжения управления с выхода блока 5 ниже минимального уровня пилообразного напря жения цифроаналогового преобразователя элемент 8 задержки обеспечивает присутствие на п+1-входе дешифратора 3 импульс логической 1 длительностью tj., формируемой после последующего спада выходного импульса компаратора 7, что обеспечивает формирование последними гасящих импульсов, чем достигается надежное выключение тиристор ного регулятора.

При уровне управляющего напряжения большем максимального уровня пилообразного напряжения на выходе компаратора 7 формируется логическая При этом после окончания времени на входе дешифратора 3 присутствует логический О, который запрещает формирование импульсов на его выходе. На тиристорный регулятор подаются только импульсы сдвиговой последова- тельности, обеспечивая режим постоянного включения, что необходимо для формирования естественной характеристики двигателя в тяговом приводе.

Для обеспечения устойчивой работы регулятора, т.е. для полного перезаряда коммутирующего конденсатора и надежного запирания тиристоров, обеспечивается фиксирование минимального

сдвига между сдвигаемой и несдвйга- емой последовательностями путем подачи на инверсный вход элемента И 10 выходного импульса дешифратора 4.

Таким образом, изобретение позволяет улучшить динамические характеристики и повысить надежность работы устройства для управления тиристор- ным импульсным регулятором.

Формула изобретения

Устройство для цифрового управления тиристорным регулятором, содержащее задающий генератор, соединенный со счетным входом п-разрядного счетчика на триггерах, имеющих прямые и инверсные выходы, прямые выходы с первого по п-й разряд соединены с входами первого дешифратора, а прямые выходы с га-го по п-й разряд соединены с входами второго дешифратора, блок упраапения, отличающееся тем, что, с целью улучшения динамических характеристик и повышения надежности работы,устройство снабжено цифроаналоговым преобразователем, компаратором, элементом задержки, формирователем импульсов сдвигаемой последовательности, выполненным на элементе И и одновибраторе, причем входы цифроаналогового преобразователя поразрядно подключены к инверсным выходам счетчика, а выход подключен к первому входу компаратора, второй вход которого подключен к выходу блока управления, а выход - к входу элемента задержки и к прямому входу элемента И, инверсный вход которого подключен к выходу второго дешифратора, выход элемента И соединен с входом одновибратора, выход которого является выходом импульсов сдвигаемой последовательности, а выход элемента задержки соединен Q п+1-входом первого дешифратора, выход которого является выходом импульсов несдвигаемой последовательности.

if

Фиг 2

if

li II

|l

It

13

th

| Устройство для цифрового управления тиристорным импульсным преобразователем (его варианты) | 1979 |

|

SU858202A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-09-30—Публикация

1986-01-13—Подача