Изобретение относится к электротехнике и может быть использовано для управления многофазным айтономным инвертором напряжения. Известно устройство для управления Автономными инверторами, содержащее задающий генератор, делитель частоты, пересчетное кольцо, одновиб ратор, омический делитель напряжения полупроводниковые реле, дешифратор, полупроводниковые ключи. Устройство позволяет формировать выходное напря жение автономного инвертора, состоящее из импульсов равной длительности, и осуществлять его широтное регулирование путем изменения длительноотей импульсов на равные интервалы С 1 . Недостатком устройства является значительное искажение формы выходно го напряжения автономного инвертора, что вызывает необходимость установки на его выходе фильтр-устройств значительной мощности. Наиболее близким по технической сущности к предлагаемому является устройство управления тиристорным преобразователем, содержащее задающий генератор, сдвигающее устройство .дешифратор, выходные каскады сдвигае мой и несдвигаемой последовательности импульсов,два счетчика,причем с целью управления m-фазным преобразователем каждый последующий триггер в счетчиках после первого соединены соответственно с прямым или инверсным выходом триггеров предыдущего разряда. Выход ьое фазное напряжение преобразователя представляет собой последовательность одноуровневых импульсов равной длительности. Регулирование выходного напряжения инвертора осуществляет ся широтным способом путем изменения длительностей формирующих выходные кривые импульсов на равные интервалы 12:1, . Недостатком указанного устройства гвляется плохой гармонический состав выходного напряжения инвертора, кото рое содержит интенсивные гармоники HHSKOto порядка, что приводит к росту мощности выходных фильтров и к ухудшению технико-экономических показателей преобразователя. Цель изобретения - улучшение гармонического состава выходного регулируемого напряжения m-фазного авто номного инвертора напряжения. Поставленная цель достигается тем что устройство. Содержащее задающий генератор, одним выходом соединенный с первым п-разрядным счетчиком на триггерах, который 2п логическими вы ходами подключен к одним входам основного дешифратора, а прямым выходом (п-11-го триггера - с выходным каска дом несдвигаемой последовательности, выходной каскад сдвигаемой последова тельноСти импульсов, второй счетчик, логическими выходами соединенный с другими входами основного дешифратора, фаэосдвигающий блок, содержащий элементы И-НЕ, ИЛИ, два элемента И, причем первый выход основного дешифратора подключен к одному входу элемента И-НЕ, другой вход которого соединен с первым выходом блока управления , второй выход которого соединен с одним входом первого элемента И, к другим входам которого подключены второй выход задающего генератора, второй вход основного дешифратора, выход элемента И-НЕ, соединенный с одним входом второго элемента И, другой вход которого подключен к первому выходу задающего генератора, а выходы упомянутых элементов И соединены с входами элемента ИЛИ, выходом подключенного к входу второго счетчика, снабженокольцевым распределителем несдвигаемых последовательностей ,m распределителями сдвигаемых последовательностей на элементах И и элементе ИЛИ, триггером, дополнительным дешифратором на элементах И, причем кольцевой распределитель несдвигаемых последовательностей, содержащий i триггеров, входом соединен с прямым выходом ц-го триггера первого счетчика и своими i-ло- гическими выходами подключен к одним входам элементов И m распределителей сдвигаемой последовательности, а другие входы упомянутых элементов И соединены попарно и подключены к выходам элементов И дополнительного дешифратора, причем входы первого элемента И дополнительного дешифратора подключены к прямому выходу (ri-1)го тригтера и инверсным выходам (и-2)го и (ti-31-го триггеров второго счетчика, а входы второго элемента И к инверсным выходам (n-l)-ro и(п-2)го триггеров и прямому выходу(п-З)го триггера второго счетчика, кроме того, выходы упомянутых i элементов И каждого из распределителей сдвигаемой последовательности подключены к входу логического элемента ИЛИ, который соединен с первыми входами двух дополнительных элементов И, выходы которых подключены к выходному каскаду сдвигаемой последовательности импульсов, вторые входы элементов И подключены к прямому и инверсному выходам триггера, счетный вход которого соединен с первым логическим выходом кольцевого распределителя несдвигаемой последовательности. На фиг. 1 изображена структурная схема устройства; на фиг. 2 - времен ные диаграммы, характеризующие работу отдельных узлов устройства при на фиг. 3 - структурная схема устройства с конкретной реализацией фазосдвигающего блока б.

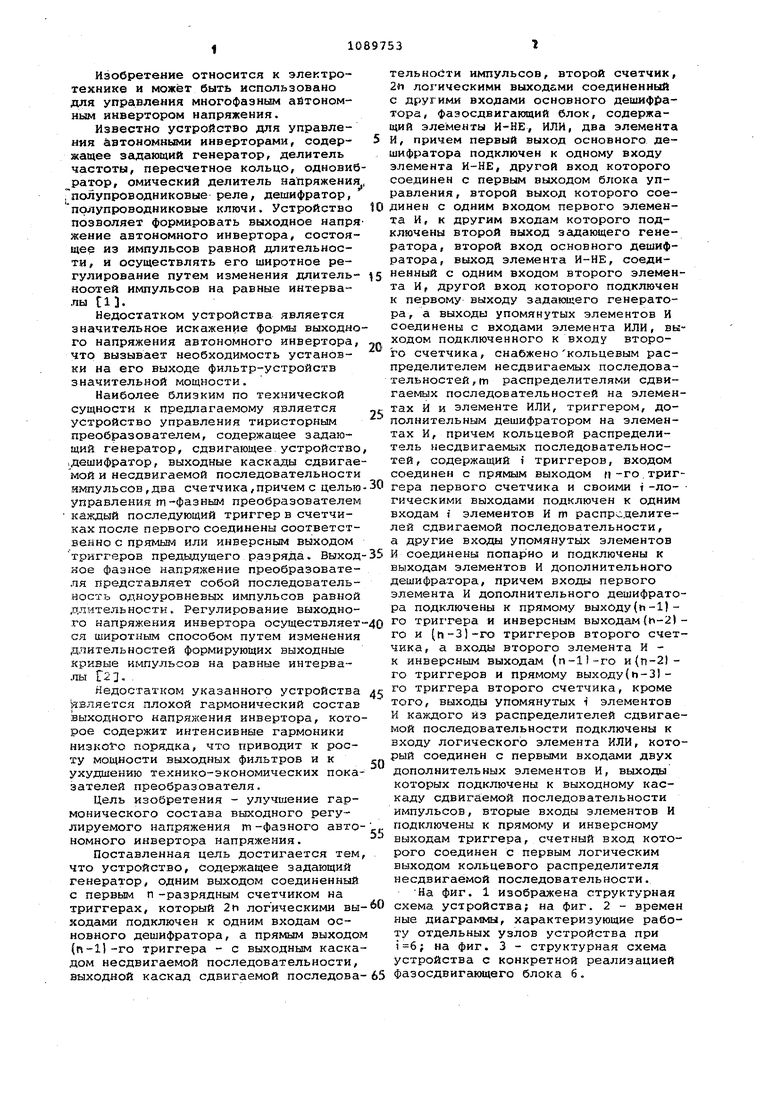

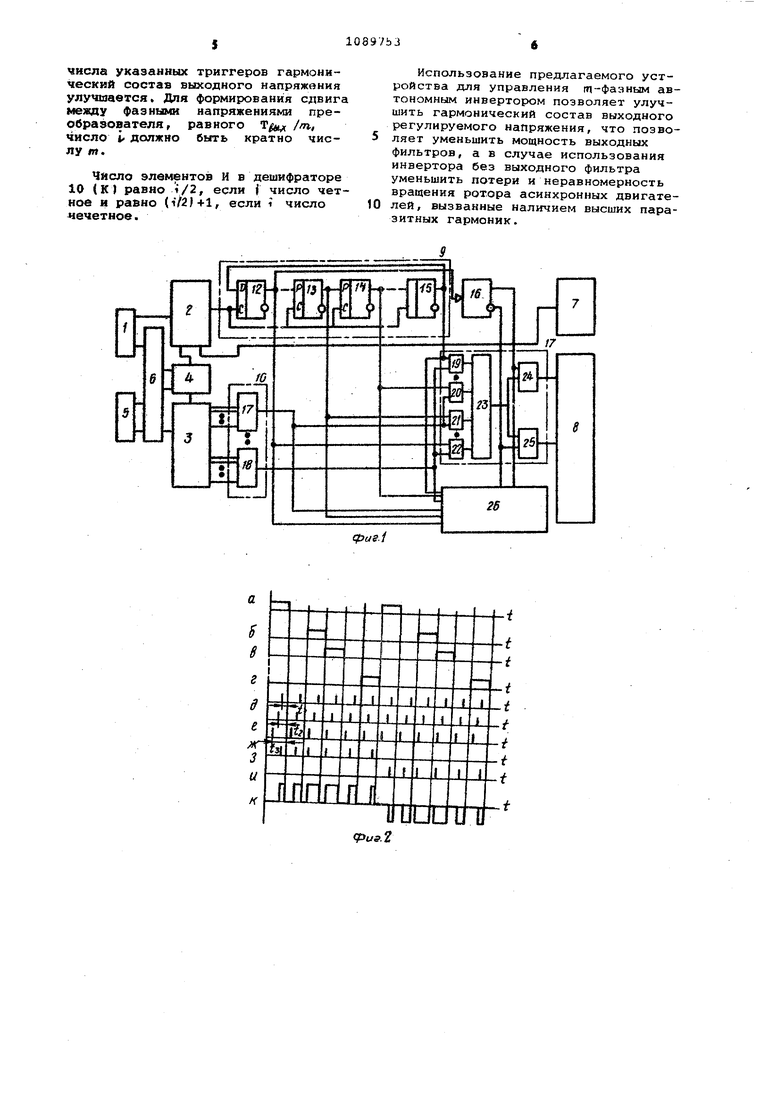

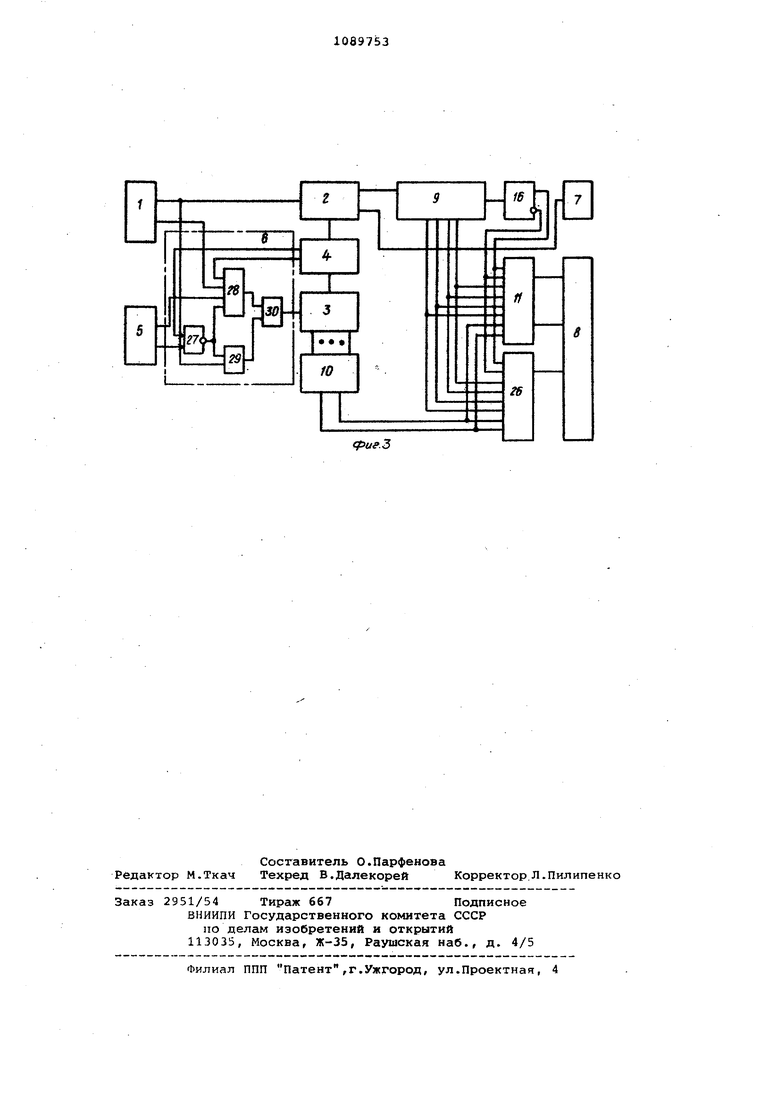

Структурная схема устройства (фиг. 1)содержит задающий генератор 1, соединенный первым выходом с входом первого двоичного п -разрядного счетчика 2, имеющего 2 п логических выходов (п прямых и п инверсных;, с помощью которых он подсоединен к первому дешифратору 4. Кроме того, второй выход задающего генератора 1 соединен с фазосдвигающим блоком 6, причем каскады несдвигаемой последовательности и сдвигаемой последовательностей 7 и 8, распределитель несдвигаемой последовательности 9, дополнительный дешифратор 10 подключены к распределителю сдвигаемой последовательности 11. Распределитель несдвигаемой последовательности 9 состоит из триггеров 12-15 и подключен к дополнительному триггеру 16.Дополнительный дешифратор 10 состоит из элементов И 17 и 18. Распределитель 11 состоит из элементов И 19-22, подключенных через элемент ИЛИ 23 к одним входам элементов И 24 и 25, к другим входам которых подключен распределитель сдвигаемой последовательности 26. Фазосдвигающий блок 6 состоит из элементов И-НЕ 27, элементов И 28 и 29, элемента ИЛИ 30.

Устройство работает следующим образом.

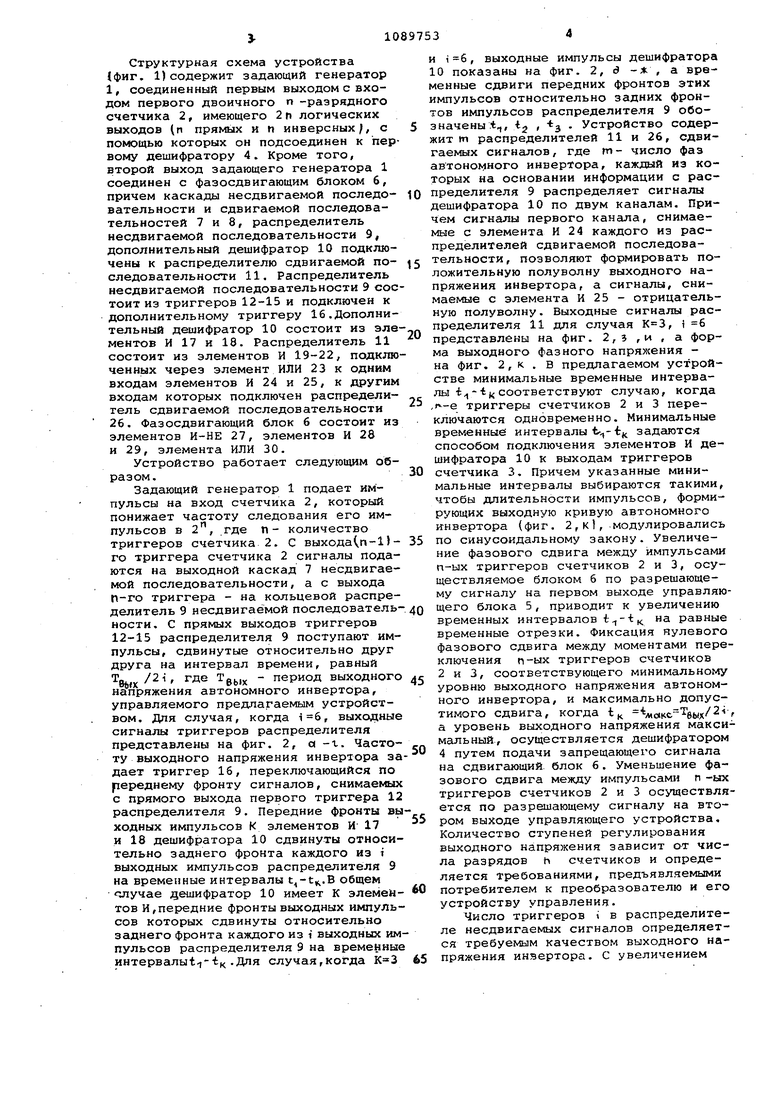

Задающий генератор 1 подает импульсы на вход счетчика 2, который понижает частоту следования его импульсов в 2, где п- количество триггеров счетчика 2. С выхода(п-1)го триггера счетчика 2 сигналы подаются на выходной каскад 7 несдвигаемой последовательности, а с выхода П-ГО триггера - на кольцевой распределитель 9 несдвигаёмой последовательности. С прямых выходов триггеров 12-15 распределителя 9 поступают импульсы, сдвинутые относительно друг друга на интервал времени, равный , где Tg, - период выходного напряжения автономного инвертора, управляемого предлагаемым устройством. Для случая, когда , выходные сигналы триггеров распределителя представлены на фиг. 2, а -г. Частоту выходного напряжения инвертора задает триггер 16, переключающийся по ререднему фронту сигналов, снимаемых с прямого выхода первого триггера 12 распределителя 9. Передние фронты выходных импульсов К элементов И 17 и 18 дешифратора 10 сдвинуты относительно заднего фронта каждого из i выходных импульсов распределителя 9 на временные интервалы ц-t.B общем «гпучае дешифратор 10 имеет К элементов И,передние фронты выходных импульсов которых сдвинуты относительно заднего фронта каждого из i выходных импульсов распределителя на временные интервалы -t.Для случая,когда

и , выходные импульсы дешифратора 10 показаны на фиг. 2, d - , а временные сдвиги передних фронтов этих импульсов относительно задних фронтов импульсов распределителя 9 обозначены , ij , з . Устройство содержит hi распределителей 11 и 26, сдвигаемых сигналов, где т- число фаз автономного инвертора, каждый из которых на основании информации с распределителя 9 распределяет сигналы

0 дешифратора 10 по двум каналам. Причем сигналы первого канала, снимаемые с элемента И 24 каждого из распределителей сдвигаемой последовательности, позволяют формировать по5ложительную полуволну выходного напряжения инвертора, а сигналы, снимаемые с элемента И 25 - отрицательную полуволну. Выходные сигналы распределителя 11 для случая , 6

0 представлены на фиг. 2,5 ,и , а форма выходного фазного напряжения на фиг. 2,к . в предлагаемом устройстве минимальные временные интервалы i -1к соответствуют случаю, когда

5 ,(-е триггеры счетчиков 2 и 3 переключаются одновременно. Минимальные временные интервалы tvi-tj задаются способом подключения элементов И дешифратора 10 к выходам триггеров

0 счетчика 3. Причем указанные минимальные интервалы выбираются такими, чтобы длительности импульсов, формирующих выходную кривую автономного и-нвертора (фиг. 2, к 1, модулировались

5 по синусоидальному закону. Увеличение фазового сдвига между импульсами п-ых триггеров счетчиков 2 и 3, осуществляемое блоком 6 по разрешающему сигналу на первом выходе управляющего блока 5, приводит к увеличению

0 временных интервалов на равные временные отрезки. Фиксация нулевого фазового сдвига между моментами переключения п-ых триггеров счетчиков 2 и 3, соответствующего минимальному

5 уровню выходного напряжения автономного инвертора, и максимально допустимого сдвига, когда t, л(с«кй бых а уровень выходного напряжения максимальный, осуществляется дешифратором

0 4 путем подачи запрещающего сигнала на сдвигающий блок 6. Уменьшение фазового сдвига между импульсами п-ых триггеров счетчиков 2 и 3 осуществляется по разрешающему сигналу на вто5ром выходе управляющего устройства. Количество ступеней регулирования выходного напряжения зависит ат числа разрядов h счетчиков и определяется Требованиями, предъявляемыми

0 потребителем к преобразователю и его устройству управления.

Число триггеров i в распределителе несдвигаемых сигналов определяется требуемым качеством выходного напряжения инвертора. С увеличением

5

числа указанных триггеров гармонический состав В1лходного напряжения улучшается. Для формирования сдвига между фазныАш напряжениякш преобразователя, равного ff /т., число 1 должно быть кратно числу т.

Число элементов И в дешифраторе 10 (К) равно , если j число четное и равно (1/21+1, если i число чечетное.

Использование предлагаемого устройства для управления гп-фазным авTOHOMHEJM инвертором позволяет улучшить гармонический состав выходного регулируемого напряжения, что позволяет уменьшить мощность выходных фильтров, а в случае использования инвертора без выходного фильтра уменьшить потери и неравномерность вращения ротора асинхронных двигателей, вызванные наличием высших паразитных гармоник.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления тиристорным преобразователем | 1980 |

|

SU921033A1 |

| Устройство для управления тиристорным преобразователем | 1978 |

|

SU714619A1 |

| Устройство для цифрового управления тиристорным регулятором | 1990 |

|

SU1744774A1 |

| Устройство для цифрового управления тиристорным регулятором | 1986 |

|

SU1427515A1 |

| Одноканальное устройство для управления -фазным преобразователем | 1978 |

|

SU775855A1 |

| Преобразователь частоты | 1981 |

|

SU1069104A1 |

| Устройство для цифрового управления @ -фазным преобразователем | 1981 |

|

SU970626A1 |

| Цифровое устройство для управления инвертором с квазисинусоидальным напряжением | 1983 |

|

SU1089756A1 |

| Устройство для цифрового управления тиристорным регулятором | 1980 |

|

SU860266A1 |

| Многоканальный полосовой цифровой фильтр | 1983 |

|

SU1092706A1 |

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ т-ФАЗНЬМ АВТОНОМНЫМ ИНВЕРТОРОМ НАПРЯЖЕНИЯ, содержащее задающий генератор, одним выходом соединенный с первьм Р-разрядным счетчиком на триггерах, который 2п логическими выходами подключен к одним входам основного дешифратора, прямым выходом (п-1|-го триггера - с вцходным каскадом несдвигаемой последовательности, выходной каскад сдвигаемой последовательности импульсов, второй счетчик 2п логическими выходами соединенный с другими входами основного дешифратора, фазосдвигающий блок/ содержащий элементы И-НЕ, ИЛИ, два элемента И, причем первый выход основного дешифратора подключен к одному входу элемента И-НЕ, другой вход которого соединен с первым выходом блока управления, второй выход которого соединен с одним входом первого элемента И, к другим входам которого подключены второй выход задающего генератора, второй вход основного дешифратора, выход элемента И-НЕ, соединенный с одним входом второго элемента И, другой вход которого подключен к перво му выходу задающего генератора, вы±Г :± ходы упомянутых элементов И соединены с входсьми элемента ИЛИ, выходом подключенного к входу второго счетчика,отличающееся тем, что, с целью улучшения гармонического состава выходного напряжения tn -фазного автономного инвертора напряжения, оно снабжено кольцевым распределителем несдвигаемых последовательностей m распределителями сдвигаемых после довательностей на элементах И и элементе ИЛИ, триггером, дополнительным дешифратором на элементах И, причем кольцевой распределитель несдвигаемых последовательностей, содержащий i триггеров, входом соединен с прямым выходом п-го триггера первого С 9 счетчика и своими i-логическими выходалш подключен к одним входам (Л i элементов И m распределителей сдан гаемой последовательности, а другие входы упомянутых элементов И соединены попарно и подключены к выходам элементов И дополнительного дешифратора, причем входы первого элемен- { та И дополнительного дешифратора под ключены к прямому выходу (n-l)-ro | триггера и инверсным выходам ( го и (п-З)-го триггеров второго счет чика, а входы второго элемента И со к инверснь выходам (h -1 1-го и (п-2) го триггеров и прямому выходу (п-3)го триггера второго счетчика, выходы О упомянутых j элементов И каждого из СО распределителей сдвигаемой последовательности подключены к входу элемента ИЛИ, который соединен с первыми входами двух элементов И, выходы которых подключены к выходному каскаду сдвигаемой последовательности импульсов, вторые входы элементов И подключены к прямому и инверсному вы ходам триггера, счетный вход которого соединен с первым логическим выходом кольцевого распределителя несдвигаемой последовательности.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Калашников Б.Е | |||

| и др | |||

| Систеfej управления автономными инверторами | |||

| М., Энергия, 1974 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления тиристорным преобразователем | 1978 |

|

SU714619A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1984-04-30—Публикация

1983-02-08—Подача