Изобретение относится к полупроводниковой электронике, а более конкретно к полупроводниковым интегральным схемам на основе биполярных транзисторов.

Известна интегральная схема, включающая выполненные на полупроводниковой подложке в эпитаксиальном слое п-типа Первый и второй транзисторы, диод Шоттки и резистор, причем катод диода Шоттки соединен с входом схемы, а анод подключен к базе первого транзистора, соединенной с шиной питания через резистор, эмиттер первого транзистора соединен с базой второго транзистора, эмиттер которого соединен с общей шиной, а коллектор образует выход.

Недостатком известного решения является пониженная помехозащищенность, обусловленная пониженным порогом переключения схемы.

Известна интегральная схема, включающая первый, второй и третий транзисторы, диод Шоттки и резистор и выполненная на

полупроводниковой подложке. Катод диода Шоттки соединен с входом схемы, а анод - с базой первого транзистора, соединенной с шиной питания. Эмиттер первого транзистора соединен с базой второго транзистора через дополнительные первый и второй резисторы, эмиттер второго транзистора соединен через дополнительные третий и четвертый резисторы с базой третьего транзистора, а эмиттер третьего транзистора соединен с общей шиной.

Недостатком известного решения является необходимость в большом количестве дополнительных схемных элементов (резисторов) для обеспечения управления порогом переключения схемы.

Наиболее близкой к предлагаемой является интегральная схема, содержащая первый транзистор, база которого через первый резистор соединена с шиной питания, а с входом схемы - через диод, включенный в направлении к входу схемы. Коллектор первого транзистора через втоXI

4 О СО

ю

рой резистор соединен с шиной питания, а эмиттер соединен с базой второго транзистора. Эмиттер второго транзистора соединен с базой третьего транзистора, эмиттер которого соединен с общей шиной. Интегральная схема выполнена на полупроводниковой подложке р-типа проводимости в отделенных друг от друга изолирующими областями участках эпитаксиального слоя а-типа проводимости со скрытыми слоями п+-типа проводимости. В участках эпитаксиального слоя сформированы области активной и пассивной базы проводимости и эмиттера п -типа проводимости первого, второго и третьего транзисторов.

Недостатком.известного решения является невозможность управления порогом переключения схемы из-за фиксированных значений прямых падений напряжения диода и переходов база -- эмиттер первого, второго и третьего транзисторов.

Целью изобретения является обеспечение возможности-управления порогом переключения и повышение помехоустойчивости известной интегральной схемы путем изменения значений прямого падения напряжения переходов база-эмиттер транзисторов.

Указанная цель достигается тем, что в интегральной схеме при формировании области р+-базы с концентрацией примеси 5х хЮ18 N 1020см 3 внедрением примеси р-типа перед формированием эмиттера осуществляется ее одновременное внедрение под область эмиттера по меньшей мере одного из транзисторов на глубину превышающую глубину эмиттера.

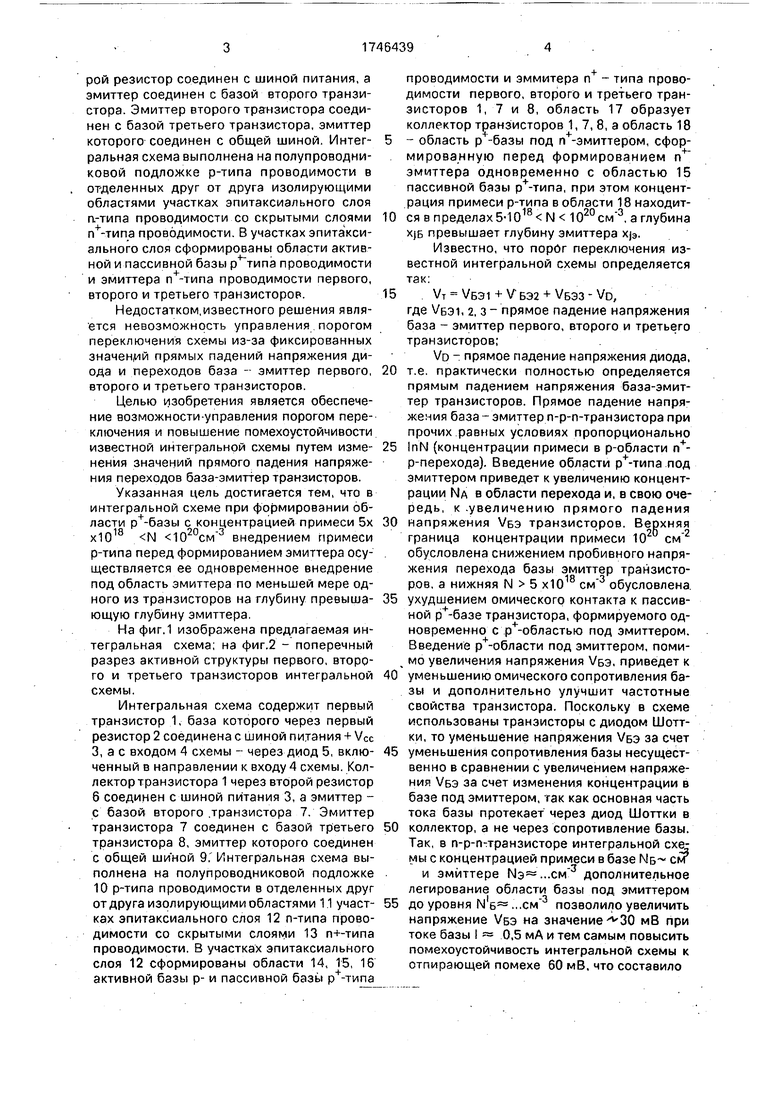

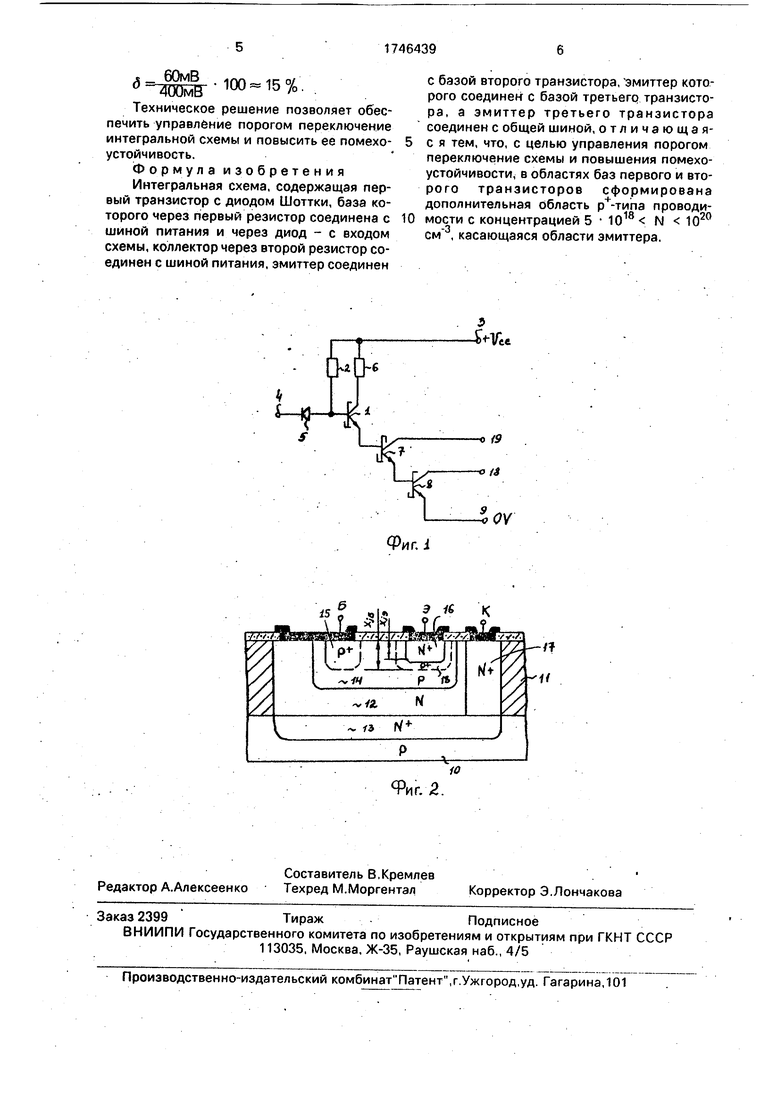

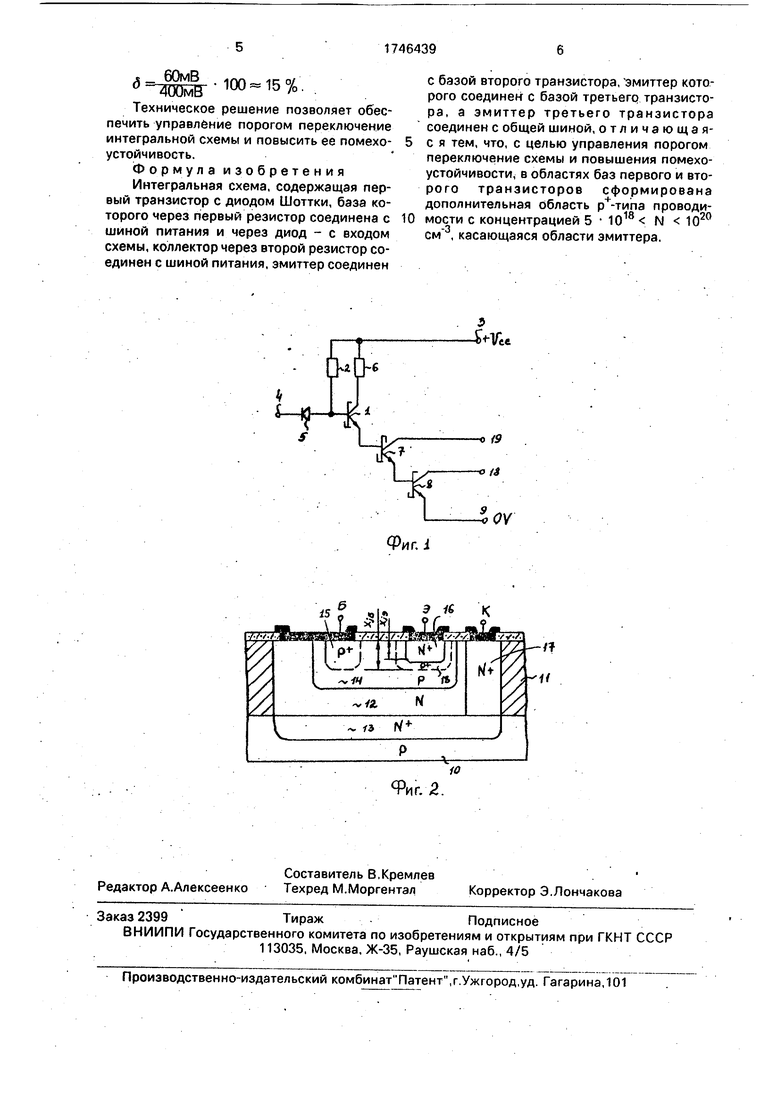

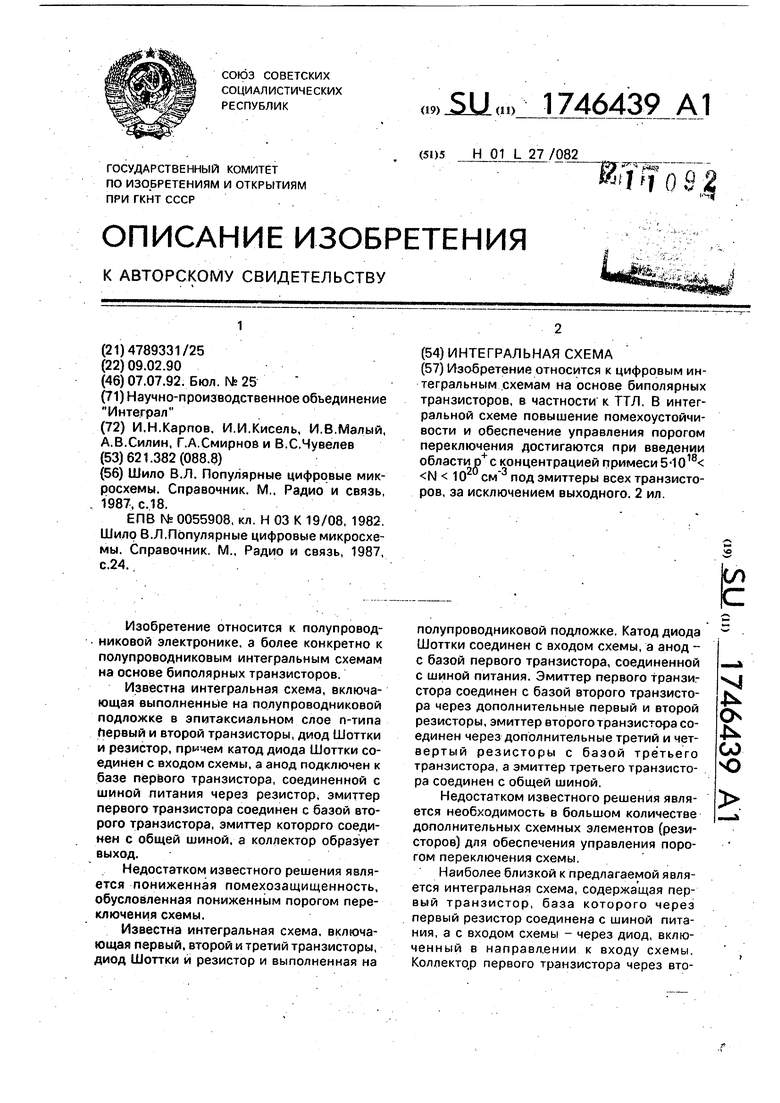

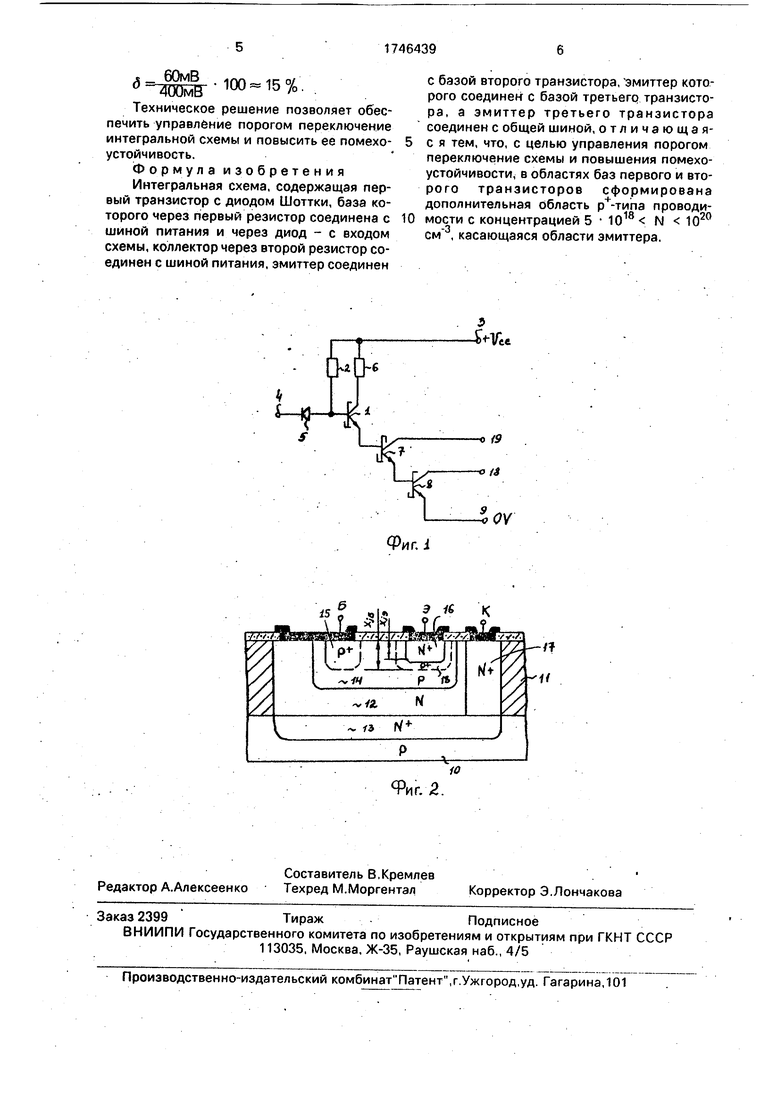

На фиг.1 изображена предлагаемая интегральная схема; на фиг.2 - поперечный разрез активной структуры первого, второго и третьего транзисторов интегральной схемы.

Интегральная схема содержит первый транзистор 1, база которого через первый резистор 2 соединена с шиной питания + VCc 3, а с входом 4 схемы - через диод 5, включенный в направлении к входу 4 схемы. Коллектор транзистора 1 через второй резистор 6 соединен с шиной питания 3, а эмиттер - С базой второго .транзистора 7. Эмиттер транзистора 7 соединен с базой третьего транзистора 8, эмиттер которого соединен с общей шиной 9, Интегральная схема выполнена на полупроводниковой подложке 10 р-типа проводимости в отделенных друг от друга изолирующими областями 11 участках эпитаксиального слоя 12 n-типа проводимости со скрытыми слоями 13 п+-типа проводимости. В участках эпитаксиального слоя 12 сформированы области 14, 15, 16 активной базы р- и пассивной базы р+-типа

проводимости и эммитера п - типа проводимости первого, второго и третьего транзисторов 1, 7 и 8, область 17 образует коллектор транзисторов 1, 7, 8, а область 18

- область р+-базы под гЛ-эмиттером, сформированную перед формированием п эмиттера одновременно с областью 15 пассивной базы р -типа, при этом концентрация примеси р-типа в области 18 находится в пределах 5-Ю18 N 1020 , а глубина XJB превышает глубину эмиттера х|Э.

Известно, что порог переключения известной интегральной схемы определяется так:

VT УБЭ1 + V БЭ2 + V533 - VD,

где VBSI, 2, з - прямое падение напряжения база - эмиттер первого, второго и третьего транзисторов;

VD - прямое падение напряжения диода,

т.е. практически полностью определяется прямым падением напряжения база-эмиттер транзисторов. Прямое падение напряжения база - эмиттер n-p-n-транзистора при прочих равных условиях пропорционально

InN (концентрации примеси в р-области п+- р-перехода). Введение области р+-типа под эмиттером приведет к увеличению концентрации NA в области перехода и, в свою очередь, к .увеличению прямого падения

напряжения УБЭ транзисторов. Верхняя граница концентрации примеси 10 обусловлена снижением пробивного напряжения перехода базы эмиттер транзисторов, а нижняя N 5 хЮ18 обусловлена

ухудшением омического контакта к пассивной р -базе транзистора, формируемого одновременно с р -областью под эмиттером. Введение р+-области под эмиттером, поми- ч мо увеличения напряжения /БЭ. приведет к

уменьшению омического сопротивления базы и дополнительно улучшит частотные свойства транзистора. Поскольку в схеме использованы транзисторы с диодом Шотт- ки, то уменьшение напряжения /БЭ за счет

уменьшения сопротивления базы несущественно в сравнении с увеличением напряжения УБЭ за счет изменения концентрации в базе под эмиттером, так как основная часть тока базы протекает через диод Шоттки в

коллектор, а не через сопротивление базы. Так, в n-p-n-транзисторе интегральной схемы с концентрацией примеси в базе NB см и эмиттере N3... дополнительное легирование области базы под эмиттером

до уровня М Б ... позволило увеличить напряжение УБЭ на значение 30 мВ при токе базы I 0,5 мА и тем самым повысить помехоустойчивость интегральной схемы к отпирающей помехе 60 мВ, что составило

А - ffjyB 1ПП « 1R °/

0 400мВ .

Техническое решение позволяет обеспечить управление порогом переключение интегральной схемы и повысить ее помехоустойчивость.

Формула изобретения

Интегральная схема, содержащая первый транзистор с диодом Шоттки, база которого через первый резистор соединена с шиной питания и через диод - с входом схемы, коллектор через второй резистор соединен с шиной питания, эмиттер соединен

с базой второго транзистора, эмиттер которого соединен с базой третьего транзистора, а эмиттер третьего транзистора соединен с общей шиной, отличающая- с я тем, что, с целью управления порогом переключение схемы и повышения помехоустойчивости, в областях баз первого и вто- рого транзисторов сформирована дополнительная область р -типа проводимости с концентрацией 5 1018 N 1020 , касающаяся области эмиттера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1984 |

|

SU1173551A1 |

| ВХОДНОЙ ЭЛЕМЕНТ ПЛАНАРНО-ЭПИТАКСИАЛЬНОЙ ИНТЕГРАЛЬНОЙ СХЕМЫ | 1990 |

|

SU1759197A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| ИНТЕГРАЛЬНАЯ СХЕМА | 1992 |

|

RU2078390C1 |

| Логический элемент И-НЕ ИШЛ | 1985 |

|

SU1262720A1 |

| D-триггер | 1985 |

|

SU1332380A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР | 2005 |

|

RU2282233C1 |

| ПОЛУПРОВОДНИКОВЫЙ ПРИБОР С СИММЕТРИЧНОЙ ВОЛЬТАМПЕРНОЙ ХАРАКТЕРИСТИКОЙ | 1993 |

|

RU2064716C1 |

| @ -Триггер | 1984 |

|

SU1188862A1 |

Изобретение относится к цифровым интегральным схемам на основе биполярных транзисторов, в частности к ТТЛ. В интегральной схеме повышение помехоустойчивости и обеспечение управления порогом переключения достигаются при введении области р+с концентрацией примеси 5-1018 N 10 под эмиттеры всех транзисторов, за исключением выходного. 2 ил сл с

Фиг. 4

| Шило В.Л | |||

| Популярные цифровые микросхемы | |||

| Справочник | |||

| М. | |||

| Радио и связь, 1987, с | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| Способ и устройство комбинированного производства желтого фосфора и силового газа | 1938 |

|

SU55908A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шило В.Л.Популярные цифровые микросхемы | |||

| Справочник | |||

| М., Радио и связь, 1987, с.24. | |||

Авторы

Даты

1992-07-07—Публикация

1990-02-09—Подача