Изобретение относится к импульсной технике и предназначено для использования в интегральных логических цифровых микросхемах.

Цель изобретения - уменьшение потребляемой мощности и увеличение быстродействия путем уменьшения напряжения питания и логического перепада.

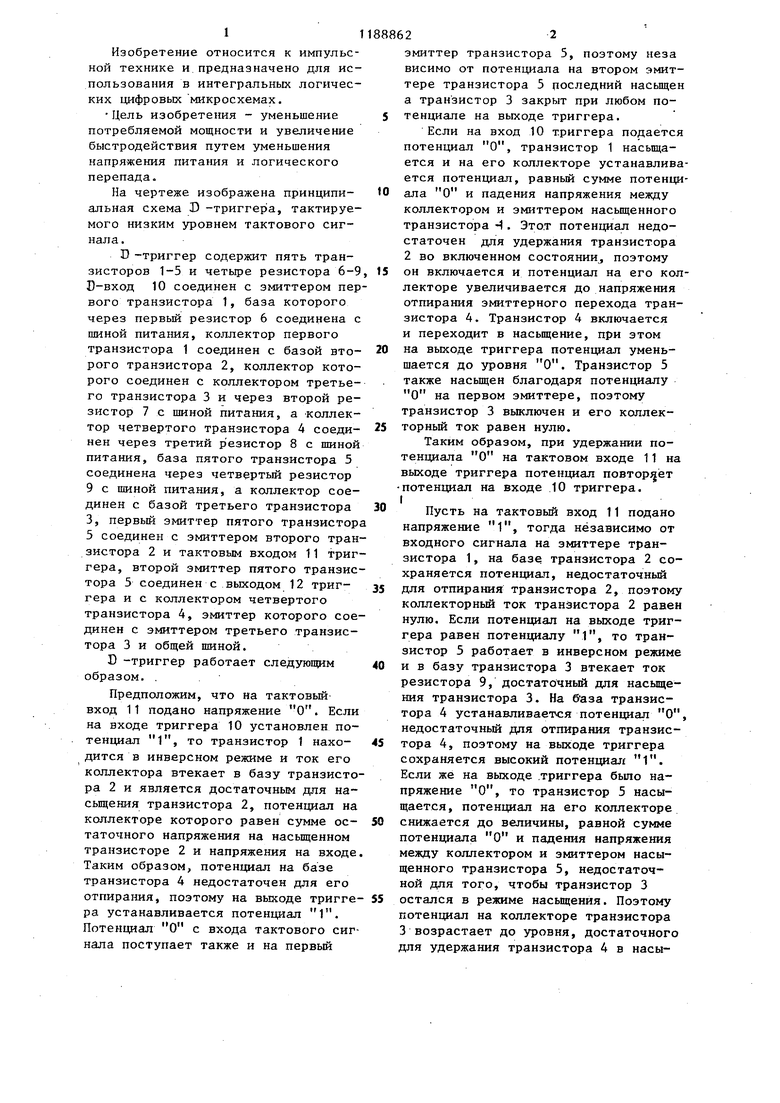

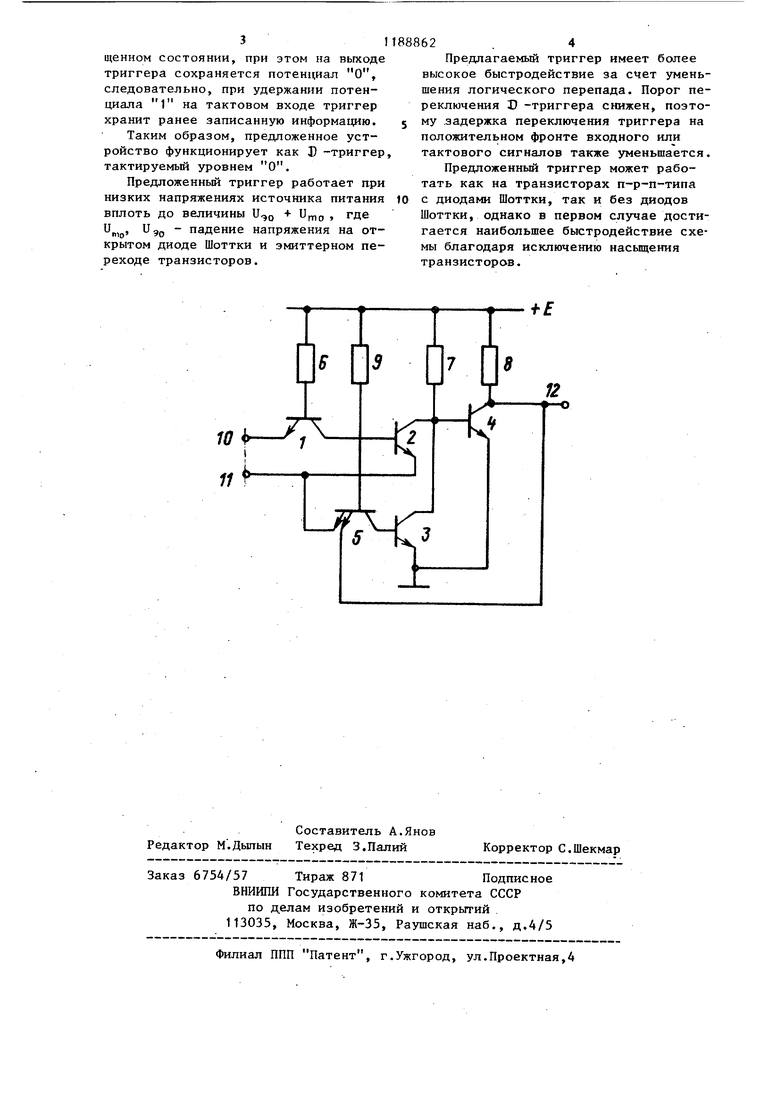

На чертеже изображена принципиальная схема D -триггера, тактируемого низким уровнем тактового сигнала .

D -триггер содержит пять транзисторов 1-5 и четыре резистора 6-9 D-вход 10 соединен с эмиттером первого транзистора 1, база которого через первый резистор 6 соединена с шиной питания, коллектор первого транзистора 1 соединен с базой второго транзистора 2, коллектор которого соединен с коллектором третьего транзистора 3 и через второй резистор 7 с шиной питания, а -коллектор четвертого транзистора 4 соединен через третий резистор 8 с шиной питания, база пятого транзистора 5 соединена через четвертый резистор 9 с шиной питания, а коллектор соединен с базой третьего транзистора 3, первый эмиттер пятого транзистора 5 соединен с эмиттером второго транзистора 2 и тактовым входом 11 триггера, второй эмиттер пятого транзистора 5 соединен с выходом 12 триггера и с коллектором четвертого транзистора 4, эмиттер которого соединен с эмиттером третьего транзистора 3 и общей шиной.

D -триггер работает следующим образом. .

Предположим, что на тактовыйвход 11 подано напряжение О. Если на входе триггера 10 установлен потенциал 1, то транзистор 1 находится в инверсном режиме и ток его коллектора втекает в базу транзистора 2 и является достаточным для насьпдения транзистора 2, потенциал на коллекторе которого равен сумме остаточного напряжения на насьщенном транзисторе 2 и напряжения на входе Таким образом, потенциал на базе транзистора 4 недостаточен для его отпирания, поэтому на выходе триггера устанавливается потенциал 1. Потенциал О с входа тактового сигнала поступает также и на первый

эмиттер транзистора 5, поэтому иеза висимо от потенциала на втором эмиттере транзистора 5 последний насыщен а транзистор 3 закрыт при любом потенциале на выходе триггера.

Если на вход 10 триггера подается потенциал О, транзистор 1 насьпцается и на его коллекторе устанавливается потенциал, равный сумме потенциала О и падения напряжения между коллектором и эмиттером насьш1енного транзистора Ч. Этот потенциал недостаточен для удержания транзистора

2во включенном состоянии, поэтому он включается и потенциал на его коллекторе увеличивается до напряжения отпирания эмиттерного перехода транзистора 4. Транзистор 4 включается

и переходит в насыщение, при этом на выходе триггера потенциал уменьшается до уровня О. Транзистор 5 также насыщен благодаря потенциалу О на первом эмиттере, поэтому транзистор 3 вьключен и его коллекторный ток равен нулю.

Таким образом, при удержании потенциала О на тактовом входе 11 на выходе триггера потенциал повторяет потенциал на входе 10 триггера. I

Пусть на тактовый вход 11 подано

напряжение 1, тогда независимо от входного сигнала на эмиттере транзистора 1, на баз транзистора 2 сохраняется потенциал, недостаточный для отпирания транзистора 2, поэтому коллекторный ток транзистора 2 ранен нулю. Если потенциал на выходе триггера равен потенциалу 1, то транзистор 5 работает в инверсном режиме и в базу транзистора 3 втекает ток резистора 9, достаточный для насыщения транзистора 3. На база транзистора 4 устанавливается потенциал О недостаточный для отпирания транзистора 4, поэтому на выходе триггера сохраняется высокий потенциагг 1. Если же на выходе .триггера было напряжение О, то транзистор 5 насыщается, потенциал на его коллекторе снижается до величины, равной сумме потенциала О и падения напряжения между коллектором и эмиттером насыщенного транзистора 5, недостаточной для того, чтобы транзистор 3 остался в режиме насыщения. Поэтому потенциал на коллекторе транзистора

3возрастает до уровня, достаточного для удержания транзистора 4 в насыщенном состоянии, при этом на выходе триггера сохраняется потенциал О, следовательно, при удержании потенциала 1 на тактовом входе триггер хранит ранее записанную информацию.

Таким образом, предложенное устройство функционирует как D -триггер тактируемый уровнем О.

Предложенный триггер работает при низких напряжениях источника питания

величины + U

вплоть до

то

и„., и на от14 - 90 падение напряжения крытом диоде Шоттки и эмиттерном переходе транзисторов.

Предлагаемый триггер имеет более высокое быстродействие за счет уменьшения логического перепада. Порог переключения D -триггера снижен, поэтому задержка переключения триггера на положительном фронте входного или тактового сигналов также уменьшается.

Предложенный триггер может работать как на транзисторах п-р-п-типа с диодами Шоттки, так и без диодов Шоттки, однако в первом случае достигдегается наибольшее быстродействие схемы благодаря исключению насьш1ения транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| @ -Триггер | 1984 |

|

SU1174987A1 |

| D-триггер | 1985 |

|

SU1332380A1 |

| @ -Триггер (его варианты) | 1984 |

|

SU1188861A1 |

| JK-триггер | 1989 |

|

SU1713091A1 |

| Д-триггер | 1984 |

|

SU1221714A1 |

| СХЕМА ЗАЩИТЫ КЛЮЧЕВОГО ТРАНЗИСТОРА | 2003 |

|

RU2245602C1 |

| Триггер | 1983 |

|

SU1150734A1 |

| Д-триггер | 1988 |

|

SU1562962A1 |

| Логическое устройство | 1984 |

|

SU1213521A1 |

| Устройство согласования | 1986 |

|

SU1383483A1 |

D - ТРИГГЕР, содержащий четыре транзистора и четыре резистора, D -вход Л -триггера соединен с эмиттером первого транзистора, база которого через первый резистор соединена с шиной питания, коллектор первого транзистора соединен с базой второго транзистора, коллектор второго транзистора соединен с коллектором третьего транзистора и через второй резистор с шиной питания, а коллектор четвертого транзистора соединен через третий резистор с шиной питания, отличающий.с я тем, что, с целью уменьшения потребляемой мощности и увеличения быстродействия, в него введен пятый транзистор, база которого соединена через четвертый резистор с шиной питания, а коллектор соединен с. с базой третьего транзистора, перS вый эмиттер пятого транзистора сое(Л динен с эмиттером второго транзистора и тактовым входом Э -триггера, второй эмиттер пятого транзистора соединен с выходом -триггера и с коллектором четвертого транзистора, эмиттер которого соединен с эмиттером третьего транзистора и общей шиной.

| Алексеенко А.Г., Шагурин И.И | |||

| Микросхемотехника | |||

| - М.: Радио и связь, 1982, с.178 | |||

| f Березенко А.И., Корягин Л.Н., Назарьян А.Р | |||

| Микропроцессорные комплекты повьппенного быстродействия | |||

| - М.: Радио и.связь, 1981, с.59, рис.39. |

Авторы

Даты

1985-10-30—Публикация

1984-04-19—Подача