Изобретение относится к вычислительной технике и предназначено для использования в интегральных логических микросхемах цифровьк ЭВМ.

Цель изобретения - снижение потребляемой мощности и повьшшние быстродействия триггера.

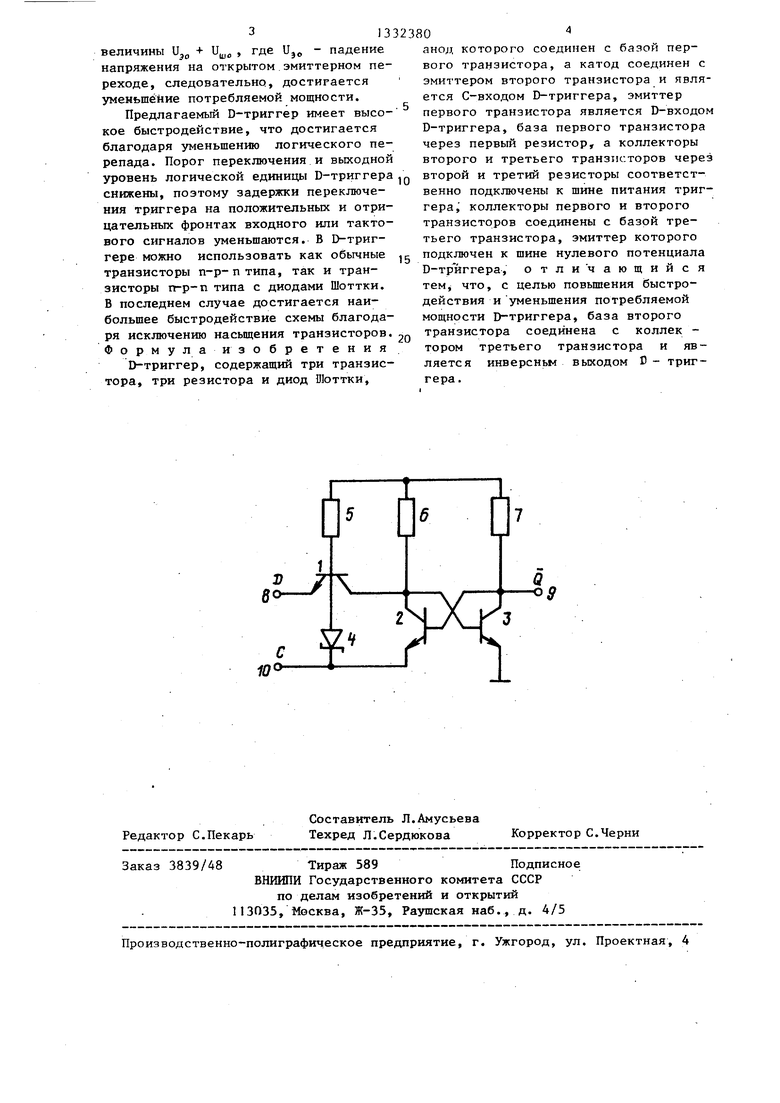

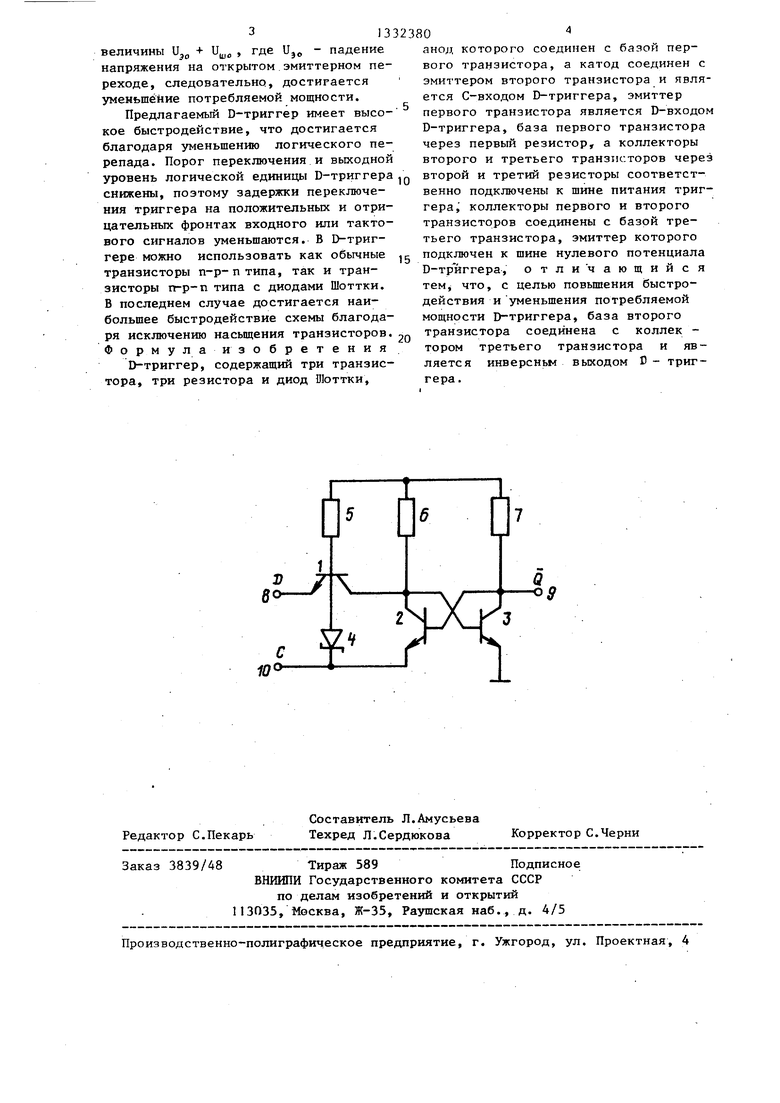

На чертеже изображена принципиальная схема D-триггера.

D-триггер содержит три транзистора 1-3, два из которых 2 и 3 образуют бистабильную ячейку, диод Шоттки 4 и три резистора 5-7, база первого транзистора 1 через токоограничительный первый резистор 5, а коллекторы второго 2 и третьего 3 транзисторов би- стабильной ячейки через нагрузочные (второй и третий) резисторы 6 и 7 соответственно соединены- с шиной пита- ния, эмиттер транзистора 1 является D-входом 8 D-триггера, коллектор транзистора 1 соединен с базой третьего транзистора 3 бистабильной ячейки, коллектор которого является инверсным выходом 9 В триггера, эмиттер транзистора 2 бистабильной ячейки является тактовым входом 10 D- триггера, анод входного диода 4 Шоттки соединен с базой транзистора 1, .а катод - с тактовым входом 10 D- триггера .база транзистора 3 бистабильной ячейки соединена, с инверсным выходом 9 D-триггера, а эмиттер транзистора 3 бистабильной ячейки соеди- нен с общей шиной.

D-триггер работает следующим образом.

Предположим, что на тактовый вход 10 подано напряжейие логической единицы и , тогда диод 4 Шоттки закрыт при любом значении потенциала на входе 8 триггера и ток через него не протекает. Если на входе 8 триггера установлен потенциал логической еди- ницы и , то транзистор 1 находится в инверсном режиме и его ток коллектора, втекает в базу транзистора 3 и является достаточным для насыщения транзистора 3, потенциал на коллекто- ре которого, т.е. на выходе 9 триггера, равен остаточноксу напряжению U , Потенциал логической единицы с входа тактового сигнала поступает также и на эмиттер транзистора 2, поэтому транзистор 2 выключен и его ток коллектора равен нулю.

Если на вход 8 триггера подается потенциал логического нуля U®, транзистор 1 насыщается и на его коллекторе устанавливается потенциал U°+ -ь и.,.,, где и - падение напряжения

JV Пft П

между коллектором и эмиттером насыщенного транзистора. Этот потенциал недостаточен для удержания транзистора 3 во включенном состоянии, поэтому он выключается и потенциал на его коллекторе увеличивается до уровня логической единицы U , однако транзистор 2 по-прежнему закрыт и его ток коллектора равен нулю.

Таким образом, при удержании потенциала логической единицы на тактовом входе 10 на выходе 9 триггера появляется потенциал логической инверсии входного сигнала.

Пусть на тактовый вход 10 подано напряжение U°, диод Шоттки открывается и потенциал базы транзистора 1 уменьшается до величины U° + ,где Uyjo - напряжение на открытом диоде Шоттки. Тогда независимо от величины входного сигнала на эмиттере транзистора 1 на базе этого транзистора сохраняется низкий потенциал U + Uyo, недостаточный для отпирания транзистора 1, поэтому коллекторный ток транзистора 1 равен нулю. Потенциал эмиттера транзистора 2 равен U, , поэтому если потенциал на выходе триггера равен и , то в базу транзистора 2 втекает ток резистора 7, достаточный для насыщения транзистора 2. На базе транзистора 3 устанавливается потенциал U(4H , недостаточный для отпирания транзистора 3, поэтому на выходе триггера сохраняется высокий потенциал и и° + Ujo. Если же на выходе триггера бьшо напряжение логического нуля и , то транзистор 2 остается закрытым, так как напряжение между его базой и змиттер зм близко к нулю, а ток резистора 6 втекает в.базу транзистора 3 и достаточен для удержания его в насыщенном состоянии. При этом на выходе 9 триггера сохраняется потенциал логического нуля U . Следовательно, при удержании потенциала логического нуля и на тактовом входе 10 триггер сохран яет записанную ранее информацию.

Таким образом, устройство, схема которого изображена на чертеже, функционирует как D-триггер, тактируемый уровнем логической единицы.

D-трИггер работает при низких напряжениях источника питания вплоть до

313

величины + , где Uj, - падение напряжения на открытом эмиттерном переходе, следовательно, достигается уменьшение потребляемой мощности.

Предлагаемый D-триггер имеет высокое быстродействие, что достигается благодаря уменьшению логического перепада. Порог переключения и выходной уровень логической единицы D-триггера снижены, поэтому задержки переключения триггера на положительных и отрицательных фронтах входного или тактового сигналов уменьшаются. В D-триг- гере можно использовать как обычные транзисторы п-р-птипа, так и транзисторы гт-р-п типа с диодами Шоттки. В последнем случае достигается наибольшее быстродействие схемы благодаря исключению насьш1еиия транзисторов. Формулаизобретения

D-триггер, содержащий три транзистора, три резистора и диод Шоттки,

5

0

2380

анод которого соединен с базой первого транзистора, а катод соединен с эмиттером второго транзистора и является С-входом D-триггера, эмиттер первого транзистора является D-входом D-триггера, база первого транзистора через первый резистор, а коллекторы второго и третьего транзисторов через второй и третий резисторы соответственно подключены к шине питания триггера j коллекторы первого и второго транзисторов соединены с базой третьего транзистора, эмиттер которого подключен к шине нулевого потенциала D-трнггера, отличающийся тем что, с целью повьш1ения быстродействия и уменьшения потребляемой мощности D-триггера, база второго транзистора соединена с коллек - тором третьего транзистора и является инверсньм выходом D - триггера.

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| @ -Триггер | 1984 |

|

SU1174987A1 |

| @ -Триггер | 1984 |

|

SU1188862A1 |

| @ -Триггер (его варианты) | 1984 |

|

SU1188861A1 |

| Триггер | 1983 |

|

SU1150734A1 |

| Динамический логический элемент | 1979 |

|

SU822370A1 |

| Транзисторно-транзисторный логический элемент | 1983 |

|

SU1128387A1 |

| Синхронный логический элемент | 1976 |

|

SU573881A1 |

| Д-триггер | 1982 |

|

SU1027802A1 |

| JK-триггер | 1989 |

|

SU1713091A1 |

| Д-триггер | 1984 |

|

SU1221714A1 |

Изобретение относится к вычислительной технике и может быть использовано в интегральных логических микросхемах цифровых ЭВМ..Целью изобретения является повышение быстродействия и уменьшенне потребляемой мощности. В предложенном D-триггере сокращаются аппаратурные затраты, повы- щается быстродействие за счет сокращения задержки переключения триггера и повышения максимальной рабочей частоты триггера, которая определяется только вторым транзистором. 1 нл. г Ь

Редактор С.Пекарь

Составитель Л.Амусьева Техред Л.Сердюкова

3839/48

Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор С.Черни

| Иванов Ю.П., Шагурин И.И | |||

| Триггеры и последовательностные узлы БИС на бистабильных ячейках с управлением по выходам | |||

| - Автоматика и вычис- лительная техника, 1982, 1 1, с | |||

| Веникодробильный станок | 1921 |

|

SU53A1 |

| @ -Триггер | 1984 |

|

SU1174987A1 |

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

Авторы

Даты

1987-08-23—Публикация

1985-07-12—Подача