Фиа. 1

Изобретение относится к импульсной технике и может быть использовано при построении цифровых устройств различного назначения для деления частоты следования периодических импульсов в дробное число раз, в частности в синтезаторах частоты.

Известно устройство для деления частоты следования импульсов, содержащее блок дробных разрядов, элемент ИЛИ, программные счетчики младшего и старшего разрядов и высокочастотный счетчик с двумя фиксированными значениями коэффициента пересчета.

Недостатком известного устройства является то, что оно не позволяет производить деление частоты на коэффициент, когда численное значение его целой части, записываемое в счетчик младшего разряда больше или равно численному значению коэффициента записываемого в счетчик старших разрядов и, в частности, когда целая часть коэффициента деления меньше 10.

Наиболее близким по технической сущности к предлагаемому является делитель частоты следования импульсов с дробным коэффициентом деления, содержащий счетные декады единиц, десятков, сотен, десятых и сотых долей коэффициента деления и средства управления дробными декадами, которые содержат блоки сдвига единиц, десятых и сотых долей коэффициента деления, блок переноса, первый вход которого соединен с выходом счетной декады единиц, второй вход - с первым выходом блока сдвига единиц, э первый выход - со счетным входом счетной декады десятков, первый выход которой соединен со счетным входом счетной декады сотен, и блок фиксации, блок обнуления, дешифраторы, триггеры сдвига десятых и сотых долей коэффициента решения, блоки управления сдвигом единиц и десятых долей коэффициента деления, мультиплексоры и инвертор.

Данный делитель обеспечивает любой , дробный коэффициент деления ICj/l, однако его недостатком является сложность и низкая надежность, обусловленные тем, что л при построении делителя с многоразрядной целой и дробной частями коэффициента деления значительно увеличиваются как аппаратные затраты, так и связи.

Цель изобретения - повышение надежности работы с одновременным обеспечением возможности реализации дробных каскадов деления частоты на больших интегральных схемах (БИС) путем обеспечения полной регулярности структуры.

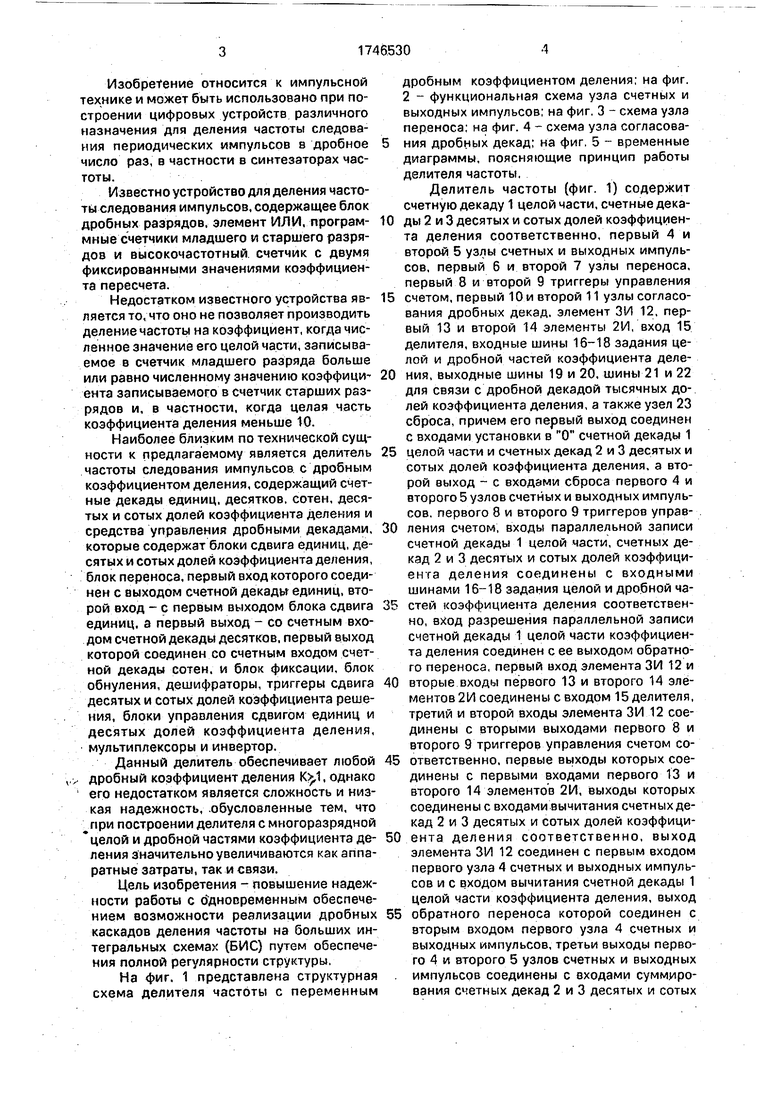

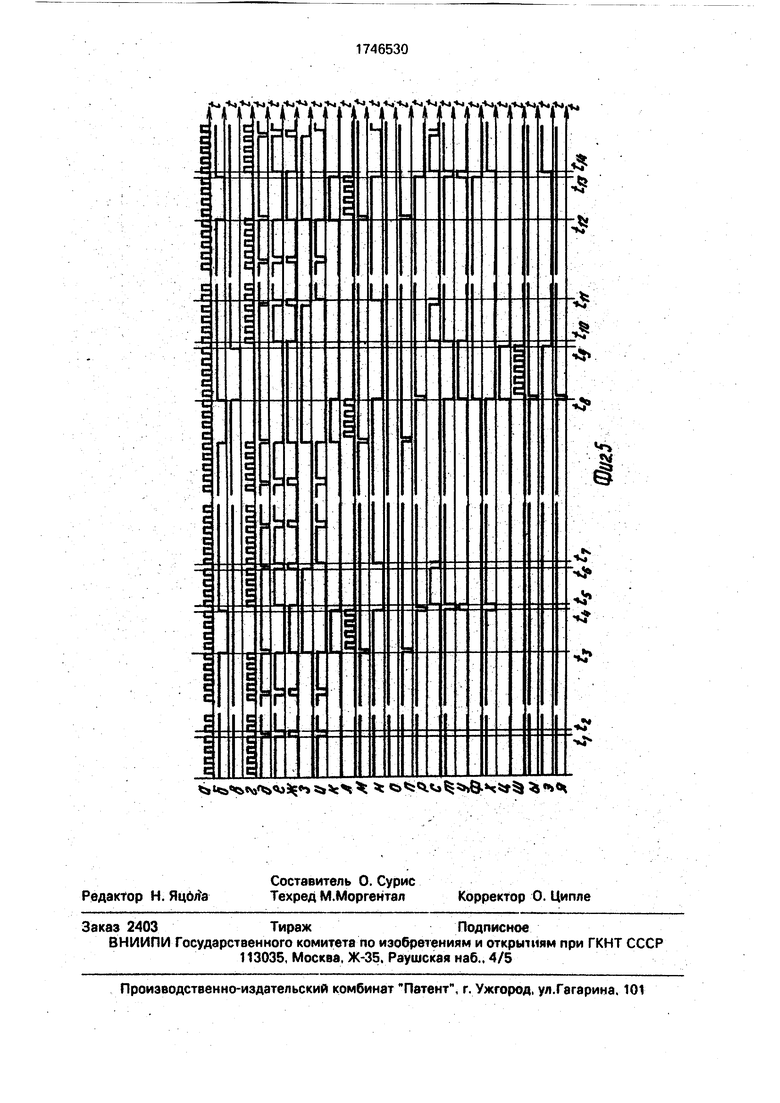

На фиг. 1 представлена структурная схема делителя частоты с переменным

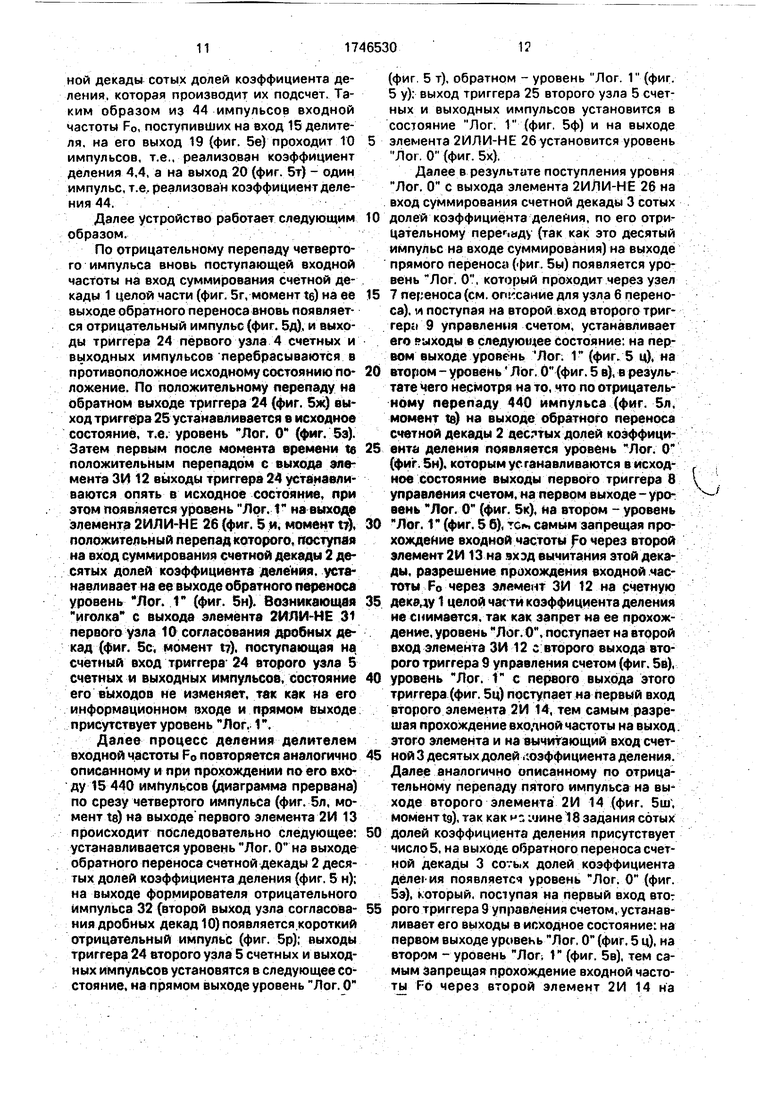

дробным коэффициентом деления; на фиг. 2 - функциональная схема узла счетных и выходных импульсов; на фиг, 3 - схема узла переноса; на фиг. 4 - схема узла согласования дробных декад; на фиг, 5 - временные диаграммы, поясняющие принцип работы делителя частоты.

Делитель частоты (фиг. 1) содержит счетную декаду 1 целой части, счетные дека0 ды 2 и 3 десятых и сотых долей коэффициента деления соответственно, первый 4 и второй 5 узлы счетных и выходных импульсов, первый 6 и второй 7 узлы переноса, первый 8 и второй 9 триггеры управления

5 счетом, первый 10 и второй 11 узлы согласования дробных декад, элемент ЗИ 12. первый 13 и второй 14 элементы 2И, вход 15 делителя, входные шины 16-18 задания целой и дробной частей коэффициента деле0 Ния, выходные шины 19 и 20, шины 21 и 22 для связи с дробной декадой тысячных долей коэффициента деления, а также узел 23 сброса, причем его первый выход соединен с входами установки в О счетной декады 1

5 целой части и счетных декад 2 и 3 десятых и сотых долей коэффициента деления, а второй выход - с входами сброса первого 4 и второго 5 узлов счетных и выходных импульсов, первого 8 и второго 9 триггеров управ0 ления счетом, входы параллельной записи счетной декады 1 целой части, счетных декад 2 и 3 десятых и сотых долей коэффициента деления соединены с входными шинами 16-18 задания целой и дробной ча5 стей коэффициента деления соответственно, вход разрешения параллельной записи счетной декады 1 целой части коэффициента деления соединен с ее выходом обратного переноса, первый вход элемента ЗИ 12 и

0 вторые входы первого 13 и второго 14 элементов 2И соединены с входом 15 делителя, третий и второй входы элемента ЗИ 12 соединены с вторыми выходами первого 8 и второго 9 триггеров управления счетом со5 ответственно, первые выходы которых соединены с первыми входами первого 13 и второго 14 элементов 2И, выходы которых соединены с входами вычитания счетных декад 2 и 3 десятых и сотых долей коэффици0 ента деления соответственно, выход элемента ЗИ 12 соединен с первым входом первого узла 4 счетных и выходных импульсов и с входом вычитания счетной декады 1 целой части коэффициента деления, выход

5 обратного переноса которой соединен с вторым входом первого узла 4 счетных и выходных импульсов, третьи выходы первого 4 и второго 5 узлов счетных и выходных импульсов соединены с входами суммирования счетных декад 2 и 3 десятых и сотых

долей коэффициента деления соответственно, выходы прямого переноса которых соединены с первыми входами первого 6 и второго 7 узлов переноса, группы вторых входов которых соединены с входными ши- нами 17 и 18 задания дробной части коэффициента деления, первые выходы первого 6 и второго 7 узлов переноса соединены с вторыми входами первого 10 и второго 11 узлов согласования дробных декад, а вто- рые выходы соединены с третьими входами первого 4 и второго 5 узлов счетных и выходных импульсов, с входами разрешения параллельной записи счетных декад десятых и сотых долей коэффициента деления и с вторыми входами первого 8 и второго 9 триггеров управления счетом, первые входы которых соединены с выходами обратного переноса счетных декад 2 и 3 десятых и сотых долей коэффициента деления и с третьими входами первого 10 и второго 11 узлов согласования дробных декад соответственно, первые и вторые выходы которых соединены с первыми и вторыми входами второго 5 и последующих узлов счетных и выходных импульсов, через шины 21 и 22 связи с дробной декадой тысячных долей коэффициента деления соответственно, первые выходы первого 4 и второго 5 узлов счетных и выходных импульсов соединены с выходными шинами 19 и 20 делителя соответственно, а вторые выходы - с первыми входами первого 10 и второго 11 узлов согласования дробных декад.

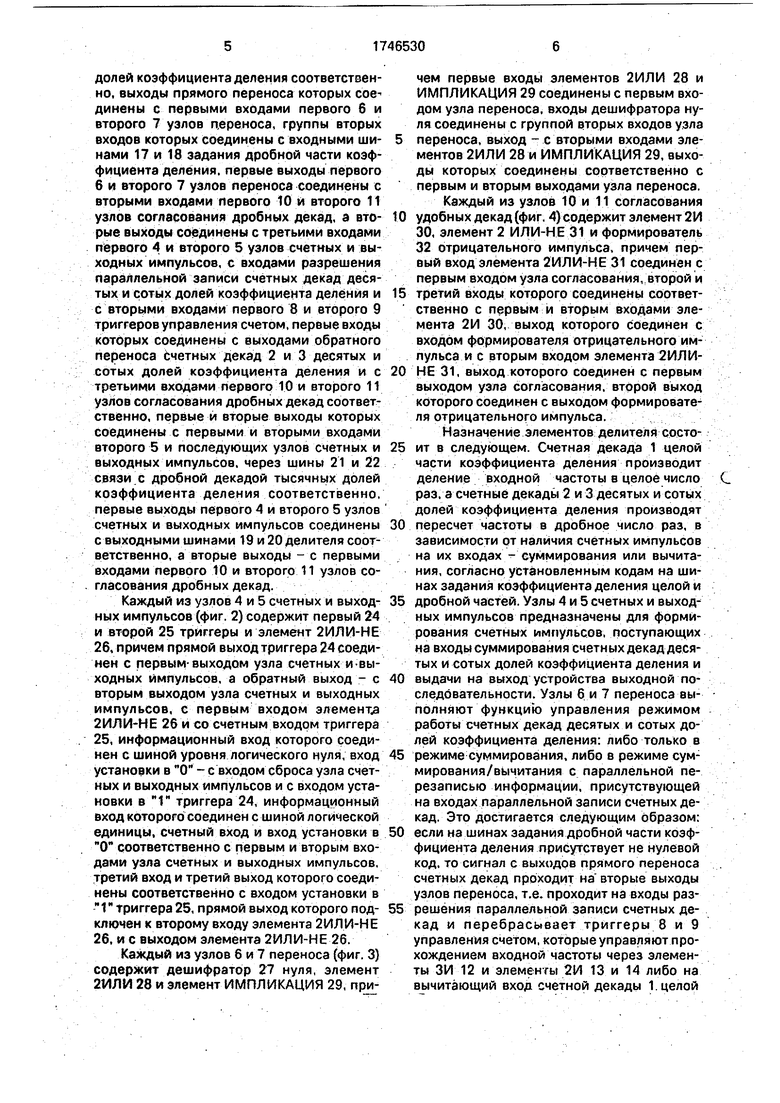

Каждый из узлов 4 и 5 счетных и выход- ных импульсов (фиг. 2) содержит первый 24 и второй 25 триггеры и элемент 2ИЛИ-НЕ 26, причем прямой выход триггера 24 соединен с первым-выходом узла счетных и-вы- ходных импульсов, а обратный выход - с вторым выходом узла счетных и выходных импульсов, с первым входом элемента 2ИЛИ-НЕ 26 и со счетным входом триггера

25,информационный вход которого соединен с шиной уровня логического нуля, вход установки в О - с входом сброса узла счетных и выходных импульсов и с входом установки в 1 триггера 24, информационный вход которого соединен с шиной логической единицы, счетный вход и вход установки в О соответственно с первым и вторым входами узла счетных и выходных импульсов, третий вход и третий выход которого соединены соответственно с входом установки в

1 триггера 25, прямой выход которого под- ключей к второму входу элемента 2ИЛИ-НЕ

26.и с выходом элемента 2ИЛИ-НЕ 26.

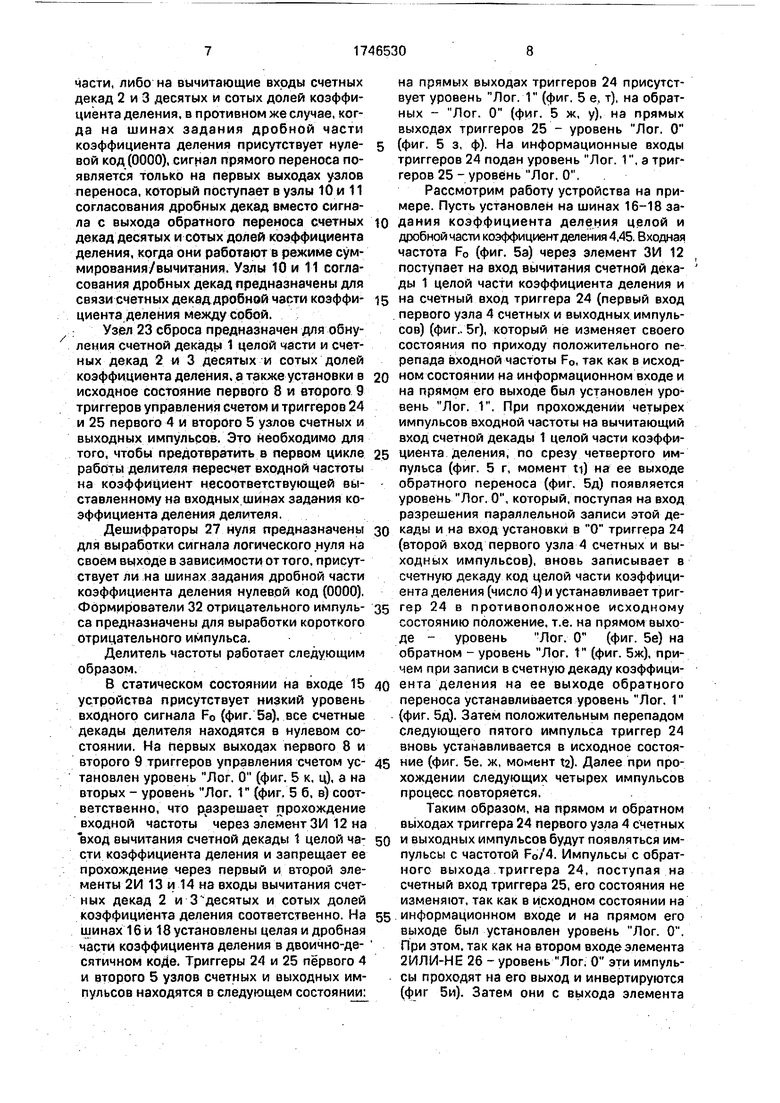

Каждый из узлов 6 и 7 переноса (фиг. 3} содержит дешифратор 27 нуля, элемент 21/1ЛИ 28 и элемент ИМПЛИКАЦИЯ 29, причем первые входы элементов 2ИЛИ 28 и ИМПЛИКАЦИЯ 29 соединены с первым входом узла переноса, входы дешифратора нуля соединены с группой вторых входов узла переноса, выход - с вторыми входами элементов 2ИЛИ 28 и ИМПЛИКАЦИЯ 29, выходы которых соединены соответственно с первым и вторым выходами узла переноса.

Каждый из узлов 10 и 11 согласования удобных декад (фиг. 4) содержит элемент 2И 30, элемент 2 ИЛИ-НЕ 31 и формирователь 32 отрицательного импульса, причем первый вход элемента 2ИЛИ-НЕ 31 соединен с первым входом узла согласования, второй и третий входы которого соединены соответственно с первым и вторым входами элемента 2И 30, выход которого соединен с входом формирователя отрицательного импульса и с вторым входом элемента 2ИЛИНЕ 31, выход которого соединен с первым выходом узла согласования, второй выход которого соединен с выходом формирователя отрицательного импульса.

Назначение элементов делителя состоит в следующем. Счетная декада 1 целой части коэффициента деления производит деление входной частоты в целое число раз. а счетные декады 2 и 3 десятых и сотых долей коэффициента деления производят пересчет частоты в дробное число раз, в зависимости от наличия счетных импульсов на их входах - суммирования или вычитания, согласно установленным кодам на шинах задания коэффициента деления целой и дробной частей. Узлы 4 и 5 счетных и выходных импульсов предназначены для формирования счетных импульсов, поступающих на входы суммирования счетных декад десятых и сотых долей коэффициента деления и выдачи на выход устройства выходной последовательности. Узлы 6 и 7 переноса выполняют функцию управления режимом работы счетных декад десятых и сотых долей коэффициента деления: либо только в режиме суммирования, либо в режиме суммирования/вычитания с параллельной перезаписью информации, присутствующей на входах параллельной записи счетных декад. Это достигается следующим образом: если на шинах задания дробной части коэффициента деления присутствует не нулевой код. то сигнал с выходов прямого переноса счетных декад проходит на вторые выходы узлов переноса, т.е. проходит на входы разрешения параллельной записи счетных декад и перебрасывает триггеры 8 и 9 управления счетом, которые управляют прохождением входной частоты через элементы ЗИ 12 и элементы 2И 13 и 14 либо на вычитающий вход счетной декады 1 целой

части, либо на вычитающие входы счетных декад 2 и 3 десятых и сотых долей коэффициента деления, в противном же случае, когда на шинах задания дробной части коэффициента деления присутствует нулевой код (0000), сигнал прямого переноса появляется только на первых выходах узлов переноса, который поступает в узлы 10 и 11 согласования дробных декад вместо сигнала с выхода обратного переноса счетных декад десятых и сотых долей коэффициента деления, когда они работают в режиме суммирования/вычитания. Узлы 10 и 11 согласования дробных декад предназначены для связи счетных декад дробной части коэффициента деления между собой.

Узел 23 сброса предназначен для обнуления счетной декады 1 целой части и счетных декад 2 и 3 десятых и сотых долей коэффициента деления, а также установки в исходное состояние первого 8 и второго 9 триггеров управления счетом и триггеров 24 и 25 первого 4 и второго 5 узлов счетных и выходных импульсов. Это необходимо для того, чтобы предотвратить в первом цикле работы делителя пересчет входной частоты на коэффициент несоответствующей выставленному на входных шинах задания коэффициента деления делителя.

Дешифраторы 27 нуля предназначены для выработки сигнала логического нуля на своем выходе в зависимости от того, присутствует ли на шинах задания дробной части коэффициента деления нулевой код (0000). Формирователи 32 отрицательного импульса предназначены для выработки короткого отрицательного импульса.

Делитель частоты работает следующим образом.

В статическом состоянии на входе 15 устройства присутствует низкий уровень входного сигнала F0 (фиг. 5а), все счетные декады делителя находятся в нулевом состоянии. На первых выходах первого 8 и второго 9 триггеров управления счетом установлен уровень Лог. О (фиг. 5 к, ц), а на вторых - уровень Лог. Г (фиг. 5 б, в) соответственно, что разрешает прохождение входной частоты через элемент ЗИ 12 на вход вычитания счетной декады t целой части коэффициента деления и запрещает ее прохождение через первый и второй элементы 2И 13 и 14 на входы вычитания счетных декад 2 и 3 десятых и сотых долей коэффициента деления соответственно. На шинах 16 и 18 установлены целая и дробная части коэффициента деления в двоично-десятичном коде. Триггеры 24 и 25 первого 4 и второго 5 узлов счетных и выходных импульсов находятся в следующем состоянии:

на прямых выходах триггеров 24 присутствует уровень Лог. 1 (фиг, 5 е, т), на обратных - Лог. О (фиг. 5 ж, у), на прямых выходах триггеров 25 - уровень Лог. О

(фиг. 5 з, ф). На информационные входы триггеров 24 подан уровень Лог. 1, а триггеров 25 - уровень Лог. О.

Рассмотрим работу устройства на примере. Пусть установлен на шинах 16-18 заДания коэффициента деления целой и дробной части коэффициент деления 4.45. Входная частота F0 (фиг. 5а) через элемент ЗИ 12 поступает на вход вычитания счетной декады 1 целой части коэффициента деления и

5 на счетный вход триггера 24 (первый вход первого узла 4 счетных и выходных импульсов) (фиг.. 5г), который не изменяет своего состояния по приходу положительного перепада входной частоты F0, так как в исход0 ном состоянии на информационном входе и на прямом его выходе был установлен уровень Лог. 1. При прохождении четырех импульсов входной частоты на вычитающий вход счетной декады 1 целой части коэффи5 циента деления, по срезу четвертого импульса (фиг. 5 г, момент ti) на ее выходе обратного переноса (фиг. 5д) появляется уровень Лог. О, который, поступая на вход разрешения параллельной записи этой де0 кады и на вход установки в О триггера 24 (второй вход первого узла 4 счетных и выходных импульсов), вновь записывает в счетную декаду код целой части коэффициента деления (число 4) и устанавливает триг5 гер 24 в противоположное исходному состоянию положение, т.е. на прямом выходе - уровень Лог. О (фиг. 5е) на обратном - уровень Лог. t (фиг. 5ж), причем при записи в счетную декаду коэффици0 ента деления на ее выходе обратного переноса устанавливается уровень Лог. 1 (фиг. 5д). Затем положительным перепадом следующего пятого импульса триггер 24 вновь устанавливается в исходное состоя5 ние (фиг. 5е, ж, момент ta). Далее при прохождении следующих четырех импульсов процесс повторяется.

Таким образом, на прямом и обратном выходах триггера 24 первого узла 4 счетных

0 и выходных импульсов будут появляться импульсы с частотой Fo/4. Импульсы с обратного выхода триггера 24, поступая на счетный вход триггера 25, его состояния не изменяют, так как в исходном состоянии на

5 информационном входе и на прямом его выходе был установлен уровень Лог. О. При этом, так как на втором входе элемента 2ИЛИ-НЕ 26 - уровень Лог. О эти импульсы проходят на его выход и инвертируются (фиг 5и). Затем они с выхода элемента

2ИЛИ-НЕ 26 поступают на суммирующий вход счетной декады 2 десятичных долей коэффициента деления, которая производит их подсчет. После прохождения 10 циклов деления этой декадной (диаграмма прервана) по отрицательному перепаду девятого импульса на ее входе суммирования (фиг. 5и, момент ta) - на выходе прямого переноса, появляется уровень Лог. О (фиг. 5м). Так как на входах дешифратора 27 нуля (группа вторых входов узла 6 переноса) присутствует не нулевой код, в данном случае число 4, то на выходе этого элемента присутствует уровень Лог, 1. Этим уровнем запрещается прохождение отрицательного импульса с выхода прямого переноса счетной декады 2 десятых долей коэффициента деления на выход элемента 2ИЛИ 28 (фиг. 5о) и разрешается его прохождение через элемент ИМПЛИКАЦИЯ 29 (фиг, 5п) на вход разрешения параллельной, записи этой декады и на вход установки в 1 триггера 25 (третий вход узла счетных и выходных импульсов 4), при этом выход триггера устанавливается в состояние Лог. 1 (фиг. 5з). и в счетную декаду 2 десятых долей коэффициента деления вновь записывается код десятой доли дробной части коэффициента деления, который подан на ее входы параллельной записи с шины 17 задания дробной части коэффициента деления.

После записи информации в счетную декаду на ее выходе прямого переноса устанавливается уровень Лог. 1 (фиг. 5м). Таким образом, на выходе прямого переноса счетной декады десятых долей коэффициента деления появляется короткий отрицательный импульс. Этот импульс, проходя через элемент ИМПЛИКАЦИЯ 29 первого узла 6 переноса, поступает на второй вход первого триггера 8 управления счетом и устанавливает на его первом выходе уровень Лог. 1 (фиг. 5к), а на втором выходе - уровень Лог. О (фиг. 56) в результате чего разрешается прохождение входной частоты FO на вычитающий вход счетной декады 2 десятых долей коэффициента деления (фиг, 5л) и запрещается прохождение этой частоты на вычитающий вход счетной декады 1 целой части коэффициента деления (фиг. 5г) Положительным перепадом импульса с выхода первого элемента 2И 13 (фиг. 5л) происходит вычитание единицы из информации, записанной в счетную декаду 2 десятых долей коэффициента деления. При достижении счетной декады нулевого состояния по срезу четвертого импульса на ее входе вычитания (момент t4. фиг. 5л) на выходе обратного переноса (фиг 5н) устанавливается уровень Лог 0 Этот уровень,

поступая на первый вход первого триггера 8 управления счетом, устанавливает его выходы в исходное состояние: на первом выходе (фиг. 5к) уровень Лог, 0, а на втором - уровень Лог. 1 (фиг. 56), тем самым запрещая прохождение входной частоты Fo через первый элемент 2И 13 на вычитающий вход счетной декады десятых долей коэффициента деления 2, и разрешая вновь ее прохождение через элемент ЗИ 12 на вычитающий вход счетной декады целой части коэффициента деления (фиг. 5л. г) соответственно.

Этот же урове нь Лог. О с выхода обратного переноса счетной декады 2 десятых долей коэффициента деления 2, поступая на второй вход элемента 2И 30 (третий вход первого узла 10 согласования дробных декад), проходит на его выход, и по отрицательному перепаду (фиг. 5н), формирователь 32 отрицательного импульса формирует короткий импульс (фиг. 5р), который поступает на вход установки в О триггера 24 (второй вход узла 5 счетных и выходных импульсов) и перебрасывает его выходы в противоположное исходному состоянию (фиг. 5т, у) аналогично описанному для триггера 24 узла 4 счетных и выходных импульсов. А так как в момент времени t4 первый триггер 8 управления счетом установился в исходное состояние и на втором и третьем входах элемента ЗИ 12 присутствует уровень Лог. 1 (фиг. 5 б, в), то по первому вновь прошедшему через элемент ЗИ 12 положительному перепаду (фиг. 5 г, момент ts). который поступает на счетным вход триггера 24 (первый вход 4 узла счетных и выходным импульсов), его выходы принимают исходное состояние: прямой - уровень Лог. 1 (фиг. 5е), обратный - уровень Лог. О (фиг. 5ж). Уровень Лог, 0 с обратного выхода триггера 24 поступает на первый вход элемента 2ИЛИ-НЕ 31 (первый вход первого узла 10 согласования дробных декад), и так как на его втором входе с выхода элемента 2И 30 установлен тоже уровень Лог. О, то на выходе элемента появится уровень Лог. 1, положительный перепад которого (фиг. 5с) поступает на счетный вход триггера 24 (первый вход второго узла 5 счетных и выходных импульсов) и устанавливает его выходы и исходное состояние (фиг. 5т, у). Далее в результате того, что выход триггера 25 (фиг. 5ф) находится в состоянии Лог. О, как было описано для триггера 24 первого узла 4 счетных и выходных импульсов, импульс с обратного выхода триггера 24 второго узла 5 счетных и выходных импульсов проходит, инвертируясь, на выход элемента 2ИЛИ-НЕ 26 (фиг. 5х) и затем поступает на выход суммирования счет11 17465301

ной декады сотых долей коэффициента де-(фиг 5 т), обратном - уровень Лог. 1 (фиг.

ления. которая производит их подсчет. Та-5 у): выход триггера 25 второго узла 5 счетким образом из 44 импульсов входнойных и выходных импульсов установится в

частоты FO, поступивших на вход 15 делите-состояние Лог. 1 (фиг. 5ф) и на выходе

ля. на его выход 19 (фиг. 5е) проходит 105 элемента 2ИЛИ-НЕ 26 установится уровень

импульсов, т.е., реализован коэффициент Лог 0 (фиг. 5х).

деления 4,4, а на выход 20 (фиг. 5т) - одинДалее в результате поступления уровня

импульс, т.е. реализован коэффициент деле- Лог. О с выхода элемента 2ИЛИ-НЕ 26 на

ния 44.вход суммирования счетной декады 3 сотых

Далее устройство работает следующим10 долей коэффициента деления, по его отриобразом.цательному перепад (так как это десятый

По отрицательному перепаду четверто-импульс на входе суммирования) на выходе го импульса вновь поступающей входнойпрямого переноса (фиг. 5ы) появляется уро- частоты на вход суммирования счетной де-вень Лог. О, который проходит через узел кады 1 целой части (фиг. 5г, момент te) на ее15 7 переноса (см. описание для узла 6 перено- выходе обратного переноса вновь появляет-са), и поступая на второй вход второго триг- ся отрицательный импульс (фиг. 5д), и выхо-repu 9 управления счетом, устанавливает ды триггера 24 первого узла 4 счетных иего РЫХОДЫ в следующее состояние: на пер- выходных импульсов перебрасываются ввом выходе уровень Лог. Г (фиг, 5 ц), на противоположное исходному состоянию по-20 втором - уровень Лог. О (фиг. 5 в), в резуль- ложение. По положительному перепаду натате чего несмотря на то, что по отрицатель- обратном выходе триггера 24 (фиг. 5ж) вы-ному перепаду 440 импульса (фиг. 5л. ход триггера 25 устанавливается в исходноемомент te) на выходе обратного переноса состояние, т.е. уровень Лог. О (фиг. 5з).счетной декады 2 десятых долей коэффици- Затем первым после момента времени te25 ента деления появляется уровень Лог. О положительным перепадом с выхода эле-(фиг. 5н). которым устанавливаются в исход- мента ЗИ 12 выходы триггера 24 устанавли-ное состояние выходы первого триггера 8 ваются опять в исходное состояние, приуправления счетом, на первом выходе-уро- ч-/ этом появляется уровень Лог. 1 на выходевень Лог. О (фиг. 5к), на втором - уровень элемента 2ИЛИ-НЕ 26 (фиг. 5 и, момент t),30 Лог. 1 (фиг. 5 б), тс, самым запрещая про- положительный перепад которого, поступаяхождение входной частоты f о через второй на вход суммирования счетной декады 2 де-элемент 2И 13 на вх эд вычитания этой дека- сятых долей коэффициента деления, , разрешение прохождения входной час- навливает на ее выходе обратного переносатоты F0 через элемент ЗИ 12 на счетную уровень Лог. Г (фиг. 5н). Возникающая35 декаду 1 целой части коэффициента деления иголка с выхода элемента 2ИЛИ-НЕ 31не снимается, так как запрет на ее прохож- первого узла 10 согласования дробных де-дение, уровень Лог.О, поступает на второй кад (фиг. 5с, момент t), поступающая навход элемента ЗИ 12 с второго выхода вто- счетный вход триггера 24 второго узла 5рого триггера 9 управления счетом (фиг. 5в), счетных и выходных импульсов, состояние40 уровень Лог. Г с первого выхода этого его выходов не изменяет, так как на еготриггера (фиг. 5ц) поступает на первый вход информационном входе и прямом выходевторого элемента 2И 14, тем самым разре- присутствует уровень Лог. 1.шая прохождение входной частоты на выход.

Далее процесс деления делителемэтого элемента и на вычитающий вход счет- входной частоты FO повторяется аналогично45 ной 3 десятых долей .коэффициента деления, описанному и при прохождении по его вхо-Далее аналогично описанному по отрица- ду 15 440 импульсов (диаграмма прервана)тельному перепаду пятого импульса на вы- по срезу четвертого импульса (фиг. 5л, мо-ходе второго элемента 2И 14 (фиг. 5ш, мент te) на выходе первого элемента 2И 13момент tg), так как м шине 18 задания сотых происходит последовательно следующее:50 долей коэффициента деления присутствует устанавливается уровень Лог. О на выходечисло 5, на выходе обратного переноса счет- обратного переноса счетной декады 2 деся-ной декады 3 сотых долей коэффициента тых долей коэффициента деления (фиг. 5 н);делег ия появляется уровень Лог. О (фиг. на выходе формирователя отрицательного5э), который, поступая на первый вход вто импульса 32 (второй выход узла согласова-55 рого триггера 9 управления счетом, устанав- ния дробных декад 10) появляется короткийливает его выходы в исходное состояние: на отрицательный импульс (фиг. 5р); выходыпервом выходе уровень Лог, 0 (фиг. 5ц), на триггера 24 второго узла 5 счетных и выход-втором - уровень Лог. 1 (фиг. 5в), тем са- ных импульсов установятся в следующее со-мым запрещая прохождение входной часто- стояние, на прямом выходе уровень Лог. Fo через второй элемент 2И 14 на

вычитающий вход счетной декады 3 сотых долей коэффициента деления и разрешая ее прохождение через элемент ЗИ 12 на вычитающий вход счетной декады 1 целой части коэффициента деления. По первому поло- жительному перепаду, вновь поступающему на вычитающий вход этой декады (фиг.Бг) момент tio), аналогично описанному, устанавливаются в следующие состояния последовательно: прямой выход триггера 24 первого узла 4 счетных и выходных импульсов в состояние Лог. 1 (фиг. 5е) обратный выход - в состояние Лог. О (фиг. 5ж); на первом выходе первого узла 10 согласования дробных декад (выход элемента 2ИЛИ- НЕ 31) уровень Лог. 1 (фиг. 5с): положительный перепад с выхода элемента 2ИЛИ-НЕ 31, поступая на счетный вход триггера 24 второго узла 5 счетных и выходных импульсов, устанавливает на его пря- мом выходе уровень Лог. 1 (фиг. 5т), на обратном - уровень Лог. О (фиг. 5у).

Таким образом, из 445 импульсов входной частоты на входе 15 делителя на его выход 19 (фиг. 5е) проходит 100 импульсов, т.е. реализован коэффициент деления 4, 45, на выход 20 - десять импульсов (фиг. 5т). т.е. реализован коэффициент деления 44,5.

Далее устройство работает аналогично описанному и на выходе обратного перено- са счетной декады 2 десятых долей коэффициента деления (фиг. 5н) установится вновь уровень Лог. 1 в результате положительного перепада, поступившего на вход суммирования (фиг. 5и. момент tn) после работы счетных декад 2 и 3 длесятых и сотых долей коэффициента деления соответственно в режиме вычитания (фиг. 5л, ш, диаграммы, заканчивающиеся моментами времени te и tg). Появление же положительного пере- пада на входе суммирования счетной декады 2 десятых долей коэффициента деления аналогично описанному для этой же декады для моментов времени te и t. Уровень Лог. 1 на выходе обратного переноса счетной декады 3 сотых долей коэффициента деления (фиг. 5э) установится также только в результате положительного перепада, поступившего на его вход следующим образом. После отрицательного перепада девятого импульса (момент ш) на входе суммирования счетной декады 2 десятых долей коэффициента деления, считая с момента времени tn (фиг. 5и. диаграмма прервана), и по отрицательному перепаду четвертого импульса на входе вычитания этой декады (фиг. 5л, момент т) на его выходе обратного переноса устанавливается уровень Лог. О (фиг. 5н), и далее по отрицательному перепаду этого уровня на выходе формирователя

32 отрицательного импульса (второй выход первого узла 10 согласования дробных декад) появляется отрицательный импульс (фиг. 5р). Этот отрицательный импульс, поступая на вход установки в О триггера 24 (второй вход второго узла 5 счетных и выходных импульсов) перебрасывает его выходы в противоположное исходному состоянию: на прямом - уровень Лог. О (фиг. 5т), на обратном - уровень Лог, 1 (фиг, 5у) и тогда по положительному перепаду на обратном выходе триггера 24 на выходе триггера 25 установится уровень Лог, 0 (фиг. 5ф) и далее для момента времени ts выход триггера 24 вновь установится в исходное состояние, и по отрицательному перепаду на его обратном выходе (фиг. 5у) на выходе элемента 2ИЛИ-НЕ 26 появится положительный перепад, который поступает на вход суммирования счетной декады 3 сотых долей коэффициента деления. Таким образом, произошел цикл работы делителя частоты с переменным дробным коэффициентом деления.

Теперь рассмотрим случай, когда коэффициент деления равен 4,05. т.е. на шине 17 задания десятых долей коэффициента деления присутствует нулевой код. Тогда на выходе дешифратора 27 нуля узла 6 переноса присутствует уровень Лог. О. Этим уровнем запрещается прохождение отрицательного импульса с выхода прямого переноса счетной декады 2 десятых долей коэффициента деления через элемент ИМПЛИКАЦИЯ 29 на втооой вход триггера 8 управления, счетом и на вход разрешения параллельной записи этой же декады, а разрешается его прохождение через элемент 2 И ЛИ 28 на второй вход узла 10 согласования дробных декад (первый вход элемента 2И 30), а так как на втором входе элемента 2И 30. соединенном с выходом обратного переноса счетной декады. 2 десятых долей коэффициента деления, присутствует уровень Лог. Г. то уровень Лог. О на первом входе элемента 2И 30 проходит на его выход. Тогда этим уровнем Лог. О и отрицательным перепадом с второго выхода узла 4 счетных и вы- ходных импульсов (обратный выход триггера 24), который поступает на первый вход узла 10 согласования дробных декад (первый вход элемента 2ИЛИ-НЕ 31), на выходе элемента 2ИЛИ-НЕ 31 появится положительный перепад. Кроме того, по отрицательному перепаду на выходе элемента 2И 30 на выходе формирователя 32 отрицательного импульса появляется короткий отрицательный импульс. Этот импульс и положительный перепад с выхода элемента 2ИЛИ-НЕ 31 поступают на второй и первый

входы второго узла 5 счетных и выходных импульсов (вход установки в О и счетный вход триггера 24 (соотвеетственно). И далее устройство работает аналогично описанному.

Таким образом, при наличии нулевого кода на группе вторых входов узла 6 переноса (входы дешифратора 27 нуля) счетная декада 2 десятых долей коэффициент деления будет работать только в режиме суммирования, так как триггер 8 управления счетом не меняет своего состояния и входная частота на вход вычитания счетной декады поступать не будет.

Применение делителя частоты с переменным дробным коэффициентом деления предлагаемой конструкции обеспечивает любой дробный коэффициент деления с необходимым числом дробных разрядов при обеспечении полной регулярности структуры, что позволяет реализовать устройство на больших интегральных микросхемах.

Формула изобретения

1. Делитель частоты с переменным дробным коэффициентом деления, содержащий счетные декады целой части, десятых и сотых долей коэффициента деления, узел сброса и средства управления счетными декадами дробной части коэффициента деления, включающими дешифратор нуля и триггер управления счетом, при этом первый выход узла сброса соединен с входами установки в О счетных декад целой и дробной частей коэффициента деления, входы параллельной записи которых соединены с входными шинами задания целой и дробной частей коэффициента деления, а вход разрешения параллельной записи счетной декады целой части соединен с выходом ее обратного переноса, отличающийся тем, что, с целью повышения надежности работы с одновременным обеспечением возможности реализации дробных каскадов деления частоты на больших интегральных схемах путем обеспечения полной регулярности структуры, средства управления каждой счетной декады дробной части коэффициента деления содержат узел счетных и выходных импульсов, элемент 2И, узел согласования дробных декад, узел переноса, кроме того, в устройство введен элемент ЗИ, причем второй выход узла сброса соединен с входами сброса узлов счетных и выходных импульсов и триггеров управления систем соответственно, первый вход элемента ЗИ и вторые входы элементов 2И первой и второй дробных декад соединены с входом устройства, третий и второй элементы ЗИ соединены с вторыми выходами триггеров управления счетом, первые выходы которых соединены с первыми входами элементов 2И, выходы которых соединены с входами вычитания счетных декад десятых и сотых долей коэффициента деления, выход элемента ЗИ соединен с первым входом узла счетных и выходных импульсов первой дробной декады и входом вычитания счетной декады целой части коэффициента деления, выход обратного переноса которой

0 соединен с вторым входом узла счетных и выходных импульсов, третьи выходы узлов счетных и выходных импульсов первой и второй дробных декад соединены с входами суммирования счетных декад десятых и со5 тых долей коэффициента деления соответственно, выходы прямого переноса которых соединены с первыми входами узлов переноса первой и второй дробных декад соответственно, группы вторых входов которых

0 соединены с входными шинами задания . дробной части коэффициента деления, первые выходы узлов переноса соединены с вторыми входами узлов согласования дробных декад, а вторые выходы соединены с

5 третьими входами узлов счетных и выходных импульсов, с входами разрешения параллельной записи счетных декад десятых и сотых долей коэффициента деления и с вторыми входами триггеров управления счетом

0 первой и второй дробных декад соответственно, первые входы триггеров управления счетом соединены с выходами обратного переноса счетных декад десятых и сотых долей коэффициента деления и с третьими входа5 ми узлов согласования дробных декад, первые и вторые выходы которых соединены с первыми и вторыми входами узлов счетных и выходных импульсов второй и последующей дробных декад, первые выходы узлов

0 счетных и выходных импульсов соединены с выходными шинами устройства, а вторые выходы с первыми входами узлов согласования дробных декад соответственно.

2. Устройство по п. 1, о т л и ч а ю щ е е5 с я тем, что каждый из узлов счетных и выходных импульсов содержит первый и второй триггеры и элемент 2ИЛИ-НЕ, причем прямой выход первого триггера соединен с первым выходом узла счетных и

0 выходных импульсов, а обратный выход - с вторым выходом узла счетных и выходных импульсов, с первым входом элемента 2ИЛИ-НЕ и счетным входом второго триггера, информационный вход которого соеди5 нен с шиной уровня логического нуля, вход установки в О - с входом сброса узла счетных и выходных импульсов и входом установки в 1 первого триггера, информационный вход которого соединен с шиной логической единицы, счетный вход и

вход установки в О - соответственно с первым и вторым входами узла счетных и выходных импульсов, третий вход и третий выход которого соединены соответственно с входом установки в 1 второго триггера, прямой выход которого подключен к второму входу элемента 2ИЛИ-НЕ, и с выходом элемента 2ИЛИ-НЕ.

3. Устройство по п. 1, о т л и ч а ю щ е е- с я тем, что каждый из узлов переноса содержит дешифратор нуля, элемент 2ИЛИ и элемент ИМПЛИКАЦИЯ, причем первые входы элементов 2 ИЛИ и ИМПЛИКАЦИЯ соединены с первым входом узла переноса, входы дешифратора нуля соединены с группой вторых входов узла переноса, выход - с вторыми входами элементов 2ИЛИ и ИМПЛИКАЦИЯ, выходы которых соединены со0

ответственно с первым и вторым выходами узла переноса.

4. Устройство поп. 1,отличающее- с я тем, что каждый из узлов согласования дробных декад содержит элемент 2И, элемент 2ИЛИ-НЕ и формирователь отрицательного импульса, причем первый вход элемента 2ИЛИ-НЕ соединен с первым входом узла согласования, второй и третий входы которого соединены соответственно с первым и вторым входами элемента 2И, выход которого соединен с входом формирователя отрицательного импульса и с вторым входом элемента 2ИЛИ-НЕ, выход которого соединен с первым выходом узла согласования, второй выход которого соединен с выходом формирователя отрицательных импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следованияиМпульСОВ C дРОбНыМ КОэффициЕНТОМдЕлЕНия | 1979 |

|

SU818021A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1117837A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧАСТОТЫ С ДРОБНЫМ КОЭФФИЦИЕНТОМ | 1971 |

|

SU436446A1 |

| Устройство для вычисления отношения временных интервалов | 1985 |

|

SU1317459A1 |

| Реверсивная пятиразрядная двоичнодесятичная счетная декада | 1976 |

|

SU577686A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1972 |

|

SU344590A1 |

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1981 |

|

SU951713A1 |

| Устройство для вычисления отношения временных интервалов | 1984 |

|

SU1287191A1 |

| Цифровой измеритель отношения временных интервалов | 1986 |

|

SU1390595A1 |

| Электронные часы | 1987 |

|

SU1500986A1 |

Изобретение относится к импульсной технике и предназначено для построения цифровых устройств деления частоты. Целью изобретения является повышение надежности работы. Устройство содержит счетные декады 1 и 2, 3 целой и дробной частей коэффициента деления, узел 23 сбро19 са, причем в средства управления счетными декадами дробной части входят триггеры 8. 9 управления счетом и дешифраторы 6, 7 нуля. Новым в устройстве является то, что в него введены узлы 4 и 5 счетных и выходных импульсов. Дробный коэффициент деления в устройстве Достигается тем, что счетные декады дробной части коэффициента деления работают в двух режимах. При наличии на шинах 17, 18 задания дробной части коэффициента деления ненулевого кода счет- ные декады работают в режиме суммирования/вычитания с параллельной записью, причем каждая последующая счетная декада производит подсчет циклов деления (кратный десяти) предыдущей декады с параллельной записью и вычитанием из информации, присутствующей на шине 16 задания целой чести коэффициента деления, единицы до обнуления этой декады 1. В случае, когда на шинах 17,18 присутствует нулевой код, счетная декада работает только в режиме суммирования. 3 з.п.ф-лы, 5 ил. 20 ie

к узлу

м

18

Шие.2

о

п

Шиз . 3

Шиа. 4

- Vi-vcls,

I i. i

м

Чч|

J+ч-К

LL

Д

4

3

r

i

-

| Делитель частоты с дробным переменным коэффициентом деления | 1985 |

|

SU1372615A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты следованияиМпульСОВ C дРОбНыМ КОэффициЕНТОМдЕлЕНия | 1979 |

|

SU818021A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-07-07—Публикация

1989-11-01—Подача