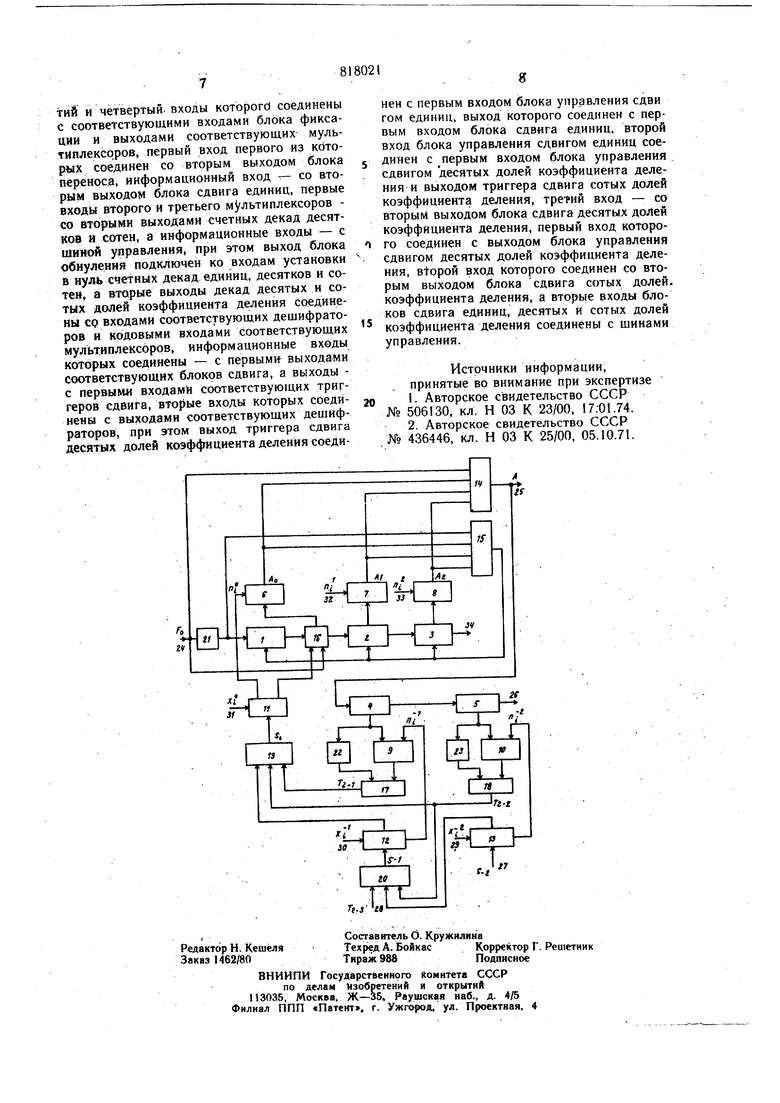

(54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ С ДРОБНЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ счетной декады единиц, второй вход - с первым выходом блока сдвига единиц, а первый выход - со счетным входом счетной декады десятков, первый выход которой соединен со счетным входом счетной декады сотен, и блок фиксации, выход которого соединен со счетным входом счетной-декады десятых долей коэффициента деления, первый выход которой соединен со счетным входом счетной декады сотых долей коэффициента деления, введены блок обнуления, дешифраторы, триггеры сдвига десятых и сотых долей коэффициента деления, блоки управления сдвигом единиц и десятых долей коэффициента деления, мульти плексоры и инвертор, вход которого подключен к входной шине, первому входу блока фиксации и третьему входу блока переноса, а выходк счетному входу счетной декады единиц и первому входу блока однуления, второй, третий и четвертый входы которого соединены с соответствующими входами блока фиксации и выходами соответствующих мультиплексоров, первый вход первого из которых соединен со вторым выходом блока переноса информационный вход со вторым выходом блока сдвига единиц, первые входы второго и третьего мультиплексоров - со вторыми выходами счетных декад десятков и сотен, а информационные входы - с шиной управления, при этом выход блока обнуления подключен ко входам установки в нуль счетных декад единиц, десятков и сотен, а вторые выходы декад десятых и сотых долей коэффициента деления соединены со входами соответствующих дешифраторов и кодовыми входами соответствующих мультиплексоров, информационные входы которых соединены - с первыми выходами соответствующих блоков сдвига, а выходы - с первыми входами соответствующих триггеров сдвига, вторые входы которых соединены с выходами соответствующих дешифраторов, при этом выход триггера сдвига десятых долей коэффициента деления соединен с первым входом блока управления сдвигом единиц, выход которого соединен с первым входом блока сдвига единиц, второй вход блока управления сдвигом единиц соединен с первым входом блока управления сдвигом десятых долей коэффициента деления и выходом триггера сдвига сотых долей коэффициента деления, третий вход - со вторым выходом блока сдвига десятых долей коэффициента деления, первый вход которого соединен с выходом блока управления сдвигом десятых долей коэффициента деления, второй вход которого соединен со вторым выходом блока сдвига сотых долей коэффициента деления, а вторые входы блоков сдвига единиц, десятых и сотых долей коэффициента деления соединены с шинами управления. На чертеже изображена структурная электрическая схема делителя частоты следования импульсов. Он содержит счетные декады 1-5 единиц десятков, сотен, десятых и сотых долей коэффициента деления, мультиплексоры 6-10, блоки 11 - 13 сдвига единиц, десятых и со-. тых долей коэффициента деления, блок 14 фиксации, блок 15 обнуления,блок 16 переноса, триггеры 17 и 18 сдвига десятых и сотых долей коэффициента деления, блоки 19 и 20 управления сдвигом единиц и десятых долей коэффициента деления, инвертор 21, дешифраторы 22 и 23 нуля счетных декад, шину 24 входную, шину 25 выходную, щину 26 выходную счетной декады сотых долей коэффициента деления, шину 27 управления сдвигом сотых долей, выходную шину 28 триггера тысячных долей коэффициента деления, шины 29-33 управления. Рассмотрим работу устройства на примере реализации коэффициента с двумя дробными разрядами где KO,K,,KJ. -целая часть, десятые, сотые доли коэффициента деления соответственно. Для получения Ktp необходимо коэффициент () получить Ki рЗЗ, а коэффициент (Ко+-.-) - (lOO-Ki) раз, т.е. в ста циклах счета необходимо изменять коэффициент с Ко+-- й на (менять программу десятых долей с 1С( на KI -f 1). При целочисленном коэффициенте деления сдвига на единицу коэффициента деления счетной декады 1 не происходит. Работает делитель в этом случае следующим образом. В исходном состоянии на шине 24 делителя присутствует низкий уровень входного сигнала FO . Все счетные декады делителя находятся в нулевом состоянии (0000). На шины 31-33 подаются сигналы высокого уровня, которые задают соответственно единицы, десятки и сотни коэффициента деления делителя. На шины 29 и 30 подаются сигналы низкого уровня, которые запрещают установку соответственно сотых и десятых долей, коэффициента деления делителя. На щине 25 установлен низкий уровень сигнала. Импульсная последовательность FO (высокий уровень входного сигнала) с периодом следования То непрерывно поступает с шины 24 на первый вход блока 14 и через инвертор 21 на счетный вход счетной декады 1 и первый вход блока 15. Все счетные декады 1-5 работают в коде 8-4-2-1. Выходы каждой счетной декады соединены с кодирующими входами (вход кода) соответствующего мультиплексора, за исключением выходов, счетной декады единиц, у которой выходы с двоичным весом 2° и 2 непосредственно соединеныс кодирующими входами мультиплексора единиц коэффициента деления, а выходы счетной декады единиц с двоичным весом 2 и 2 соединены через блок 16 с кодирующими входами мультиплексора единиц соответственно. Сигнал А на шине 25 появляется с высоким уровенем в моменты времени, определяемые следующим общим логическим уравнением: .) где Л члпянп гг гтг гитюгч/г гг nnrMJQDO п, -СИМВОЛ логического произведения выходных сигналов мультиплексоров единиц, десятков и т.д. коэффициента деления; -выходной сигнал j-ro мультиплексора;-номер мультиплексора делителя. Для осуществления деления с дробным коэффициентом деления в делителе проводится подсчет циклов деления (кратный десяти) и осуществление сдвига на единицу коэффициента деления, устанавливаемого на информационном входе , мультиплексора 6. Подсчет циклов производят счетные декады 4 и 5. Сдвиг К{ на единицу осуществляет блок 11 Дешифраторы нуля выдают выходной сигнал при состоянии счетных декад 0000, мультиплексоров 9 и 10 при состояниях на кодирующих входах, соответствующих информационным входам п и HL . В общем случае делитель содержит j (j 0,-1,...,-), групп сдвига взаимосвязанных устройств 4, 9, 12, 17, 20 и 22, причем число групп сдвига равно числу разрядов десятичной дроби. Схема управления сдвигом в общем виде описывается обобщенным логическим уравнением j-4j-iv T.-axgЦ--r -i JS; - выходной сигнал блока управления сдвигом j-ои группы сдви га; Тг --1-выходной сигнал триггера сдви га (J - 1) группы сдвига; Tii-z.-выходной сигнал триггера сдвига (J-2) группы сдвига; х - вход установки 9 (j-1) группы сдвига; 3(,-1,,..-ео)-номер группы сдвига; ч О-группа сдвига единиц коэффициента деления; J-i-группа сдвига десятых долей коэффициента деления и т.д. Схема управления сдвигом управляет соответствующим блоком сдвига, выходной сигнал которого описывается логическим уравнением ; / -. . . ,,.sj, -входы i и (i+1) установки j-oro блока сдвига на единицу дробных долей коэффициента деления; j 0,-l,...-«e Особеностью мультиплексоров 7, 8 и т.д. является то, что их информационные входы непосредственные входы установки десятков, сотен и т.д. коэффициента деления. При получении коэффициентов деления с дробями, когда число единиц равно 9 (на Хд-присутствует высокий уровень сигнала), блок 11 под воздействием сигнала соответствующего блока 19 подает управляющий сигнал на информационный вход п°ц мультиплексора б, что приводит делитель к ложному рабочему режиму, потому что счетная декада имеет наибольщий двоичный код 1001. Во избежание ошибок в данной ситуации (когда число единиц устанавливается на 9 и необходимо для получения дробности увеличить коэффициент на единицу в определенных циклах счета, т.е. получить 10), введен блок 16, который задерживает на один период следования То заполнение счетной декады 2 и формирует на входе кода мультиплексора 6 двиочный вектор 1010, соответствующий информационному входу nj. Следовательно, ри работе делителя управляющий сигнал п на информационные входы мультиплексора 6 подается высоким уровнем на один из 11 входов, т.е. 1 0,...,10, а на информационные входы остальных мультиплексоров подается собственный управляющий сигнал п высоким уровнем на один из 10 входов, т.е. i 0,...,9. В общем виде коэффициент деления предлагаемого делителя определяется из арифметического выражения . Кс..1х1.0 Последняя формула справедлива для всех значений КецЯ и характеризует диапазон изменения коэффициента деления делителя. Формула изобретения Делитель частоты следования импульсов с дробным коэффициентом деления, содержащий счетные декады единиц, десятков, сотен, десятых и сотых долей коэффициента деления, блоки сдвига единиц, десятых и сотых долей коэффициента деления, блок переноса, первый вход которого соединен с выходом счетной декады единиц, второй вход с первым выходом блока сдвига единиц, а первый выход - со счетным входом счетной декады десятков, первый вь1ход которой соединен со счетным входом счетной декады сотен, и блок фиксации, выход которого соединен со счетным входом счетной декады десятых долей коэффициента деления, первый выход которой соединен со счетным входом счетной декады сотых долей коэффициента деления, отличающийся тем, что, с целью расщирения функциональных возможностей при одновременном упрощении, в него введены блок обнуления, дешифраторы, триггеры сдвига десятых и сотых долей коэффициента деления, блоки управления сдвигом единиц и десятых долей коэффициента деления, мутилиплексоры и инвертор, вход которого подключен к входной щине, первому входу блока фиксации и третьему входу блока переноса, а выход - к счетному входу счетно декады единиц и первому входу блока обнуления, второй, третиЙ и четвертый входы которого соединены с соответствующими входами блока фиксации н выходами соответствующих мультиплексоров, первый вход первого из которых соединен со вторым выходом блока переноса, информационный вход - со вторым выходом блока сдвига единиц, первые входы второго и третьего мультиплексоров со вторыми выходами счетных декад десятков и сотен, а информационные входы - с шиной управления при этом выход блока обнуления подключен ко входам установки в нул1 счетных декад единиц, десятков и сотен, а вторые выходы декад десятых и сотых долей коэффициента деления соединены со входами соответствующих дещифраторов и кодовыми входами соответствующих мультиплексоров, информационные входы которых соединены - с первыми выходами соответствующих блоков сдвига, а выходы с первыми входами соответствующих триггеров сдвига, вторые входы которых соединены с выходами соответствующих дещифраторов, при этом выход триггера сдвига десятых долей коэффициента делення соедииен с первым входом блока управления сдви гом единиц, выход которого соединен с первым входом блока сдвига единиц, второй вход блока управления сдвигом единиц соединен с первым входом блока управления сдвигом десятых долей коэффициента деления и выходом триггера сдвига сотых долей коэффициента деления, третий вход - со вторым выходом блока сдвига десятых долей коэффициента делення, первый вход которого соединен с выходом блока управления сдвигом десятых долей коэффициента деления, вtopoй вход которого соединен со вторым выходом блока сдвига сотых долей, коэффициента деления, а вторые входы блоков сдвига единиц, десятых и сотых долей коэффициента делення соединены с шннами управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 506130, кл. Н 03 К 23/00, 17.01.74. 2.Авторское свидетельство СССР № 436446, кл. Н 03 К 25/00, 05.10.71.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным дробным коэффициентом деления | 1989 |

|

SU1746530A1 |

| Устройство для вычисления отношения временных интервалов | 1985 |

|

SU1317459A1 |

| Делитель частоты импульсов | 1979 |

|

SU845292A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧАСТОТЫ С ДРОБНЫМ КОЭФФИЦИЕНТОМ | 1971 |

|

SU436446A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1117837A1 |

| Устройство для динамической индикацииВРЕМЕНи СуТОК и КАлЕНдАРя | 1978 |

|

SU805244A2 |

| Цифровой измеритель отношения временных интервалов | 1986 |

|

SU1390595A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Делитель частоты с изменяемым коэффициентом деления | 1979 |

|

SU783996A1 |

| Делитель частоты с изменяемым коэффициентом деления | 1980 |

|

SU900459A2 |

Авторы

Даты

1981-03-30—Публикация

1979-04-23—Подача