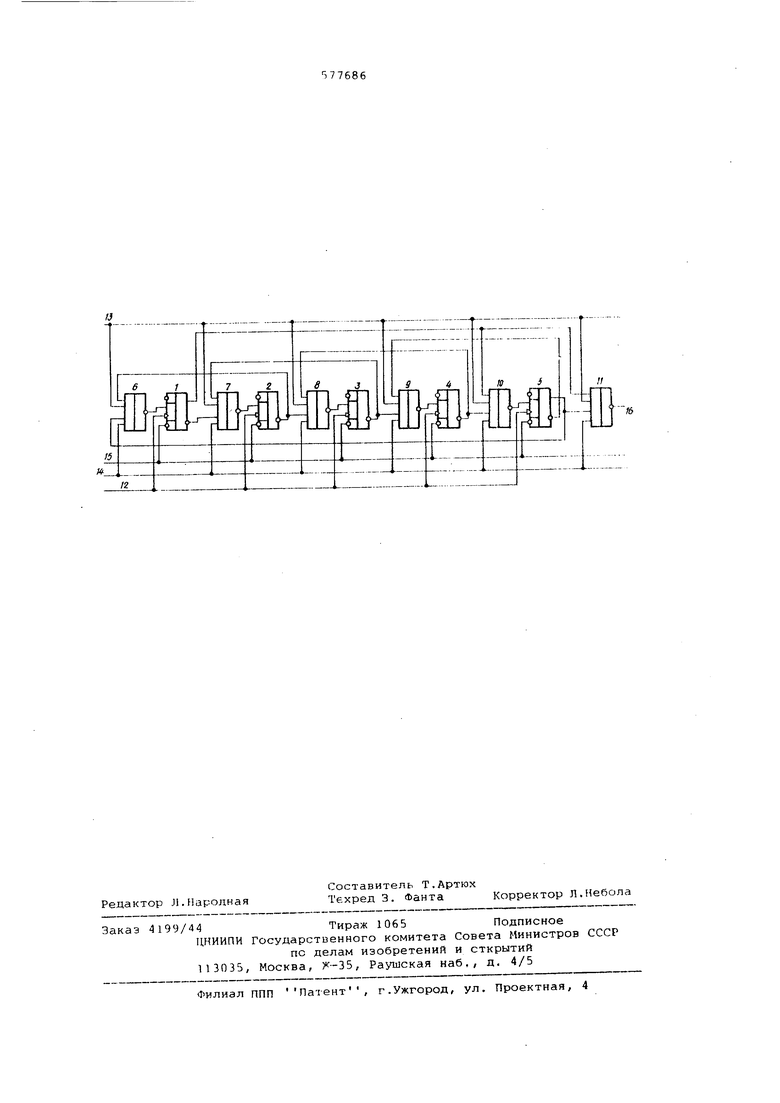

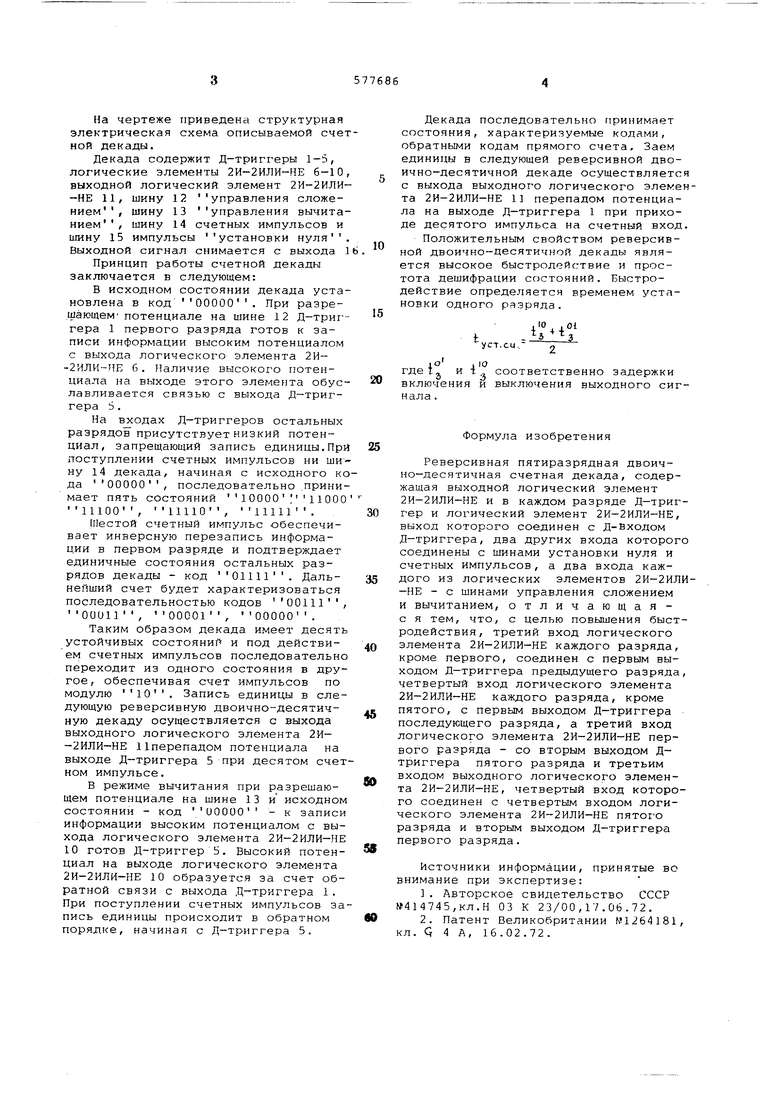

:54) РЕВЕРСИВНАЯ ПЯТИРАЗРЯДНАЯ ДВОИЧНО-ДЕСЯТИЧНАЯ СЧЕТНАЯ ДЕКАДА На чертеже приведена структурная электрическая схема описываемой счет ной декады. Декада содержит Д-триггеры 1-5, логические элементы 2И-2ИЛИ-1Е 6-10 выходной логический элемент 2И-2ИЛИ- -НЕ 11, шину 12 управления сложением, шину 13 управления вычитанием , шину 14 счетных импульсов и шину 15 импульсы установки нуля Выходной сигнал снимается с выхода Принцип работы счетной декады заключается в следующем: В исходном состоянии декада уста 00000 При разреновлена в код шающем потенциале на шине 12 Д-трИ1 гера 1 первого разряда готов к записи информации высоким потенциалом с выхода логического элемента 2И-2ИЛИ ЯЕ 6. Наличие высокого потенциала на выходе этого элемента обус лавливается связью с выхода Д-триггера 5 . На входах Д-триггеров остальных разрядов присутствует низкий потенциал, запрещающий запись единицы.При поступлении счетных импульсов ни ши ну 14 декада, начиная с исходного ко да 00000 , последовательно .прини мает пять состояний 1 0000.11000 11100, 11110, 41111. Пестой счетный импульс обеспечивает инверсную перезапись информации в первом разряде и подтверждает единичные состояния остальных разрядов декады - код 01111. Дальнейший счет будет характеризоваться последовательностью кодов 00111 00011 , 00001 , 00000 . Таким образом декада имеет десять устойчивых состояний и под действием счетных импульсов последовательно переходит из одного состояния в другое, обеспечивая счет импульсов по Запись единицы в слемодулюдующую реверсивную двоично-десятичную декаду осуществляется с выхода выходного логического элемента 2И-2ИЛИ-НЕ 11перепадом потенциала на выходе Д-триггера 5 при десятом счет ном импульсе. В режиме вычитания при разрешающем потенциале на шине 13 и исходном UOOOO состоянии - код - к записи информации высоким потенциалом с выхода логического элемента 2И-2ИЛИ-НЕ 10 готов Д-триггер 5. Высокий потенциал на выходе логического элемента 2И-2ИЛИ-НЕ 10 образуется за счет обратной связи с выхода Д-триггера 1 . При поступлении счетных импульсов за пись единицы происходит в обратном порядке, начиная с Д-триггера 5. Декада последовательно принимает состояния, характеризуемые кодами, обратными кодам прямого счета. Заем единицы в следующей реверсивной двоично-десятичной декаде осуществляется с выхода выходного логического элемента 2И-2ИЛИ-НЕ 11 перепадом потенциала на выходе Д-триггера 1 при приходе десятого импульса на счетный вход. Положительным свойством реверсивной двоично-десятичной декады является высокое быстродействие и простота дешифрации состояний. Быстродействие определяется временем установки одного разряда, ,10 01 t УСТ.СЦ..- 2 11, ,j соответственно задержки включения и выключения выходного сигнала . Формула изобретения Реверсивная пятиразрядная двоично-десятичная счетная декада, содержащая выходной логический элемент 2И-2ИЛИ-НЕ и в каждом разряде Д-триггер и логический элемент 2И-2ИЛИ-НЕ, выход которого соединен с Д-входом Д-триггера, два других входа которого соединены с шинами установки нуля и счетных импульсов, а два входа каждого из логических элементов 2И-2ИЛИ-НЕ - с шинами управления сложением и вычитанием, отличающаяс я тем, что, с целью повышения быстродействия, третий вход логического элемента 2И-2ИЛИ-НЕ каждого разряда, кроме первого, соединен с первым выходом Д-триггера предыдущего разряда, четвертый вход логического элемента 2И-2ИЛИ-НЕ каждого разряда, кроме пятого, с первым выходом Д-триггера последующего разряда, а третий вход логического элемента 2И-2ИЛИ-НЕ первого разряда - со вторым выходом Дтриггера пятого разряда и третьим входом выходного логического элемента 2И-2ИЛИ-НЕ, четвертый вход которого соединен с четвертым входом логического элемента 2И-2ИЛИ-НЕ пятогО разряда и вторым выходом Д-триггера первого разряда. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР №414745,кл.Н 03 К 23/00,17.06.72. 2.Патент Великобритании М1264181, кл, Q 4 А, 16,02.72,

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1117837A1 |

| Устройство для измерения девиации частоты линейно-частотно-модулированного колебания | 1989 |

|

SU1711087A1 |

| РЕВЕРСИВНАЯ ДВОИЧНО-ДЕСЯТИЧНАЯ ДЕКАДА | 1970 |

|

SU272692A1 |

| Делитель частоты с переменным дробным коэффициентом деления | 1989 |

|

SU1746530A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для контроля напряжения | 1989 |

|

SU1613964A1 |

| Адаптивный формирователь опережающего синхросигнала | 1988 |

|

SU1554110A1 |

| Цифровой измерительный неуравновешанный мост | 1978 |

|

SU789767A1 |

| РЕВЕРСИВНАЯ ПЕРЕСЧЕТНАЯ ДЕКАДА | 1969 |

|

SU238249A1 |

| Цифровой измеритель магнитной индукции | 1988 |

|

SU1644054A1 |

Авторы

Даты

1977-10-25—Публикация

1976-02-04—Подача