Изобретение относится к цифровой и вычислительной технике и может быть использовано при построении высоконадежных устройств на основе однотипных

резервируемых блоков

/

Известно устройство для контроля вычислительных машин, содержащее два резервируемых блока (машины), элемент сравнения, триггер, коммутатор, элементы И и ИЛИ.

Недостатком указанного устройства является низкая надежность, обусловленная наличием лишь двух резервируемых блоков, и невозможность обеспечения работоспособности при двух отказах.

Известно устройство для реконфигурации резервируемых блоков, содержащее четыре резервируемых блока, пять коммутаторов, шесть элементов сравнения, четыре счетчика, четыре мажоритарных элемента, элементы И и ИЛИ

Недостатком указанного устройства является низкая надежность, обусловленная тем, что отказ хотя бы одного из элементов

сравнения может привести к отказу всего устройства.

Наиболее близким по технической сущности и достигаемому положительному эффекту является устройство, содержащее первый-четвертый резервируемые блоки, первый и второй элементы сравнения, коммутатор, причем выход первого резервируемого блока соединен с первым входом первого элемента сравнения, выход которого соединен с первым управляющим входом коммутатора, выход которого соединен с первым управляющим входом коммутатора, выход которого является выходом данных устройства, выход второго резервируемого блока соединен с первым втором второго элемента сравнения, выход кбторого соединен с вторым управляющим входом коммутатора, выход третьего резервируемого блока соединен с вторым входом первого элемента сравнения и первым информационным входом коммутатора, выход четвертого резервируемого блока соединен с вторым входом второго элемента сравнения

сл

с

ч сл о

00

ю

00

и вторым информационным входом коммутатора.

Недостатком известного устройства является низкая надежность, обусловленная тем,что неисправностьдвух резервируемых блоков, выходы которых контролируются различными схемами сравнения, приводит к отказу устройства в целом, так как отсутствует возможность поиска и выбора другой двухканальной работоспособной конфигу- рации, составленной из оставшихся исправных резервируемых блоков.

Кроме того, недостатком известного устройства является низкая достоверность выдаваемой информации (низкая достовер- ность контроля). Так, если один из блоков, контролируемых одной схемой сравнения, отказал, то на выходе схемы сравнения появится ноль, который блокирует соответствующий вход коммутатора. Однако, если в процессе дальнейшего функционирования откажет и второй резервируемый блок, выход которого соединен с другим входом того же элемента сравнения, и информация на выходах этих блоков совпадает (либо совпа- дает периодически), то в коммутаторе происходит смешивание рабочей и ложной информации, что приводит к выдаче на выход устройства неверной выходной последовательности.

Целью изобретения является повышение надежности и достоверности контроля устройства.

Сущность изобретения состоит в увеличении надежности устройства и достовер- ности выдаваемой информации путем обеспечения сохранения работоспособной конфигурации резервируемых блоков при любых двух отказавших до возникновения отказа в третьем из четырех блоков, блоки- рования выходов элементов сравнения, осуществляющих контроль резервируемых блоков, которые признаны отказавшими, а также обеспечения сохранения работоспособности устройства при отказе одного из элементов сравнения,

Введение регистра и обусловленных им связей необходимо для исключения попадания на выход данных устройства ложной информации, которая появляется на выходе первого коммутатора с момента отказа одного из резервируемых блоков до момента блокирования соответствующего информационного выхода первого коммутатора.

Введение третьей-шестой схем сравне- ния и обусловленных ими связей необходимо для обеспечения попарного контроля выходов резервируемых блоков

Введение первого-четвертого счетчиков, первого-шестого элементов ИЛИ и

обусловленных ими связей необходимо для обеспечения блокирования выходов соответствующих элементов сравнения при отказе резервируемых блоков.

Введение седьмого элемента И, второ- го-пятого коммутаторов обусловленных ими связей необходимо для обеспечения работы устройства после появления первого отказавшего резервируемого блока.

Введение первого-четвертого мажоритарных элементов и обусловленных ими связей необходимо для определения первого отказавшего резервируемого блока даже при отказе одного из трех элементов сравнения, контролирующих ею выходы.

Введение первого-четвертого элементов И и обусловленных ими связей необходимо для определения второго отказавшего блока.

Введение пятого элемента И и обусловленных им связей необходимо для определения состояния устройства, при котором отказавшими признаны три из четырех резервируемых блоков.

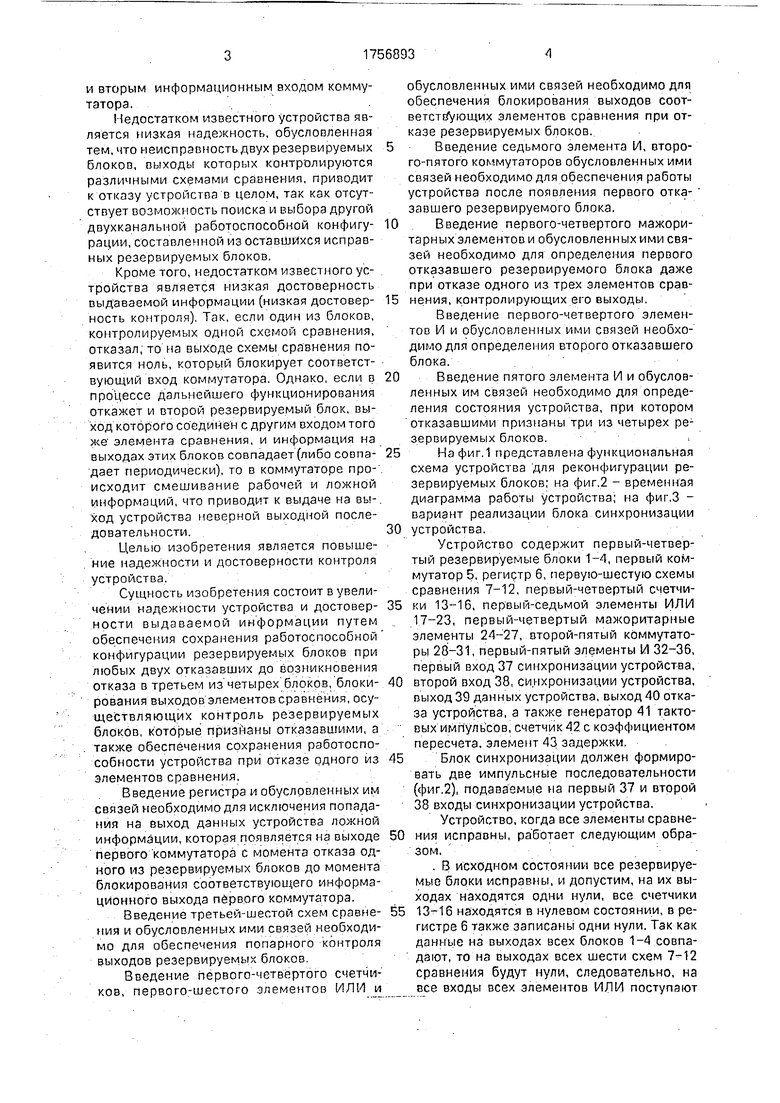

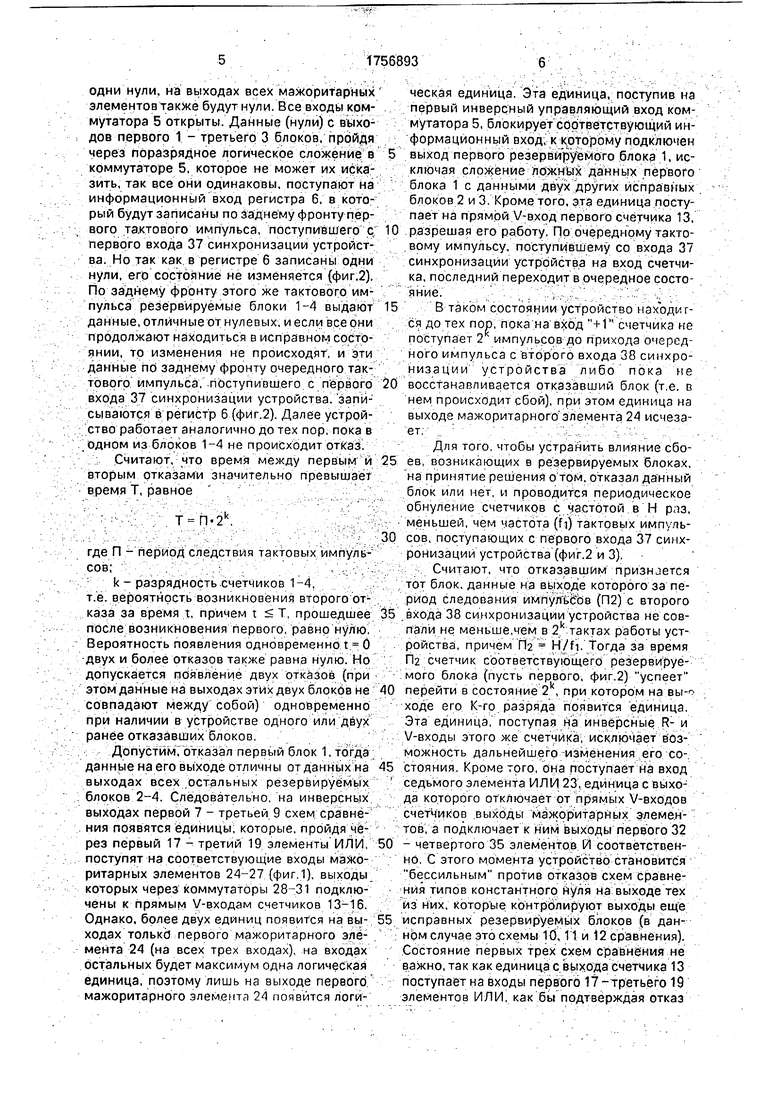

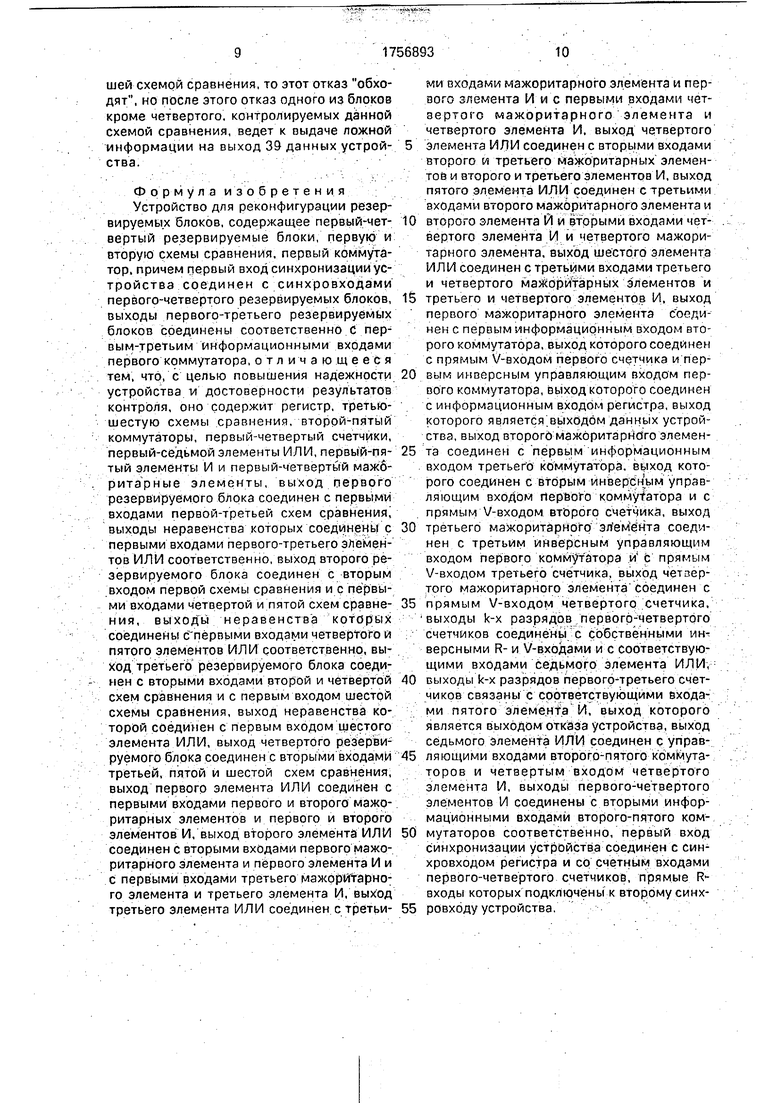

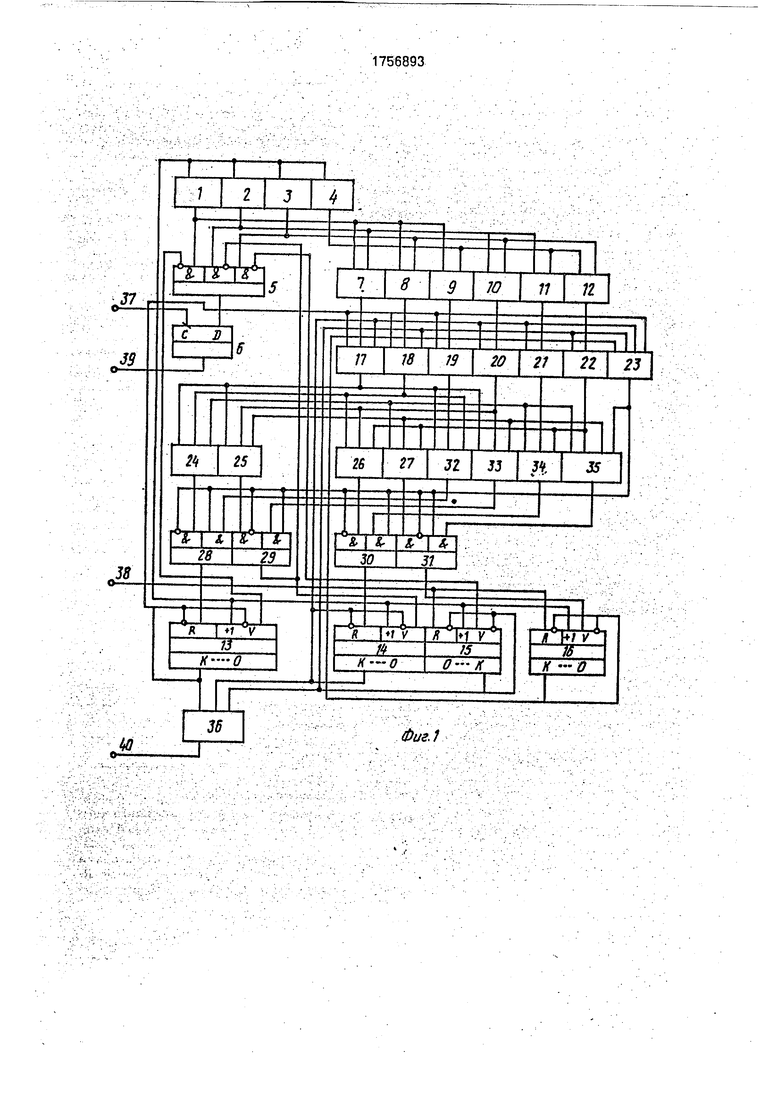

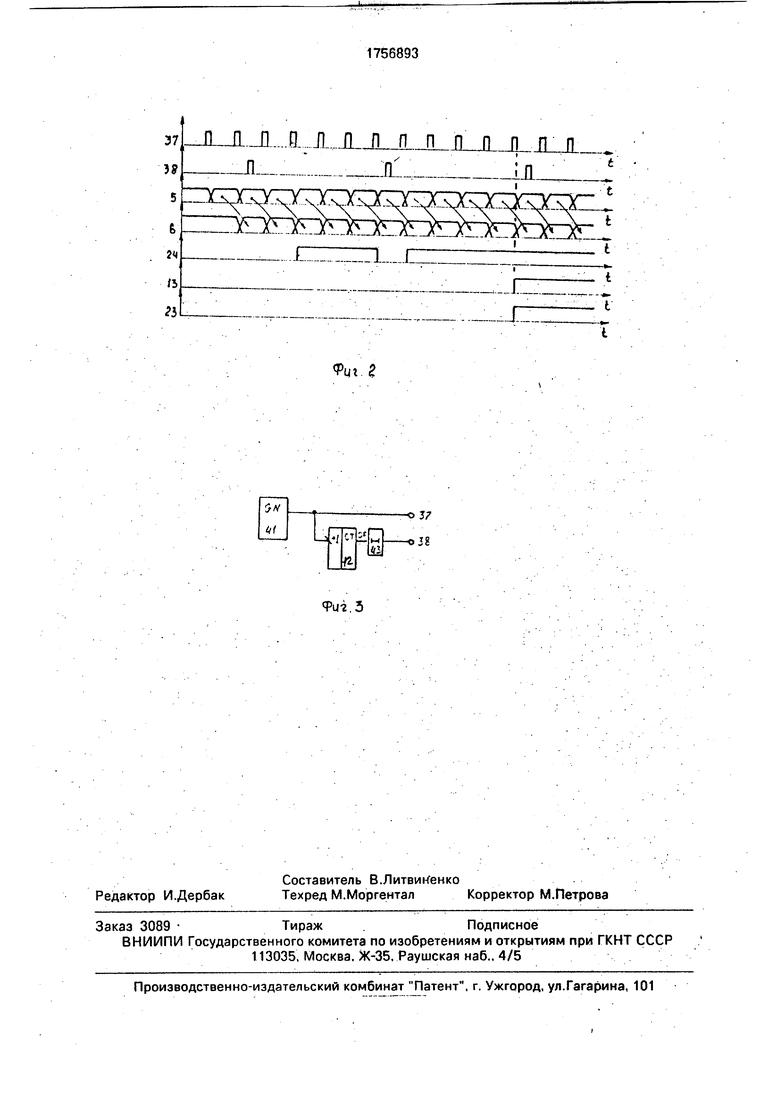

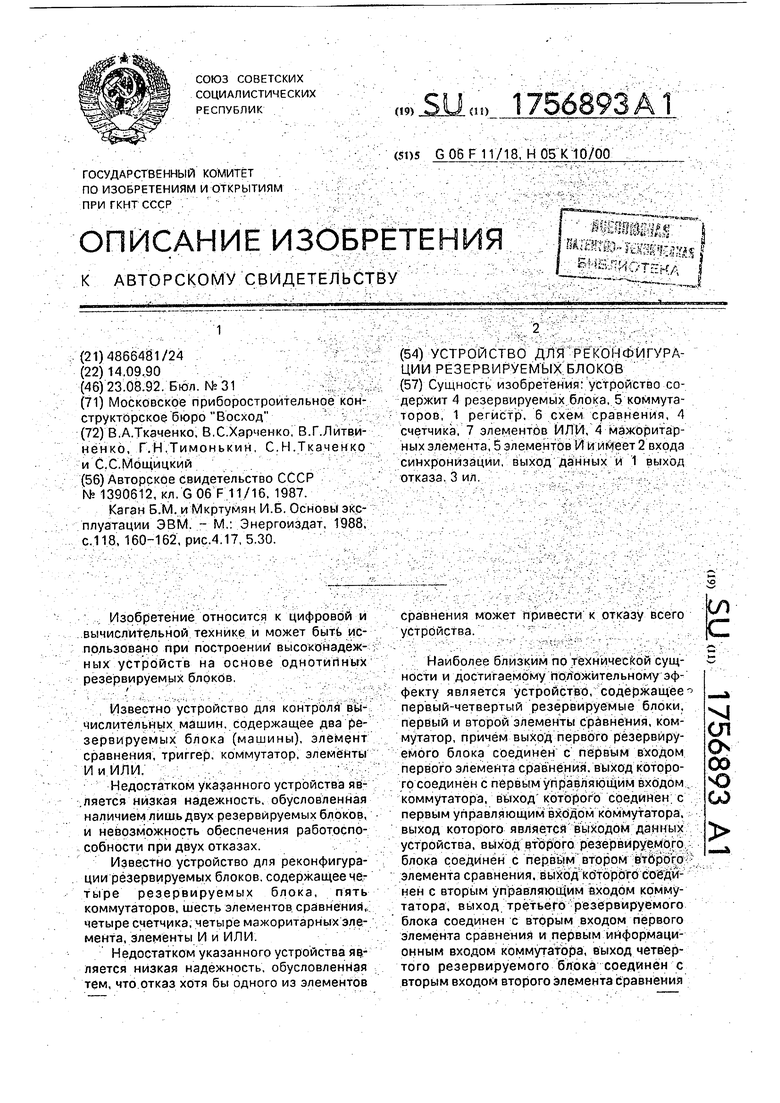

На фиг.1 представлена функциональная схема устройства для реконфигурации резервируемых блоков; на фиг.2 - временная диаграмма работы устройства; на фиг.З - вариант реализации блока синхронизации устройства.

Устройство содержит первый-четвер- тый резервируемые блоки 1-4, первый коммутатор 5, регистр б, первую-шестую схемы сравнения 7-12, первый-четвертый счетчики 13-16, первый-седьмой элементы ИЛИ 17-23, первый-четвертый мажоритарные элементы 24-27, второй-пятый коммутаторы 28-31, первый-пятый элементы И 32-36, первый вход 37 синхронизации устройства, второй вход 38, синхронизации устройства, выход 39 данных устройства, выход 40 отказа устройства, а также генератор 41 тактовых импульсов, счетчик 42 с коэффициентом пересчета, элемент 43 задержки.

Блок синхронизации должен формировать две импульсные последовательности (фиг.2), подаваемые на первый 37 и второй 38 входы синхронизации устройства.

Устройство, когда все элементы сравнения исправны, работает следующим образом.

. В исходном состоянии все резервируемые блоки исправны, и допустим, на их выходах находятся одни нули, все счетчики 13-16 находятся в нулевом состоянии, в регистре 6 также записаны одни нули. Так как данные на выходах всех блоков 1-4 совпадают, то на выходах всех шести схем 7-12 сравнения будут нули, следовательно, на все входы всех элементов ИЛИ поступают

одни нули, на выходах всех мажоритарных элементов также будут нули. Все входы коммутатора 5 открыты. Данные (нули) с выходов первого 1 - третьего 3 блоков, пройдя через поразрядное логическое сложение в коммутаторе 5, которое не может их исказить, так все они одинаковы, поступают на информационный вход регистра 6, в который будут записаны по заднему фронту первого тактового импульса, поступившего с первого входа 37 синхронизации устройства. Но так как в регистре 6 записаны одни нули, его состояние не изменяется (фиг.2). По заднему фронту этого же тактового импульса резервируемые блоки 1-4 выдают данные, отличные от нулевых, и если все они продолжают находиться в исправном состоянии, то изменения не происходят, и эти данные по заднему фронту очередного тактового импульса, поступившего с первого входа 37 синхронизации устройства, записываются в регистр 6 (фиг.2). Далее устройство работает аналогично до тех пор, пока в одном из блоков 1-4 не происходит отказ.

Считают, что время между первым и вторым отказами значительно превышает время Т, равное

T n-2k.

где П - период следствия тактовых импульсов;

k - разрядность счетчиков 1-4, т.е. вероятность возникновения второго отказа за время t, причем t 2 Т, прошедшее после возникновения первого, равно нулю. Вероятность появления одновременно t О двух и более отказов также равна нулю. Но допускается появление двух отказов (при этом данные на выходах этих двух блоков не совпадают между собой) одновременно при наличии в устройстве одного или двух ранее отказавших блоков

Допустим, отказал первый блок 1, тогда данные на его выходе отличны от данных на выходах всех остальных резервируемых блоков 2-4. Следовательно на инверсных выходах первой 7 - третьей 9 схем сравнения появятся единицы, которые, пройдя через первый 17 - третий 19 элементы ИЛИ, поступят на соответствующие входы мажоритарных элементов 24-27 (фиг 1), выходы которых через коммутаторы 28-31 подключены к прямым V-входам счетчиков 13-16. Однако, более двух единиц появится на вы- ходах только первого мажоритарного элемента 24 (на всех трех входах), на входах остальных будет максимум одна логическая единица, поэтому лишь на выходе первого мажоритарного элемента 24 появится логи50 5 0

5

0

5 0

5 0 5

ческая единица. Эта единица, поступив на первый инверсный управляющий вход коммутатора 5, блокирует соответствующий информационный вход, к которому подключен выход первого резервируемого блока 1, исключая сложение ложных данных первого блока 1 с данными двух других исправных блоков 2 и 3. Кроме того, эта единица поступает на прямой V-вход первого счетчика 13, разрешая его работу. По очередному тактовому импульсу, поступившему со входа 37 синхронизации устройства на вход счетчика, последний переходит в очередное состояние.

В таком состоянии устройство находится до тех пор, пока на вход +1 счетчика не поступает 2 импульсов до прихода очередного импульса с второго входа 38 синхронизации устройства либо пока vie восстанавливается отказавший блок (те. с нем происходит сбой), при этом единица на выходе мажоритарного элемента 24 исчезает

Для того чтобы устранить влияние сбоев, возникающих в резервируемых блоках, на принятие решения о том. отказал данный блок или нет, и проводится периодическое обнуление счетчиков с частотой в Н раз, меньшей, чем частота (fi) тактовых импульсов, поступающих с первого входа 37 синхронизации устройства (фиг.2 и 3).

Считают, что отказавшим признается тот блок, данные на выходе которого за период следования импульсГов (П2) с второго входа 38 синхронизации устройства не совпали не меньше,чем в 2 тактах работы устройства, причем Пг H/fi. Тогда за время счетчик соответствующего резервируемого блока (пусть первого, фиг 2) успеет перейти в состояние 2 , при котором на вы- ходе его К-ro разряда появится единица. Эта единица, поступая на инверсные R- и V-входы этого же счетчика, исключает возможность дальнейшего изменения его состояния. Кроме того, она поступает на вход седьмого элемента ИЛИ 23, единица с выхода которого отключает от прямых V-входов счетчиков выходы мажоритарных элементов, а подключает к ним выходы первого 32 - четвертого 35 элементов И соответственно С этого момента устройство становится бессильным против отказов схем сравнения типов константного нуля на выходе тех из них, которые контролируют выходы еще исправных резервируемых блоков (в данном случае это схемы 10,11 и 12 сравнения). Состояние первых трех схем сравнения не важно, так как единица с выхода счетчика 13 поступает на входы первого 17-третьего 19 элементов ИЛИ, как бы подтверждая отказ

данного блока. В случае отказа второго блока 2 единица поступаете выхода счетчика 14 на входы первого 17, четвертого 20 и пятого 21 элементов ИЛИ, при отказе же третьего 3 - на входы второго 18, четвертого 20 и шестого 22, а при отказе четвертого 4 - на входы третьего 19, пятого 21 и шестого 22 элементов ИЛИ

Далее устройство ожидает появление очередного отказавшего блока. Допустим, отказал второй блок 2, тогда на выходе четвертой 10 и пятой 11 схем сравнения появляются единицы, которые через элементы ИЛИ 20 и 21 поступают на соответствующие входы элементов И 32-35 (фиг.2). Теперь единица присутствует на выходе не только первого элемента И 32 (она там появилась после отказа первого блока), но и на выходе второго элемента И 33, так как на всех трех его входах теперь единичные потенциалы. Остальные же два элемента И 34 и 35 сохраняют нули на своих выходах, так как на одном из сходов - нуль, поступающий с выхода схемы 12 сравнения (третий 3 и четвертый 4 блоки исправны) через элемент ИЛИ 22 Единица с выхода элемента И 33 поступает через коммутатор 29 на второй инверсный управляющий вход коммутатора 5, блокируя тем самым выход блока 2, а также на прямой V-еход второго счетчика 14, разрешая ему режим прямого счета После того, как счетчик переходит в состояние, при котором на выходе его К-ro разряда появляется единица, ею блокируются четвертый 10 и пятый 11 элементы сравнения (она поступает на входы элементов ИЛИ 20 и 21) Далее устройство ожидает отказа одного из оставшихся двух блоков 3 или 4. Их состояние контролирует единственная неблокированная схема 12 сравнения. При отказе одного из этих блоков единица с выхода схемы 12 сравнения, пройдя через элемент ИЛИ 22, поступает на входы элементов И 34, 35, открывая последние. Единица с выходов И 34 и 35 через коммутаторы 30 и 31 поступает на прямые V-входы счетчиков 15 и 16. Кроме того, единица с выхода коммутатора 30 поступает на третий управляющий вход коммутатора 5, блокируя последний его выход, очередным тактовым импульсом с входа 37 в регистр 6 записываются только нули. Кроме того, теперь на всех трех входах пятого элемента И 36 присутствуют единицы, поступающие с выходов соответствующих коммутаторов 28-30, единица с выхода элемента И 36 поступает на выход 40 отказа устройства, сигнализируя 0 том, что в устройстве отказало более двух резервируемых блоков

В случае же, если после отказа одного из блоков в устройстве возник групповой отказ последних (одновременно отказало два или три блока), то на выходах всех злементов сравнения присутствуют единицы, что приводит к их появлению на выходах всех элементов И 32-36. Ситуация аналогична описанной, но условием при этом является то, что данные на выходах отказавших

0 блоков не совпадают между собой.

Устройство в условиях отказа схем сравнения работает следующим образом. Отказ схемы сравнения может быть двух видов: ложный нуль, т.е. данные на входах его не

5 совпадают, а на инверсном выходе все равно нулевой потенциал (константный нуль); и ложная единица - данные совпадают, а на выходе - единица (константная единица). Отказы второго вида в предлагаемом и

0 известных устройствах могут привести лишь к преждевременном выдаче сигнала об отказе устройства в целом, исключая незамеченное попадание на выход 39 данных устройства ложных данных. Отказы типа

5 константного нуля опаснее, такой отказ ведет к необнаружению несовпадения данных на выходах действительно отказавшего блока. Во всех известных устройствах появления такого отказа хотя бы в одной из схем

0 сравнения приводит к выдаче ложных данных на выход данных устройства при отказе хотя бы одного из блоков, контролируемых отказавшей схемой сравнения.

Рассматривают случай, когда отказ типа

5 константного нуля произошел в одной из схем сравнения в момент, когда все резервируемые блоки еще исправны. Допустим, отказала третья схема 9 сравнения. Возможны два алгоритма работы устройства в

0 этом случае. Это событие обнаруживается пятой 11 и шестой 12 схемами сравнения, и четвертый мажоритарный элемент 27 на основании единичных потенциалов, поступивших на два из трех его входов, принимает

5 решение об отказе четвертого блока. После того, как счетчик отсчитывает 2k тактов, единицы поступят на входы третьего 19, пятого 21 и шестого 22 элементов ИЛИ, замаскировав тем самым отказавшую схему 9 сравне0 ния, исключив влияние нуля с ее выхода на дальнейшую работу устройства. После обнаружения первого отказавшего блока устройство теряет способность адаптации к Отказам схем сравнения, и отказ типа кон5 стантного нуля в любом из еще не замаскированных схем сравнения может привести к выдаче ложных данных на выход 39 данных устройства.

По второму алгоритму, если происходит отказ блока, неконтролируемого отказавшей схемой сравнения, то этот отказ обходят, но после этого отказ одного из блоков кроме четвертого, контролируемых данной схемой сравнения, ведет к выдаче ложной информации на выход 39 данных устройства.

Формула изобретения Устройство для реконфигурации резервируемых блоков, содержащее первый-чет- вертый резервируемые блоки, первую и вторую схемы сравнения, первый коммутатор, причем первый вход синхронизации устройства соединен с синхровхоДами перйого-четвертого резервируемых блоков, выходы первого-третьего резервируемых блоков соединены соответственно С первым-третьим информационными входами первого коммутатора, отличающееся тем, что, с целью повышения надежности устройства и достоверности результатов контроля, оно содержит регистр, третью- шестую схемы сравнения, второй-пятый коммутаторы, первый-четвертый счетчики, первый-седьмой элементы ИЛИ, первый-пя- тый элементы И и первый-четвертый мажоритарные элементы, выход первого резервируемого блока соединен с первыми входами первой-третьей схем сравнения, выходы неравенства которых соединены с первыми входами первого-третьего элементов ИЛИ соответственно, выход второго резервируемого блока соединен с вторым входом первой схемы сравнения и с первыми входами четвертой и пятой схем сравнения, выходы неравенства которых соединены с первыми входами четвертого и пятого элементов ИЛИ соответственно, выход третьего резервируемого блока соединен с вторыми входами второй и четвертой схем сравнения и с первым входом шестой схемы сравнения, выход неравенства которой соединен с первым входом шестого элемента ИЛИ, выход четвертого резервируемого блока соединен с вторыми входами третьей, пятой и шестой схем сравнения, выход первого элемента ИЛИ соединен с первыми входами первого и второго мажоритарных элементов и первого и второго элементов И, выход второго элемента ИЛИ соединен с вторыми входами первого мажоритарного элемента и первого элемента И и с первыми входами третьего мажоритарного элемента и третьего элемента И, выход третьего элемента ИЛИ соединен с третьими входами мажоритарного элемента и первого элемента И и с первыми входами четвертого мажоритарного элемента и четвертого элемента И, выход четвертого

элемента ИЛИ соединен с вторыми входами второго и третьего мажоритарных элементов и второго и третьего элементов И, выход пятого элемента ИЛИ соединен с третьими входами второго мажоритарного элемента и

второго элемента И и вторыми входами четвертого элемента И и четвертого мажоритарного элемента, выход шестого элемента ИЛИ соединен с третьими входами третьего и четвертого мажоритарных элементов и

третьего и четвертого элементов И, выход первого мажоритарного элемента Соединен с первым информационным входом второго коммутатора, выход которого соединен с прямым V-входом первого счетчика и первым инверсным управляющим входом первого коммутатора, выход которого соединен с информационным входом регистра, выход которого является выходом данных устройства, выход второго мажоритарного элемента соединен с первым информационным входом третьего коммутатора, выход которого соединен с вторым инверсным управляющим входом Первого коммутатора и с прямым V-входом второго счетчика, выход

третьего мажоритарного эл ем ента соединен с третьим инверсным управляющим входом первого коммутатора и с прямым V-входом третьего счетчика, выход четзер- того мажоритарного элемента соединен с

прямым V-входом четвертого счетчика, выходы k-x разрядов первого-четвертого счетчиков соединены с собственными инверсными R- и V-входами и с соответствующими входами седьмого элемента ИЛИ,

выходы k-x разрядов первого-третьего счетчиков связаны с соответствующими входами пятого элемента И, выход которого является выходом отказа устройства, выход седьмого элемента ИЛИ соединен с управляющими входами второго-пятого коммутаторов и четвертым входом четвертого элемента И, выходы первого-четвертого элементов И соединены с вторыми информационными входами второго-пятого коммутаторов соответственно, первый вход синхронизации устройства соединен с син- хровходом регистра и со счетным входами первого-четвертого счетчиков, прямые R- входы которых подключены к второму синхровходу устройства.

JLJLJ Q- Л ППППП.ПППП Q.. Д1IJL

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для оперативной реконфигурации резервированной системы | 1990 |

|

SU1727125A1 |

| Устройство для реконфигурации резервируемых блоков | 1990 |

|

SU1748155A1 |

| Устройство для контроля и реконфигурации резервируемых блоков | 1990 |

|

SU1800456A1 |

| Резервируемое устройство | 1990 |

|

SU1732505A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1990 |

|

SU1716628A1 |

| Резервированная система | 1982 |

|

SU1089771A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1991 |

|

SU1820385A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1989 |

|

SU1667280A1 |

| Устройство микропрограммного управления диагностированием и восстановлением цифровых систем | 1984 |

|

SU1624456A1 |

Сущность изобретения1 устройство содержит 4 резервируемых блока, 5 коммутаторов, 1 регистр. 6 схем сравнения, 4 счетчика, 7 элементов ИЛИ, 4 мажоритарных элемента, 5 элементов И и имеет 2 входа синхронизации, выход данных и 1 выход отказа. 3 ил

Фцг 2

Pu 3

| Устройство для контроля вычислительных машин | 1986 |

|

SU1390612A1 |

| Каган Б.М | |||

| и Мкртумян И.Б | |||

| Основы эксплуатации ЭВМ | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-08-23—Публикация

1990-09-14—Подача