Изобретение относится к автоматике и вычислительной технике и может быть использовано в резервируемых цифровых системах, выполненных на БИС и СБИС, в качестве устройства, осуществляющего реконфигурацию структуры в соответствии с результатами контроля на основе метода гибридного резервирования

Известно устройство, содержащее три резервируемых блока, три мажоритарных элемента, три схемы сравнения, генератор импульсов, дешифратор, регистры перестройки и контроля, три элемента И, преобразователь кода.

Недостатком данного устройства является низкая надежность.

Из известных устройств наиболе.е близким к предлагаемому по технической сущности и достигаемому эффекту является устройство для реконфигурации резервированной системы, содержащее с первого по третий резервируемые блоки, с первого по третий мажоритарные блоки, с первой по третью схемы сравнения, генератор импульсов, коммутаторы перестройки и прерывания, первый и второй триггеры прерывания, дешифратор, регистры перестройки и контроля, шифратор и мажоритарный элемент, с первого по третий элементы И, преобразователь кода контроля в код перестройки и коммутатор записи, причем выходы с первого по третий резервируемых блоков соединены с соответствующими входами с первой по третью схем сравнения и соответствующими информационными входами с- первого по третий мажоритарных блоков,: выходы

VI ГО XI

ю ел

оторых являются информационными выхоами устройства, вход результатов контроя устройства соединен с информационным входом регистра, выход которого соединен входом преобразователя кода контроля в код перестройки, первый выход дешифратора соединен с управляющими входами коммутатора записи, выход которого соединен с управляющим входом регистра перестройки, выход регистра перестройки соеинен с управляющими входами с первого по третий мажоритарных блоков, выходы с первой по третью схем сравнения соединены с первыми информационными входами коммутатора прерывания, выход которого соединен с D-входом первого триггера прерывания, первым информационным входом коммутатора записи и через шифратор с первым информационным входом коммутатора перестройки, входы прерывания, конца команды и конца контроля устройства соединены соответственное вторым информационным входом коммутатора прерывания и первыми входами первого и второго элементов И, первый выход генератора импульсов соединен с входом синхронизации регистра перестройки с С-входом первого триггера прерывания, прямой выход которого соединен с первым входом дешифратора и вторым входом первого элемента И, выход которого соединен с S-входом второго триггера прерывания, прямой выход которого является выходом прерывания устройства и соединен с вторым входом дешифратора, первый выход которого соединен с первым управляющим входом коммутатора перестройки и V-входом вто- рого триггера прерывания, второй выход - с первым входом третьего элемента И, вторым информационным входом коммутатора записи и вторым управляющим входом коммутатора перестройки, а третий выход - с вторым входом второго элемента И, второй выход генератора импульсов соединен с третьими входами первого и второго элементов И и вторым входом третьего элемента И, выход которого соединен с С- и К-входами второго триггера прерывания, выход рторого элемента И соединен с R-вхо- дом первого триггера прерывания и входом синхронизации регистра контроля, выход разрядов которого соединен с входами мажоритарного элемента, выход которого соединен с управляющим входом коммутатора прерываний, выход преобразователя кода контроля в код перестройки соединен с вторым информационным входом коммутатора перестройки, выход которого соединен с информационным входом регистра перестройки.

Недостатком данного устройства является низкая надежность, обусловленная невозможностью использования резервируемых блоков с внутренним резервированием части (или всей) схемы блока.

Целью изобретения является увеличение надежности устройства.

Сущность изобретения заключается: в увеличении надежности устройства за

счет использования блоков резервируемых элементов с внутренним резервированием части (или всей) схемы блока, причем команда переключения на резерв подается извне, а не самим блоком; схема внутреннего контроля в блоке отсутствует;

в увеличении надежности устройства за счет увеличения гибкости алгоритма резервирования, реализованного аппаратным путем, что позволяет оперативно, в реальном

масштабе времени выполнять переключение на резерв (и обратно при сбое) при отказе части блока без тестирования последнего при появлении более чем одного отказа (сбоя) в устройстве.

Введение формирователя сигнала отказа и обусловленных им связей необходимо для определения такого состояния устройства, при котором окончательно отказавшими признаны два или три резервируемых

блока. Это состояние отказа устройства в целом назовем фатальным отказом (ФО).

Введение первого-третьего элементов ИЛИ и третьего триггера переключения и обусловленных ими связей необходимо для

организации коммутации управляющих импульсов с выходов дешифратора состояния на С-входы соответствующего счетчика состояния,

Первый-третий счетчики состояния и

обусловленные ими связи необходимы для организации непосредственного управления переключением на резерв и обратно в первом-третьем резервируемых блоках соответственно, а также для определения состояния соответствующих резервируемых блоков: работоспособное или окончательный отказ.

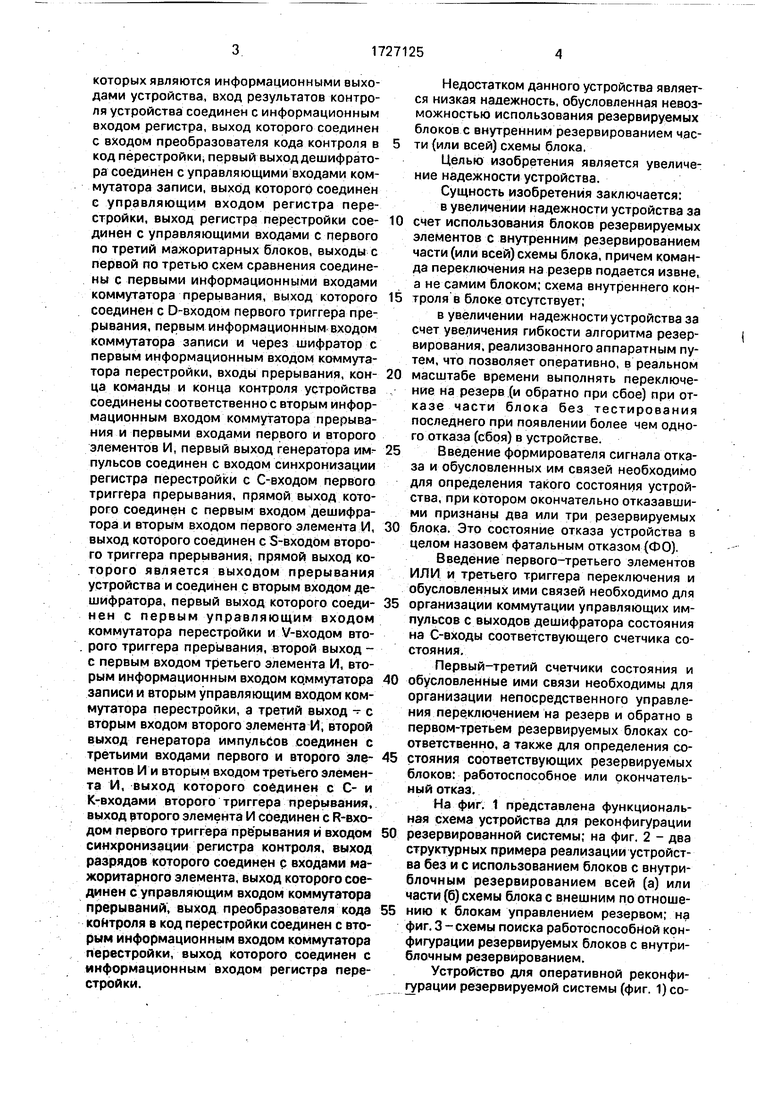

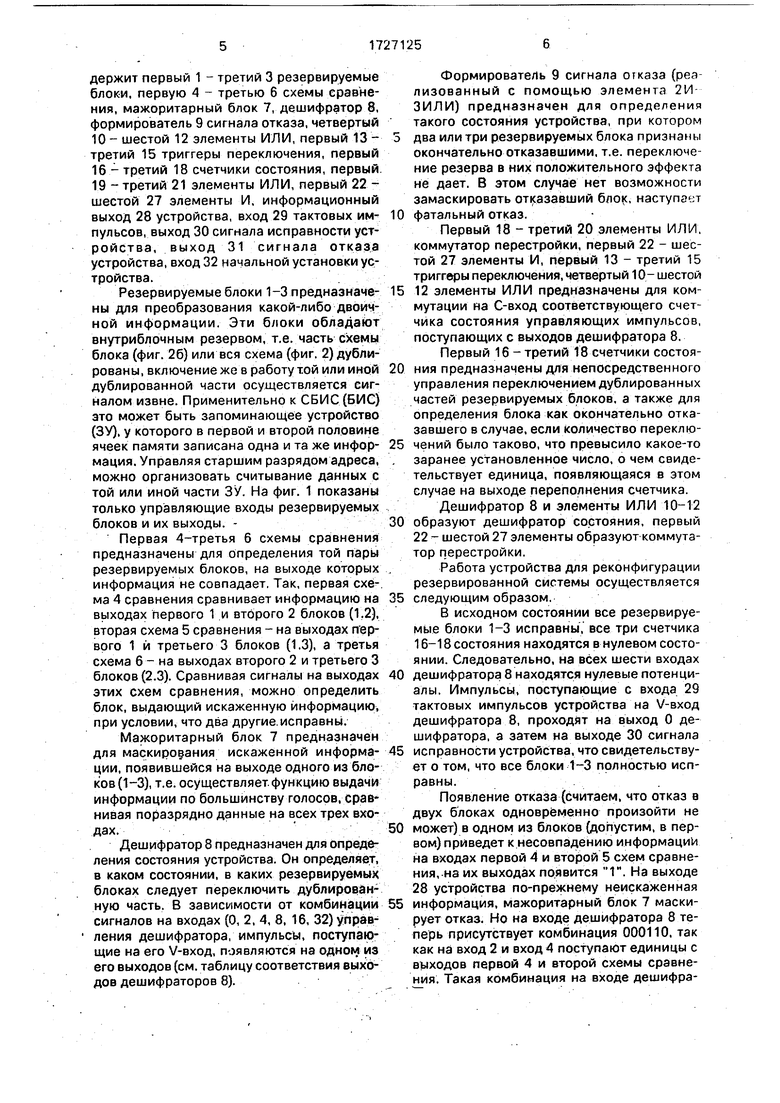

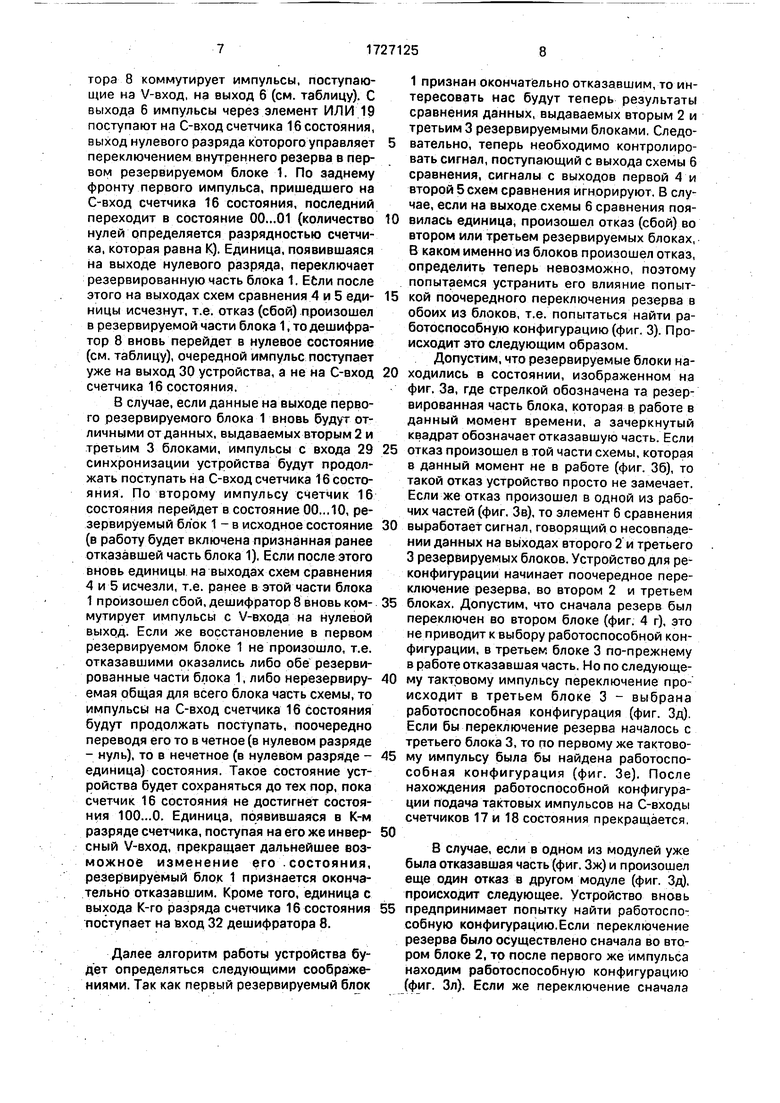

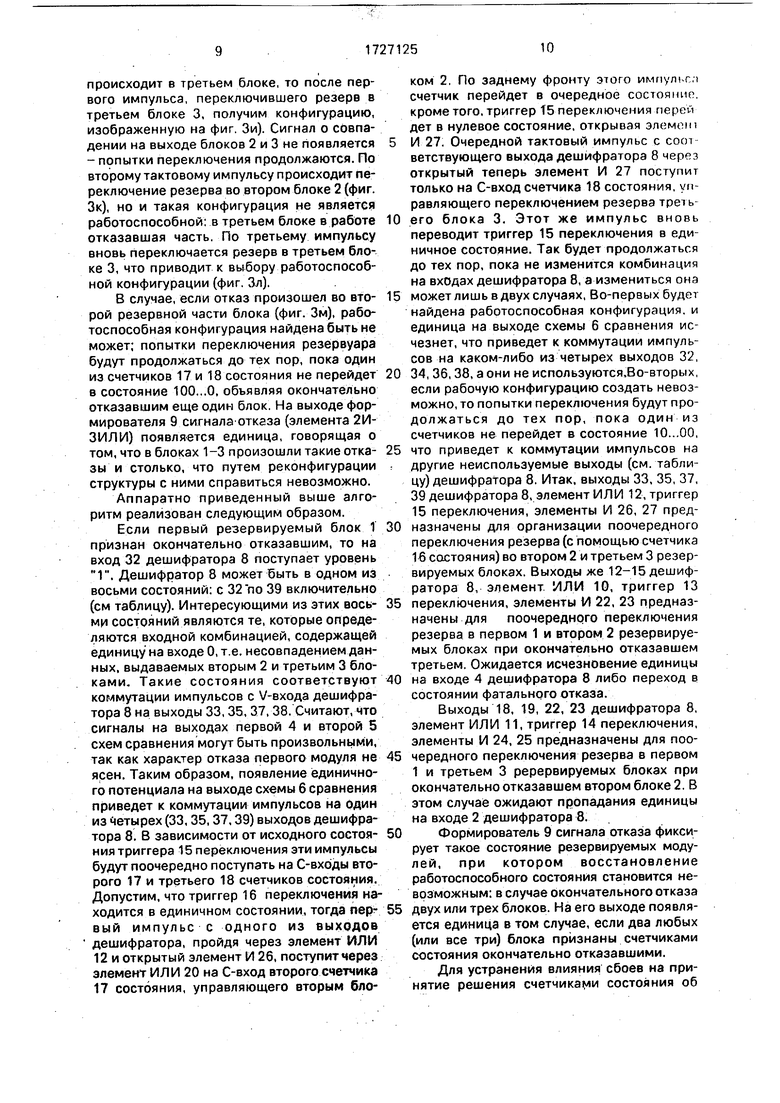

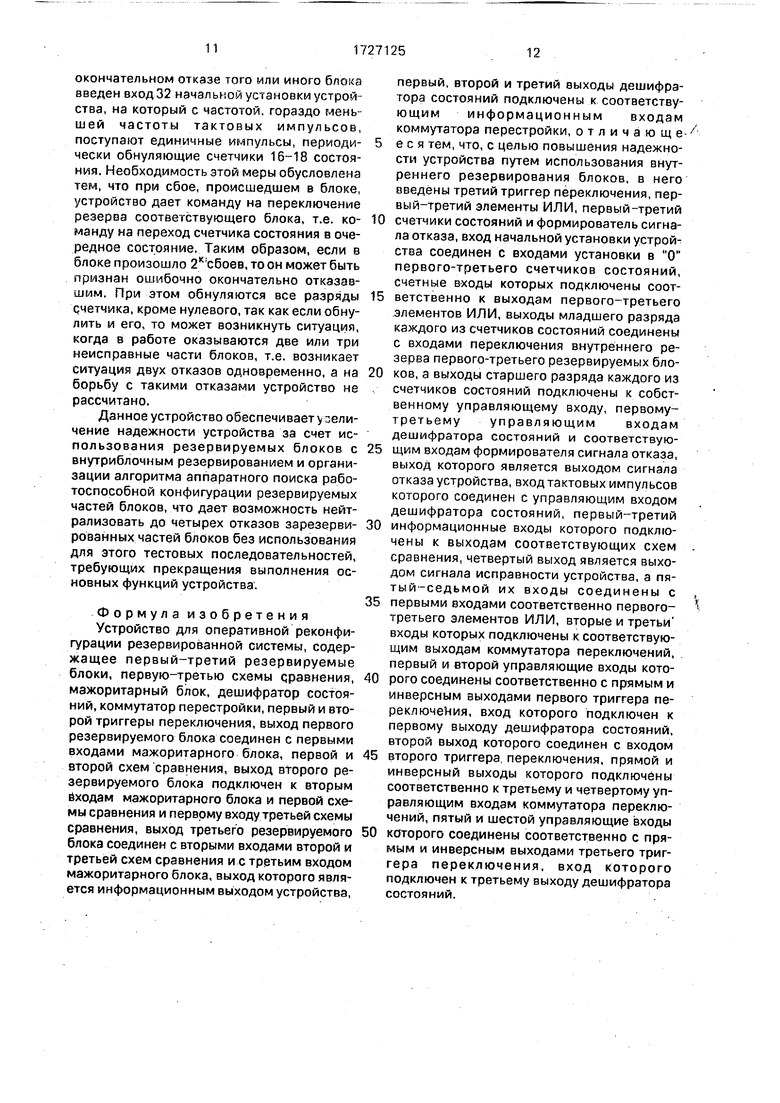

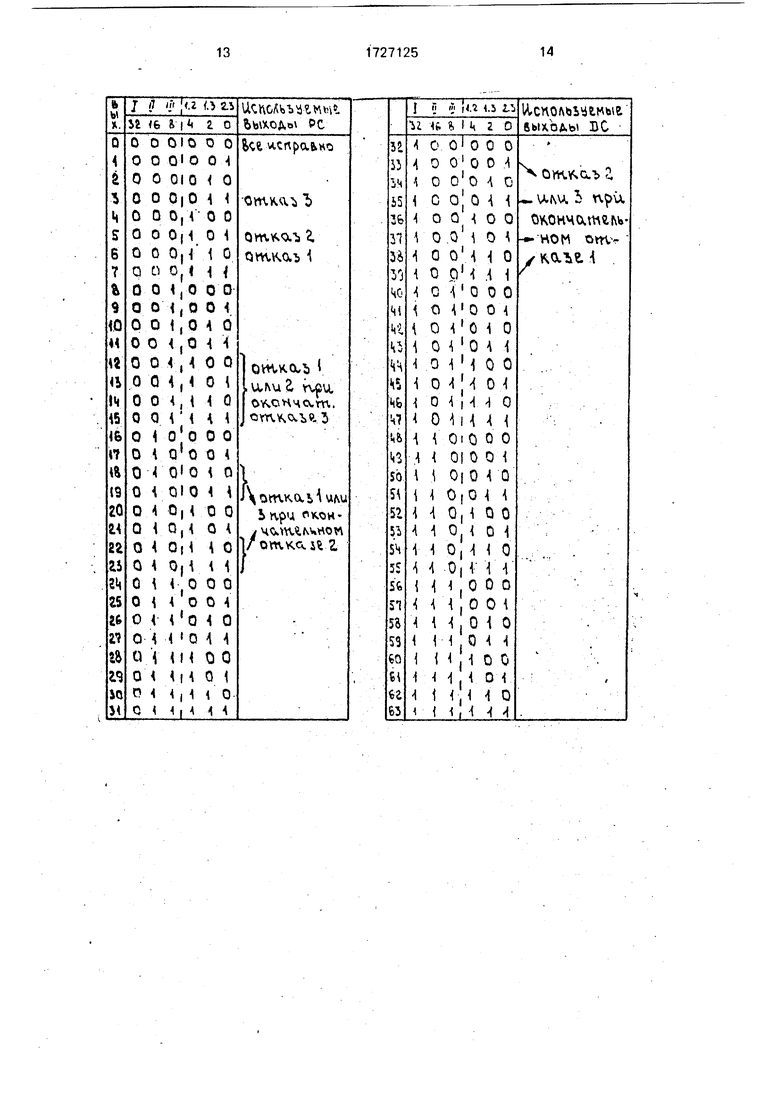

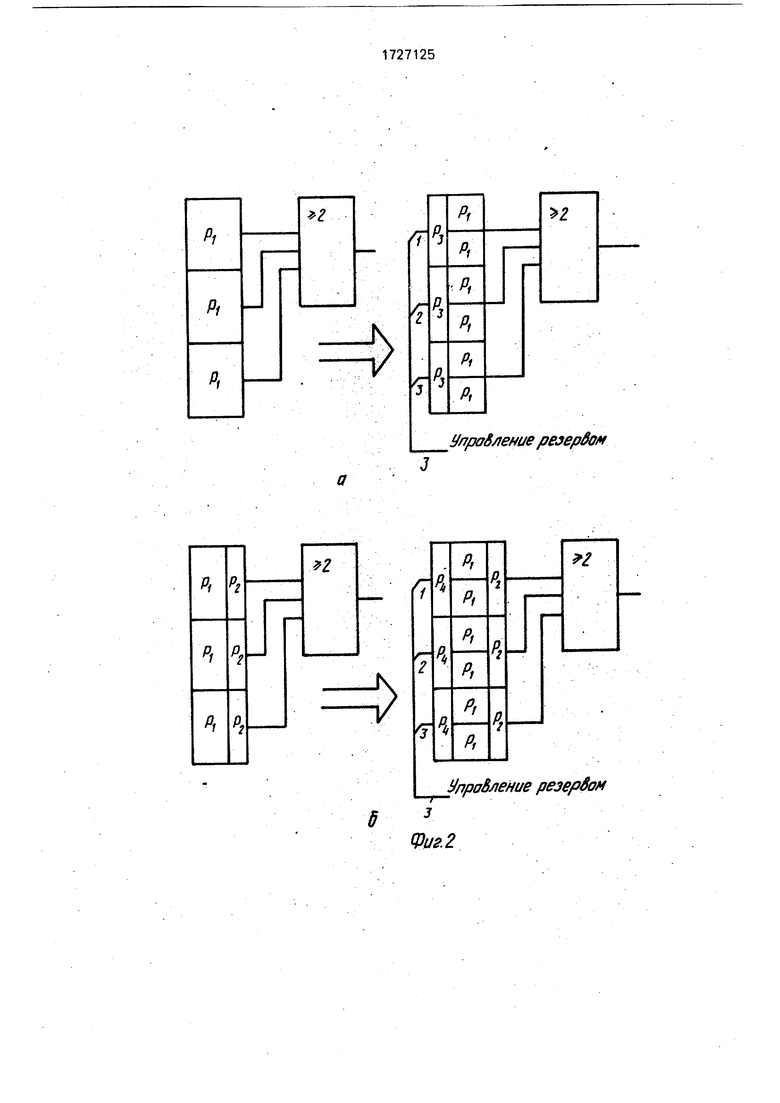

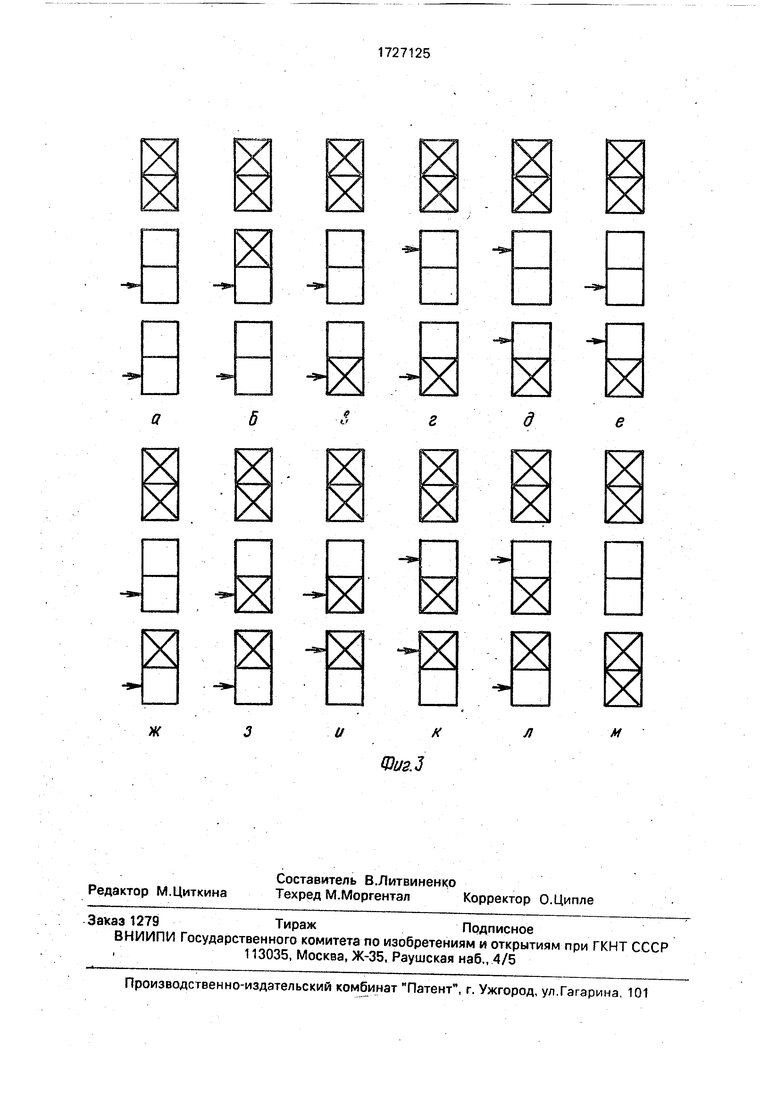

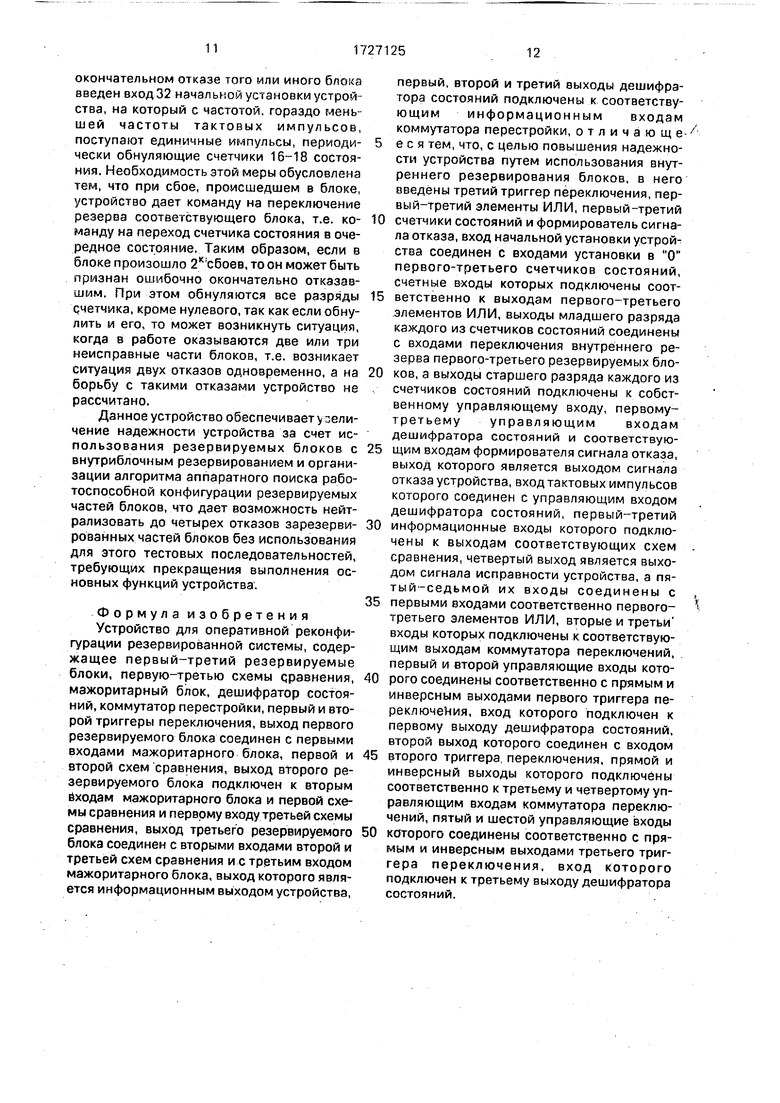

На фиг. 1 представлена функциональная схема устройства для реконфигурации

резервированной системы; на фиг. 2 - два структурных примера реализации устройства без и с использованием блоков с внутри- блочным резервированием всей (а) или части (б) схемы блока с внешним по отношению к блокам управлением резервом; на фиг. 3 -схемы поиска работоспособной конфигурации резервируемых блоков с внутри- блочным резервированием.

Устройство для оперативной реконфигурации резервируемой системы (фиг. 1) содержит первый 1 - третий 3 резервируемые блоки, первую 4 - третью 6 схемы сравнения, мажоритарный блок 7, дешифратор 8, формирователь 9 сигнала отказа, четвертый 10- шестой 12 элементы ИЛИ, первый 13- третий 15 триггеры переключения, первый 16 -третий 18 счетчики состояния, первый. 19 -третий 21 элементы ИЛИ, первый 22 - шестой 27 элементы И, информационный выход 28 устройства, вход 29 тактовых импульсов, выход 30 сигнала исправности устройства, выход 31 сигнала отказа устройства, вход 32 начальной установки устройства.

Резервируемые блоки 1-3 предназначены для преобразования какой-либо двоичной информации. Эти блоки обладают внутриблочным резервом, т.е. часть схемы блока (фиг. 26) или вся схема (фиг. 2) дублированы, включение же в работу той или иной дублированной части осуществляется сигналом извне. Применительно к СБИС (БИС) это может быть запоминающее устройство (ЗУ), у которого в первой и второй половине ячеек памяти записана одна и та же информация. Управляя старшим разрядом адреса, можно организовать считывание данных с той или иной части ЗУ. На фиг. 1 показаны только управляющие входы резервируемых блоков и их выходы. Первая 4-третья 6 схемы сравнения предназначены для определения той пары резервируемых блоков, на выходе которых информация не совпадает, Так, первая схе-. ма 4 сравнения сравнивает информацию на выходах первого 1 и второго 2 блоков (1.2), вторая схема 5 сравнения - на выходах п ер- врго 1 и третьего 3 блоков (1.3), а третья схема 6- на выходах второго 2 и третьего 3 блоков (2.3). Сравнивая сигналы на выходах этих схем сравнения, можно определить блок, выдающий искаженную информацию, при условии, что два другие.исправны.

Мажоритарный блок 7 предназначен для маскирования искаженной информации, появившейся на выходе одного из блоков (1-3), т.е. осуществляет, функцию выдачи информации по большинству голосов, сравнивая поразрядно данные на всех трех входах.

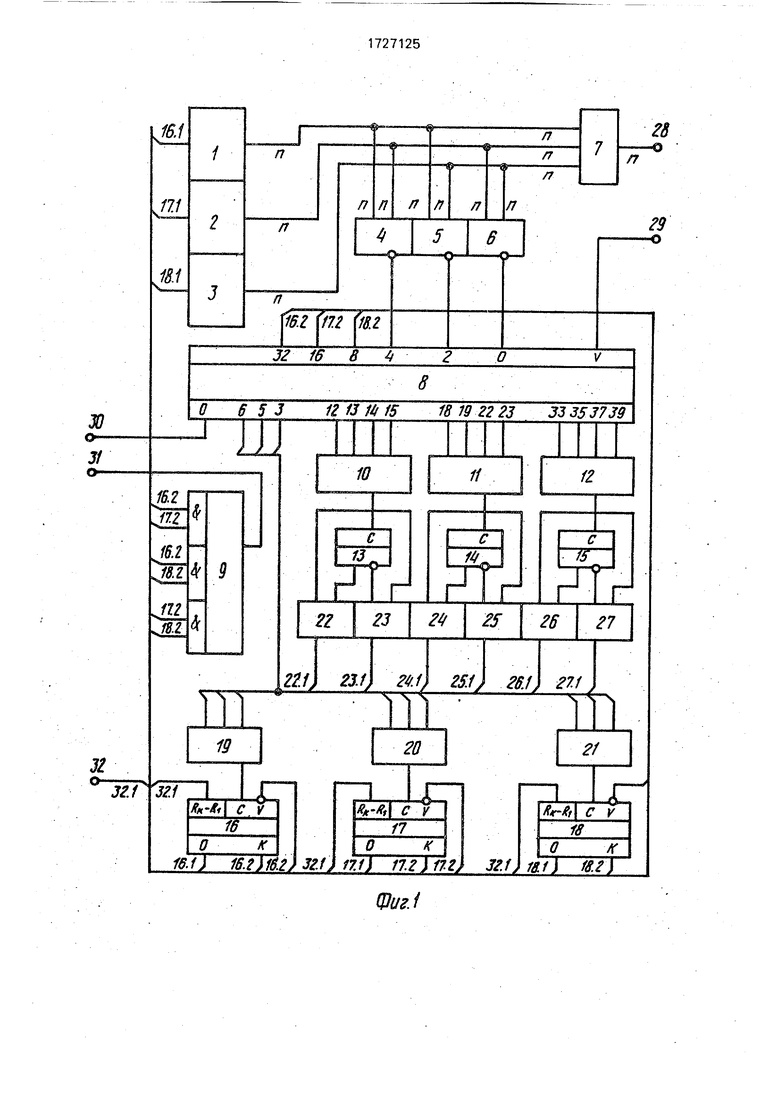

Дешифратор 8 предназначен для определения состояния устройства. Он определяет, в каком состоянии, в каких резервируемых блоках следует переключить дублированную часть. В зависимости от комбинации сигналов на входах (0, 2, 4, 8, 16, 32) управления дешифратора, импульсы, поступающие на его V-вход, появляются на одном из его выходов (см. таблицу соответствия выходов дешифраторов 8).

Формирователь 9 сигнала отказа (реализованный с помощью элемента 2И ЗИЛИ) предназначен для определения такого состояния устройства, при котором 5 два или три резервируемых блока признаны окончательно отказавшими, т.е. переключение резерва в них положительного эффекта не дает. В этом случае нет возможности замаскировать отказавший блок, наступает 0 фатальный отказ.

Первый 18 - третий 20 элементы ИЛИ. коммутатор перестройки, первый 22 - шестой 27 элементы И, первый 13 - третий 15 триггеры переключения, четвертый 10- шестой 5 12 элементы ИЛИ предназначены для коммутации на С-вход соответствующего счетчика состояния управляющих импульсов, поступающих с выходов дешифратора 8.

Первый 16 -третий 18 счетчики состоя- 0 ния предназначены для непосредственного управления переключением дублированных частей резервируемых блоков, а также для определения блока как окончательно отказавшего в случае, если количество переклю- 5 чений было таково, что превысило какое-то заранее установленное число, о чем свидетельствует единица, появляющаяся в этом случае на выходе переполнения счетчика.

Дешифратор 8 и элементы ИЛИ 10-12 0 образуют дешифратор состояния, первый 22 - шестой 27 элементы образуют коммутатор перестройки.

Работа устройства для реконфигурации резервированной системы осуществляется 5 следующим образом.

В исходном состоянии все резервируемые блоки 1-3 исправны, все три счетчика 16-18 состояния находятся в нулевом состоянии. Следовательно, на всех шести входах 0 дешифратора 8 находятся нулевые потенциалы. Импульсы, поступающие с входа 29 тактовых импульсов устройства на V-вход дешифратора 8, проходят на выход 0 дешифратора, а затем на выходе 30 сигнала 5 исправности устройства, что свидетельствует о том, что все блоки 1-3 полностью исправны.

Появление отказа (считаем, что отказ в двух блоках одновременно произойти не 0 может) в одном из блоков (допустим, в первом) приведет к несовпадению информации на входах первой 4 и второй 5 схем сравнения, на их выходах появится 1й. На выходе 28 устройства по-прежнему неискаженная 5 информация, мажоритарный блок 7 маскирует отказ. Но на входе дешифратора 8 теперь присутствует комбинация 000110. так как на вход 2 и вход 4 поступают единицы с выходов первой 4 и второй схемы сравнения. Такая комбинация на входе дешифратора 8 коммутирует импульсы, поступающие на V-вход, на выход 6 (см. таблицу). С выхода 6 импульсы через элемент ИЛИ 19 поступают на С-вход счетчика 16 состояния, выход нулевого разряда которого управляет переключением внутреннего резерва в первом резервируемом блоке 1. По заднему фронту первого импульса, пришедшего на С-вход счетчика 16 состояния, последний переходит в состояние 00...01 (количество нулей определяется разрядностью счетчика, которая равна К). Единица, появившаяся на выходе нулевого разряда, переключает резервированную часть блока 1. Если после этого на выходах схем сравнения 4 и 5 единицы исчезнут, т.е. отказ (сбой) произошел в резервируемой части блока 1, то дешифратор 8 вновь перейдет в нулевое состояние (см. таблицу), очередной импульс поступает уже на выход 30 устройства, а не на С-вход счетчика 16 состояния.

В случае, если данные на выходе первого резервируемого блока 1 вновь будут отличными отданных, выдаваемых вторым2 и третьим 3 блоками, импульсы с входа 29 синхронизации устройства будут продолжать поступать на С-вход счетчика 16 срсто- яния. По второму импульсу счетчик 16 состояния перейдет в состояние 00...10, резервируемый блок 1 - в исходное состояние (в работу будет включена признанная ранее отказавшей часть блока 1). Если после этого вновь единицы на выходах схем сравнения 4 и 5 исчезли, т.е. ранее в этой части блока 1 произошел сбой, дешифратор 8 вновь коммутирует импульсы с V-входа на нулевой выход. Если же восстановление в первом резервируемом блоке 1 не произошло, т.е. отказавшими оказались либо обе резервированные части блока 1, либо нерезервируемая общая для всего блока часть схемы, то импульсы на С-вход счетчика 16 состояния будут продолжать поступать, поочередно переводя его то в четное (в нулевом разряде - нуль), то в нечетное (в нулевом разряде - единица) состояния. Такое состояние устройства будет сохраняться до тех пор, пока счетчик 16 состояния не достигнет состояния 100...0. Единица, появившаяся в К-м разряде счетчика, поступая на его же инверсный V-вход, прекращает дальнейшее возможное изменение его .состояния, резервируемый блок 1 признается окончательно отказавшим. Кроме того, единица с выхода К-го разряда счетчика 16 состояния поступает на вход 32 дешифратора 8.

Далее алгоритм работы устройства будет определяться следующими соображениями. Так как первый резервируемый блок

1 признан окончательно отказавшим, то интересовать нас будут теперь результаты сравнения данных, выдаваемых вторым 2 и третьим 3 резервируемыми блоками. Следовательно, теперь необходимо контролировать сигнал, поступающий с выхода схемы 6 сравнения, сигналы с выходов первой 4 и второй 5 схем сравнения игнорируют. В случае, если на выходе схемы 6 сравнения поя0 вилась единица, произошел отказ (сбой) во втором или третьем резервируемых блоках, В каком именно из блоков произошел отказ, определить теперь невозможно, поэтому попытаемся устранить его влияние попыт5 кой поочередного переключения резерва в обоих из блоков, т.е. попытаться найти работоспособную конфигурацию (фиг. 3). Происходит это следующим образом.

Допустим, что резервируемые блоки на0 ходились в состоянии, изображенном на фиг. За, где стрелкой обозначена та резервированная часть блока, которая в работе в данный момент времени, а зачеркнутый квадрат обозначает отказавшую часть. Если

5 отказ произошел в той части схемы, которая в данный момент не в работе (фиг. 36), то такой отказ устройство просто не замечает. Если же отказ произошел в одной из рабочих частей (фиг, Зв), то элемент 6 сравнения

0 выработает сигнал, говорящий о несовпадении данных на выходах второго 2 и третьего 3 резервируемых блоков. Устройство для реконфигурации начинает поочередное переключение резерва, во втором 2 и третьем

5 блоках. Допустим, что сначала резерв был переключен во втором блоке (фиг. 4 г), это не приводит к выбору работоспособной конфигурации, в третьем блоке 3 по-прежнему в работе отказавшая часть. Но по следующе0 му тактовому импульсу переключение происходит в третьем блоке 3 - выбрана работоспособная конфигурация (фиг. Зд). Если бы переключение резерва началось с третьего блока 3, то по первому же тактово5 му импульсу была бы найдена работоспособная конфигурация (фиг. Зе). После нахождения работоспособной конфигурации подача тактовых импульсов на С-входы счетчиков 17 и 18 состояния прекращается.

0

В случае, если в одном из модулей уже была отказавшая часть (фиг. Зж) и произошел еще один отказ в другом модуле (фиг. Зд), происходит следующее. Устройство вновь

5 предпринимает попытку найти работоспособную конфигурацию.Если переключение резерва было осуществлено сначала во втором блоке 2, то после первого же импульса находим работоспособную конфигурацию (фиг. Зл). Если же переключение сначала

происходит в третьем блоке, то после первого импульса, переключившего резерв в третьем блоке 3, получим конфигурацию, изображенную на фиг. Зи). Сигнал о совпадении на выходе блоков 2 и 3 не появляется - попытки переключения продолжаются. По второму тактовому импульсу происходит переключение резерва во втором блоке 2 (фиг. Зк), но и такая конфигурация не является работоспособной: в третьем блоке в работе отказавшая часть. По третьему импульсу вновь переключается резерв в третьем блоке 3, что приводит к выбору работоспособной конфигурации (фиг. Зл).

В случае, если отказ произошел во вто- рой резервной части блока (фиг. Зм), работоспособная конфигурация найдена быть не может; попытки переключения резервуара будут продолжаться до тех пор, пока один из счетчиков 17 и 18 состояния не перейдет в состояние 100...О, объявляя окончательно отказавшим еще один блок. На выходе формирователя 9 сигнала отказа (элемента 2И- ЗИЛИ) появляется единица, говорящая о том, что в блоках 1-3 произошли такие отка- зы и столько, что путем реконфигурации структуры с ними справиться невозможно.

Аппаратно приведенный выше алгоритм реализован следующим образом.

Если первый резервируемый блок Т признан окончательно отказавшим, то на вход 32 дешифратора 8 поступает уровень 1. Дешифратор 8 может быть в одном из восьми состояний: с 32 по 39 включительно (см таблицу). Интересующими из этих вось- ми состояний являются те, которые определяются входной комбинацией, содержащей единицу на входе 0, т.е. несовпадением данных, выдаваемых вторым 2 и третьим 3 блоками. Такие состояния соответствуют коммутации импульсов с V-входа дешифратора 8 на выходы 33, 35, 37, 38. Считают, что сигналы на выходах первой 4 и второй 5 схем сравнения могут быть произвольными, так как характер отказа первого модуля не ясен. Таким образом, появление единичного потенциала на выходе схемы 6 сравнения приведет к коммутации импульсов на один из четырех (33,35,37,39) выходов дешифратора 8. В зависимости от исходного состоя- ния триггера 15 переключения эти импульсы будут поочередно поступать на С-входы второго 17 и третьего 18 счетчиков состояния. Допустим, что триггер 16 переключения находится в единичном состоянии, тогда пер вый импульс с одного из выходов дешифратора, пройдя через элемент ИЛИ 12 и открытый элемент И 26, поступит через элемент ИЛИ 20 на С-вход второго счетчика 17 состояния, управляющего вторым блоком 2. По заднему фронту этого импульс, счетчик перейдет в очередное состояние. кроме того, триггер 15 переключения .переидет в нулевое состояние, открывая элемет И 27. Очередной тактовый импульс с соси ветствующего выхода дешифратора 8 через открытый теперь элемент И 27 поступит только на С-вход счетчика 18 состояния, управляющего переключением резерва третьего блока 3. Этот же импульс вновь переводит триггер 15 переключения в единичное состояние. Так будет продолжаться до тех пор, пока не изменится комбинация на входах дешифратора 8, а измениться она может лишь в двух случаях, Во-первых будет найдена работоспособная конфигурация, и единица на выходе схемы 6 сравнения исчезнет, что приведет к коммутации импульсов на каком-либо из четырех выходов 32, 34, 36,38, а они не используются.Во-вторых, если рабочую конфигурацию создать невозможно, то попытки переключения будут продолжаться до тех пор, пока один из счетчиков не перейдет в состояние 10...00, что приведет к коммутации импульсов на другие неиспользуемые выходы (см. таблицу) дешифратора 8. Итак, выходы 33, 35, 37, 39 дешифратора 8, элемент ИЛИ 12, триггер

15переключения, элементы И 26, 27 предназначены для организации поочередного переключения резерва (с помощью счетчика

16состояния) во втором 2 и третьем 3 резервируемых блоках. Выходы же 12-15 дешифратора 8, элемент. ИЛИ 10, триггер 13 переключения, элементы И 22, 23 предназначены для поочередного переключения резерва в первом 1 и втором 2 резервируемых блоках при окончательно отказавшем третьем. Ожидается исчезновение единицы на входе 4 дешифратора 8 либо переход в состоянии фатального отказа.

Выходы 18, 19, 22, 23 дешифратора 8, элемент ИЛИ 11, триггер 14 переключения, элементы И 24, 25 предназначены для поочередного переключения резерва в первом 1 и третьем 3 рерервируемых блоках при окончательно отказавшем втором блоке 2. В этом случае ожидают пропадания единицы на входе 2 дешифратора 8.

Формирователь 9 сигнала отказа фиксирует такое состояние резервируемых модулей, при котором восстановление работоспособного состояния становится невозможным: в случае окончательного отказа двух или трех блоков. На его выходе появляется единица в том случае, если два любых (или все три) блока признаны счетчиками состояния окончательно отказавшими.

Для устранения влияния сбоев на принятие решения счетчиками состояния об

окончательном отказе того или иного блока введен вход 32 начальной установки устройства, на который с частотой, гораздо меньшей частоты тактовых импульсов, поступают единичные импульсы, периодически обнуляющие счетчики 16-18 состояния. Необходимость этой меры обусловлена тем, что при сбое, происшедшем в блоке, устройство дает команду на переключение резерва соответствующего блока, т.е. команду на переход счетчика состояния в очередное состояние. Таким образом, если в блоке произошло 2 сбоев. то он может быть признан ошибочно окончательно отказавшим. При этом обнуляются все разряды счетчика, кроме нулевого, так как если обнулить и его, то может возникнуть ситуация, когда в работе оказываются две или три неисправные части блоков, т.е. возникает ситуация двух отказов одновременно, а на борьбу с такими отказами устройство не рассчитано.

Данное устройство обеспечивает у оели- чение надежности устройства за счет использования резервируемых блоков с внутриблочным резервированием и организации алгоритма аппаратного поиска работоспособной конфигурации резервируемых частей блоков, что дает возможность нейтрализовать до четырех отказов зарезервированных частей блоков без использования для этого тестовых последовательностей, требующих прекращения выполнения основных функций устройства.

Формула изобретения Устройство для оперативной реконфигурации резервированной системы, содержащее первый-третий резервируемые блоки, первую-третью схемы сравнения, мажоритарный блок, дешифратор состояний, коммутатор перестройки, первый и второй триггеры переключения, выход первого резервируемого блока соединен с первыми входами мажоритарного блока, первой и второй схем сравнения, выход второго резервируемого блока подключен к вторым входам мажоритарного блока и первой схемы сравнения и первому входу третьей схемы Сравнения, выход третьего резервируемого блока соединен с вторыми входами второй и третьей схем сравнения и с третьим входом мажоритарного блока, выход которого является информационным выходом устройства,

первый, второй и третий выходы дешифратора состояний подключены к соответствующим информационным входам коммутатора перестройки, отличающее с я тем, что, с целью повышения надежности устройства путем использования внутреннего резервирования блоков, в него введены третий триггер переключения, первый-третий элементы ИЛИ, первый-третий

счетчики состояний и формирователь сигнала отказа, вход начальной установки устройства соединен с входами установки в О первого-третьего счетчиков состояний, счетные входы которых подключены соответственно к выходам первого-третьего элементов ИЛИ, выходы младшего разряда каждого из счетчиков состояний соединены с входами переключения внутреннего резерва первого-третьего резервируемых блоков, а выходы старшего разряда каждого из

счетчиков состояний подключены к собственному управляющему входу, первому- третьему управляющим входам дешифратора состояний и соответствующим входам формирователя сигнала отказа, выход которого является выходом сигнала отказа устройства, вход тактовых импульсов которого соединен с управляющим входом дешифратора состояний, первый-третий

информационные входы которого подключены к выходам соответствующих схем сравнения, четвертый выход является выходом сигнала исправности устройства, а пя- тый-седьмой их входы соединены с

первыми входами соответственно первого- третьего элементов ИЛИ, вторые и третьи входы которых подключены к соответствующим выходам коммутатора переключений, первый и второй управляющие входы которого соединены соответственно с прямым и инверсным выходами первого триггера переключения, вход которого подключен к первому выходу дешифратора состояний, второй выход которого соединен с входом

второго триггера, переключения, прямой и инверсный выходы которого подключены соответственно к третьему и четвертому управляющим входам коммутатора переключений, пятый и шестой управляющие входы

которого соединены соответственно с прямым и инверсным выходами третьего триггера переключения, вход которого подключен к третьему выходу дешифратора состояний.

16.1

л

8

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство для реконфигурации резервируемых блоков | 1990 |

|

SU1756893A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И РЕЗЕРВИРОВАНИЯ ИНФОРМАЦИОННОЙ СИСТЕМЫ | 2010 |

|

RU2453079C2 |

| Адаптивное резервированное устройство | 1983 |

|

SU1174929A1 |

| Четырехканальная резервированная система | 1990 |

|

SU1746383A1 |

| Устройство для управления реконфигурацией резервированного вычислительного комплекса | 1983 |

|

SU1149449A1 |

| Устройство для контроля и реконфигурации резервируемых блоков | 1990 |

|

SU1800456A1 |

| Мажоритарно-резервированный интерфейс памяти | 1980 |

|

SU953639A1 |

| Адаптивное четырехканальное резервированное устройство | 1990 |

|

SU1742821A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в резервируемых цифровых системах, выполненных на БИС, СБИС, в качестве устройства, осуществляющего реконфигурацию структуры в соответствии с результатами контроля на основе гибридного резервирования, Целью изобретения является повышение надежности устройства. Устройство содержит первый-третий резервируемые блоки, первую.-третью схемы сравнения, мажоритарный блок, дешифратор, формирователь сигнала отказа, четвер- тый-шестой элементы ИЛИ, первый-третий триггеры переключения, первый-третий счетчики состояния, первый-третий элементы ИЛИ, первый-шестой элементы И. 3 ил., 1 табл. (Л С

П

Л

ГШ (f7.2 Ш

32 16 8 4 2 о

x.i)i7.D П2}пг) зг.ПтП &П

л

/7

п

п

п

л

л

гэ

-о

Фиг.1

I 3

Фиг.2

К

Ж

и

л

м

Фиг.З

| Трехканальное резервированное устройство | 1972 |

|

SU463972A1 |

| Авторское свидетельство СССР № 1398652, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-15—Публикация

1990-04-16—Подача