Известны дискриминаторы знака для преобразователя аналог-цифра, основанного на способе поразрядного уравновешивания, содержащие мостовой модулятор, импульсный усилитель и фазовый детектор.

В предлагаемом дискриминаторе мостовой модулятор формирования однократного симметричного импульсного сигнала содержит две пары полупроводниковых ключей, подсоединенных один к другому колотекторами, а также к устройству управления; эмиттеры первых триодов каждой нары объединены и подсоедипешз через сопротивления к первичгюй обмотке импульспого трансформатора, средняя точка которого подключена к диодному ограничителю тока, а вторичная обмотка нодсоединепа к импульсному усилителю.

Это позволяет увеличить быстродействие преобразователя, умепьшнть влияние перегрузок на быстродействия и уменьшить потребление тока от измерительной схемы.

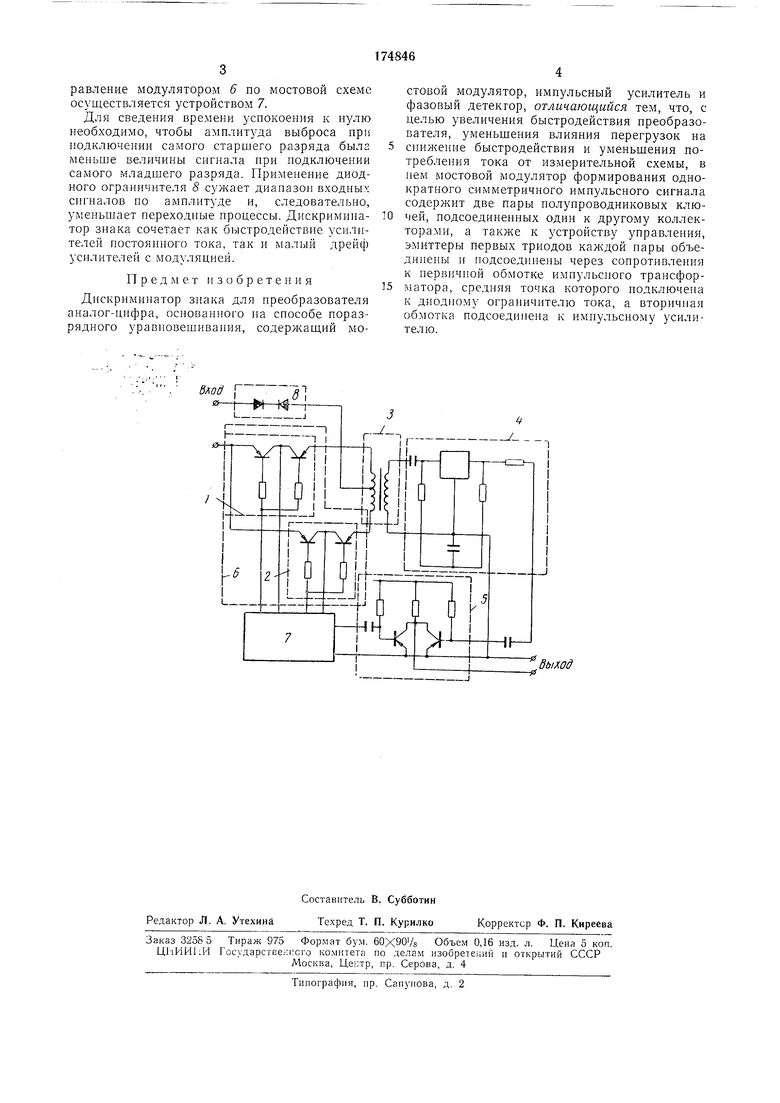

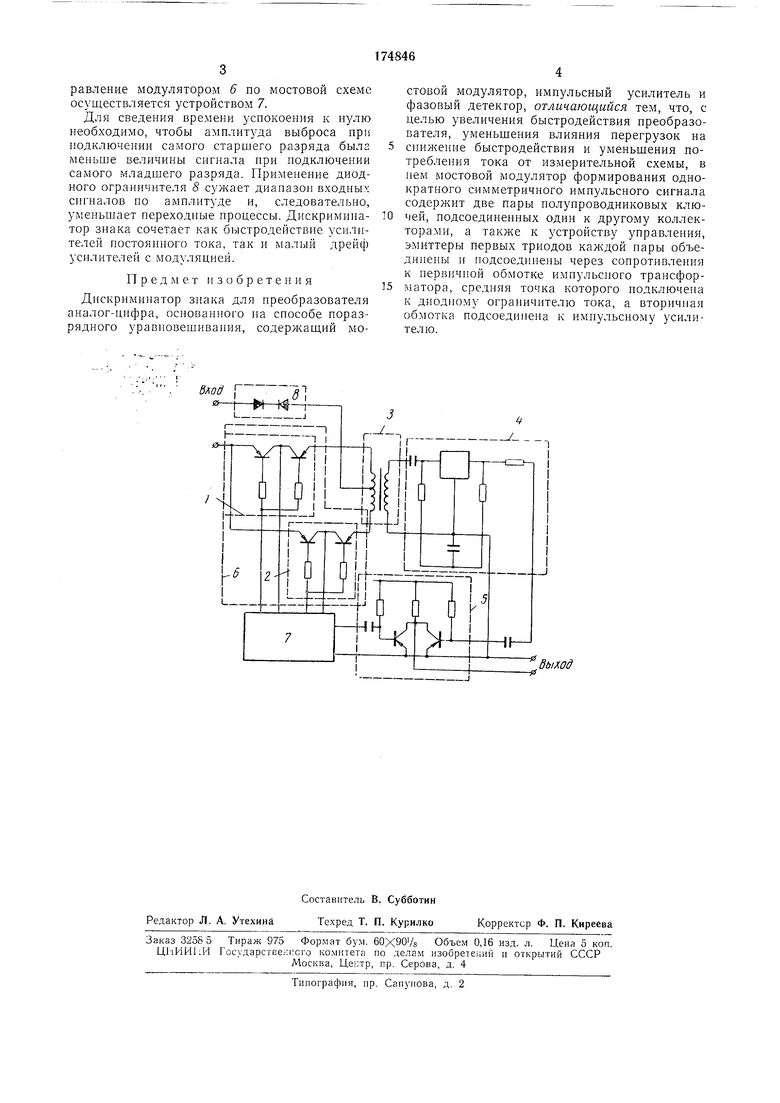

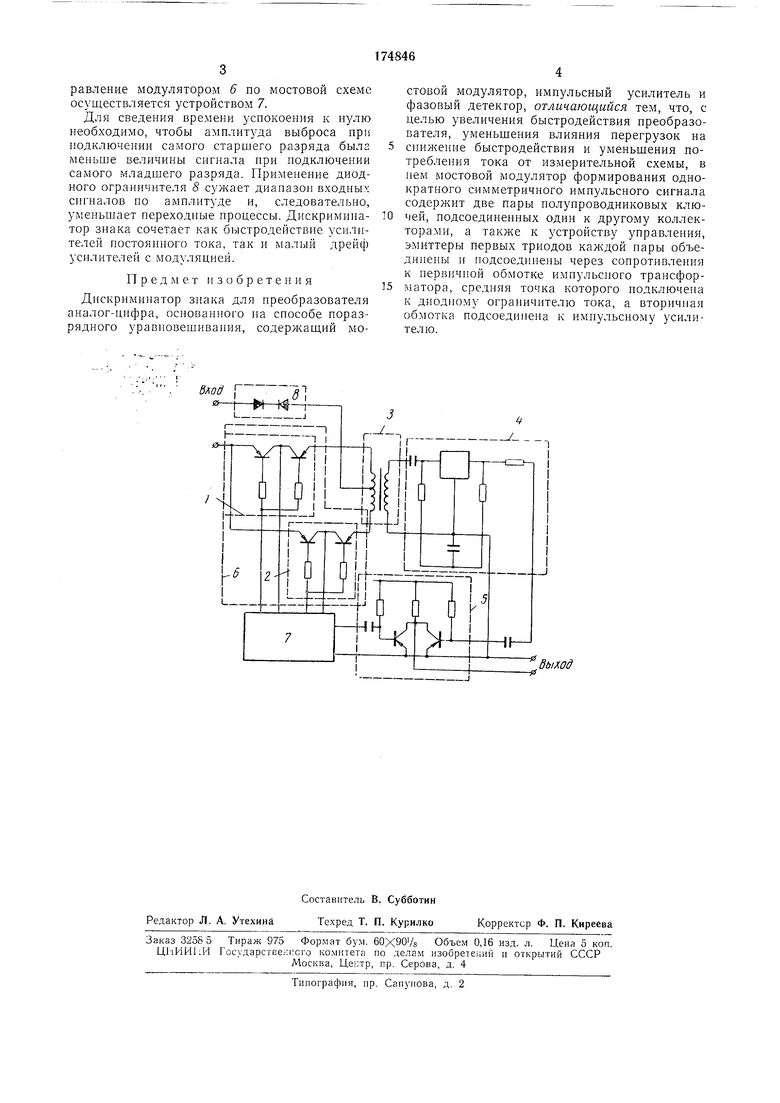

На чертеже представлена блок-схема предлагаемого дискриминатора.

При преобразовании напряжения в двоичный код по приппипу поразрядного уравновешивания на вычитаюш,ее устройство подают кодируемое папряжение, а с другой стороны, начиная со старшего разряда, подключают разрядные напряжения.

чается дискриминатор зиака, выдающий сигнал на отключение разрядного напряжения, если величина последнего в сумме с подключенпыми рапее папрял еииями старших разрядов больше, чем величина кодируемого напряжения. В противном случае сигнал на выходе дискриминатора отсутствовать и разрядное напряжение остается включенным. Чувствительность дискриминатора должна

быть не хуже, по крайней мере, чем i/o цепи младшего разряда.

Сигнал на входе дискриминатора имеет ступенчатую форму и содержит как постоянную составляющую, так и сиектр других частот,

ширина которого зависит от скорости подключения разрядов. Динамический диапазон составляет 2п, где п-число двоичных разрядов. Высокое быстродействие предлагаемой схемы достигается однократным формированием

симметричного входного сигнала при подключении каждого разряда преобразователя. Это достигается подключением полупроводннковых ключей 1 и 2. Сигнал такой формы отличается тем, что в нем отсутствует постоянная

составляющая, и формирование его легко осуществляется при помощи ключей 1 и 2, а также импульсного трансформатора 3. Этот сигнал дает малые последствия при прохождепии через импульсный усилитель 4. Далее сигравление модулятором 6 по мостовой схеме осуществляется устройством 7.

Для сведения времени успокоения к пулю необходимо, чтобы амплитуда выброса при подключении самого старшего разряда была меньше величины сигнала при подключении самого младшего разряда. Применение диодного ограничителя 8 сужает диапазон входных спгналов по амплитуде и, следовательно, уменьшает переходпые процессы. Дискриминатор зпака сочетает как быстродействие усилителей постоянного тока, так и малый дрейф усилителей с модуляцией.

Пред м е т и з о б р е т е н и я

Дискриминатор знака для преобразователя аналог-цифра, основанного на способе поразрядного уравновешивания, содержаш,пй мостовой модулятор, импульсный усилитель и фазовый детектор, отличающийся тем, что, с целью увеличения быстродействия преобразователя, уменьшения влияния перегрузок на снижение быстродействия и уменьшения потребления тока от измерительной схемы, в нем мостовой модулятор формирования однократного симметричного импульсного сигнала содерл ит две пары полупроводниковых ключей, подсоединеппых один к другому коллекторами, а также к устройству управления, эмиттеры первых триодов каждой пары объединены и подсоединены через сонротивления к нервнчной обмотке имнульсного трансформатора, средняя точка которого подключена к диодному ограничителю тока, а вторичная обмотка подсоединена к импульсному усилителю.

| название | год | авторы | номер документа |

|---|---|---|---|

| Побайтный преобразователь из двоичного в двоично-кодированное остаточное представление | 1972 |

|

SU437067A1 |

| МОДУЛЯТОР ТЕЛЕФОННОГО КАНАЛА С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1973 |

|

SU421139A1 |

| Устройство для преобразования сопротивления в код | 1989 |

|

SU1751849A1 |

| Преобразователь угла поворотаВАлА B КОд | 1979 |

|

SU798945A1 |

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД | 1970 |

|

SU269634A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1347186A1 |

| Параллельный матричный сумматор- вычитатель | 1977 |

|

SU737950A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU395875A1 |

Выход

Даты

1965-01-01—Публикация