Изобретение относится к области цифровых измерительных устройств и может быть использовано в устройствах кодирования технологических параметров управляющих вычислительных машин.

Известны различные виды преобразователей напряжения в код поразрядного уравновешивания с коммутатором на входе.

Однако кодирование эталонного уровня О в, заведенного в ряд каналов коммутатора, в известных преобразователях ничем не отличается от кодирования любого другого напряжения. Это приводит к увеличению общего времени преобразования входной инфор.мации, а схема сравнения напряжений испытывает максимально возможные перегрузки, так как в большинстве тактов взвешивания уравновешивающее напряжение, вырабатываемое преобразователем кода в напряжение, больше кодируемого.,

Целью изобретения является повышение эффективности преобразователя напряжения в код.

Сущность изобретения заключается в том, что преобразователь напряжения в код содержит блок сквозного переноса, входы которогоподсоединены к симметричному выходу преобразователя кода в напряжение, к выходу первого разряда регистра последовательных сдвигов, ко входу источника кодируемого напрял ;ения, ко входу запуска всего устройства; выход блока сквозного переноса соединен со входом регистра последовательных сдвигов.

Блок сквозного переноса содержит схему сравнения, схему «И и триггер, причем выход схемы сравнения через схему «Я соединен с одним входом триггера, другой вход которого подключен ко входу запуска устройства, а выход соединен с регистром последовательных сдвигов, к выходу первого разряда которого подключен другой вход схемы «Я.

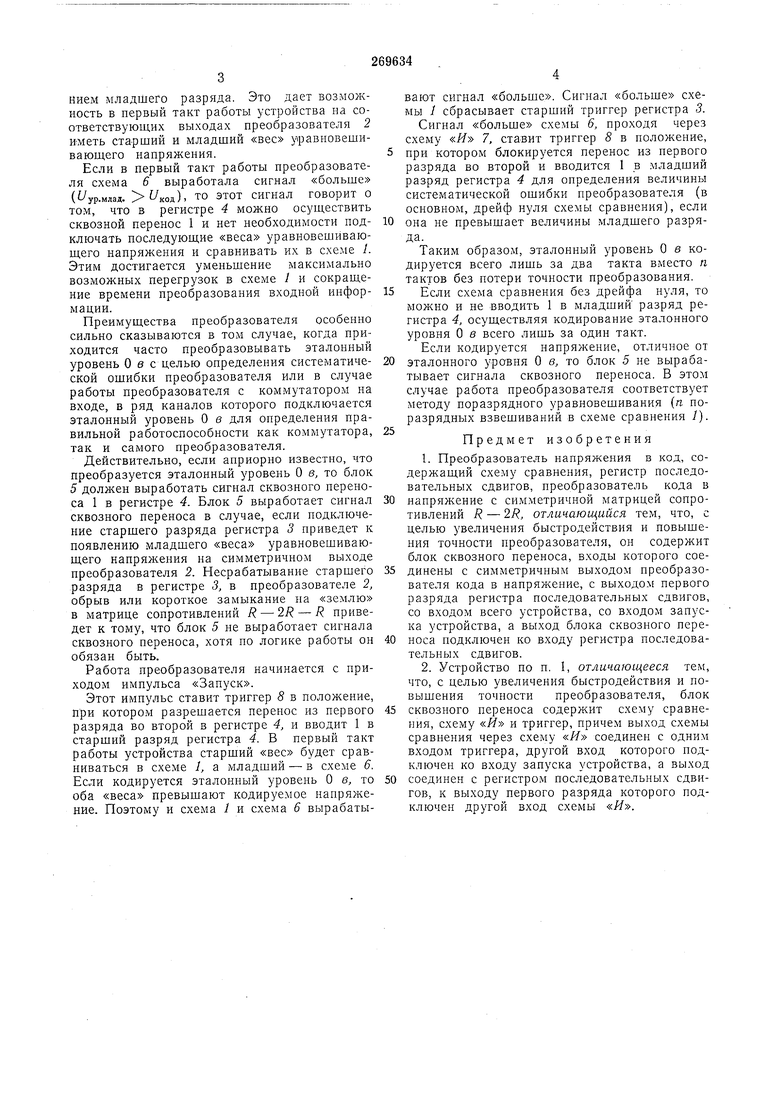

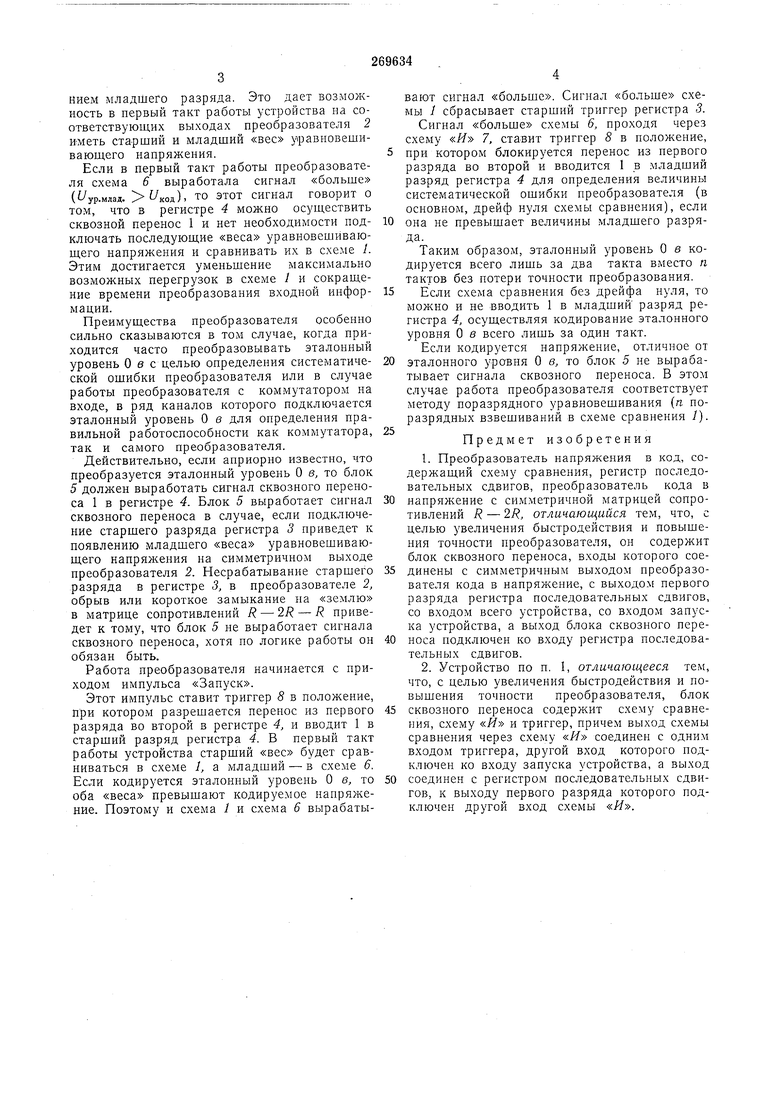

На чертеже изображена блок-схема описываемого преобразователя напряжения в код, где 1 - схема сравнения напряжений; 2 - преобразователь кода в напряжение с матрицей сопротивлений; 5 - регистр формирователя кода; 4 - регистр последовательных сдвигов; 5-блок сквозного переноса; 6-схема сравнения напряжений; 7-схема S - триггер.

Повышение эффективности преобразователя нанряжения в код достигается за счет того, что введен блок 5, а в преобразователе 2 применяется матрица сопротивлений (например, : 1атрица сопротивлений R - 2R - R), в кото рой используются два выхода: выход, определяемый положением старшего разряда, что связано с алгоритмом нреобразователя поразрядного уравновешивания, и симметричный выход, определяемый, как известно, положением младшего разряда. Это дает возможность в первый такт работы устройства на соответствующих выходах преобразователя 2 иметь старший и младший «вес уравновешиваюш,его напряжения.

Если в первый такт работы преобразователя схема 6 выработала сигнал «больше

(ур.млад. Ькод), то ЭТОТ СИГНаЛ ГОВОрИТ О

том, что в регистре 4 можпо осуш,ествить сквозной перенос 1 и нет необходимости подключать последуюш,ие «веса уравновешиваюш,его напряжения и сравнивать их в схеме А Этим достигается уменьшение максимально возможных перегрузок в схеме / и сокрашение времени преобразования входной информации.

Преимуш,ества преобразователя особенно сильно сказываются в том случае, когда приходится часто преобразовывать эталонный уровень О в с целью определения систематической ошибки преобразователя или в случае работы преобразователя с коммутатором на входе, в ряд каналов которого подключается эталонный уровень О в для определения правильной работоспособности как коммутатора, так и самого преобразователя.

Действительно, если априорно известно, что преобразуется эталонный уровень О в, то блок 5 должен выработать сигнал сквозного переноса 1 в регистре 4. Блок 5 выработает сигнал сквозного переноса в случае, если подключение старшего разряда регистра 3 приведет к появлению младшего «веса уравновешивающего напряжения на симметричном выходе преобразователя 2. Несрабатывание старшего разряда в регистре 3, в преобразователе 2, обрыв или короткое замыкание на «землю в матрице сопротивлений R - 2R - R приведет к тому, что блок 5 не выработает сигнала сквозного переноса, хотя но логике работы он обязан быть.

Работа преобразователя начинается с приходом импульса «Запуск.

Этот импульс ставит триггер 8 в положение, при котором разрешается перенос из первого разряда во второй в регистре 4, и вводит 1 в старший разряд регистра 4. В первый такт работы устройства старший «вес будет сравниваться в схеме I, а младший - в схеме 6. Если кодируется эталонный уровень О в, то оба «веса превышают кодируемое напряжение. Поэтому и схема 1 и схема 6 вырабатывают сигнал «больше. Сигнал «больше схемы / сбрасывает старший триггер регистра 3. Сигнал «больше схемы 6, проходя через схему «И 7, ставит триггер 8 в положение,

при котором блокируется перенос из нервого разряда во второй и вводится 1 в младший разряд регистра 4 для определения величины систематической ошибки преобразователя (в основном, дрейф нуля схемы сравнения), если

она не превышает величины младшего разряда.

Таким образом, эталонный уровень О в кодируется всего лишь за два такта вместо п тактов без потери точности преобразования.

Если схема сравнения без дрейфа нуля, то можно и не вводить 1 в младший разряд регистра 4, осуществляя кодирование эталонного уровня О 8 всего лишь за один такт.

Если кодируется напряжение, отличное от

эталонного уровня О в, то блок 5 не вырабатывает сигнала сквозного переноса. В этом случае работа преобразователя соответствует методу поразрядного уравновешивания (ге поразрядных взвешиваний в схеме сравнения /).

Предмет изобретения

1.Преобразователь напряжения в код, содержащий схему сравнения, регистр последовательных сдвигов, нреобразователь кода в

напряжение с симметричной матрицей сопротивлений R - 1R, отличающийся тем, что, с целью увеличения быстродействия и повышения точности преобразователя, он содержит блок сквозного переноса, входы которого соединены с симметричным выходом преобразователя кода в нанряжение, с выходом первого разряда регистра последовательных сдвигов, со входом всего устройства, со входом запуска устройства, а выход блока сквозного переноса подключен ко входу регистра последовательных сдвигов.

2.Устройство по п. 1, отличающееся тем, что, с целью увеличения быстродействия и повышения точности преобразователя, блок

сквозного нереноса содержит схему сравнения, схему «Я и триггер, причем выход схемы сравнения через схему «// соединен с одним входом триггера, другой вход которого подключен ко входу запуска устройства, а выход

соединен с регистром последовательных сдвигов, к выходу первого разряда которого подключен другой вход схемы «Я.

Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля аналоговых объектов | 1986 |

|

SU1397941A1 |

| Аналого-цифровой преобразователь поразрядного кодирования | 1980 |

|

SU936418A1 |

| ТЕЙТМ- 1П 11^f vu4«*'pr'-'&i! Ti Ari!. -^t-i-^b»SHbJiKOTEaA | 1969 |

|

SU254223A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1985 |

|

SU1352650A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1179533A1 |

| Многоканальный преобразователь угла поворота вала в код | 1977 |

|

SU732956A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Цифровой преобразователь координат | 1977 |

|

SU742944A1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU750727A1 |

Ошибка

f

« Cffpoc

„Запуск

51

,А

I

Даты

1970-01-01—Публикация