. .- 1/ - : . ..

Изобретение относится к вычислительной технике и может быть использовано в специализированных ЦВМ, обладающих повышенной надежностью, быстродействием, помехоустойчивостью и устойчивостью к дестабилизирующим фактор 1м. ,

Известны одно- и многоразрядные, сумматоры-вычитатели для систем счис|лёния с основанием т, использукадие унитарные коды 1 из т, и содержащие в каждом т-ном разряде матрицы сложения и вычитания, как правило, построенные на магнитных элементах: с НПГ, прошитых входными и выходными обмотками с использованием электронных ключей и усилителей-формирователей 1, 21 и 3 .

Подобные устройства действуют по принципу совпадения двух полутоков, что приводит к уменьшению надежности и снижению быстродействия из-за жестких требований к величинам полутоков и невозможности форсированного переключения. Реализация операций сложения и вычитания в аналогичных устройствах осуществляется либо введением двух матриц, реализующих таблицы сложения и вычитания н.а каждый т-ный разряд, либо введением двух групп выходных обмоток, прошитых в соответствии с таблицами сложения и .

с вычитания, что приводит к усложнению конструкции устройства.

Наиболее близким к предлагаемому является параллельный матричный сумматор-вычитатель,содержащий матри-;

10 цу ферритовых сердечников, координатные обмотки, две группы выходных обмоток, формирователи коо1рдинатных токов, усилители считывания, обмотки переноса, усилители считывания обмоток переноса, шины управления, обмот5 ку восстановления и Формирователь тока восстановления 4.

Недостатком да.нного устройства является сложность конструкции, а именно, наличие двух групп выходных

20 обмоток, обмоток переноса, прошивающих всю матрицу, и усилителей считывания обмоток переноса, а также низкая помехоустойчивость, обусловленная присутствием в схеме помех от

25

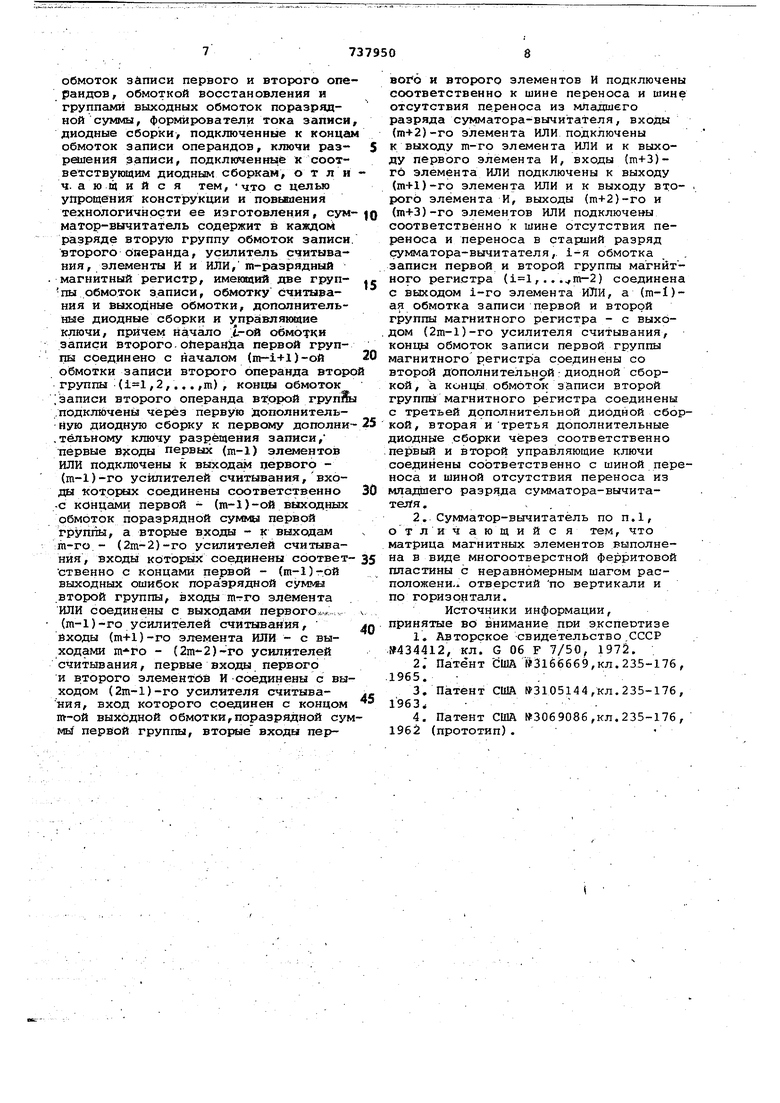

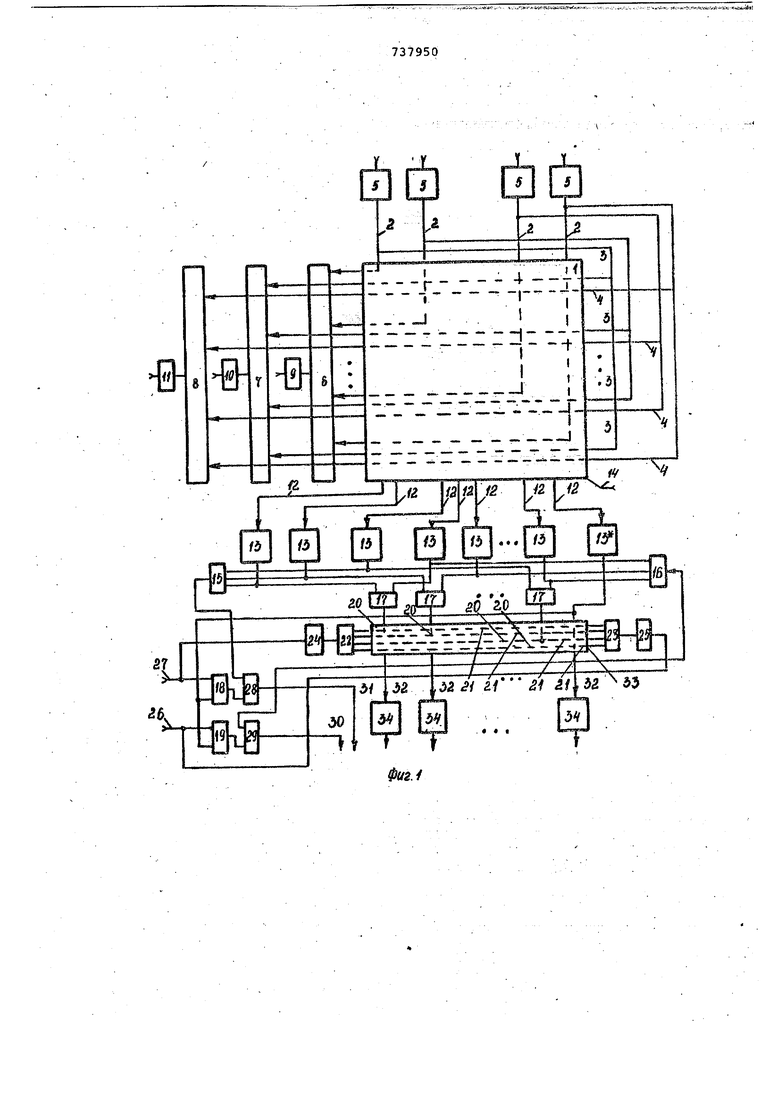

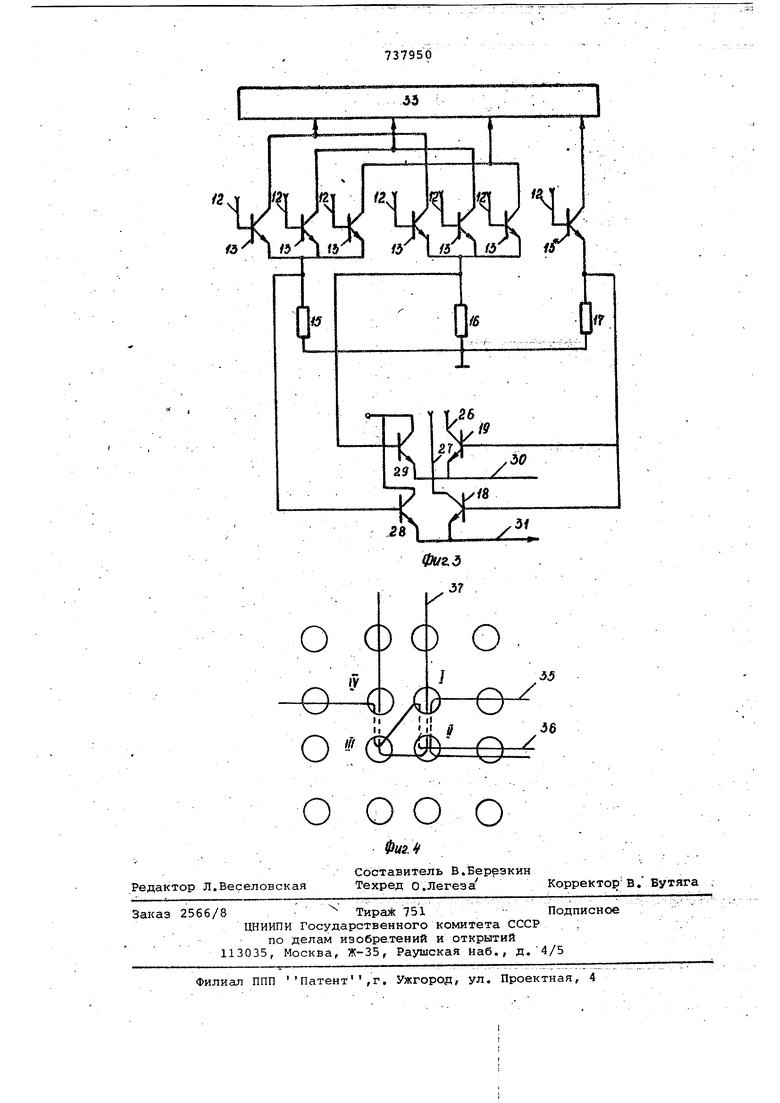

гт полувыбранных в такте считывания сердечников, переключающихся по пологой части петли гистерезиса, и взаимным влиянием соседних элементов матрицы друг на друга. Цель изобретения - упрощение кон Гс рУЩйи и повшгение технологй ностй ее изготовления. Цель достигается , что параллельный матричный сумматб р- вЁгчй ате содержащий в ка(ждом т-ном разряде матрицу магнитных элементов из мате риала с прямоугольной петлей гистерезиса (где т-основание системы счисления для унитарного кода 1 из :Л1) , прошитую группами обмоток записй пёрвого .и второго операндов, обм кой восстановления и группами выход ных обмоток поразрядной суммы, формирователи тока записи диодные .сборки, подключенные к концам обмоток записи операндов, ключи разрешения записи, подключенные к с:6от.вётствукяцим диодйым сборкам:, содержит в каждом разряде вторую группу обмоток записи второго операнда, усилитель считывания, элементы И и ИЛИ, т-разрядный магнитный регистр, имекщий две группы обмоток записи, обмотку считывания и выходные обмот кйi Дбполййтёльйыё диодные сборки и; управЛйКхйие ключи, причем начало i-бй записи второго операнд гхерврй группы соединено с началом (m-i+i)-6й группы обмотки з аписй второго операнда вуорой группы (i 1,2, ..,, m), концы обмоток запис второго операнда второй группы подк чены через первую дополните 1ьную диодную сборку к первому дополнител ному ключу разрешения записи, первы входы первых (т-1) элементов ИЛИ по ключены к выходам первого - (m-l)го усилителей считывания, входы кот .сЬёдййёны соответственно с концами первой - (т-1)-ой выходных обм ток поразрядной суммы первой группы а вторые входы - к выходам т-го (2т-2)-гоусилителей считывания, вхЪдн которых соединены соответственно с концами первой - (га-1)-ой выходных сшибок поразрядной суммы второй группы, входы т-го элемента ИЛИ ЬЪедййёны с выходами первого (ra-D-rb усилителей считывания, вх ды (iri+l)-ro элемента ИЛИ с выходами т-го (2Jn-2)-ro усилителей считывания, первые входы первого и второго элементов И соединены с выходом (2М-1)-го усилителя считывания, вхо которого с концсхм т-ой выходнсй обмотки поразрядной суммы первсот группы,вторые входы nejpBoro и второго элементов И подключены соот-бётсгйШно к tnHMe переноса и йШнё (ЭтеуФетвйя переноса из младшегб | а§ рййа сумматора-вычитателя, входы (т+2)-го элемента ИЛИ подключёйй К выходу т-го элемента ИЛИ и к выходу, первого элемента И, вход (га+З)-го элемента ИЛИ подключены к выходу (т+1)-го элемента ИЛИ и к выходу второго -з лемента И, выходы (m+2)-rq и (т+3)-го элементов ИЛИ подключены соответственно к шине отсутствия переноса и переноса в старший разряд сумматора-вычитателя, i-я обмотка записи первой и второй группы магнитного регистра (,. .., т-2) соединена с выходом i-ro элемента ИЛИ, а (т-1)-ая обмотка записи первой и второй группы магнитного регистра - с выходом (2т-1)-го усилителя считывания, концы обмоток записи первой группы магнитного регистра соединены со второй дополнительной диодной сборкой, а концы обмоток записи второй группы магнитного регистра соединены с третьей дополнительной диодной сборкой, вторая и третья дополнительный диодные сборки через соответственно первый и второй управляющие ключи соединены соответственно с шиной переноса и шиной отсутствия переноса из младшего разряда сумматора-вычитателя. Матрица магнитных элементов выполнена в виде многоотверстий ферритовой пластины с нёравнормерным шагом расположения отверстий по вертикали и по горизонтали. На фиг.1 представлена схема параллельного матричного сумматора-вычитателя; на фиг.2 - схема прошивки матрицы сумматора-вычитателя для кода 1 из 4, элементы, матрицы условно показаны в виде тороидальных сердечников; на фиг.З - схема выработки переноса на транзисторах дляодного разряда в коде 1 из 4; на фиг.4 - один элемент матрицы и схемы анализа результата, выполненной на многоотверстной ферритовой пластине с неравномерным шагом расположения отверстий со всеми необходимыми прошивками. Параллельный матричный сумматор вычитатель содержит матрицу 1 маг нитных элементов размером mxm, прошитую шинами 2 записи первого операнда, шинами 3, 4 записи второго операнда В прямом коде и обратном коде (фиг. 1 и 2). Начала всех шин подключены к общим формирователям 5 тока записи. Концы всех обмоток через соответствующие разделительные диодные сборки 6, 7 и 8 подключены к ключам 9, 10 и 11 разрешения подачи операндов. Имею,тся также выходные обмотки 12, присоединенные к усилителям-формирователям 13 и обмотки восставовления 14. Выходы формирователей 13, соответствующих значениям суммы О, ..., in-2, подключены ко входам элемента ИЛИ 15, а выходы формирователей 13, сор тветствующих значениям суммы го, ..., 2(т-1), подключены ко входс1М элемента ИЛИ 16, Кроме того, выходы данных формирователей подклю- , чены ко входам двухвходовых элементов ИЛИ 17, причем на входы j-ro элемента ИЛИ 17 поданы выходы j-ro и (j+m)-ro фоЕвУШрователя 13 (, ..., m-2) . Выход формирова еля 13, соответствующего значению суммы m-l (на фиг.1 помечен звеэдочкой) подключен ко вторым входам двухвходовых элементов И 18, 19. Кроме того выход данного формирователя 13 и выходы элементов И 17 подключены каж- дый к соответствующей обмотке первой 20 и второй 21 групп обмоток записи магнитного регистра 33. Другие ксжцы данных групп обмоток подключены через соответствующие диоды сборки 2 и 23 к ключам 24 и 25 раэрааеиия зап си результата с учетом переноса из младшего разряда и без его учета.Вхо ды данных ключей подключены к ошиам 26 наличия и 27 отсутствия переноса из младшего разряда. Кроме того, шина 26 подключена к первому входу элемента И 19, а шина 27 - к первому входу элемента И 18. Вьтод элемента 18 подключен ко йторому входу двухвходовоГо элемента ИЛИ 28 а выход элемента 19 - ко второму входу ДВУХВХОДОВОГО элалента 29 ИЛН К первым входам элементов 28 и 29 по ключены выходы соответствующих элементов 15 и 16 ИЛИ. Выход элемента 29 подключен к шине 30 переноса, а выход элемента 28 - к шине 31 отсутс вия переноса в старший разряд.Выходные обмотки магнитного регистра 33 подключены к усилителям 34. На фиг .4 представлено расположение прошивок для одного элемента .; .Матрицы,или регистра. В многоотверстнойферритрвой пластине с неравйо Йерным шагом по вертикали и по гори зонтали имеются группы отверстий по 4 в Ксщцой, причем расстояния между центрами соседних отверстий, принад лежащих одной группе, меиыце рассто НИИ между центрами соседних отверстий г принадлежащих равным группам. Элемент .занимает одну группу отверстий vi содержит обмотку записи 35, обмотку считьшания 36 и выходную обмотку 37. Устройство работает следукяцим образом. В первом такте происходит подача первого операнда в коде 1 из га (например 1 из 4) на формирователи 5 с одновременной подачей сигнала раз решения на ключ 9. При этом потечет ток,записи по обмотке записи одной из строк матрицы (Фиг.2), пере.водя все сердечники данной строки в (под словом сердечник подразумевается участок многоотверстной пластины). Во втором такте подается второй операнд на,те же формирователи 5, но при этом открывается ключ 10, управляющий сложением, или ключ 11, управляющий вычитанием, в зависимое ТИ от выполняемой операции. При это потечет ток по одной из вертикальных обмоток, переводя один кэ сердечников выбранной строки в .На выходнЁш обмотках матрицы появится сигнал псчразрядной суммы.На выходе элемента 28, либо.29, появится сигнал, соответствующий налич или отсутствию переноса в староий разряд. Результат операции будет записан в магнитный регистр 33 либо без изменений, либо увеличенный на единицу (при наличии переноса из младшего разряда). В третьем такте происходит восстановление матрицы подачей сигнала по шине 14 и считывание содержимого Магнитного регистра 33 на усилители 34. Такимобразом, осуществляется суммирование или вычитание Двух кодов за три такта с возможностью форсированного переключения сердечника. На фиг.З показан вариант реализации элементов 15, 16; 17, 18, 13, 28, 29. Элаленты ИДИ 15, 16 реализованы объединением эмиттеров соответствующих формирователей 13, элементы ИЛИ 17 - путам объединения коллекторов соответствующих формирователей 13, элементы И 18, 19 реализованы на одном транзисторе каждый, элементы ИЛИ 28 и 29 также регшизованы объединением эмиттеров соответствующих транзисторов При такой схемной реализации введение вышеуказанных элементов требует очень мало дополнительного оборудования (три транзистора для кода 1 из 4)/ Введение вышеуказанных элементов и новые связи, описанные выше, позволяют упростить конструкцию. Введение магнитного регистра и новые связи позволяют исключить из матрицы столбец элементов и обмотки, учитывакдаие перенос из младшего разряда. Введение двух групп обмоток для подачи второго операнда и новые связи позволяют упростить прошивку вызсодных обмоток, сделав их общими для суммы и разности. Упрощение конструкции приводит к повышению технологичности изготовления устройства. Принбние многоотверстных пластин с неравномерным шагом расположения отверстий позволяет уменьшить взаимное влияние между соседними элементами. С ОЕЯлула изобретения 1, Параллельный матричный сумматорвычитатель, содержащий в каждом тном разряде матрицу магнитных элементов из материала, с прямоугольной петлей гистерезиса (где m - основание системы счисления для унитарного кода 1 из т), прошитую группами обмоток записи первого и второго опе рандов, обмоткой восстановления и группами выходных обмоток поразрядной суммы, формирователи тока записи диодные сборки, подключенные к конца обмоток записи операндов, ключи разрешения записи, подключенные к соответствукидим диодным сборкам, от ли ч. а ю щ и и с я тем, что с целью упрощения конструкции и повьЕаения технологичности ее изготовления, сум матор-вычитатель содержит в каждой разряде вторую группу обмоток записи второго операнда, усилитель считывания, элементы И и ИЛИ,т-разрядный магнитный регистр, имекиций две группы обмоток записи, обмотку считывания и выходные обмотки, дополнительные диодные сборки и управляющие ключи, причем начгшо .t-ой обмо-рки записи второго. оЛеранзца первой группы соединено с началом (п1-1+1)-ой обмотки записи второго операнда втор группы-(,2,...,т), концы обмоток записи второго операнда второй .подклйчены через первую дополнительную диодную сборку к первому дополни .тельному ключу размещения записи, первые входы первых (га-1) элементов ИЛИ подключены к выходгм первого (m-l)-ro усилителей считывания,входы которых соединены соответственно -с концами первой - (т-1)-ой выходных обмоток поразрядной суммы первой группы, а вторые входы - к выходам :т-го.- (2т-2)-го усилителей считывания, входы которых соединены соответ ственно с концами первой - {т-1)-,ой выходных ошибок поразрядной второй группы, входы т-гго элемента ИЛИ соединены с выходами первого.,. (т-1)-го усилителей считывания, входы (т+1)-го элемента ИЛИ - с выходами - (2т-2)-го усилителей считывания, первые входы первого и второго элементов И -соединены с вы ходом (2т-1)-го усилителя считывания, вход которого соединен с концом т-ой выходной обмотки,поразрядной сум Mbf первой группы, вторые входы первогб и второго элементов И подключены соответственно к шине переноса и шине отсутствия пе.реноса из младшего разряда сумматора-вычитателя, входы (т+2)-го элемента ИЛИ подключены к выходу т-то элемента ИЛИ и к выходу первого элемента И, входы (т+3)г6 элемента ИЛИ подключены к выходу (т+1)-го элемента ИЛИ и к выходу вто- . рого элемента И, выходы (т+2)-го и (inH:-3)-ro элементов ИЛИ подключены соответственно к шине отсутствия переноса и переноса в старший разряд сумматора-вычитателя,. i-я обмотка записи первой и второй группы магнитного реги.стра (, .. .т-2) соединена с выходом 1-го элемента ИЛИ, а (m-I)ая обмотка записи первой и второй группы магнитного регистра - с выхОдом (2in-l)-ro усилителя считывания, концы обмоток записи первой группы магнитного регистра соединены со второй дополнительной:диодной сборкой , а концы обмОток записи второй группы магнитного регистра соединены с третьей дополнительной диОдной сборкой, вторая итретья дополнительные диодные сборки через соответственно первый и второй управляющие ключи соединены соответственно с шиной переноса и шиной отсутствия переноса из младшего разряда сумматора-вычитателя., . 2.Сумматор-вычитатёль по п.1, отлич а ющ и и с я тем, что матрица магнитных элементов выполнена в виде многоотверстной ферритовой пластины с неравномерным шагом расположение отверстий по вертикали и по горизонтали. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство,СССР 434412, кл. G 06 F 7/50, 1972. 2. Патент США №3166669,кл. 235-176 , 1965. . 3.Патент США №3105144,кл.235-176, 1963 . . 4.Патент США №3069086,кл.235-176, 1962 (прототип).

L:L

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Логическое запоминающее устройство | 1974 |

|

SU507899A1 |

| Побайтный преобразователь из двоичного в двоично-кодированное остаточное представление | 1972 |

|

SU437067A1 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

| Магнитное оперативное запоминающее устройство | 1983 |

|

SU1129654A1 |

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ ИЗ ОСТАТОЧНОЙ СИСТЕМЫ СЧИСЛЕНИЯ В ПОЛИАДИЧЕСКУЮ | 1973 |

|

SU407301A1 |

| Счетчик импульсов | 1981 |

|

SU978358A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

it V t Ia2tll 1анмм4 « « 1 , гГго ЕР ; ь,.„ « i- ii; -ri23f--i « U / / /. zi2z:X:rzrir j. /, i M 21 f,, Фи2Л J

Авторы

Даты

1980-05-30—Публикация

1977-11-03—Подача