15

(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство символьной синхронизации | 1990 |

|

SU1775869A1 |

| Устройство для восстановления синхроинформации | 1981 |

|

SU1003322A1 |

| Цифровой электропривод | 1982 |

|

SU1050077A1 |

| Устройство для разгона и торможения электропривода | 1986 |

|

SU1374182A1 |

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Устройство для экстремальной фильтрации | 1988 |

|

SU1520507A1 |

| Делитель частоты следования импульсов с регулируемой длительностью импульсов | 1987 |

|

SU1444937A1 |

| Устройство для контроля группы цифровых узлов | 1987 |

|

SU1534461A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Устройство для деления в избыточном последовательном коде | 1986 |

|

SU1365078A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для синхронизации вычислительных систем, работающих в реальном масштабе времени. Целью изобретения является повышение достоверности. Устройство содержит генератор 1 тактовых им- пульсов, дешифратор 6, счетчики 2-4. сумматор 5, блок 7 анализа, делитель 8 частоты, триггер 9 и два элемента 10,11 задержки. Устройство обеспечивает абсолютную компенсацию погрешности синхронизации, накопленной в i-м цикле в течение (М)-го цикла. 6 ил

х|

сл

jl

xj С) XJ

Изобретение относится к автоматике и вычислительной технике и может быть использовано для синхронизации вычислительной системы, работающей в реальном масштабе времени.

Цель изобретения - повышение достоверности функционирования.

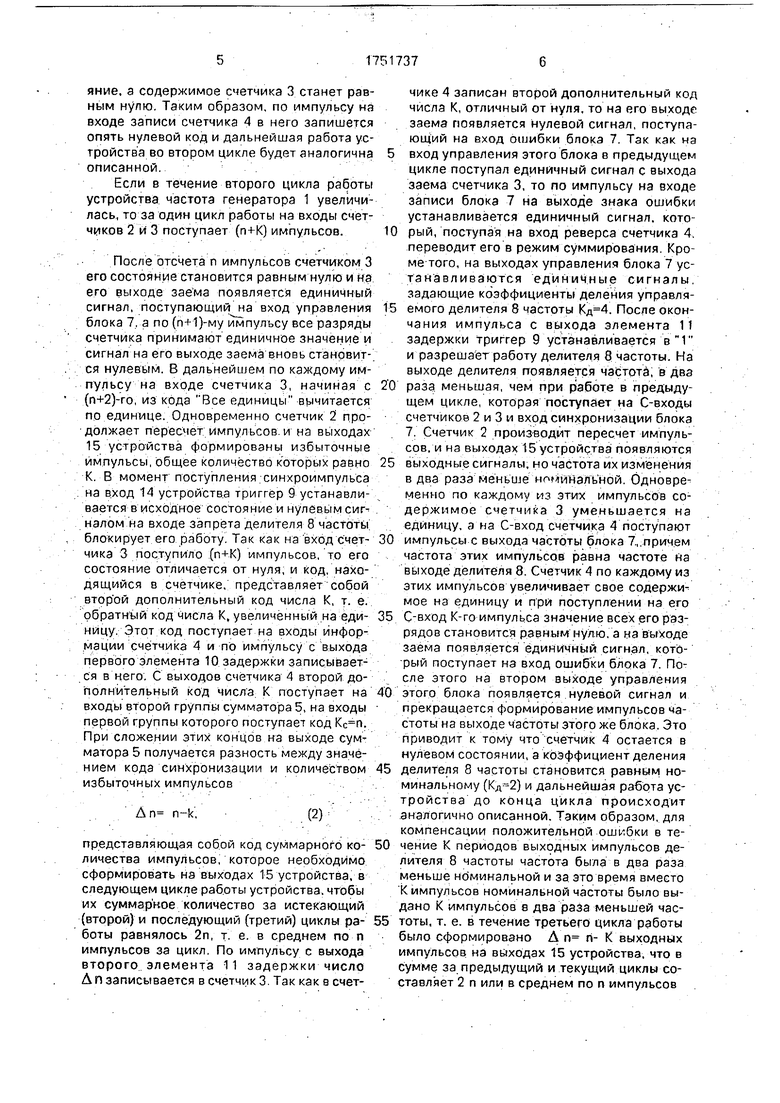

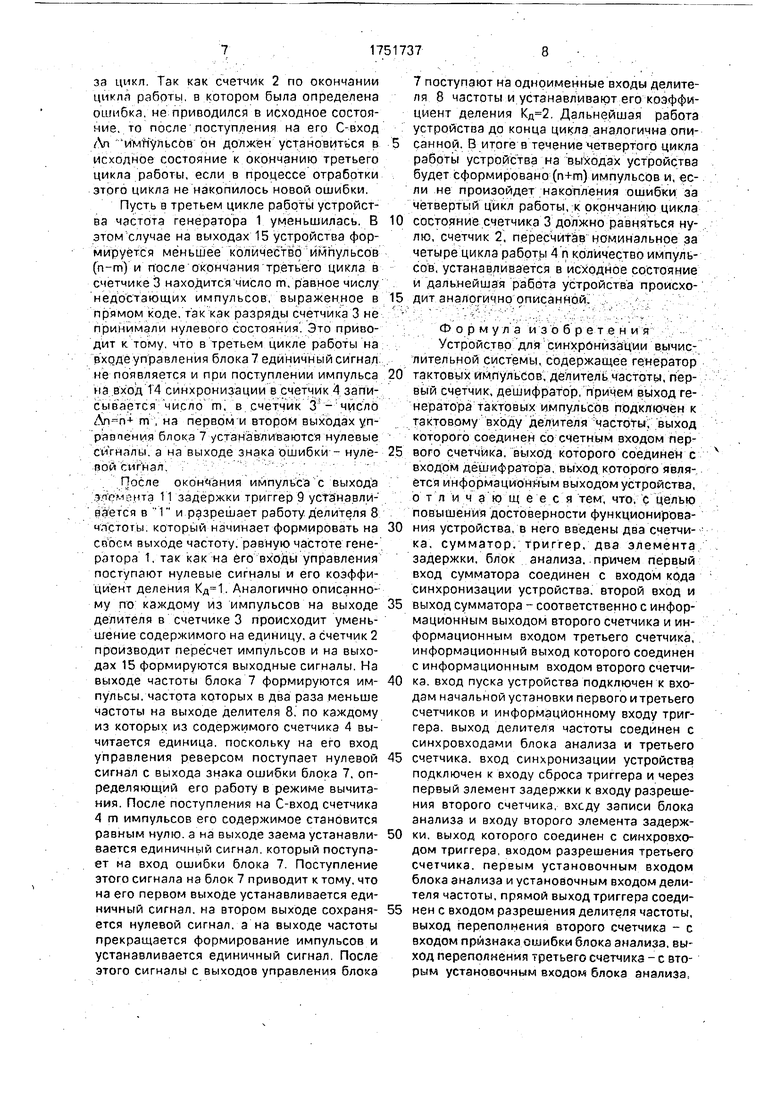

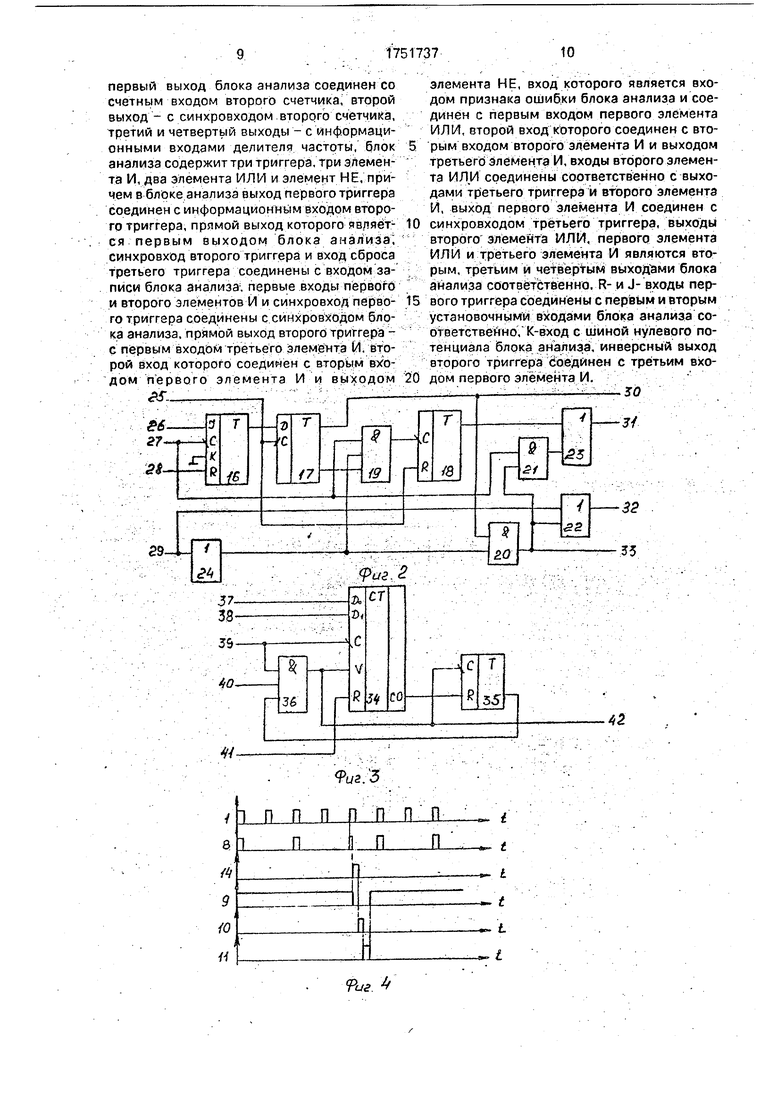

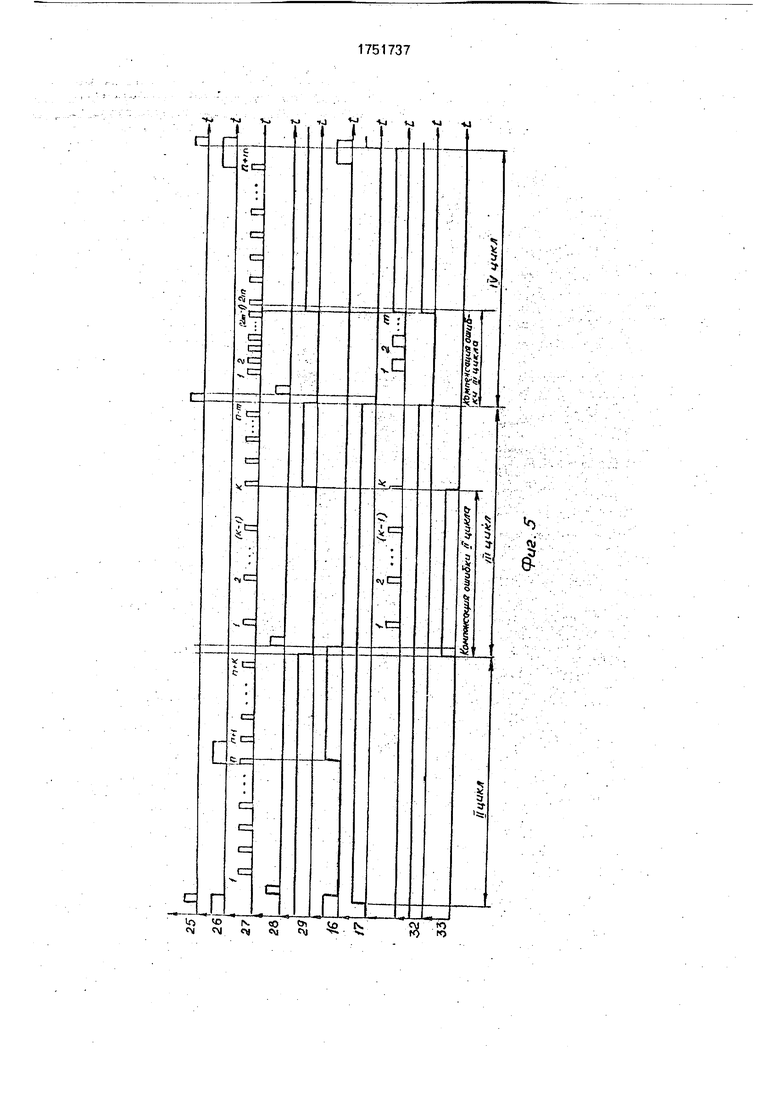

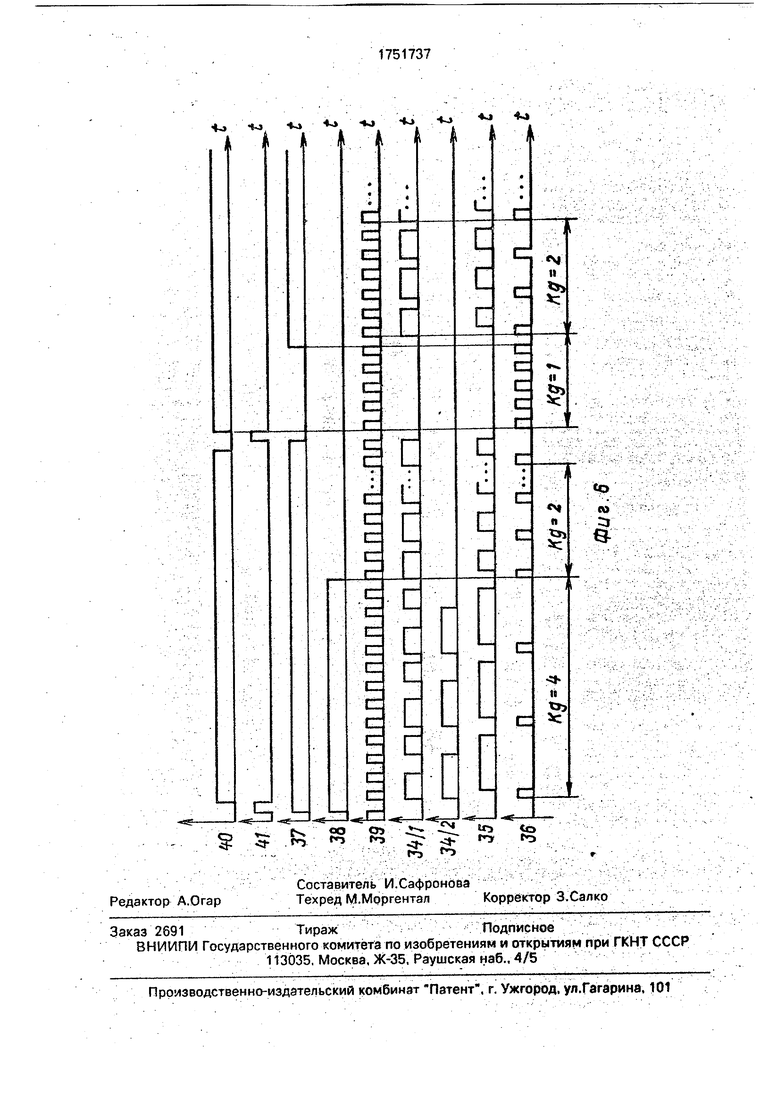

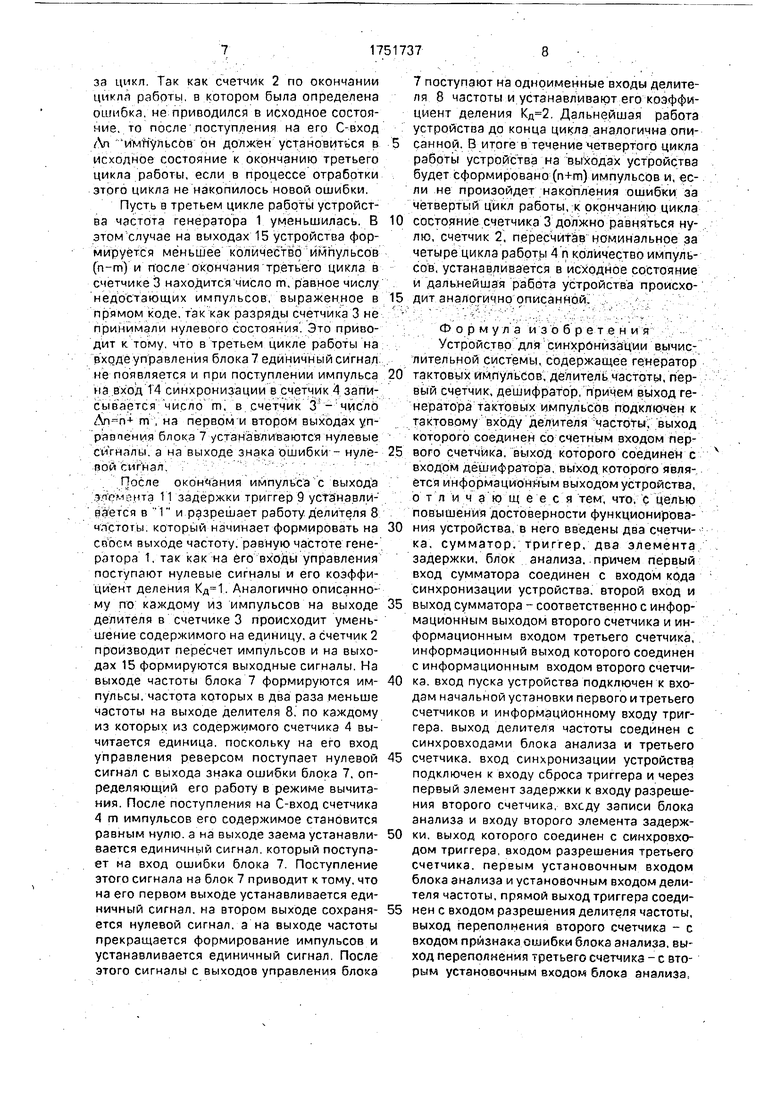

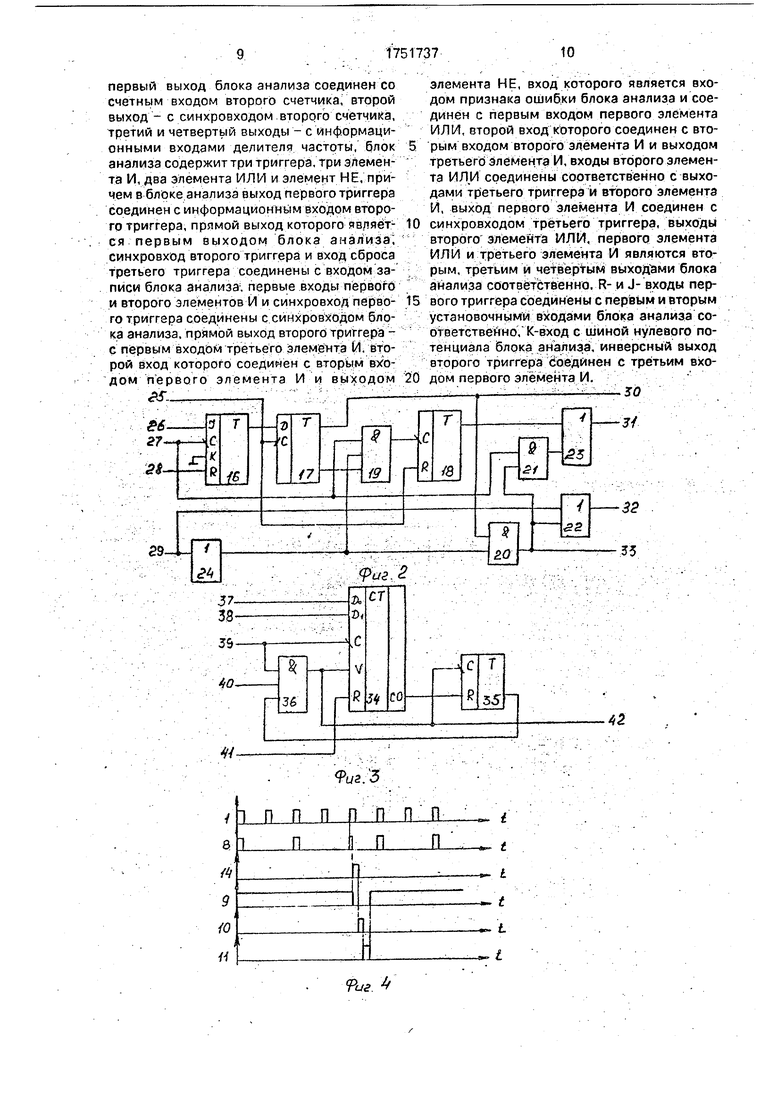

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 и 3 - функциональные схемы блока анализа и делителя частоты соответственно; на фиг. А - временная диаграмма, иллюстрирующая поступление импульса синхронизации на вход синхронизации устройства при совпадении с импульсом частоты генератора; на фиг. 5 - временная диаграмма работы блока анализа; на фиг. б - временная диаграмма работы делителя частоты.

Устройство для синхронизации вычислительной системы содержит генератор 1, счетчики 2-4 тактовых импульсов, сумматор 5, дешифратор 6, блок 7 анализа, делитель 8 частоты, триггер 9. первый 10 и второй 11 элементы задержки, вход 12 кода синхронизации, вход 13 пуска, вход 14 синхронизации и выход 15

Блок 7 анализа включают триггеры 16- 18, элементы И 19-21, элементы ИЛИ 22 и 23, элемент НЕ 24, вход 25 записи, вход 26 установки, вход 27 синхронизации, вход 28 установки, вход 29 ошибки и выходы 30-33

Делитель 8 частоты содержит вычитающий счетчик 34 триггер 35 и элемент И 36, а также информационные входы 37 и 38, вход 39 синхронизации, вход 40 разрешений, вход 41 установки и выход 42.

Устройство работает следующим образом.

Запуск устройства происходит по появлении на входе 13 пуска единичного сигнала В произвольный момент времени, но обязательно до подачи на вход 13 пуска единичного сигнала на входы 12 кода синхронизации поступает код синхронизации Кс равный произведению количества синхроимпульсов на каждом из выходов 15 синхронизации в течение одного периода синхронизирующих импульсов на входе 14 устройства на количество выходов 15, т е

Кс I L

(D

где I - количество импульсов на каждом из выходов устройства за один период синхроимпульсов на входе устройства,

L - количество выходов устройства Таким образом - номинальному колинеству импульсов за один цикл работы устройства на выходе делителя частоты После этого дрлитель частоты начинает работать с коэффициентом деления . так как на его первый и второй входы управления поступают соответственно единичный и нулевой сигналы с выходов блока 7 анализа,

Так как в счетчике 4 записан нулевой код, поступающий на входы второй группы сумматора 5, то на выходы сумматора 5 выдается без изменения код синхронизации, поступающий на входы первой группы сум0 матора с выходов 12 кода синхронизации.

Этот код поступает на входы информации

счетчика 3 и по импульсу с выхода элемента

11 задержки, поступающему на вход записи

счетчика 3 устанавливается нулевой сигнал,

5 поступающий на вход управления блока 7. По каждому импульсу на выходе делителя 8 частоты, поступающему на С-вход счетчика 2, он изменяет свое состояние и сигналы с выходов этого счетчика через дешифратор б

0 поступают на входы 15 устройства. Эти же импульсы с выхода делителя частоты поступают и на С-вход вычитающего счетчика записывается в него При этом на выходе заема счетчика 3. в который записан код

5 синхронизации, и по каждому из импульсов содержигое счетчика уменьшается на единицу Поскольку в счетчике 4 записан нулевой код. то на его выходе заема присут- ствует единичный сигнал, поступающий на

0 вход ошибки блока 7, в результате чего на выходе частоты блока анализа отсутствуют импульсы частоты и счетчик 4 не изменяет своего состояния В этом случае значение сигнала на выходе знака ошибки блока 7,

5 поступающего на вход управления реверсом счетчика 4, безразлично.

При поступлении второго после запуска устройства импульса на вход 14 синхронизации триггер 9 по его фронту устанавлива0 ется в исходное состояние, и на входе запрета делителя 8 частоты устанавливается нулевой сигнал, который запрещает прохождение импульсов на выход делителя, вследствие чего исключается возможность

5 изменения состояния счетчиков 2 и 3 и записи в счетчик 4 искаженного кода. Затем задерживающий импульс с выхода элемента 10 задержки поступает на вход записи счетчика 4. на входы информации которого

0 поступает код состояния разрядов с выхода вычитающего счетчика 3. Если в течение первого цикла работы устройства частоты генератора 1 сохраняла свое номинальное значение, то на входы счетчиков 2 и 3 долж5 но было поступить h импульсов с выхода делителя 8 частоты Следовательно, на каждом из L выходов 15 устройства будет сформировано по I выходных импульсов в счетчике 2 выполнит I полных циклов пересчета импульсов и придет в исходное состояние. а содержимое счетчика 3 станет равным нулю. Таким образом, по импульсу на входе записи счетчика 4 в него запишется опять нулевой код и дальнейшая работа устройства во втором цикле будет аналогична описанной.

Если в течение второго цикла работы устройства частота генератора 1 увеличилась, то за один цикл работы на входы счетчиков 2 и 3 поступает (n+К) импульсов.

После отсчета п импульсов счетчиком 3 его состояние становится равным нулю и на его выходе заема появляется единичный сигнал, поступающий на вход управления блока 7, а по (п-Н)-му импульсу все разряды счетчика принимают единичное значение и сигнал на его выходе заема вновь становится нулевым. В дальнейшем по каждому импульсу на входе счетчика 3, начиная с (п+2)-го, из кода Все единицы вычитается по единице. Одновременно счетчик 2 продолжает пересчет импульсов и на выходах 15 устройства формированы избыточные импульсы, общее количество которых равно К. В момент поступления синхроимпульса на вход 14 устройства триггер 9 устанавливается в исходное состояние и нулевым сигналом на входе запрета делителя 8 частоты блокирует его работу Так как на вход счетчика 3 поступило (n+К) импульсов, то его состояние отличается от нуля, и код, находящийся в счетчике, представляет собой второй дополнительный код числа К, т. е. обратный код числа К, увеличенный на единицу Этот код поступает на входы информации счетчика 4 и по импульсу с выхода первого элемента 10 задержки записывается в него. С выходов счетчика 4 второй дополнительный код числа К поступает на входы второй группы сумматора 5, на входы первой группы которого поступает код . При сложении этих концов на выходе сумматора 5 получается разность между значением кода синхронизации и количеством избыточных импульсов

An n-k,

(2)

представляющая собой код суммарного количества импульсов, которое необходимо сформировать на выходах 15 устройства, в следующем цикле работы устройства, чтобы их суммарное количество за истекающий (второй) и последующий (третий) циклы работы равнялось 2п, т. е. в среднем по п импульсов за цикл. По импульсу с выхода второго элемента 11 задержки число А П записывается в счетчик 3 Так как в счетчике 4 записан второй дополнительный код числа К, отличный от нуля, то на его выходе заема появляется нулевой сигнал, поступающий на вход ошибки блока 7 Так как на 5 вход управления этого блока в предыдущем цикле поступал единичный сигнал с выхода заема счетчика 3, то по импульсу на еходе записи блока 7 на выходе знака ошибки устанавливается единичный сигнал, кото10 рый, поступая на вход реверса счетчика 4 переводит его в режим суммирования Кроме того, на выходах управления блока 7 ус- танавливаются единичные сигналы задающие коэффициенты деления управля5 емого делителя 8 частоты . После окончания импульса с выхода элемента 11 задержки триггер 9 устанавливается в Г и разрешает работу делителя 8 частоты. На выходе делителя появляется частота, в два

0 раза меньшая, чем при работе в предыдущем цикле, которая поступает на С-входы счетчиков 2 и 3 и вход синхронизации блока 7 Счетчик 2 производит пересчет импульсов, и на выходах 15 устройства появляются

5 выходные сигналы, но частота их изменения в два раза меньше номинальной Одновременно по каждому из этих импульсов содержимое счетчика 3 уменьшается на единицу, а на С-вход счетчика 4 поступают

0 импульсы с выхода частоты блока 7, причем частота этих импульсов равна частоте на выходе делителя 8. Счетчик 4 по каждому из этих импульсов увеличивает свое содержимое на единицу и при поступлении на его

5 С-вход К-го импульса значение всех его разрядов становится равным нулю, а на выходе заема появляется единичный сигнал, который поступает на вход ошибки блока 7. После этого на втором выходе управления

0 этого блока появляется нулевой сигнал и прекращается формирование импульсов частоты на выходе частоты этого же блока. Это приводит к тому что счетчик 4 остается в нулевом состоянии, а коэффициент деления

5 делителя 8 частоты становится равным номинальному () и дальнейшая работа устройства до конца цикла происходит аналогично описанной. Таким образом, для компенсации положительной ошибки в те0 чение К периодов выходных импульсов делителя 8 частоты частота была в два раза меньше номинальной и за это время вместо К импульсов номинальной частоты было выдано К импульсов в два раза меньшей час5 тоты, т. е. в течение третьего цикла работы было сформировано А п п- К выходных импульсов на выходах 15 устройства, что в сумме за предыдущий и текущий циклы составляет 2 п или в среднем по п импульсов

за цикл Так как счетчик 2 по окончании цикла работы в котором была определена ошибка не приводился в исходное состояние, то после поступления на его С-вход Лп импульсов он должен установиться в исходное состояние к окончанию третьего цикла работы, если в процессе отработки этого цикла не накопилось новой ошибки.

Пусть в третьем цикле работы устройства частота генератора 1 уменьшилась. В этом случае на выходах 15 устройства формируется меньшее количество импульсов (n-m) и после окончания третьего цикла в сметчике 3 находится число т, равное числу недостающих импульсов, выраженное в прямом коде, так как разряды счетчика 3 не принимали нулевого состояния Это приводит к тому что в третьем цикле работы на входе управления блока 7 единичный сигнал не появляется и при поступлении импульса на вход 14 синхронизации в счетчик 4 записывается число т, в счетчик 3 - число Лп-п+ m , на первом и втором выходах уп- равпения блока 7 устанавливаются нулевые сигналы а на выходе знака ошибки - нулевой сигнал

После окончания импульса с выхода Э1гм.нтз 11 задержки триггер 9 устанавливается в Г и разрешает работу делителя 8 члстоты который начинает формировать на своем выходе частоту, равную частоте генератора 1. так как на его входы управления поступают нулевые сигналы и его коэффициент деления Аналогично описанному по каждому из импульсов на выходе делителя в счетчике 3 происходит уменьшение содержимого на единицу, а счетчик 2 производит пересчет импульсов и на выходах 15 формируются выходные сигналы На выходе частоты блока 7 формируются импульсы, частота которых в два раза меньше частоты на выходе делителя 8. по каждому из которых из содержимого счетчика 4 вычитается единица, поскольку на его вход управления реверсом поступает нулевой сигнал с выхода знака ошибки блока 7. определяющий его работу в режиме вычитания. После поступления на С-вход счетчика 4 m импульсов его содержимое становится равным нулю а на выходе ззема устанавливается единичный сигнал который поступает на вход ошибки блока 7 Поступление этого сигнала на блок 7 приводит к тому, что на его первом выходе устанавливается единичный сигнал, на втором выходе сохраняется нулевой сигнал, а на выходе частоты прекращается формирование импульсов и устанавливается единичный сигнал После этого сигналы с выходов управления блока

7 поступают на одноименные входы делителя 8 частоты и устанавливают его коэффициент деления Дальнейшая работа устройства до конца цикла аналогична описанной. В итоге в течение четвертого цикла работы устройства на выходах устройства будет сформировано (n+m) импульсов и, если не произойдет накопления ошибки за четвертый цикл работы, к окончанию цикла

состояние счетчика 3 должно равняться нулю, счетчик 2, пересчитав номинальное за четыре цикла работы 4 п количество импульсов, устанавливается в исходное состояние и дальнейшая работа устройства происходит аналогично описанной.

Формула изобретения Устройство для синхронизации вычислительной системы, содержащее генератор

тактовых импульсов, делитель частоты, первый счетчик, дешифратор, причем выход генератора тактовых импульсов подключен к тактовому входу делителя частоты, выход которого соединен со счетным входом первого счетчика, выход которого соединен с v входом дешифратора, выход которого является информационным выходом устройства, отличающееся тем, что, с целью повышения достоверности функционирования устройства, в него введены два счетчика, сумматор, триггер, два элемента задержки, блок анализа, причем первый вход сумматора соединен с входом кода синхронизации устройства, второй вход и

выход сумматора - соответственно с информационным выходом второго счетчика и информационным входом третьего счетчика, информационный выход которого соединен с информационным входом второго счетчика вход пуска устройства подключен к входам начальной установки первого и третьего счетчиков и информационному входу триггера, выход делителя частоты соединен с синхровходами блока анализа и третьего

счетчика, вход синхронизации устройства подключен к входу сброса триггера и через первый элемент задержки к входу разрешения второго счетчика, вхсду записи блока анализа и входу второго элемента задержки, выход которого соединен с синхровхо- дом триггера входом разрешения третьего счетчика, первым установочным входом блока анализа и установочным входом делителя частоты, прямой выход триггера соединен с входом разрешения делителя частоты, выход переполнения второго счетчика - с входом признака ошибки блока анализа, выход переполнения третьего счетчика - с вторым установочным входом блока анализа

первый выход блока анализа соединен со счетным входом второго счетчика, второй выход - с синхроеходом второго счетчика, третий и четвертый выходы - с информационными входами делителя частоты, блок анализа содержит три триггера, три элемента И, два элемента ИЛИ и элемент НЕ, причем в блоке анализа выход первого триггера соединен с информационным входом второго триггера, прлмой выход которого являет- ся первым выходом блока анализа, синхровход второго триггера и вход сброса третьего триггера соединены с входом записи блока анализа, первые входы первого и второго элементов И и синхровход перво- го триггера соединены с синхровходом блока анализа, прямой выход второго триггера - с первым входом третьего элемента И. второй вход которого соединен с вторым входом первого элемента И и выходом 2S.

Ј6- 273829 rW3

Рие 4

элемента НЕ, вход которого является входом признака ошибки блока анализа и соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с вторым входом второго элемента И и выходом третьего элемента И, входы второго элемента ИЛИ соединены соответственно с выходами третьего триггера и второго элемента И, выход первого элемента И соединен с синхровходом третьего триггера, выходы второго элемента ИЛИ, первого элемента ИЛИ и третьего элемента И являются вторым, третьим и четвертым выходами блока анализа соответственно. R- и J- входы первого триггера соединены с первым и вторым установочными входами блока анализа соответственно, К-вход с шиной нулевого потенциала блока анализа, инверсный выход второго триггера ёоединен с третьим входом первого элемента И.

SO

-J/

32

35

s

&

«O CO

e

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1149235A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для синхронизации вычислительной системы | 1986 |

|

SU1456942A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-07-30—Публикация

1990-07-10—Подача