Изобретение относится к измерительной технике и предназначено для измерения параметров амплитудно-моду- лированных (AM) сигналов при синусоидальной форме огибающей, а именно: амплитуд, несущей и огибающей, глубины модуляции, фаз несущей и огибающей.

Цель изобретения - повышение точности за счет исключения методической погрешности дискретности, уменьшение

времени измерений и расширение функциональных возможностей за счет измерения фазы несущей.

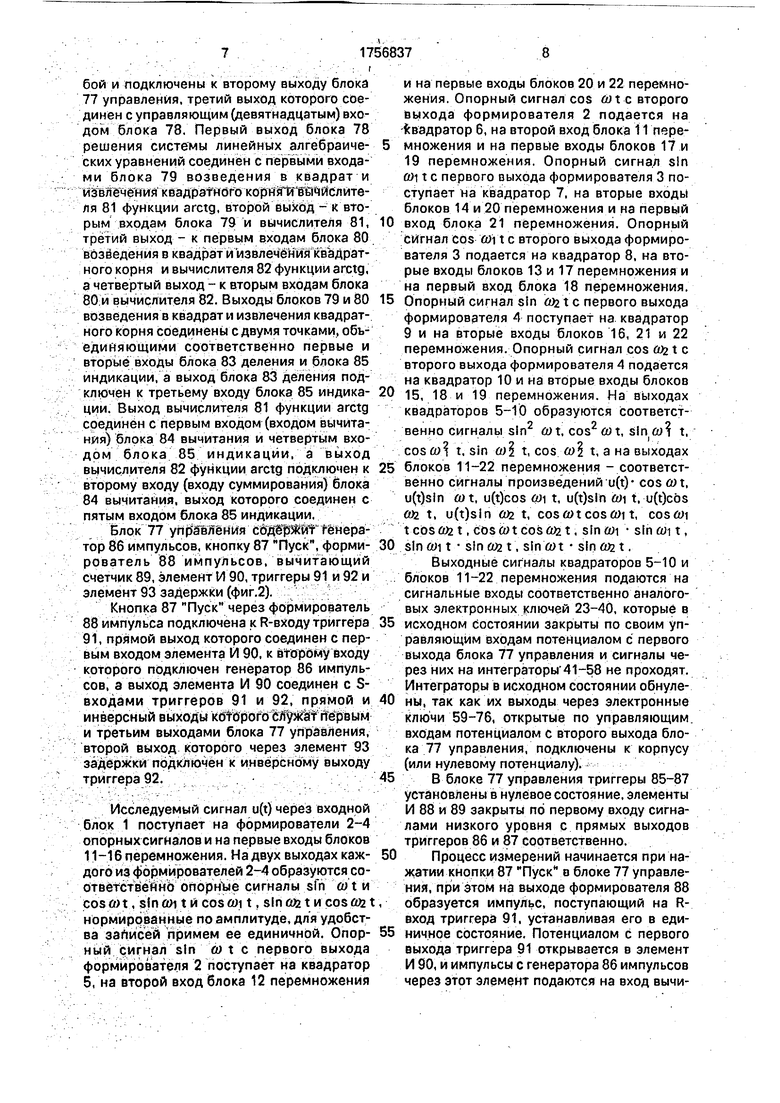

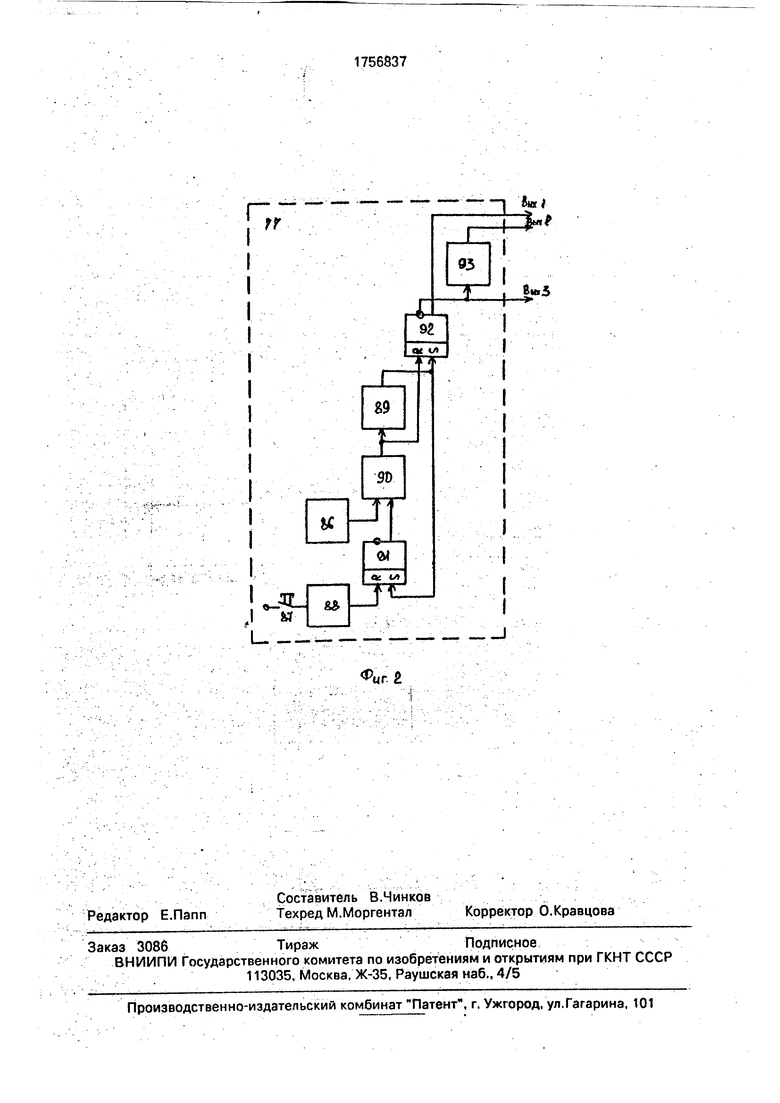

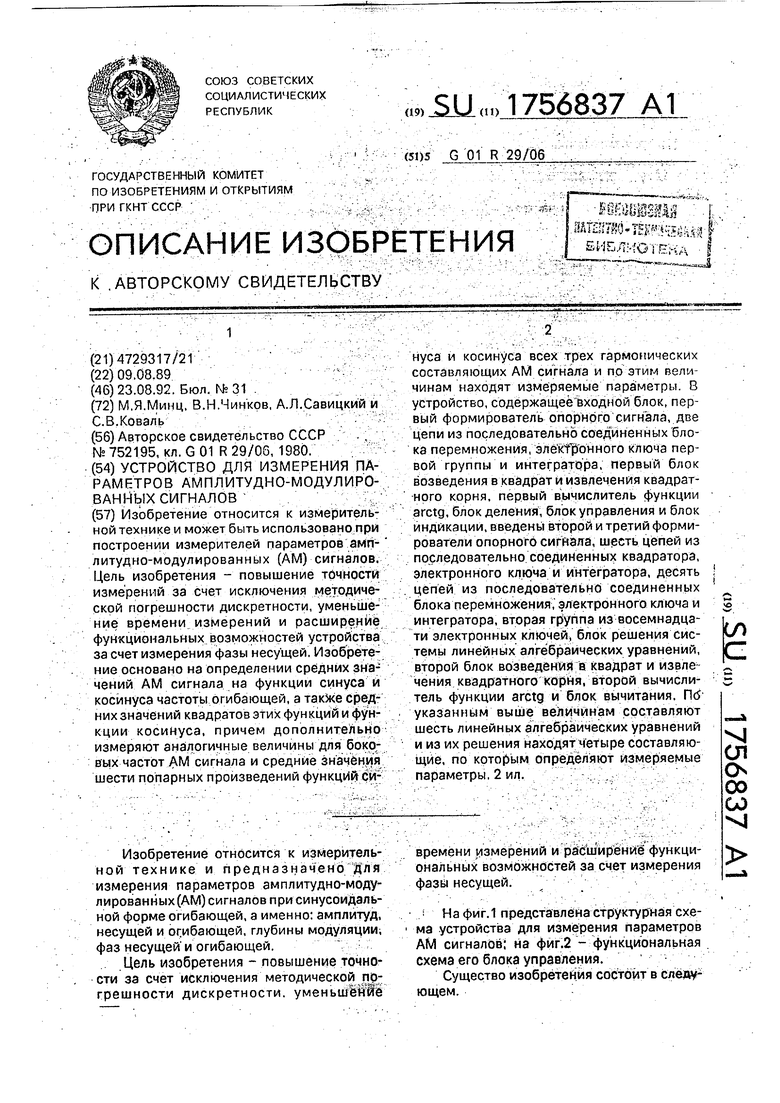

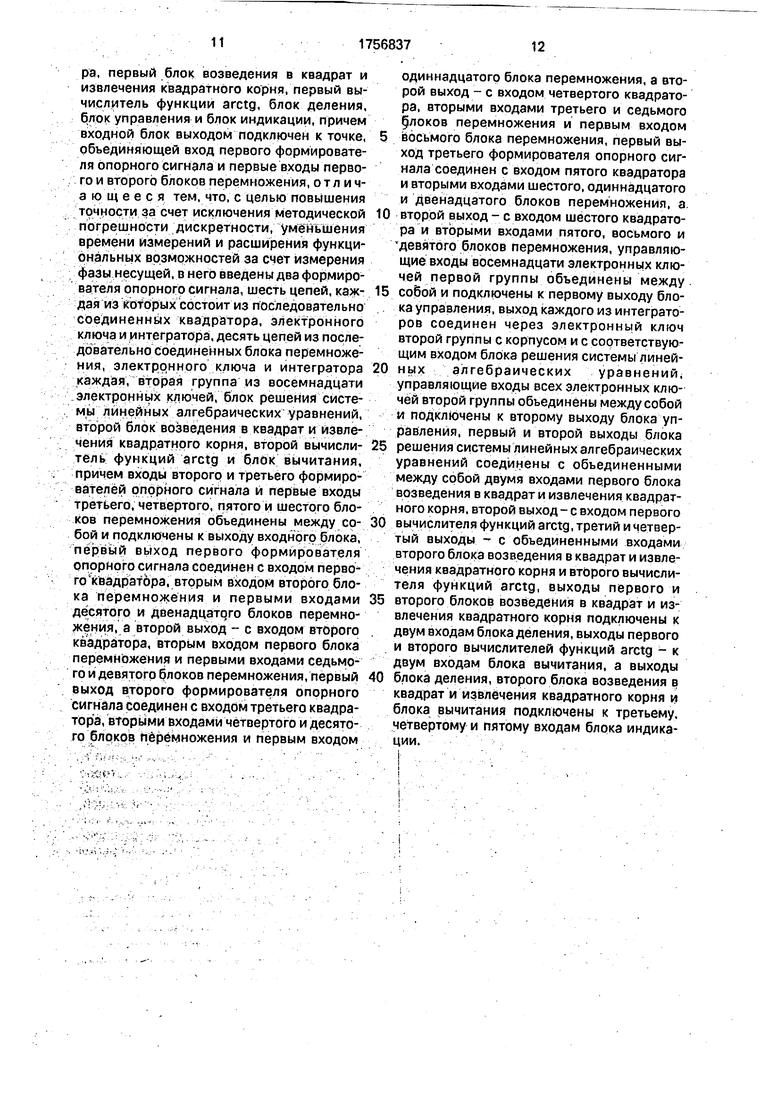

На фиг.1 представлена структурная схема устройства для измерения параметров AM сигналов; на фиг.2 - функциональная схема его блока управления.

Существо изобретения состоит в слеау- ющем.

где

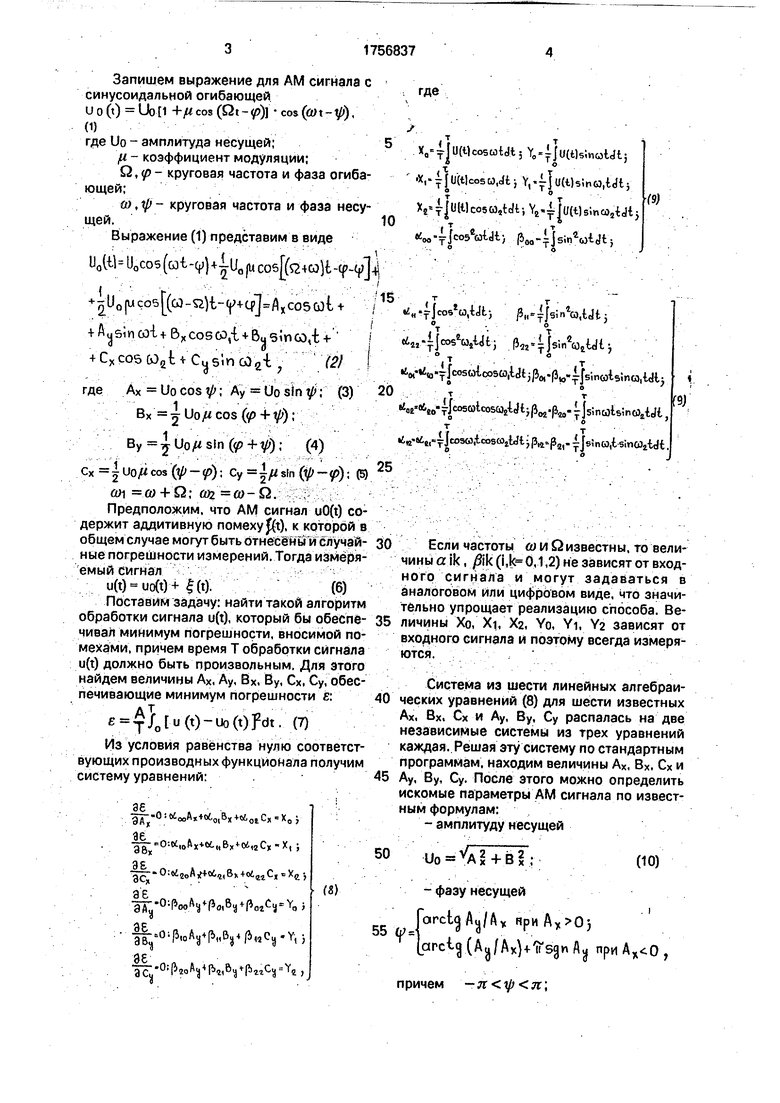

Запишем выражение для AM сигнала с синусоидальной огибающей

Uo(t) +ficos () cos(uH-V),

(1)s

где Uo - амплитуда несущей;5

fi - коэффициент модуляции;

Q.p- круговая частота и фаза огиба-«.ОДесваД} .Ub

й-от о

Xe4JUMcosuWt 5 Ye.i}u(t)s neUtj

ющей;

щей.

a),ip- круговая частота и фаза несу-X8«f juiilcos a«toli-, Y8«ifuctisincojUt,

10

(9)

Выражение (1) представим в виде oo-ffc05 &&-, (5ОТ--jsin4u)tJt;

U0(i U0C05 (CO t-ф) 4iU0 |U C05(Q4CO)t-Ср-у ц|

+ (a-a)i-v+tfJ AJlco5fi)t + ,15 .) ft.-Ai-Vuti

/оо

+ A 5;ncoUB,costt,l + &3smGvt+ .

+ C,COS togt + CuSincOn-t ,(2)„ . л i,in° IТ ,

92 V {ra e Jtj|VP 4Js in e n j

и 6

тT

iW4|eo9ce tco8e Ut j p.pj,. i e5nco,t Sincoz-tJt.

где Ax Uocos ; Ay Uosln# ; (3) 20т т ы

BX « Uo/г cos g + V): - «« « ti - lrtnelrtn ut,

(+V),- (4) Cx | (-0); Cy |/lsin (V-f): (5) 25

ftfl o + Q; ей -со- Й.

Предположим, что AM сигнал uO(t) содержит аддитивную помеху$t), к которой в

общем случае могут быть отнесены и случай- 30Если частоты са и Q известны, то велиные погрешности измерений. Тогда измеря-ЧИны a ik, /5ik (i,k 0,1,2) не зависят от входемый сигналного сигнала и могут задаваться в

u(t) uo(t) + 5 W- (6)аналоговом или цифровом виде, что значиПоставим задачу: найти такой алгоритмтельно упрощает реализацию способа. Веобработки сигнала u(t), который бы обеспе- 35личины Хо, Xi, X2, Yo, Yi, Y2 зависят от

чивал минимум погрешности, вносимой по-входного сигнала и поэтому всегда измерямехами, причем время Т обработки сигналаются. u(t) должно быть произвольным. Для этого

найдем величины Ах, Ау, Вх, By, Cx, Су, обес-Система из шести линейных алгебраипечивающие минимум погрешности Е: 40ческих уравнений (8) для шести известных

ruM-unMFdt тАх Вх Сх и Ау Ву Су Распалась на Две

TJol uw чнезависимые системы из трех уравнений

Из условия равенства нулю соответст-каждая. Решая эту систему по стандартным

вующих производных функционала получимпрограммам, находим величины Ах, Вх, Сх и

45 Ay, By, Су. После этого можно определить искомые параметры AM сигнала по известным формулам:

систему уравнений:

ае

gj-O: «„Аиобо.Вх Сх - Х0 }

ас «0:«,0Ах+«.,, ;

3Ј

0.«i2oA c6,,8x +otMC, « Хе ,

4i

ЭЕ

+ ,}

О

|r..(,Bj4/5,7crY,)

(В)

38 3C:-05|iwA |bi,B.,t|b«C Yt,

о

где

Xe4JUMcosuWt 5 Ye.i}u(t)s neUtj

(9)

и 6

тT

iW4|eo9ce tco8e Ut j p.pj,. i e5nco,t Sincoz-tJt.

- «« « ti - lrtnelrtn ut,

программам, находим величины Ах, Вх, Сх и

Ay, By, Су. После этого можно определить искомые параметры AM сигнала по известным формулам:

- амплитуду несущей

50

Uo- x+Bi; - фазу несущей

(Ю)

55 (р

ГагсЦ нри arctg ()4-1Г5дп А при ,

причем - )7t

- амплитуду огибающей игщ 2 7вТ+вУ

или

Um2 2VCi+C - фазу огибающей

(12)

, ()-Vпри6х 0)

. аРс Свд/вхКвдпВ приВ о. - глубину или коэффициент модуляции

Um1/Uo

или

fl2 Um2/Uo(14)

Можно взять среднее значение глубины модуляции

() и оценить погрешность измерения ft:

4

l/л .

Это же относится и к фазам несущей и огибающей, если предварительно определить величины:

arc

Н

В,

при

агсЦ(Бе|/Вх / 6 при j

у-ср.

arctcjCij/Cx приСх 0; аРсЦ(С(Су)чу1Г5 пСу приСх 0,

а затем найти

Cf-Ј(v«pHit -4 }

).

Можно также оценить остаточную погрешность

(t)-uo(t)32dt, ,

если в выражение (1) для uo(t) подставить полученные значения

AXI Ay, Bx, By, Cx, Су.

Таким образом, устройство основано на выполнении следующих основных операций:

-выделении и формировании шести опор- ных сигналов sin ом и cos cot; )i t и coso)i t; slntwztncosftfct ;

-измерении величин Хо и Yo; Xi и Yi; X nY2;

-измерении и задании величин айои#ю;а11и/ 11 ;«22и/ 22;

/ 10;002 «20ИД)2 Дю;«21 «12 И

jfei /812:

-определении величин Ах, Вх (или Сх) и Ау, Ву (или Су) путем решения двух независимых систем из трех уравнений, входящих в систему уравнений (8);

-определении параметров AM сигнала Uo. Um-V- . р и ju .

Устройство содержит входной блок 1, формирователи 2-4 опорных сигналов, квадраторы 5-10, блоки 11-22 перемножения, первую группу электронных ключей 23- 40, интеграторы 41-58. вторую группу электронных ключей 59-76, блок 77 управ- ления, блок 78 решения системы линейных алгебраических уравнений, блоки 79 и 80 возведения в квадрат и извлечения квадратного корня, вычислители 81 и 82 функций arctg, блок 83 деления, блок 84 вычитания, блок 85 индикации (фиг. 1).

Вход устройст&а через входной или масштабный блок 1 соединен с входами формирователей 2-4 опорных сигналов и первыми

входами блоков 11-16 перемножения. Первый выход формирователя 2 опорного сигнала подключен к входу квадратора 5, второму входу блока 12 перемножения и первым входам блоков 20 и 22 перемножения, а второй выход - к входу квадратора 6, второму входу блока fl перемножения и первым входам блоков 17 и 19 перемножения. Первый выход формирователя 3 опорного сигнала соединен с входом квадратора

7, вторыми входами блоков 14 и 20 перемножения и первым входом блока 21 перемножения, а второй выход с входом квадратора 8, вторыми входами блоков 13 и 17 перемножения и первым входом блока 18 перемножения. Первый выход формирователя 4 опорного сигнала подключен к входу квад-° ратора 9 и вторым входам блоков 16,21 и 22 перемножения, а второй выход - к входу квадратора 10 и вторым входам блоков 15,

18и 19 перемножения. Выходы квадраторов 5-10 и блоков 11-22 перемножения через электронные ключи 23-40 подключены к входам интеграторов 41-58 соответственно. Управляющие входы электронных ключей

23-40 объединены между собой и соединены с первым выходом блока 77 управления. Выход каждого из интеграторов41-58 подключен к соответствующему сигнальному входу (от первого до восемнадцатого) блока 78 решения системы линейных алгебраических уравнений и- сигнальному входу одного из электронных ключей 59-76, выходы которых соединены с шиной нулевого потенциала, а управляющие входы объединены между собой и подключены к второму выходу блока 77 управления, третий выход которого соединен с управляющим (девятнадцатым) входом блока 78. Первый выход блока 78 решения системы линейных алгебраиче- ских уравнений соединен с первыми входами блока 79 возведения в квадрат и извлечения квадратного корняТгг в Йчйслите- ля 81 функции arctg, второй выход - к вторым входам блока 79 и вычислителя 81, третий выход - к первым входам блока 80 возёедения в квадрат и извлечения квадратного корня и вычислителя 82 функции arctg, а четвертый выход - к вторым входам блока 80 и вычислителя 82. Выходы блоков 79 и 80 возведения в квадрат и извлечения квадратного корня соединены с двумя точками, объединяющими соответственно первые и вторые входы блока 83 деления и блока 85 индикации, а выход блока 83 деления подключен к третьему входу блока 85 индика- ции. Выход вычислителя 81 функции arctg соединен с первым входом (входом вычитания) блока 84 вычитания и четвертым входом блока 85 индикации, а выход вычислителя 82 функции arctg подключен к второму входу (входу суммирования) блока 84 вычитания, выход которого соединен с пятым входом блока 85 индикации.

Блок 77 упр Эвлёния генератор 86 импульсов, кнопку 87 Пуск, форми- рователь 88 импульсов, вычитающий счетчик 89, элемент И 90, триггеры 91 и 92 и элемент 93 задержки (фиг.2).

Кнопка 87 Пуск через формирователь 88 импульса подключена к R-входу триггера 91, прямой выход которого соединен с первым входом элемента И 90, к второму входу которого подключен генератор 86 импульсов, а выход элемента И 90 соединен с S- входами триггеров 91 и 92, прямой и инверсный выходы которого сйужаг первым и третьим выходами блока 77 управления, второй выход которого через элемент 93 задержки подключен к инверсному выходу триггера 92.

Исследуемый сигнал u(t) через входной блок 1 поступает на формирователи 2-4 опорных сигналов и на первые входы блоков 11-16 перемножения. На двух выходах каж- дого из формирователей 2-4 образуются соответственно опорн ые сигналы sfn (о t и

, Sin tHCOSft) t , SlnOfctMCOSftfct

нормированные по амплитуде, для удобства записей примем ее единичной. Опор- ный сигнал sin a) t с первого выхода формирователя 2 поступает на квадратор 5, на второй вход блока 12 перемножения

и на первые входы блоков 20 и 22 перемножения. Опорный сигнал cos UH с второго выхода формирователя 2 подается на Квадратор 6, на второй вход блока 11 перемножения и на первые входы блоков 17 и 19 перемножения. Опорный сигнал sin с первого выхода формирователя 3 поступает на квадратор 7, на вторые входы блоков 14 и 20 перемножения и на первый вход блока 21 перемножения. Опорный сигнал cos t с второго выхода формирователя 3 подается на квадратор 8, на вторые входы блоков 13 и 17 перемножения и на первый вход блока 18 перемножения. Опорный сигнал sin чг t с первого выхода формирователя 4 поступает на квадратор 9 и на вторые входы блоков 16, 21 и 22 перемножения. Опорный сигнал cos (Ог t с второго выхода формирователя 4 подается на квадратор 10 и на вторые входы блоков 15, 18 и 19 перемножения. На выходах квадраторов 5-10 образуются соответственно сигналы sin2 О) t, COS2 ft) t, Sin W2 t,

cos 0) t, sin d) t, cos со t, а на выходах блоков 11-22 перемножения - соответственно сигналы произведений u(t)- cos wt, u(t)sin ft)t, u(t)cos ffli t, u(t)sln йл t, u(t)cos ftfc t, u(t)sin (Oi t, cosft)tcosft i t,

tCOSftfct , COSft tCOSUfct , SinWl t , Sin 0) t Sin ОД2 t , Sin ft)t Sin (Oi t .

Выходные сигналы квадраторов 5-10 и блоков 11-22 перемножения подаются на сигнальные входы соответственно аналоговых электронных ключей 23-40, которые в исходном состоянии закрыты по своим управляющим входам потенциалом с первого выхода блока 77 управления и сигналы через них на интеграторы 41-58 не проходят. Интеграторы в исходном состоянии обнулены, так как их выходы через электронные ключи 59-76, открытые по управляющим входам потенциалом с второго выхода блока 77 управления, подключены к корпусу (или нулевому потенциалу).

В блоке 77 управления триггеры 85-87 установлены в нулевое состояние, элементы И 88 и 89 закрыты по первому входу сигналами низкого уровня с прямых выходов триггеров 86 и 87 соответственно.

Процесс измерений начинается при нажатии кнопки 87 Пуск в блоке 77 управления, при этом на выходе формирователя 88 образуется импульс, поступающий на R- вход триггера 91, устанавливая его в единичное состояние. Потенциалом с первого выхода триггера 91 открывается в элемент И 90, и импульсы с генератора 86 импульсов через этот элемент подаются на вход вычи1756837

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой анализатор спектра | 1990 |

|

SU1777096A1 |

| Цифровой измеритель коэффициента нелинейных искажений | 1976 |

|

SU618695A1 |

| Способ измерения амплитуды сигнала | 1986 |

|

SU1465786A1 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 2013 |

|

RU2541147C1 |

| ИЗМЕРИТЕЛЬ ДЕВИАЦИИ ЧАСТОТЫ СИГНАЛОВ С ГАРМОНИЧЕСКОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 1992 |

|

RU2054680C1 |

| Квазикогерентный демодулятор сигналов манипуляции с минимальным сдвигом | 1987 |

|

SU1561214A1 |

| Устройство для измерения девиации частоты,возникающей при паразитном преобразовании амплитудной модуляции в частотную | 1984 |

|

SU1176261A1 |

| Адаптивный частотный детектор | 1990 |

|

SU1805544A1 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА АНАЛОГОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1994 |

|

RU2106747C1 |

| СПОСОБ АВТОКОРРЕЛЯЦИОННОГО ПРИЕМА ШУМОПОДОБНОГО СИГНАЛА | 2006 |

|

RU2309550C1 |

Изобретение относится к измерительной технике и может быть использовано при построении измерителей параметров амп- литудно-модулированных (AM) сигналов. Цель изобретения - повышение точности измерений за счет исключения методической погрешности дискретности, уменьшение времени измерений и расширение функциональных возможностей устройства за счет измерения фазы несущей. Изобретение основано на определении средних значений AM сигнала на функции синуса и косинуса частоты огибающей, а также средних значений квадратов этих функций и функции косинуса, причем дополнительно измеряют аналогичные величины для боковых частот AM сигнала и средние значения шести попарных произведений функций синуса и косинуса всех трех гармонических составляющих AM сигнала и по этим вели чинам находят измеряемые параметры В устройство, содержащее входной блок, первый формирователь опорного сигнала, две цепи из последовательно соединенных блока перемножения, электронного ключа первой группы и интегратора, первый блок возведения в квадрат и извлечения квадратного корня, первый вычислитель функции arctg, блок деления, блок управления и блок индикации, введены второй и третий формирователи опорного сигнала, шесть цепей из последовательно соединенных квадратора, электронного ключа и интегратора, десять цепей из последовательно соединенных блока перемножения, электронного ключа и интегратора, вторая группа из восемнадцати электронных ключей, блок решения системы линейных алгебраических уравнений, второй блок возведений а квадрат и извле чения квадратного корня, второй вычислитель функции arctg и блок вычитания. Пб указанным выше величинам составляют шесть линейных алгебраических уравнений и из их решения находят четыре составляющие, по которым определяют измеряемые параметры, 2 ил. (Л С vi ел о 00 со VJ

тающего счетчика 89 и на R-вход триггера 92. Первым тактовым импульсом, поступающим с выхода элемента И 90 на R-вход триггера 92, последний устанавливается в единичное состояние. Потенциалом с прямого выхода триггера 92, подаваемым по, первому выходу блока 77 управления на объединенные между собой управляющие входы электронных ключей 23-40, последние открываются, и сигналы с выходов квадраторов 5-10 и блоков 11-22 перемножения поступают на интеграторы 41-58 соответственно. Одновременно с этим потенциалом с инверсного выхода триггера 92, подаваемым по второму выходу блока 77 управления на объединенные между собой управляющие входы электронных ключей 59-76, последние закрываются, снимая нулевой потенциал с выходов интеграторов.

С поступлением на вычитающий счетчик 89 числа тактовых импульсов, равного Кп, он обнуляется и на его выходе образуется сигнал переполнения, который подаемся на S-входы триггеров 91 и 92, возвращая Их в исходное (нулевое) состояние. Тем самым сигналом с прямого выхода триггера 91 закрывается элемент И 90, а сигналом с прямого выхода триггера 92 (первый выход блока 77 управления) закрываются электронные ключи 23-40. К этому моменту времени на выходах интеграторов 41-58 образуются напряжения, пропорциональные соответственно величинам

А , «ЭО , , 011 , , «22 , Хо, Yo, XL Vl,

Ха, Y2, «01. CCQZ , , /%1 , Д)2 , . Эти напряжения вводятся в блок 78 решения системы линейных алгебраичебких уравнений по сигналу, поступающему с третьего выхода блока 77 управления на девятнадцатый вход, вход управления блока 78, в котором осуществляется решение системы уравнений (8), в результате чего на его четырех выходах образуются сигналы (аналоговые или цифровые), пропорциональные величинам Ах, Ау, Вх, By. С задержкой, определяемой временем переходных процессов блока 78 и задаваемой элементом 93 задержки в блоке 77 управления, на его втором выходе образуется потенциал, которым электронные ключи 59-76 открываются, закорачивая выходы интеграторов 41-58 на корпус и тем самым обнуляя их (или возвращая в исходное состояние).

Сигналы, пропорциональные величинам АХ и Ау,. с первого и второго выходов блока 78 поступают на блок 79 возведения в квадрат и извлечения квадратного корня и на вычислитель 81 функции arctg, на выходах которых образуются сигналы, пропорциональные амплитуде несущей Uo согласно формуле (10) и фазе несущей согласно формуле (11).

Сигналы, пропорциональные величинам Вх и Ву, с третьего и четвертого выходов блока 78 поступают на блок 80 возведения в квадрат и извлечения квадратного корня и на вычислитель 82 функции arctg, на выходах которых образуются сигналы, пропорциональные амплитуде огибающей Umi согласно формуле (12) и величине arctg(By/Bx) при Вх 0 и величине arctg(By/Bx) + jrsgnBy при Вх 0.

Сигналы с выходов блоков 79 и 80 возведения в квадрат и извлечения квадратного корня подаются на блок 83 деления, на выходе которого образуется сигнал, пропорциональный коэффициенту модуляции I согласно формуле (14).

Сигналы с выходов вычислителей 81 и 82 функции arctg поступают на блок 84 вычитания, на выходе которого образуется сигнал, пропорциональный фазе огибающей согласно формуле (13).

Выходные сигналы блоков 79-84, пропорциональные измеряемым величинам Uo. Dm, /i, V; и V соответственно, поступают на блок 85 индикации для отображения результатов измерений. На этом процесс измерений завершается.

Таким образом, использование предла- гаемого способа и устройства для измерения параметров амплитудно-моду- лированных сигналов, обеспечивает повышение точности измерений, которое обусловлено исключением методической погрешности дискретности, вызываемой тем, что в известных изобретениях для определения коэффициента модуляции и фазы

огибающей используются только отдельные отсчеты (или мгновенные значения) AM сигнала, соответствующие амплитудам несущей за период огибающей, а в предлагаемом устройстве - все мгновенные

значения AM сигнала за время измерений Т; уменьшение времени измерений, которое может быть выбрано произвольно и, как показано выше, меньше периода огибающей, что особенно существенно при низких и инфранизких частотах; расширение функциональных возможностей за счет измерения фаз огибающей и несущей.

Формула изобретения Устройство для измерения параметров

амплитудно-модулированных сигналов, содержащее входной блок, первый формирователь опорного сигнала, две цепи из последовательно соединенных блока перемножения, электронного ключа и интегратоpa, первый блок возведения в квадрат и извлечения квадратного корня, первый вычислитель функции arctg, блок деления, блок управления и блок индикации, причем входной блок выходом подключен к точке, объединяющей вход первого формирователя опорного сигнала и первые входы первого и второго блоков перемножения, отличающееся тем, что, с целью повышения точности за счет исключения методической погрешности дискретности, уменьшения времени измерений и расширения функциональных возможностей за счет измерения фазы несущей, в него введены два формирователя опорного сигнала, шесть цепей, каждая из которых состоит из поел едо вате л ь но соединенных квадратора, электронного ключа и интегратора, десять цепей из последовательно соединенных блока перемножения, электронного ключа и интегратора каждая, вторая группа из восемнадцати электронных ключей, блок решения системы линейных алгебраических уравнений, второй блок возведения в квадрат и извлечения квадратного корня, второй вычислитель функций arctg и блок вычитания, причем входы второго и третьего формирователей опорного сигнала и первые входы третьего, четвертого, пятого и шестого блоков перемножения объединены между собой и подключены к выходу входного блока, первый выход первого формирователя опорного сигнала соединен с входом первого «свадратбра. вторым входом второго блока перемножения и первыми входами десятого и двенадцатого блоков перемножения, а второй выход - с входом второго квадратора, вторым входом первого блока перемножения и первыми входами седьмого и девятого блоков перемножения, первый выход второго формирователя опорного сигнала соединен с входом третьего квадратора, вторыми входами четвертого и десятого блоков перемножения и первым входом

одиннадцатого блока перемножения, а второй выход - с входом четвертого квадратора, вторыми входами третьего и седьмого бтюков перемножения и первым входом

восьмого блока перемножения, первый выход третьего формирователя опорного сигнала соединен с входом пятого квадратора и вторыми входами шестого, одиннадцатого и Двенадцатого блоков перемножения, а.

второй выход - с входом шестого квадратора и вторыми входами пятого, восьмого и девятого блоков перемножения, управляющие входы восемнадцати электронных ключей первой группы объединены между

собой и подключены к первому выходу блока управления, выход каждого из интеграторов соединен через электронный ключ второй группы с корпусом и с соответствующим входом блока решения системы линейных алгебраических уравнений; управляющие входы всех электронных ключей второй группы объединены между собой и подключены к второму выходу блока управления, первый и второй выходы блока

решения системы линейных алгебраических уравнений соединены с объединенными между собой двумя входами первого блока возведения в квадрат и извлечения квадратного корня, второй выход - с входом первого

вычислителя функций arctg, третий и четвертый выходы - с объединенными входами второго блока возведения в квадрат и извлечения квадратного корня и второго вычислителя функций arctg, выходы первого и

второго блоков возведения в квадрат и извлечения квадратного корня подключены к двум входам блока деления, выходы первого и второго вычислителей функций arctg - к двум входам блока вычитания, а выходы

блока деления, второго блока возведения в квадрат и извлечения квадратного корня и блока вычитания подключены к третьему, четвертому и пятому входам блока индикации.

iC89SU

«VЈ

| Измеритель параметров амплитудномодулированных сигналов | 1978 |

|

SU752195A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-08-23—Публикация

1989-08-09—Подача